# E·XFL

Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                    |

|----------------------------|-----------------------------------------------------------|

| Core Processor             | eZ8                                                       |

| Core Size                  | 8-Bit                                                     |

| Speed                      | 20MHz                                                     |

| Connectivity               | I <sup>2</sup> C, IrDA, SPI, UART/USART                   |

| Peripherals                | Brown-out Detect/Reset, DMA, POR, PWM, WDT                |

| Number of I/O              | 31                                                        |

| Program Memory Size        | 64KB (64K x 8)                                            |

| Program Memory Type        | FLASH                                                     |

| EEPROM Size                | -                                                         |

| RAM Size                   | 4K x 8                                                    |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                 |

| Data Converters            | A/D 8x10b                                                 |

| Oscillator Type            | Internal                                                  |

| Operating Temperature      | -40°C ~ 105°C (TA)                                        |

| Mounting Type              | Surface Mount                                             |

| Package / Case             | 44-LQFP                                                   |

| Supplier Device Package    | 44-LQFP (10x10)                                           |

| Purchase URL               | https://www.e-xfl.com/product-detail/zilog/z8f6421an020eg |

|                            |                                                           |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| Flash Status RegisterPage Select RegisterFlash Sector Protect Register | 177 |

|------------------------------------------------------------------------|-----|

| Flash Frequency High and Low Byte Registers                            | 179 |

| Option Bits                                                            | 180 |

| Operation                                                              | 180 |

| Option Bit Configuration By Reset                                      |     |

| Option Bit Address Space                                               |     |

| Flash Memory Address 0000H                                             |     |

| Flash Memory Address 0001H                                             | 182 |

| On-Chip Debugger                                                       | 183 |

| Architecture                                                           | 183 |

| Operation                                                              |     |

| OCD Interface                                                          |     |

| DEBUG Mode                                                             |     |

| OCD Data Format                                                        |     |

| OCD Autobaud Detector/Generator                                        |     |

| OCD Serial Errors                                                      |     |

| Breakpoints                                                            |     |

| On-Chip Debugger Commands                                              |     |

| On-Chip Debugger Control Register Definitions                          |     |

| OCD Control Register                                                   |     |

| OCD Status Register                                                    |     |

| On-Chip Oscillator                                                     |     |

| Operating Modes                                                        |     |

| Crystal Oscillator Operation                                           |     |

| Oscillator Operation with an External RC Network                       | 198 |

| Electrical Characteristics                                             |     |

| Absolute Maximum Ratings                                               |     |

| DC Characteristics                                                     |     |

| On-Chip Peripheral AC and DC Electrical Characteristics                | 211 |

| AC Characteristics                                                     |     |

| General-Purpose I/O Port Input Data Sample Timing                      |     |

| General-Purpose I/O Port Output Timing                                 |     |

| On-Chip Debugger Timing                                                |     |

| SPI Master Mode Timing                                                 |     |

| SPI Slave Mode Timing                                                  |     |

| I <sup>2</sup> C Timing                                                |     |

| UART Timing                                                            | 223 |

#### 6

### **DMA Controller**

The Z8 Encore! XP F64xx Series feature three channels of DMA. Two of the channels are for register RAM to and from I/O operations. The third channel automatically controls the transfer of data from the ADC to the memory.

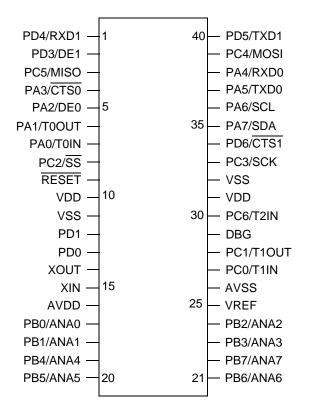

## **Pin Configurations**

Figures 2 through 7 display the pin configurations for all of the packages available in the Z8 Encore! XP F64xx Series. For signal descriptions, see <u>Table 3</u> on page 14.

Figure 2. Z8 Encore! XP F64xx Series in 40-Pin Dual Inline Package (PDIP)

**Note:** Timer 3 and T2OUT are not supported in the 40-pin PDIP package.

## **Signal Descriptions**

Table 3 lists the Z8 Encore! XP signals. To determine the available signals for a specific package style, see the <u>Pin Configurations</u> section on page 8.

| Signal<br>Mnemonic         | I/O        | Description                                                                                                                                                                                                                                                                                                   |

|----------------------------|------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| General-Pur                | pose I/O P | Ports A–H                                                                                                                                                                                                                                                                                                     |

| PA[7:0]                    | I/O        | Port A[7:0]. These pins are used for general-purpose I/O and support 5V-tolerant inputs.                                                                                                                                                                                                                      |

| PB[7:0]                    | I/O        | Port B[7:0]. These pins are used for general-purpose I/O.                                                                                                                                                                                                                                                     |

| PC[7:0]                    | I/O        | Port C[7:0]. These pins are used for general-purpose I/O. These pins are used for general-purpose I/O and support 5V-tolerant inputs                                                                                                                                                                          |

| PD[7:0]                    | I/O        | Port D[7:0]. These pins are used for general-purpose I/O. These pins are used for general-purpose I/O and support 5V-tolerant inputs                                                                                                                                                                          |

| PE[7:0]                    | I/O        | Port E[7:0]. These pins are used for general-purpose I/O. These pins are used for general-purpose I/O and support 5V-tolerant inputs.                                                                                                                                                                         |

| PF[7:0]                    | I/O        | Port F[7:0]. These pins are used for general-purpose I/O. These pins are used for general-purpose I/O and support 5V-tolerant inputs.                                                                                                                                                                         |

| PG[7:0]                    | I/O        | Port G[7:0]. These pins are used for general-purpose I/O. These pins are used for general-purpose I/O and support 5V-tolerant inputs.                                                                                                                                                                         |

| PH[3:0]                    | I/O        | Port H[3:0]. These pins are used for general-purpose I/O.                                                                                                                                                                                                                                                     |

| I <sup>2</sup> C Controlle | er         |                                                                                                                                                                                                                                                                                                               |

| SCL                        | 0          | Serial Clock. This is the output clock for the I <sup>2</sup> C. This pin is multiplexed with a general-purpose I/O pin. When the general-purpose I/O pin is configured for alternate function to enable the SCL function, this pin is open-drain.                                                            |

| SDA                        | I/O        | Serial Data. This open-drain pin transfers data between the I <sup>2</sup> C and a slave.<br>This pin is multiplexed with a general-purpose I/O pin. When the general-pur-<br>pose I/O pin is configured for alternate function to enable the SDA function,<br>this pin is open-drain.                        |

| SPI Controlle              | er         |                                                                                                                                                                                                                                                                                                               |

| SS                         | I/O        | Slave Select. This signal can be an output or an input. If the Z8 Encore! XP F64xx Series is the SPI master, this pin may be configured as the Slave Select output. If the Z8 Encore! XP F64xx Series is the SPI slave, this pin is the input slave select. It is multiplexed with a general-purpose I/O pin. |

| SCK                        | I/O        | SPI Serial Clock. The SPI master supplies this pin. If the Z8 Encore! XP F64xx<br>Series is the SPI master, this pin is an output. If the Z8 Encore! XP F64xx<br>Series is the SPI slave, this pin is an input. It is multiplexed with a general-pur-<br>pose I/O pin.                                        |

#### **Table 3. Signal Descriptions**

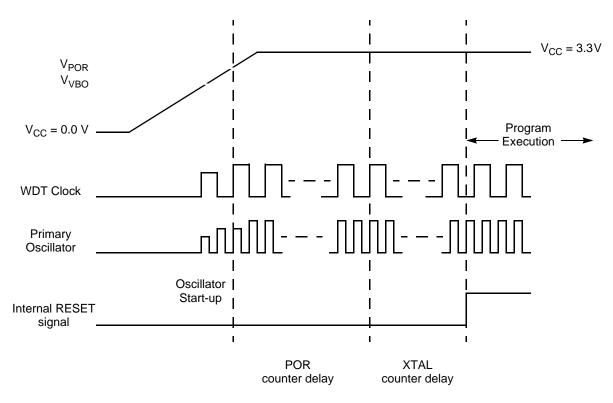

#### **Power-On Reset**

Each device in the Z8 Encore! XP F64xx Series contains an internal Power-On Reset circuit. The POR circuit monitors the supply voltage and holds the device in the Reset state until the supply voltage reaches a safe operating level. After the supply voltage exceeds the POR voltage threshold ( $V_{POR}$ ), the POR Counter is enabled and counts 66 cycles of the Watchdog Timer oscillator. After the POR counter times out, the XTAL Counter is enabled to count a total of 16 system clock pulses. The devices are held in the Reset state until both the POR Counter and XTAL counter have timed out. After the Z8 Encore! XP F64xx Series devices exit the POR reset state, the eZ8 CPU fetches the Reset vector. Following Power-On Reset, the POR status bit in the Watchdog Timer Control (WDTCTL) Register is set to 1.

Figure 8 displays Power-On Reset operation. For the POR threshold voltage ( $V_{POR}$ ), see the <u>Electrical Characteristics</u> chapter on page 200.

Figure 8. Power-On Reset Operation

## Port A–H Input Data Registers

Reading from the Port A–H Input Data registers, shown in Table 21, returns the sampled values from the corresponding port pins. The Port A–H Input Data registers are read-only.

| Bit     | 7    | 6                                              | 5    | 4    | 3    | 2    | 1    | 0    |

|---------|------|------------------------------------------------|------|------|------|------|------|------|

| Field   | PIN7 | PIN6                                           | PIN5 | PIN4 | PIN3 | PIN2 | PIN1 | PIN0 |

| RESET   |      | X                                              |      |      |      |      |      |      |

| R/W     |      | R                                              |      |      |      |      |      |      |

| Address |      | FD2H, FD6H, FDAH, FDEH, FE2H, FE6H, FEAH, FEEH |      |      |      |      |      |      |

| Bit   | Description                                         |

|-------|-----------------------------------------------------|

| [7:0] | Port Input Data                                     |

| PxIN  | Sampled data from the corresponding port pin input. |

|       | 0 = Input data is logical 0 (Low).                  |

|       | 1 = Input data is logical 1 (High).                 |

| Note: | x indicates register bits in the range [7:0].       |

## Port A-H Output Data Register

The Port A–H Output Data Register, shown in Table 22, writes output data to the pins.

Table 22. Port A–H Output Data Register (PxOUT)

| Bit     | 7     | 6     | 5           | 4         | 3         | 2          | 1     | 0     |

|---------|-------|-------|-------------|-----------|-----------|------------|-------|-------|

| Field   | POUT7 | POUT6 | POUT5       | POUT4     | POUT3     | POUT2      | POUT1 | POUT0 |

| RESET   |       | 0     |             |           |           |            |       |       |

| R/W     |       | R/W   |             |           |           |            |       |       |

| Address |       | FD3   | H, FD7H, FI | DBH, FDFH | FE3H, FE7 | H, FEBH, F | EFH   |       |

| Bit            | Description                                                                                                                                                                                                                                                                                         |

|----------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| [7:0]<br>PxOUT | <ul> <li>Port Output Data</li> <li>These bits contain the data to be driven out from the port pins. The values are only driven if the corresponding pin is configured as an output and the pin is not configured for alternate function operation.</li> <li>0 = Drive a logical 0 (Low).</li> </ul> |

| Note: x ii     | <ul> <li>1 = Drive a logical 1 (High). High value is not driven if the drain has been disabled by setting the corresponding Port Output Control Register bit to 1.</li> </ul>                                                                                                                       |

| Bit         | Description (Continued)                                                                                                                                                                                                                                                                                                                                                                                |

|-------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| [2]<br>TDRE | <ul> <li>Transmitter Data Register Empty</li> <li>This bit indicates that the UART Transmit Data Register is empty and ready for additional data.</li> <li>Writing to the UART Transmit Data Register resets this bit.</li> <li>0 = Do not write to the UART Transmit Data Register.</li> <li>1 = The UART Transmit Data Register is ready to receive an additional byte to be transmitted.</li> </ul> |

| [1]<br>TXE  | <ul> <li>Transmitter Empty</li> <li>This bit indicates that the Transmit Shift Register is empty and character transmission is finished.</li> <li>0 = Data is currently transmitting.</li> <li>1 = Transmission is complete.</li> </ul>                                                                                                                                                                |

| [0]<br>CTS  | CTS Signal<br>When this bit is read, it returns the level of the CTS signal.                                                                                                                                                                                                                                                                                                                           |

### **UART Status 1 Register**

The UART Status 1 Register, shown in Table 56, contains multiprocessor control and UART status bits.

#### Table 56. UART Status 1 Register (UxSTAT1)

| Bit     | 7         6         5         4         3         2         1         0 |  |  |         |         |  |      | 0 |

|---------|-------------------------------------------------------------------------|--|--|---------|---------|--|------|---|

| Field   | Reserved NEWFRM MPRX                                                    |  |  |         |         |  | MPRX |   |

| RESET   | 0                                                                       |  |  |         |         |  |      |   |

| R/W     | R R/W R                                                                 |  |  |         |         |  | 2    |   |

| Address |                                                                         |  |  | F44H ar | nd F4CH |  |      |   |

| Bit           | Description                                                                                                                                                                                                                                                                                     |

|---------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| [7:2]         | Reserved<br>These bits are reserved and must be programmed to 000000.                                                                                                                                                                                                                           |

| [1]<br>NEWFRM | <ul> <li>New Frame</li> <li>Status bit denoting the start of a new frame. Reading the UART Receive Data Register resets this bit to 0.</li> <li>0 = The current byte is not the first data byte of a new frame.</li> <li>1 = The current byte is the first data byte of a new frame.</li> </ul> |

| [0]<br>MPRX   | Multiprocessor Receive<br>Returns the value of the last multiprocessor bit received. Reading from the UART Receive<br>Data Register resets this bit to 0.                                                                                                                                       |

101

|                                                                                                               | 20.0 MHz Sys                                                                                                                     | stem Clock                                                                                                  |                                                                                         | 1                                                                                                             | 8.432MHz S                                                                                                                                      | ystem Clock                                                                                            |                                                                                      |  |

|---------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------|--|

| Desired<br>Rate<br>(kHz)                                                                                      | BRG<br>Divisor<br>(Decimal)                                                                                                      | Actual Rate<br>(kHz)                                                                                        | Error<br>(%)                                                                            | Desired<br>Rate<br>(kHz)                                                                                      | BRG<br>Divisor<br>(Decimal)                                                                                                                     | Actual Rate<br>(kHz)                                                                                   | Error<br>(%)                                                                         |  |

| 1250.0                                                                                                        | 1                                                                                                                                | 1250.0                                                                                                      | 0.00                                                                                    | 1250.0                                                                                                        | 1                                                                                                                                               | 1152.0                                                                                                 | -7.84%                                                                               |  |

| 625.0                                                                                                         | 2                                                                                                                                | 625.0                                                                                                       | 0.00                                                                                    | 625.0                                                                                                         | 2                                                                                                                                               | 576.0                                                                                                  | -7.84%                                                                               |  |

| 250.0                                                                                                         | 5                                                                                                                                | 250.0                                                                                                       | 0.00                                                                                    | 250.0                                                                                                         | 5                                                                                                                                               | 230.4                                                                                                  | -7.84%                                                                               |  |

| 115.2                                                                                                         | 11                                                                                                                               | 113.6                                                                                                       | -1.36                                                                                   | 115.2                                                                                                         | 10                                                                                                                                              | 115.2                                                                                                  | 0.00                                                                                 |  |

| 57.6                                                                                                          | 22                                                                                                                               | 56.8                                                                                                        | -1.36                                                                                   | 57.6                                                                                                          | 20                                                                                                                                              | 57.6                                                                                                   | 0.00                                                                                 |  |

| 38.4                                                                                                          | 33                                                                                                                               | 37.9                                                                                                        | -1.36                                                                                   | 38.4                                                                                                          | 30                                                                                                                                              | 38.4                                                                                                   | 0.00                                                                                 |  |

| 19.2                                                                                                          | 65                                                                                                                               | 19.2                                                                                                        | 0.16                                                                                    | 19.2                                                                                                          | 60                                                                                                                                              | 19.2                                                                                                   | 0.00                                                                                 |  |

| 9.60                                                                                                          | 130                                                                                                                              | 9.62                                                                                                        | 0.16                                                                                    | 9.60                                                                                                          | 120                                                                                                                                             | 9.60                                                                                                   | 0.00                                                                                 |  |

| 4.80                                                                                                          | 260                                                                                                                              | 4.81                                                                                                        | 0.16                                                                                    | 4.80                                                                                                          | 240                                                                                                                                             | 4.80                                                                                                   | 0.00                                                                                 |  |

| 2.40                                                                                                          | 521                                                                                                                              | 2.40                                                                                                        | -0.03                                                                                   | 2.40                                                                                                          | 480                                                                                                                                             | 2.40                                                                                                   | 0.00                                                                                 |  |

| 1.20                                                                                                          | 1042                                                                                                                             | 1.20                                                                                                        | -0.03                                                                                   | 1.20                                                                                                          | 960                                                                                                                                             | 1.20                                                                                                   | 0.00                                                                                 |  |

| 0.60                                                                                                          | 2083                                                                                                                             | 0.60                                                                                                        | 0.02                                                                                    | 0.60                                                                                                          | 1920                                                                                                                                            | 0.60                                                                                                   | 0.00                                                                                 |  |

| 0.30                                                                                                          | 4167                                                                                                                             | 0.30                                                                                                        | -0.01                                                                                   | 0.30                                                                                                          | 3840                                                                                                                                            | 0.30                                                                                                   | 0.00                                                                                 |  |

| 1                                                                                                             |                                                                                                                                  | votom Clock                                                                                                 |                                                                                         | 11.0592MHz System Clock                                                                                       |                                                                                                                                                 |                                                                                                        |                                                                                      |  |

|                                                                                                               | 6.667 MHz S                                                                                                                      | ystem Clock                                                                                                 |                                                                                         | I                                                                                                             |                                                                                                                                                 | System Clock                                                                                           |                                                                                      |  |

| Desired<br>Rate<br>(kHz)                                                                                      | BRG<br>Divisor<br>(Decimal)                                                                                                      | Actual Rate<br>(kHz)                                                                                        | Error<br>(%)                                                                            | Desired<br>Rate<br>(kHz)                                                                                      | BRG<br>Divisor<br>(Decimal)                                                                                                                     | Actual Rate<br>(kHz)                                                                                   | Error<br>(%)                                                                         |  |

| Desired<br>Rate                                                                                               | BRG<br>Divisor                                                                                                                   | Actual Rate                                                                                                 |                                                                                         | Desired<br>Rate                                                                                               | BRG<br>Divisor                                                                                                                                  | Actual Rate                                                                                            |                                                                                      |  |

| Desired<br>Rate<br>(kHz)                                                                                      | BRG<br>Divisor<br>(Decimal)                                                                                                      | Actual Rate<br>(kHz)                                                                                        | (%)                                                                                     | Desired<br>Rate<br>(kHz)                                                                                      | BRG<br>Divisor<br>(Decimal)                                                                                                                     | Actual Rate<br>(kHz)                                                                                   | (%)                                                                                  |  |

| Desired<br>Rate<br>(kHz)<br>1250.0                                                                            | BRG<br>Divisor<br>(Decimal)<br>1                                                                                                 | Actual Rate<br>(kHz)<br>1041.69                                                                             | <b>(%)</b><br>-16.67                                                                    | Desired<br>Rate<br>(kHz)<br>1250.0                                                                            | BRG<br>Divisor<br>(Decimal)                                                                                                                     | Actual Rate<br>(kHz)<br>N/A                                                                            | <b>(%)</b><br>N/A                                                                    |  |

| Desired<br>Rate<br>(kHz)<br>1250.0<br>625.0                                                                   | BRG<br>Divisor<br>(Decimal)<br>1<br>2                                                                                            | Actual Rate<br>(kHz)<br>1041.69<br>520.8                                                                    | <b>(%)</b><br>-16.67<br>-16.67                                                          | Desired<br>Rate<br>(kHz)<br>1250.0<br>625.0                                                                   | BRG<br>Divisor<br>(Decimal)<br>N/A<br>1                                                                                                         | Actual Rate<br>(kHz)<br>N/A<br>691.2                                                                   | (%)<br>N/A<br>10.59                                                                  |  |

| Desired<br>Rate<br>(kHz)<br>1250.0<br>625.0<br>250.0                                                          | BRG<br>Divisor<br>(Decimal)<br>1<br>2<br>4                                                                                       | Actual Rate<br>(kHz)<br>1041.69<br>520.8<br>260.4                                                           | (%)<br>-16.67<br>-16.67<br>4.17                                                         | Desired<br>Rate<br>(kHz)<br>1250.0<br>625.0<br>250.0                                                          | BRG<br>Divisor<br>(Decimal)<br>N/A<br>1<br>3                                                                                                    | Actual Rate<br>(kHz)<br>N/A<br>691.2<br>230.4                                                          | (%)<br>N/A<br>10.59<br>-7.84                                                         |  |

| Desired<br>Rate<br>(kHz)<br>1250.0<br>625.0<br>250.0<br>115.2                                                 | BRG<br>Divisor<br>(Decimal)<br>1<br>2<br>4<br>9                                                                                  | Actual Rate<br>(kHz)<br>1041.69<br>520.8<br>260.4<br>115.7                                                  | (%)<br>-16.67<br>-16.67<br>4.17<br>0.47                                                 | Desired<br>Rate<br>(kHz)<br>1250.0<br>625.0<br>250.0<br>115.2                                                 | BRG<br>Divisor<br>(Decimal)<br>N/A<br>1<br>3<br>6                                                                                               | Actual Rate<br>(kHz)<br>N/A<br>691.2<br>230.4<br>115.2                                                 | (%)<br>N/A<br>10.59<br>-7.84<br>0.00                                                 |  |

| Desired<br>Rate<br>(kHz)<br>1250.0<br>625.0<br>250.0<br>115.2<br>57.6                                         | BRG<br>Divisor<br>(Decimal)<br>1<br>2<br>4<br>9<br>18                                                                            | Actual Rate<br>(kHz)<br>1041.69<br>520.8<br>260.4<br>115.7<br>57.87                                         | (%)<br>-16.67<br>-16.67<br>4.17<br>0.47<br>0.47                                         | Desired<br>Rate<br>(kHz)<br>1250.0<br>625.0<br>250.0<br>115.2<br>57.6                                         | BRG<br>Divisor<br>(Decimal)<br>N/A<br>1<br>3<br>6<br>12                                                                                         | Actual Rate<br>(kHz)<br>N/A<br>691.2<br>230.4<br>115.2<br>57.6                                         | (%)<br>N/A<br>10.59<br>-7.84<br>0.00<br>0.00                                         |  |

| Desired<br>Rate<br>(kHz)<br>1250.0<br>625.0<br>250.0<br>115.2<br>57.6<br>38.4                                 | BRG<br>Divisor<br>(Decimal)<br>1<br>2<br>4<br>9<br>18<br>27                                                                      | Actual Rate<br>(kHz)<br>1041.69<br>520.8<br>260.4<br>115.7<br>57.87<br>38.6                                 | (%)<br>-16.67<br>-16.67<br>4.17<br>0.47<br>0.47<br>0.47                                 | Desired<br>Rate<br>(kHz)<br>1250.0<br>625.0<br>250.0<br>115.2<br>57.6<br>38.4                                 | BRG<br>Divisor<br>(Decimal)<br>N/A<br>1<br>3<br>6<br>12<br>18                                                                                   | Actual Rate<br>(kHz)<br>N/A<br>691.2<br>230.4<br>115.2<br>57.6<br>38.4                                 | (%)<br>N/A<br>10.59<br>-7.84<br>0.00<br>0.00<br>0.00                                 |  |

| Desired<br>Rate<br>(kHz)<br>1250.0<br>625.0<br>250.0<br>115.2<br>57.6<br>38.4<br>19.2                         | BRG           Divisor           (Decimal)           1           2           4           9           18           27           54 | Actual Rate<br>(kHz)<br>1041.69<br>520.8<br>260.4<br>115.7<br>57.87<br>38.6<br>19.3                         | (%)<br>-16.67<br>4.17<br>0.47<br>0.47<br>0.47<br>0.47<br>0.47                           | Desired<br>Rate<br>(kHz)<br>1250.0<br>625.0<br>250.0<br>115.2<br>57.6<br>38.4<br>19.2                         | <b>BRG</b><br><b>Divisor</b><br>(Decimal)<br>N/A<br>1<br>3<br>6<br>12<br>18<br>36                                                               | Actual Rate<br>(kHz)<br>N/A<br>691.2<br>230.4<br>115.2<br>57.6<br>38.4<br>19.2                         | (%)<br>N/A<br>10.59<br>-7.84<br>0.00<br>0.00<br>0.00<br>0.00                         |  |

| Desired<br>Rate<br>(kHz)<br>1250.0<br>625.0<br>250.0<br>115.2<br>57.6<br>38.4<br>19.2<br>9.60                 | BRG<br>Divisor<br>(Decimal)<br>1<br>2<br>4<br>9<br>18<br>27<br>54<br>54<br>109                                                   | Actual Rate<br>(kHz)<br>1041.69<br>520.8<br>260.4<br>115.7<br>57.87<br>38.6<br>19.3<br>9.56                 | (%)<br>-16.67<br>4.17<br>0.47<br>0.47<br>0.47<br>0.47<br>0.47<br>-0.45                  | Desired<br>Rate<br>(kHz)<br>1250.0<br>625.0<br>250.0<br>115.2<br>57.6<br>38.4<br>19.2<br>9.60                 | BRG           Divisor           (Decimal)           N/A           1           3           6           12           18           36           72 | Actual Rate<br>(kHz)<br>N/A<br>691.2<br>230.4<br>115.2<br>57.6<br>38.4<br>19.2<br>9.60                 | (%)<br>N/A<br>10.59<br>-7.84<br>0.00<br>0.00<br>0.00<br>0.00<br>0.00                 |  |

| Desired<br>Rate<br>(kHz)<br>1250.0<br>625.0<br>250.0<br>115.2<br>57.6<br>38.4<br>19.2<br>9.60<br>4.80         | BRG<br>Divisor<br>(Decimal)<br>1<br>2<br>4<br>9<br>18<br>27<br>54<br>27<br>54<br>109<br>217                                      | Actual Rate<br>(kHz)<br>1041.69<br>520.8<br>260.4<br>115.7<br>57.87<br>38.6<br>19.3<br>9.56<br>4.80         | (%)<br>-16.67<br>4.17<br>0.47<br>0.47<br>0.47<br>0.47<br>0.47<br>-0.45<br>-0.83         | Desired<br>Rate<br>(kHz)<br>1250.0<br>625.0<br>250.0<br>115.2<br>57.6<br>38.4<br>19.2<br>9.60<br>4.80         | BRG<br>Divisor<br>(Decimal)<br>N/A<br>1<br>3<br>6<br>12<br>18<br>36<br>72<br>144                                                                | Actual Rate<br>(kHz)<br>N/A<br>691.2<br>230.4<br>115.2<br>57.6<br>38.4<br>19.2<br>9.60<br>4.80         | (%)<br>N/A<br>10.59<br>-7.84<br>0.00<br>0.00<br>0.00<br>0.00<br>0.00<br>0.00         |  |

| Desired<br>Rate<br>(kHz)<br>1250.0<br>625.0<br>250.0<br>115.2<br>57.6<br>38.4<br>19.2<br>9.60<br>4.80<br>2.40 | BRG<br>Divisor<br>(Decimal)<br>1<br>2<br>4<br>9<br>18<br>27<br>54<br>109<br>217<br>434                                           | Actual Rate<br>(kHz)<br>1041.69<br>520.8<br>260.4<br>115.7<br>57.87<br>38.6<br>19.3<br>9.56<br>4.80<br>2.40 | (%)<br>-16.67<br>4.17<br>0.47<br>0.47<br>0.47<br>0.47<br>0.47<br>-0.45<br>-0.83<br>0.01 | Desired<br>Rate<br>(kHz)<br>1250.0<br>625.0<br>250.0<br>115.2<br>57.6<br>38.4<br>19.2<br>9.60<br>4.80<br>2.40 | BRG<br>Divisor<br>(Decimal)<br>N/A<br>1<br>3<br>6<br>12<br>18<br>36<br>72<br>144<br>288                                                         | Actual Rate<br>(kHz)<br>N/A<br>691.2<br>230.4<br>115.2<br>57.6<br>38.4<br>19.2<br>9.60<br>4.80<br>2.40 | (%)<br>N/A<br>10.59<br>-7.84<br>0.00<br>0.00<br>0.00<br>0.00<br>0.00<br>0.00<br>0.00 |  |

#### Table 62. UART Baud Rates

112

since the previous pulse was detected). This gives the endec a sampling window of minus four baud rate clocks to plus eight baud rate clocks around the expected time of an incoming pulse. If an incoming pulse is detected inside this window this process is repeated. If the incoming data is a logical 1 (no pulse), the endec returns to the initial state and waits for the next falling edge. As each falling edge is detected, the endec clock counter is reset, resynchronizing the endec to the incoming signal. This action allows the endec to tolerate jitter and baud rate errors in the incoming data stream. Resynchronizing the endec does not alter the operation of the UART, which ultimately receives the data. The UART is only synchronized to the incoming data stream when a start bit is received.

## Infrared Encoder/Decoder Control Register Definitions

All infrared endec configuration and status information is set by the UART control registers as defined in the <u>UART Control Register Definitions</u> section on page 98.

**Caution:** To prevent spurious signals during IrDA data transmission, set the IREN bit in the UARTx Control 1 Register to 1 to enable the Infrared Encoder/Decoder before enabling the GPIO Port alternate function for the corresponding pin.

| Bit         | Description (Continued)                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|-------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| [5]<br>COL  | <ul> <li>Collision</li> <li>0 = A multimaster collision (mode fault) has not occurred.</li> <li>1 = A multimaster collision (mode fault) has been detected.</li> </ul>                                                                                                                                                                                                                                                                                                    |

| [4]<br>ABT  | <ul> <li>Slave Mode Transaction Abort</li> <li>This bit is set if the SPI is configured in slave mode, a transaction is occurring and SS deasserts before all bits of a character have been transferred as defined by the NUMBITS field of the SPIMODE Register. The IRQ bit also sets, indicating the transaction has completed.</li> <li>0 = A slave mode transaction abort has not occurred.</li> <li>1 = A slave mode transaction abort has been detected.</li> </ul> |

| [3:2]       | <b>Reserved</b><br>These bits are reserved and must be programmed to 00.                                                                                                                                                                                                                                                                                                                                                                                                  |

| [1]<br>TXST | Transmit Status<br>0 = No data transmission currently in progress.<br>1 = Data transmission currently in progress.                                                                                                                                                                                                                                                                                                                                                        |

| [0]<br>SLAS | Slave Select<br>If SPI enabled as a Slave, then the following conditions are true:<br>$0 = \frac{SS}{SS}$ input pin is asserted (Low).<br>$1 = \frac{SS}{SS}$ input is not asserted (High).<br>If SPI enabled as a Master, this bit is not applicable.                                                                                                                                                                                                                    |

| Bit         | Description (Continued)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|-------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| [5]<br>ACK  | <ul> <li>Acknowledge This bit indicates the status of the Acknowledge for the last byte transmitted or received. When set, this bit indicates that an Acknowledge occurred for the last byte transmitted or received. This bit is cleared when IEN = 0 or when a Not Acknowledge occurred for the last byte transmitted or received. It is not reset at the beginning of each transaction and is not reset when this register is read. </li> <li>Caution: When making decisions based on this bit within a transaction, software cannot determine when the bit is updated by hardware. In the case of write transactions, the I<sup>2</sup>C pauses at the beginning of the Acknowledge cycle if the next transmit data or address byte has not been written (TDRE = 1) and stop and start = 0. In this case the ACK bit is not updated until the transmit interrupt is serviced and the Acknowledge cycle for the previous byte completes. For examples of how the ACK bit can be used, see the Address Only Transaction with a 7-bit Address section on page 133 and the Address Only Transaction with a 10-bit Address section on page 135.</li></ul> |

| [4]         | <b>10-Bit Address</b>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 10B         | This bit indicates whether a 10- or 7-bit address is being transmitted. After the start bit is set, if the five most significant bits of the address are 11110B, this bit is set. When set, it is reset once the first byte of the address has been sent.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| [3]         | <b>Read</b>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| RD          | This bit indicates the direction of transfer of the data. It is active High during a read. The status of this bit is determined by the least significant bit of the I <sup>2</sup> C Shift Register after the start bit is set.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| [2]         | <b>Transmit Address State</b>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| TAS         | This bit is active High while the address is being shifted out of the I <sup>2</sup> C Shift Register.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| [1]         | Data Shift State                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| DSS         | This bit is active High while data is being shifted to or from the I <sup>2</sup> C Shift Register.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| [0]<br>NCKI | <b>NACK Interrupt</b><br>This bit is set High when a Not Acknowledge condition is received or sent and neither the start<br>nor the stop bit is active. When set, this bit generates an interrupt that can only be cleared by<br>setting the start or stop bit, allowing you to specify whether to perform a stop or a repeated<br>start.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

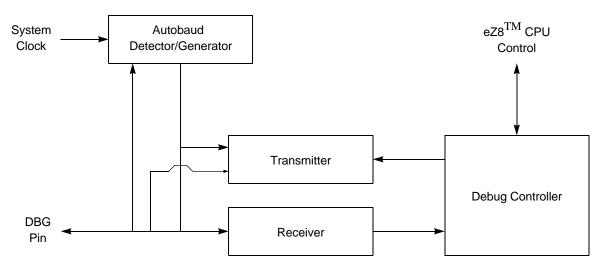

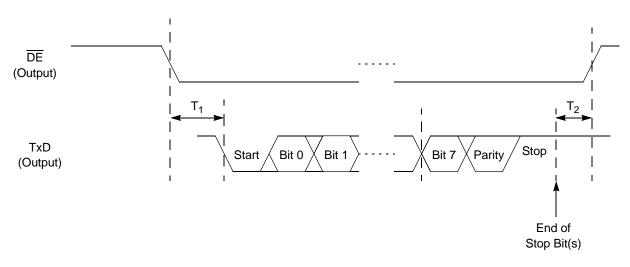

# **On-Chip Debugger**

The Z8 Encore! XP F64xx Series products contain an integrated On-Chip Debugger (OCD) that provides advanced debugging features including:

- Reading and writing of the Register File

- Reading and writing of Program and Data memory

- Setting of breakpoints

- Execution of eZ8 CPU instructions

## Architecture

The On-Chip Debugger consists of four primary functional blocks: transmitter, receiver, autobaud generator, and debug controller. Figure 36 displays the architecture of the On-Chip Debugger.

| Debug Command                 | Command<br>Byte | Enabled when<br>NOT in DEBUG<br>Mode? | Disabled by Read Protect Option Bit                                                                                                                                       |

|-------------------------------|-----------------|---------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Read OCD Revision             | 00H             | Yes                                   | -                                                                                                                                                                         |

| Read OCD Status<br>Register   | 02H             | Yes                                   | _                                                                                                                                                                         |

| Read Runtime Counter          | 03H             | —                                     |                                                                                                                                                                           |

| Write OCD Control<br>Register | 04H             | Yes                                   | Cannot clear DBGMODE bit                                                                                                                                                  |

| Read OCD Control<br>Register  | 05H             | Yes                                   | _                                                                                                                                                                         |

| Write Program Counter         | 06H             | _                                     | Disabled                                                                                                                                                                  |

| Read Program Counter          | 07H             | _                                     | Disabled                                                                                                                                                                  |

| Write Register                | 08H             | _                                     | Only writes of the Flash memory control<br>registers are allowed. Additionally, only the<br>Mass Erase command is allowed to be<br>written to the Flash Control Register. |

| Read Register                 | 09H             | _                                     | Disabled                                                                                                                                                                  |

| Write Program Memory          | 0AH             | _                                     | Disabled                                                                                                                                                                  |

| Read Program Memory           | 0BH             | —                                     | Disabled                                                                                                                                                                  |

| Write Data Memory             | 0CH             | _                                     | Disabled                                                                                                                                                                  |

| Read Data Memory              | 0DH             | _                                     | Disabled                                                                                                                                                                  |

| Read Program Memory<br>CRC    | 0EH             |                                       | _                                                                                                                                                                         |

| Reserved                      | 0FH             | _                                     | _                                                                                                                                                                         |

| Step Instruction              | 10H             |                                       | Disabled                                                                                                                                                                  |

| Stuff Instruction             | 11H             |                                       | Disabled                                                                                                                                                                  |

| Execute Instruction           | 12H             | —                                     | Disabled                                                                                                                                                                  |

| Reserved                      | 13H–FFH         | —                                     | -                                                                                                                                                                         |

#### Table 102. On-Chip Debugger Commands

In the following list of OCD commands, data and commands sent from the host to the On-Chip Debugger are identified by DBG  $\leftarrow$  Command/Data. Data sent from the On-Chip Debugger back to the host is identified by DBG  $\rightarrow$  Data.

**Read OCD Revision (00H).** The Read OCD Revision command determines the version of the On-Chip Debugger. If OCD commands are added, removed, or changed, this revision number changes.

## **On-Chip Debugger Control Register Definitions**

This section describes the features of the On-Chip Debugger Control and Status registers.

## **OCD Control Register**

The OCD Control Register, shown in Table 103, controls the state of the On-Chip Debugger. This register enters or exits DEBUG Mode and enables the BRK instruction.

A *reset and stop* function can be achieved by writing 81H to this register. A *reset and go* function can be achieved by writing 41H to this register. If the device is operating in DEBUG Mode, a *run* function can be implemented by writing 40H to this register.

| Bit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 7                                                                                                                                                                                                                                                                                                            | 6     | 5      | 4       | 3 | 2        | 1 | 0   |  |  |  |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|--------|---------|---|----------|---|-----|--|--|--|

| Field                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | DBGMODE                                                                                                                                                                                                                                                                                                      | BRKEN | DBGACK | BRKLOOP |   | Reserved |   | RST |  |  |  |

| RESET                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                                                                                                                                                                                                                              |       |        | 0       |   |          |   |     |  |  |  |