# E·XFL

Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                    |

|----------------------------|-----------------------------------------------------------|

| Core Processor             | eZ8                                                       |

| Core Size                  | 8-Bit                                                     |

| Speed                      | 20MHz                                                     |

| Connectivity               | I <sup>2</sup> C, IrDA, SPI, UART/USART                   |

| Peripherals                | Brown-out Detect/Reset, DMA, POR, PWM, WDT                |

| Number of I/O              | 31                                                        |

| Program Memory Size        | 64KB (64K x 8)                                            |

| Program Memory Type        | FLASH                                                     |

| EEPROM Size                |                                                           |

| RAM Size                   | 4K x 8                                                    |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                 |

| Data Converters            | A/D 8x10b                                                 |

| Oscillator Type            | Internal                                                  |

| Operating Temperature      | 0°C ~ 70°C (TA)                                           |

| Mounting Type              | Surface Mount                                             |

| Package / Case             | 44-LQFP                                                   |

| Supplier Device Package    | 44-LQFP (10x10)                                           |

| Purchase URL               | https://www.e-xfl.com/product-detail/zilog/z8f6421an020sg |

|                            |                                                           |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| Program Memory Address (Hex)              | Function                     |  |

|-------------------------------------------|------------------------------|--|

| 0006-0007                                 | Illegal Instruction Trap     |  |

| 0008-0037                                 | Interrupt Vectors*           |  |

| 0038-BFFF                                 | Program Memory               |  |

| Z8F642x Products                          |                              |  |

| 0000-0001                                 | Option Bits                  |  |

| 0002-0003                                 | Reset Vector                 |  |

| 0004-0005                                 | WDT Interrupt Vector         |  |

| 0006-0007                                 | Illegal Instruction Trap     |  |

| 0008-0037                                 | Interrupt Vectors*           |  |

| 0038-FFFF                                 | Program Memory               |  |

| Note: *See Table 23 on page 48 for a list | st of the interrupt vectors. |  |

Table 5. Z8 Encore! XP F64xx Series Program Memory Maps (Continued)

## **Data Memory**

The Z8 Encore! XP F64xx Series does not use the eZ8 CPU's 64KB data memory address space.

# **Information Area**

Table 6 describes the Z8 Encore! XP F64xx Series' Information Area. This 512-byte Information Area is accessed by setting bit 7 of the Page Select Register to 1. When access is enabled, the Information Area is mapped into program memory and overlays the 512 bytes at addresses FE00H to FFFFH. When the Information Area access is enabled, execution of the LDC and LDCI instructions from these program memory addresses return the Information Area data rather than the program memory data. Reads of these addresses through the On-Chip Debugger also returns the Information Area data. Execution of code from these addresses continues to correctly use program memory. Access to the Information Area is read-only.

| Address (H  | lex) Register Description         | Mnemonic     | Reset (Hex) | Page       |  |

|-------------|-----------------------------------|--------------|-------------|------------|--|

| Timer 2 (co | ontinued)                         |              |             |            |  |

| F14         | Timer 2 PWM High Byte             | T2PWMH       | 00          | <u>75</u>  |  |

| F15         | Timer 2 PWM Low Byte              | T2PWML       | 00          | <u>75</u>  |  |

| F16         | Timer 2 Control 0                 | T2CTL0       | 00          | <u>76</u>  |  |

| F17         | Timer 2 Control 1                 | T2CTL1       | 00          | <u>77</u>  |  |

| Timer 3 (U  | navailable in the 44-Pin Package) |              |             |            |  |

| F18         | Timer 3 High Byte                 | T3H          | 00          | <u>72</u>  |  |

| F19         | Timer 3 Low Byte                  | T3L          | 01          | <u>72</u>  |  |

| F1A         | Timer 3 Reload High Byte          | T3RH         | FF          | <u>74</u>  |  |

| F1B         | Timer 3 Reload Low Byte           | T3RL         | FF          | <u>74</u>  |  |

| F1C         | Timer 3 PWM High Byte             | T3PWMH       | 00          | <u>75</u>  |  |

| F1D         | Timer 3 PWM Low Byte              | T3PWML       | 00          | <u>75</u>  |  |

| F1E         | Timer 3 Control 0                 | T3CTL0       | 00          | <u>76</u>  |  |

| F1F         | Timer 3 Control 1                 | T3CTL1       | 00          | 77         |  |

| 20–3F       | Reserved                          | _            | XX          |            |  |

| UART 0      |                                   |              |             |            |  |

| F40         | UART0 Transmit Data               | U0TXD        | XX          | <u>98</u>  |  |

|             | UART0 Receive Data                | U0RXD        | XX          | <u>99</u>  |  |

| F41         | UART0 Status 0                    | U0STAT0      | 0000011Xb   | 100        |  |

| F42         | UART0 Control 0                   | U0CTL0       | 00          | <u>102</u> |  |

| F43         | UART0 Control 1                   | U0CTL1       | 00          | <u>102</u> |  |

| F44         | UART0 Status 1                    | U0STAT1      | 00          | <u>100</u> |  |

| F45         | UART0 Address Compare Register    | U0ADDR       | 00          | <u>105</u> |  |

| F46         | UART0 Baud Rate High Byte         | <b>U0BRH</b> | FF          | <u>105</u> |  |

| F47         | UART0 Baud Rate Low Byte          | U0BRL        | FF          | <u>105</u> |  |

| UART 1      |                                   |              |             |            |  |

| F48         | UART1 Transmit Data               | U1TXD        | XX          | <u>98</u>  |  |

|             | UART1 Receive Data                | U1RXD        | XX          | <u>99</u>  |  |

| F49         | UART1 Status 0                    | U1STAT0      | 0000011Xb   | <u>100</u> |  |

| F4A         | UART1 Control 0                   | U1CTL0       | 00          | <u>102</u> |  |

| F4B         | UART1 Control 1                   | U1CTL1       | 00          | <u>102</u> |  |

| F4C         | UART1 Status 1                    | U1STAT1      | 00          | <u>100</u> |  |

## Table 7. Z8 Encore! XP F64xx Series Register File Address Map (Continued)

Note: XX = Undefined.

enabled, the timer output pin changes state (from Low to High or from High to Low) at timer reload.

Observe the following procedure for configuring a timer for COUNTER Mode and initiating the count:

- 1. Write to the Timer Control 1 Register to:

- Disable the timer.

- Configure the timer for COUNTER Mode.

- Select either the rising edge or falling edge of the timer input signal for the count. This also sets the initial logic level (High or Low) for the timer output alternate function. However, the timer output function does not have to be enabled.

- Write to the Timer High and Low Byte registers to set the starting count value. This

only affects the first pass in COUNTER Mode. After the first timer reload in COUNTER Mode, counting always begins at the reset value of 0001H. Generally, in COUNTER Mode the Timer High and Low Byte registers must be written with the value

0001H.

- 3. Write to the Timer Reload High and Low Byte registers to set the reload value.

- 4. If appropriate, enable the timer interrupt and set the timer interrupt priority by writing to the relevant interrupt registers.

- 5. Configure the associated GPIO port pin for the timer input alternate function.

- 6. If using the timer output function, configure the associated GPIO port pin for the timer output alternate function.

- 7. Write to the Timer Control 1 Register to enable the timer.

In COUNTER Mode, the number of timer input transitions since the timer start is calculated using the following equation:

COUNTER Mode Timer Input Transitions = Current Count Value – Start Value

#### **PWM Mode**

In PWM Mode, the timer outputs a Pulse-Width Modulator (PWM) output signal through a GPIO port pin. The timer input is the system clock. The timer first counts up to the 16bit PWM match value stored in the Timer PWM High and Low Byte registers. When the timer count value matches the PWM value, the timer output toggles. The timer continues counting until it reaches the reload value stored in the Timer Reload High and Low Byte registers. Upon reaching the reload value, the timer generates an interrupt, the count value in the Timer High and Low Byte registers is reset to 0001H and counting resumes.

- Set or clear the CTSE bit to enable or disable control from the remote receiver via the  $\overline{\text{CTS}}$  pin

- 8. Execute an EI instruction to enable interrupts.

The UART is now configured for interrupt-driven data transmission. Because the UART Transmit Data Register is empty, an interrupt is generated immediately. When the UART transmit interrupt is detected, the associated interrupt service routine performs the following functions:

- 1. Write the UART Control 1 Register to select the outgoing address bit:

- Set the MULTIPROCESSOR Bit Transmitter (MPBT) if sending an address byte; clear it if sending a data byte.

- 2. Write the data byte to the UART Transmit Data Register. The transmitter automatically transfers the data to the Transmit Shift Register and transmits the data.

- 3. Clear the UART transmit interrupt bit in the applicable Interrupt Request Register.

- 4. Execute the IRET instruction to return from the interrupt service routine and wait for the Transmit Data Register to again become empty.

## **Receiving Data using the Polled Method**

Observe the following procedure to configure the UART for polled data reception:

- 1. Write to the UART Baud Rate High and Low Byte registers to set the appropriate baud rate.

- 2. Enable the UART pin functions by configuring the associated GPIO port pins for alternate function operation.

- 3. Write to the UART Control 1 Register to enable MULTIPROCESSOR Mode functions, if appropriate.

- 4. Write to the UART Control 0 Register to:

- Set the receive enable bit (REN) to enable the UART for data reception

- Enable parity, if appropriate and if MULTIPROCESSOR Mode is not enabled, and select either even or odd parity

- 5. Check the RDA bit in the UART Status 0 Register to determine if the Receive Data Register contains a valid data byte (indicated by a 1). If RDA is set to 1 to indicate available data, continue to <u>Step 6</u>. If the Receive Data Register is empty (indicated by a 0), continue to monitor the RDA bit awaiting reception of the valid data.

byte indicating an overrun error, the Receive Data Register must be read again to clear the error bits is the UART Status 0 Register. Updates to the Receive Data Register occur only when the next data word is received.

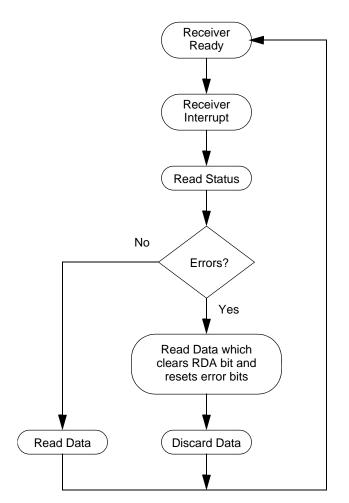

## **UART Data and Error Handling Procedure**

Figure 18 displays the recommended procedure for use in UART receiver interrupt service routines.

Figure 18. UART Receiver Interrupt Service Routine Flow

## **Baud Rate Generator Interrupts**

If the Baud Rate Generator interrupt enable is set, the UART Receiver interrupt asserts when the UART Baud Rate Generator reloads. This action allows the Baud Rate Generator to function as an additional counter if the UART functionality is not employed.

## **Slave Operation**

The SPI block is configured for SLAVE Mode operation by setting the SPIEN bit to 1 and the MMEN bit to 0 in the SPICTL Register and setting the SSIO bit to 0 in the SPIMODE Register. The IRQE, PHASE, CLKPOL, WOR bits in the SPICTL Register and the NUMBITS field in the SPIMODE Register must be set to be consistent with the other SPI devices. The STR bit in the SPICTL Register may be used if appropriate to force a *start-up* interrupt. The BIRQ bit in the SPICTL Register and the SSV bit in the SPIMODE Register are not used in SLAVE Mode. The SPI baud rate generator is not used in SLAVE Mode so the SPIBRH and SPIBRL registers need not be initialized.

If the slave has data to send to the master, the data must be written to the SPIDAT Register before the transaction starts (first edge of SCK when  $\overline{SS}$  is asserted). If the SPIDAT Register is not written prior to the slave transaction, the MISO pin outputs whatever value is currently in the SPIDAT Register.

Due to the delay resulting from synchronization of the SPI input signals to the internal system clock, the maximum SPICLK baud rate that can be supported in SLAVE Mode is the system clock frequency ( $X_{IN}$ ) divided by 8. This rate is controlled by the SPI master.

## **Error Detection**

The SPI contains error detection logic to support SPI communication protocols and recognize when communication errors have occurred. The SPI Status Register indicates when a data transmission error has been detected.

## **Overrun (Write Collision)**

An overrun error (write collision) indicates that a write to the SPI Data Register was attempted while a data transfer was in progress (in either MASTER or SLAVE modes). An overrun sets the OVR bit in the SPI Status Register to 1. Writing a 1 to OVR clears this error flag. The data register is not altered when a write occurs while data transfer is in progress.

## Mode Fault (Multimaster Collision)

A mode fault indicates when more than one Master is trying to communicate at the same time (a multimaster collision). The mode fault is detected when the enabled Master's  $\overline{SS}$  pin is asserted. A mode fault sets the COL bit in the SPI Status Register to 1. Writing a 1 to COL clears this error flag.

## Slave Mode Abort

In the SLAVE Mode of operation, if the  $\overline{SS}$  pin deasserts before all bits in a character have been transferred, the transaction is aborted. When this condition occurs, the ABT bit is set in the SPISTAT Register as well as the IRQ bit (indicating the transaction is complete).

| Bit           | Description (Continued)                                                                                                                                                                                                                                                                            |

|---------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| [4]<br>PHASE  | <b>Phase Select</b><br>Sets the phase relationship of the data to the clock. For more information about operation of the PHASE bit, see the <u>SPI Clock Phase and Polarity Control</u> section on page 116.                                                                                       |

| [3]<br>CLKPOL | Clock Polarity<br>0 = SCK idles Low (0).<br>1 = SCK idle High (1).                                                                                                                                                                                                                                 |

| [2]<br>WOR    | <ul> <li>Wire-OR (OPEN-DRAIN) Mode Enabled</li> <li>0 = SPI signal pins not configured for open-drain.</li> <li>1 = All four SPI signal pins (SCK, SS, MISO, MOSI) configured for open-drain function. This setting is typically used for multimaster and/or multislave configurations.</li> </ul> |

| [1]<br>MMEN   | SPI Master Mode Enable0 = SPI configured in SLAVE Mode.1 = SPI configured in MASTER Mode.                                                                                                                                                                                                          |

| [0]<br>SPIEN  | <b>SPI Enable</b><br>0 = SPI disabled.<br>1 = SPI enabled.                                                                                                                                                                                                                                         |

## **SPI Status Register**

The SPI Status Register, shown in Table 66, indicates the current state of the SPI. All bits revert to their reset state if the SPIEN bit in the SPICTL Register = 0.

#### Table 66. SPI Status Register (SPISTAT)

| Bit       | 7             | 6              | 5              | 4         | 3   | 2      | 1    | 0    |

|-----------|---------------|----------------|----------------|-----------|-----|--------|------|------|

| Field     | IRQ           | OVR            | COL            | ABT       | Res | served | TXST | SLAS |

| RESET     |               |                |                | 0         |     |        |      | 1    |

| R/W       |               | R/             | W*             |           |     |        | R    |      |

| Address   |               |                |                | F6        | 2H  |        |      |      |

| Note: R/W | /* = Read acc | ess. Write a 1 | to clear the l | bit to 0. |     |        |      |      |

| Bit        | Description                                                                                                                                                                                                                                                                                                                                                             |

|------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| [7]<br>IRQ | Interrupt Request<br>If SPIEN = 1, this bit is set if the STR bit in the SPICTL Register is set, or upon completion of<br>an SPI master or slave transaction. This bit does not set if SPIEN = 0 and the SPI Baud Rate<br>Generator is used as a timer to generate the SPI interrupt.<br>0 = No SPI interrupt request pending.<br>1 = SPI interrupt request is pending. |

| [6]<br>OVR | Overrun<br>0 = An overrun error has not occurred.<br>1 = An overrun error has been detected.                                                                                                                                                                                                                                                                            |

# Operation

This section describes the operational aspects of the ADC's power-down and conversion features.

## **Automatic Power-Down**

If the ADC is idle (i.e., no conversions are in progress) for 160 consecutive system clock cycles, portions of the ADC are automatically powered down. From this powered-down state, the ADC requires 40 system clock cycles to power up. The ADC powers up when a conversion is requested using the ADC Control Register.

## **Single-Shot Conversion**

When configured for single-shot conversion, the ADC performs a single analog-to-digital conversion on the selected analog input channel. After completion of the conversion, the ADC shuts down. Observe the following procedure for setting up the ADC and initiating a single-shot conversion:

- 1. Enable the appropriate analog inputs by configuring the general-purpose I/O pins for alternate function. This configuration disables the digital input and output drivers.

- 2. Write to the ADC Control Register to configure the ADC and begin the conversion. The bit fields in the ADC Control Register can be written simultaneously:

- Write to the ANAIN[3:0] field to select one of the 12 analog input sources

- Clear CONT to 0 to select a single-shot conversion

- Write to the  $\overline{\text{VREF}}$  bit to enable or disable the internal voltage reference generator

- Set CEN to 1 to start the conversion

- 3. CEN remains 1 while the conversion is in progress. A single-shot conversion requires 5129 system clock cycles to complete. If a single-shot conversion is requested from an ADC powered-down state, the ADC uses 40 additional clock cycles to power up before beginning the 5129 cycle conversion.

- 4. When the conversion is complete, the ADC control logic performs the following operations:

- 10-bit data result written to {ADCD\_H[7:0], ADCD\_L[7:6]}

- CEN resets to 0 to indicate the conversion is complete

- An interrupt request is sent to the Interrupt Controller

- 5. If the ADC remains idle for 160 consecutive system clock cycles, it is automatically powered down.

- 4. Write the second unlock command 8CH to the Flash Control Register.

- 5. Rewrite the page written in <u>Step 2</u> to the Page Select Register.

- 6. Write Flash memory using LDC or LDCI instructions to program the Flash.

- 7. Repeat <u>Step 6</u> to program additional memory locations on the same page.

- 8. Write 00H to the Flash Control Register to lock the Flash Controller.

## **Page Erase**

Flash memory can be erased one page (512 bytes) at a time. Page-erasing Flash memory sets all bytes in a page to the value FFH. The Page Select Register identifies the page to be erased. While the Flash Controller executes the Page Erase operation, the eZ8 CPU idles; however, the system clock and on-chip peripherals continue to operate. The eZ8 CPU resumes operation after the Page Erase operation completes. Interrupts that occur when the Page Erase operation is in progress are serviced after the Page Erase operation is complete. When the Page Erase operation is complete, the Flash Controller returns to its locked state. Only pages located in unprotected sectors can be erased.

Observe the following procedure to perform a Page Erase operation:

- 1. Write 00H to the Flash Control Register to reset the Flash Controller.

- 2. Write the page to be erased to the Page Select Register.

- 3. Write the first unlock command 73H to the Flash Control Register.

- 4. Write the second unlock command 8CH to the Flash Control Register.

- 5. Rewrite the page written in <u>Step 2</u> to the Page Select Register.

- 6. Write the Page Erase command 95H to the Flash Control Register.

## **Mass Erase**

The Flash memory cannot be mass-erased by user code.

## **Flash Controller Bypass**

The Flash Controller can be bypassed and the control signals for Flash memory can be brought out to the GPIO pins. Bypassing the Flash Controller allows faster programming algorithms by controlling the Flash programming signals directly.

Flash Controller Bypass is recommended for gang programming applications and large volume customers who do not require in-circuit programming of Flash memory.

```

DBG ← 00H

DBG OCDREV[15:8] (Major revision number)

DBG OCDREV[7:0] (Minor revision number)

```

**Read OCD Status Register (02H).** The Read OCD Status Register command reads the OCDSTAT Register.

```

DBG \leftarrow 02H

DBG OCDSTAT[7:0]

```

Write OCD Control Register (04H). The Write OCD Control Register command writes the data that follows to the OCDCTL Register. When the Read Protect option bit is enabled, the DBGMODE bit (OCDCTL[7]) can only be set to 1, it cannot be cleared to 0 and the only method of putting the device back into normal operating mode is to reset the device.

```

DBG \leftarrow 04H

DBG \leftarrow OCDCTL[7:0]

```

**Read OCD Control Register (05H).** The Read OCD Control Register command reads the value of the OCDCTL Register.

```

DBG ← 05H

DBG OCDCTL[7:0]

```

**Write Program Counter (06H).** The Write Program Counter command writes the data that follows to the eZ8 CPU's Program Counter (PC). If the device is not in DEBUG Mode or if the Read Protect option bit is enabled, the Program Counter (PC) values are discarded.

```

DBG \leftarrow 06H

DBG \leftarrow ProgramCounter[15:8]

DBG \leftarrow ProgramCounter[7:0]

```

**Read Program Counter (07H).** The Read Program Counter command reads the value in the eZ8 CPU's Program Counter (PC). If the device is not in DEBUG Mode or if the Read Protect option bit is enabled, this command returns FFFFH.

```

DBG ← 07H

DBG ProgramCounter[15:8]

DBG ProgramCounter[7:0]

```

**Write Register (08H).** The Write Register command writes data to the Register File. Data can be written 1-256 bytes at a time (256 bytes can be written by setting size to zero). If the device is not in DEBUG Mode, the address and data values are discarded. If the Read Protect option bit is enabled, then only writes to the Flash Control Registers are allowed and all other register write data values are discarded.

```

DBG \leftarrow 08H

DBG \leftarrow {4'h0,Register Address[11:8]}

DBG \leftarrow Register Address[7:0]

```

# **On-Chip Oscillator**

The products in the Z8 Encore! XP F64xx Series feature an on-chip oscillator for use with external crystals with frequencies from 32kHz to 20MHz. In addition, the oscillator can support external RC networks with oscillation frequencies up to 4MHz or ceramic resonators with oscillation frequencies up to 20MHz. This oscillator generates the primary system clock for the internal eZ8 CPU and the majority of the on-chip peripherals. Alternatively, the  $X_{IN}$  input pin can also accept a CMOS-level clock input signal (32kHz–20MHz). If an external clock generator is used, the  $X_{OUT}$  pin must be left unconnected.

When configured for use with crystal oscillators or external clock drivers, the frequency of the signal on the  $X_{IN}$  input pin determines the frequency of the system clock (that is, no internal clock divider). In RC operation, the system clock is driven by a clock divider (divide by 2) to ensure 50% duty cycle.

# **Operating Modes**

The Z8 Encore! XP F64xx Series products support four different oscillator modes:

- On-chip oscillator configured for use with external RC networks (<4MHz)

- Minimum power for use with very low frequency crystals (32kHz to 1.0MHz)

- Medium power for use with medium frequency crystals or ceramic resonators (0.5 MHz to 10.0 MHz)

- Maximum power for use with high frequency crystals or ceramic resonators (8.0MHz to 20.0MHz)

The oscillator mode is selected through user-programmable option bits. For more information, see the <u>Option Bits</u> chapter on page 180.

# **Crystal Oscillator Operation**

Figure 40 displays a recommended configuration for connection with an external fundamental-mode, parallel-resonant crystal operating at 20MHz. Recommended 20MHz crystal specifications are provided in Table 105. Resistor R1 is optional and limits total power dissipation by the crystal. The printed circuit board layout must add no more than 4 pF of stray capacitance to either the  $X_{IN}$  or  $X_{OUT}$  pins. If oscillation does not occur, reduce the values of capacitors C1 and C2 to decrease loading.

# **DC Characteristics**

Table 107 lists the DC characteristics of the Z8 Encore! XP F64xx Series products. All voltages are referenced to  $V_{SS}$ , the primary system ground.

|                  |                                             | T <sub>A</sub> =    | <b>-40°C to</b> 1 | 125°C                |       |                                                                                                                                                 |

|------------------|---------------------------------------------|---------------------|-------------------|----------------------|-------|-------------------------------------------------------------------------------------------------------------------------------------------------|

| Symbol           | Parameter                                   | Minimum             | Typical           | Maximum              | Units | Conditions                                                                                                                                      |

| V <sub>DD</sub>  | Supply Voltage                              | 3.0                 | -                 | 3.6                  | V     |                                                                                                                                                 |

| V <sub>IL1</sub> | Low Level Input<br>Voltage                  | -0.3                | -                 | 0.3*V <sub>DD</sub>  | V     | For all input pins except<br>RESET, DBG, X <sub>IN</sub>                                                                                        |

| V <sub>IL2</sub> | Low Level Input<br>Voltage                  | -0.3                | -                 | 0.2*V <sub>DD</sub>  | V     | For RESET, DBG, and<br>X <sub>IN</sub> .                                                                                                        |

| V <sub>IH1</sub> | High Level Input<br>Voltage                 | 0.7*V <sub>DD</sub> | -                 | 5.5                  | V     | Port A, C, D, E, F, and G pins.                                                                                                                 |

| V <sub>IH2</sub> | High Level Input<br>Voltage                 | 0.7*V <sub>DD</sub> | -                 | V <sub>DD</sub> +0.3 | V     | Port B and H pins.                                                                                                                              |

| V <sub>IH3</sub> | High Level Input<br>Voltage                 | 0.8*V <sub>DD</sub> | -                 | V <sub>DD</sub> +0.3 | V     | RESET, DBG, and X <sub>IN</sub><br>pins                                                                                                         |

| V <sub>OL1</sub> | Low Level Output<br>Voltage Standard Drive  | -                   | _                 | 0.4                  | V     | $I_{OL} = 2 \text{ mA}; V_{DD} = 3.0 \text{V}$<br>High Output Drive dis-<br>abled.                                                              |

| V <sub>OH1</sub> | High Level Output<br>Voltage Standard Drive | 2.4                 | _                 | -                    | V     | $I_{OH} = -2 \text{ mA}; V_{DD} = 3.0 \text{ V}$<br>High Output Drive disabled.                                                                 |

| V <sub>OL2</sub> | Low Level Output<br>Voltage High Drive      | -                   | _                 | 0.6                  | V     | $I_{OL} = 20 \text{ mA}; V_{DD} = 3.3 \text{ V}$<br>High Output Drive<br>enabled<br>$T_A = -40^{\circ}\text{C} \text{ to } +70^{\circ}\text{C}$ |

| V <sub>OH2</sub> | High Level Output<br>Voltage<br>High Drive  | 2.4                 | _                 | -                    | V     | $I_{OH} = -20$ mA; $V_{DD} = 3.3$ V<br>High Output Drive<br>enabled;<br>$T_A = -40^{\circ}$ C to +70°C                                          |

| V <sub>OL3</sub> | Low Level Output<br>Voltage<br>High Drive   | -                   | _                 | 0.6                  | V     | $I_{OL}$ = 15 mA; $V_{DD}$ = 3.3V<br>High Output Drive<br>enabled;<br>$T_A$ = +70°C to +105°C                                                   |

| Table | 107. | DC | Characteristics |

|-------|------|----|-----------------|

| 14010 |      |    | •               |

Notes:

1. This condition excludes all pins that have on-chip pull-ups, when driven Low.

2. These values are provided for design guidance only and are not tested in production.

Table 111 list the Flash memory electrical characteristics and timing.

|                                                  |         | <sub>DD</sub> = 3.0–3.<br>–40°C to 1 |         |        |                                                                                                                                                                |

|--------------------------------------------------|---------|--------------------------------------|---------|--------|----------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Parameter                                        | Minimum | Typical                              | Maximum | Units  | Notes                                                                                                                                                          |

| Flash Byte Read Time                             | 50      | _                                    | -       | ns     |                                                                                                                                                                |

| Flash Byte Program<br>Time                       | 20      | _                                    | 40      | μs     |                                                                                                                                                                |

| Flash Page Erase Time                            | 10      | _                                    | -       | ms     |                                                                                                                                                                |

| Flash Mass Erase Time                            | 200     | _                                    | -       | ms     |                                                                                                                                                                |

| Writes to Single<br>Address Before Next<br>Erase | -       | _                                    | 2       |        |                                                                                                                                                                |

| Flash Row Program<br>Time                        | _       | _                                    | 8       | ms     | Cumulative program time for single<br>row cannot exceed limit before next<br>erase. This parameter is only an<br>issue when bypassing the Flash<br>Controller. |

| Data Retention                                   | 100     | _                                    | _       | years  | 25°C                                                                                                                                                           |

| Endurance, –40°C to 105°C                        | 10,000  | -                                    | -       | cycles | Program/erase cycles                                                                                                                                           |

| Endurance, 106°C to 125°C                        | 1,000   | -                                    | -       | cycles | Program/erase cycles                                                                                                                                           |

Table 112 lists the Watchdog Timer electrical characteristics and timing.

|                  |                                                               |         | <sub>DD</sub> = 3.0–3.<br>–40°C to 1 |         |       |            |

|------------------|---------------------------------------------------------------|---------|--------------------------------------|---------|-------|------------|

| Symbol           | Parameter                                                     | Minimum | Typical                              | Maximum | Units | Conditions |

| F <sub>WDT</sub> | WDT Oscillator<br>Frequency                                   | 5       | 10                                   | 20      | kHz   |            |

| I <sub>WDT</sub> | WDT Oscillator Current<br>including internal RC<br>Oscillator | _       | <1                                   | 5       | μA    |            |

213

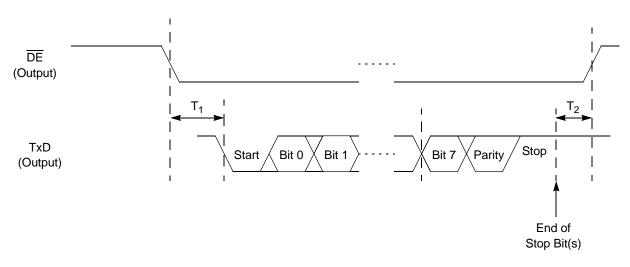

Figure 57 and Table 122 provide timing information for UART pins for the case where the Clear To Send input signal ( $\overline{\text{CTS}}$ ) is not used for flow control. In this example, it is assumed that the Driver Enable polarity has been configured to be Active Low and is represented here by  $\overline{\text{DE}}$ .  $\overline{\text{DE}}$  asserts after the UART Transmit Data Register has been written.  $\overline{\text{DE}}$  remains asserted for multiple characters as long as the Transmit Data Register is written with the next character before the current character has completed.

Figure 57. UART Timing without CTS

| Table 122  | UΔRT | Timina  | without CTS |

|------------|------|---------|-------------|

| Table 122. | UALI | rinning | without CTS |

|                |                                                                | Dela                       | ıy (ns)                                      |

|----------------|----------------------------------------------------------------|----------------------------|----------------------------------------------|

| Parameter      | Abbreviation                                                   | Minimum                    | Maximum                                      |

| T <sub>1</sub> | DE Assertion to TxD Falling Edge (Start) Delay                 | 1 bit period               | 1 bit period +<br>1 * X <sub>IN</sub> period |

| T <sub>2</sub> | End of stop bit(s) to $\overline{\text{DE}}$ Deassertion Delay | 1 * X <sub>IN</sub> period | 2 * X <sub>IN</sub> period                   |

## Hex Address: F19

#### Table 163. Timer 0–3 Low Byte Register (TxL)

| Bit     | 7                      | 6   | 5 | 4 | 3 | 2 | 1 | 0 |  |  |  |

|---------|------------------------|-----|---|---|---|---|---|---|--|--|--|

| Field   |                        | TL  |   |   |   |   |   |   |  |  |  |

| RESET   |                        | 0 1 |   |   |   |   |   |   |  |  |  |

| R/W     |                        | R/W |   |   |   |   |   |   |  |  |  |

| Address | F01H, F09H, F11H, F19H |     |   |   |   |   |   |   |  |  |  |

## Hex Address: F1A

#### Table 164. Timer 0–3 Reload High Byte Register (TxRH)

| Bit     | 7                      | 6   | 5 | 4 | 3 | 2 | 1 | 0 |  |  |

|---------|------------------------|-----|---|---|---|---|---|---|--|--|

| Field   |                        | TRH |   |   |   |   |   |   |  |  |

| RESET   |                        | 1   |   |   |   |   |   |   |  |  |

| R/W     |                        | R/W |   |   |   |   |   |   |  |  |

| Address | F02H, F0AH, F12H, F1AH |     |   |   |   |   |   |   |  |  |

## Hex Address: F1B

#### Table 165. Timer 0–3 Reload Low Byte Register (TxRL)

| Bit     | 7 | 6   | 5 | 4          | 3         | 2 | 1 | 0 |  |  |

|---------|---|-----|---|------------|-----------|---|---|---|--|--|

| Field   |   | TRL |   |            |           |   |   |   |  |  |

| RESET   |   | 1   |   |            |           |   |   |   |  |  |

| R/W     |   | R/W |   |            |           |   |   |   |  |  |

| Address |   |     | F | 03H, F0BH, | F13H, F1B | H |   |   |  |  |

#### Hex Address: F1C

#### Table 166. Timer 0–3 PWM High Byte Register (TxPWMH)

| Bit     | 7 | 6    | 5 | 4          | 3         | 2 | 1 | 0 |  |  |

|---------|---|------|---|------------|-----------|---|---|---|--|--|

| Field   |   | PWMH |   |            |           |   |   |   |  |  |

| RESET   |   | 0    |   |            |           |   |   |   |  |  |

| R/W     |   | R/W  |   |            |           |   |   |   |  |  |

| Address |   |      | F | 04H, F0CH, | F14H, F1C | Н |   |   |  |  |

## Hex Address: F43

## Table 174. UART Control 1 Register (UxCTL1)

| Bit     | 7       | 6    | 5       | 4       | 3       | 2      | 1      | 0    |  |  |  |

|---------|---------|------|---------|---------|---------|--------|--------|------|--|--|--|

| Field   | MPMD[1] | MPEN | MPMD[0] | MPBT    | DEPOL   | BRGCTL | RDAIRQ | IREN |  |  |  |

| RESET   |         | 0    |         |         |         |        |        |      |  |  |  |

| R/W     |         | R/W  |         |         |         |        |        |      |  |  |  |

| Address |         |      |         | F43H ar | nd F4BH |        |        |      |  |  |  |

## Hex Address: F44

## Table 175. UART Status 1 Register (UxSTAT1)

| Bit     | 7 | 6                    | 5 | 4 | 3 | 2 | 1 | 0 |  |  |  |

|---------|---|----------------------|---|---|---|---|---|---|--|--|--|

| Field   |   | Reserved NEWFRM MPRX |   |   |   |   |   |   |  |  |  |

| RESET   |   | 0                    |   |   |   |   |   |   |  |  |  |

| R/W     |   | R R/W R              |   |   |   |   |   |   |  |  |  |

| Address |   | F44H and F4CH        |   |   |   |   |   |   |  |  |  |

## Hex Address: F45

## Table 176. UART Address Compare Register (UxADDR)

| Bit     | 7 | 6         | 5 | 4       | 3       | 2 | 1 | 0 |  |  |

|---------|---|-----------|---|---------|---------|---|---|---|--|--|

| Field   |   | COMP_ADDR |   |         |         |   |   |   |  |  |

| RESET   |   | 0         |   |         |         |   |   |   |  |  |

| R/W     |   |           |   | R/      | W       |   |   |   |  |  |

| Address |   |           |   | F45H ar | nd F4DH |   |   |   |  |  |

## Hex Address: F46

## Table 177. UART Baud Rate High Byte Register (UxBRH)

| Bit     | 7 | 6 | 5 | 4       | 3       | 2 | 1 | 0 |  |  |

|---------|---|---|---|---------|---------|---|---|---|--|--|

| Field   |   |   |   | BF      | RH      |   |   |   |  |  |

| RESET   |   | 1 |   |         |         |   |   |   |  |  |

| R/W     |   |   |   | R/      | W       |   |   |   |  |  |

| Address |   |   |   | F46H ar | nd F4EH |   |   |   |  |  |

# **General-Purpose Input/Output (GPIO)**

For more information about these GPIO Control registers, see the <u>GPIO Control Register</u> <u>Definitions</u> section on page 39.

### Hex Address: FD0

#### Table 229. Port A–H GPIO Address Registers (PxADDR)

| Bit     | 7 | 6          | 5           | 4         | 3           | 2          | 1   | 0 |  |  |

|---------|---|------------|-------------|-----------|-------------|------------|-----|---|--|--|

| Field   |   | PADDR[7:0] |             |           |             |            |     |   |  |  |

| RESET   |   | 00H        |             |           |             |            |     |   |  |  |

| R/W     |   |            |             | R/        | W           |            |     |   |  |  |

| Address |   | FD0        | H, FD4H, Fl | D8H, FDCH | , FE0H, FE4 | H, FE8H, F | ECH |   |  |  |

### Hex Address: FD1

#### Table 230. Port A–H Control Registers (PxCTL)

| Bit     | 7 | 6    | 5           | 4         | 3           | 2          | 1   | 0 |  |  |  |

|---------|---|------|-------------|-----------|-------------|------------|-----|---|--|--|--|

| Field   |   | PCTL |             |           |             |            |     |   |  |  |  |

| RESET   |   | 00H  |             |           |             |            |     |   |  |  |  |

| R/W     |   |      |             | R/        | W           |            |     |   |  |  |  |

| Address |   | FD1  | H, FD5H, FI | D9H, FDDH | , FE1H, FE5 | H, FE9H, F | EDH |   |  |  |  |

#### Hex Address: FD2

#### Table 231. Port A–H Input Data Registers (PxIN)

| Bit     | 7    | 6                                      | 5           | 4          | 3         | 2          | 1   | 0 |  |  |

|---------|------|----------------------------------------|-------------|------------|-----------|------------|-----|---|--|--|

| Field   | PIN7 | PIN7 PIN6 PIN5 PIN4 PIN3 PIN2 PIN1 PIN |             |            |           |            |     |   |  |  |

| RESET   | X    |                                        |             |            |           |            |     |   |  |  |

| R/W     |      | R                                      |             |            |           |            |     |   |  |  |

| Address |      | FD2                                    | H, FD6H, FI | DAH, FDEH, | FE2H, FE6 | H, FEAH, F | EEH |   |  |  |

## Hex Address: FD3

#### Table 232. Port A–H Output Data Register (PxOUT)

| Bit     | 7     | 6                                              | 5 | 4 | 3 | 2 | 1 | 0 |  |

|---------|-------|------------------------------------------------|---|---|---|---|---|---|--|

| Field   | POUT7 | POUT7 POUT6 POUT5 POUT4 POUT3 POUT2 POUT1 POU  |   |   |   |   |   |   |  |

| RESET   | 0     |                                                |   |   |   |   |   |   |  |

| R/W     | R/W   |                                                |   |   |   |   |   |   |  |

| Address |       | FD3H, FD7H, FDBH, FDFH, FE3H, FE7H, FEBH, FEFH |   |   |   |   |   |   |  |

## Hex Address: FD4

#### Table 233. Port A–H GPIO Address Registers (PxADDR)

| Bit     | 7          | 6                                              | 5 | 4 | 3 | 2 | 1 | 0 |  |

|---------|------------|------------------------------------------------|---|---|---|---|---|---|--|

| Field   | PADDR[7:0] |                                                |   |   |   |   |   |   |  |

| RESET   | 00H        |                                                |   |   |   |   |   |   |  |

| R/W     | R/W        |                                                |   |   |   |   |   |   |  |

| Address |            | FD0H, FD4H, FD8H, FDCH, FE0H, FE4H, FE8H, FECH |   |   |   |   |   |   |  |

## Hex Address: FD5

#### Table 234. Port A–H Control Registers (PxCTL)

| Bit     | 7    | 6   | 5           | 4          | 3           | 2           | 1   | 0 |  |

|---------|------|-----|-------------|------------|-------------|-------------|-----|---|--|

| Field   | PCTL |     |             |            |             |             |     |   |  |

| RESET   | 00H  |     |             |            |             |             |     |   |  |

| R/W     | R/W  |     |             |            |             |             |     |   |  |

| Address |      | FD1 | H, FD5H, Fl | D9H, FDDH, | , FE1H, FE5 | 5H, FE9H, F | EDH |   |  |

#### Hex Address: FD6

#### Table 235. Port A-H Input Data Registers (PxIN)

| Bit     | 7    | 6    | 5           | 4          | 3           | 2          | 1    | 0    |  |

|---------|------|------|-------------|------------|-------------|------------|------|------|--|

| Field   | PIN7 | PIN6 | PIN5        | PIN4       | PIN3        | PIN2       | PIN1 | PIN0 |  |

| RESET   | X    |      |             |            |             |            |      |      |  |

| R/W     | R    |      |             |            |             |            |      |      |  |

| Address |      | FD2  | H, FD6H, FD | DAH, FDEH, | , FE2H, FE6 | H, FEAH, F | EEH  |      |  |

compare with carry 231 compare with carry - extended addressing 231 complement 234 complement carry flag 232, 233 condition code 228 continuous conversion (ADC) 165 continuous mode 79 control register definition, UART 99 control register, I2C 145 counter modes 79 CP 231 CPC 231 **CPCX 231** CPU and peripheral overview 4 CPU control instructions 233 **CPX 231** Customer Feedback Form 305 customer feedback form 294 **Customer Information 305**

# D

DA 228, 231 data register, I2C 142 DC characteristics 203 debugger, on-chip 184 DEC 231 decimal adjust 231 decrement 231 decrement and jump non-zero 234 decrement word 231 **DECW 231** destination operand 229 device, port availability 37 DI 233 direct address 228 direct memory access controller 151 disable interrupts 233 **DJNZ 234** DMA address high nibble register 156 configuring DMA0-1 data transfer 151 configuring for DMA\_ADC data transfer 153 control of ADC 166

control register 154 control register definitions 153 controller 6 DMA\_ADC address register 158 DMA ADC control register 159 DMA\_ADC operation 152 end address low byte register 157 I/O address register 155 operation 151 start/current address low byte register 157 status register 160 DMAA\_STAT register 160 **DMAACTL** register 159 DMAxCTL register 154, 268, 269 DMAxEND register 157, 269, 270 DMAxH register 156, 268, 270 DMAxI/O address (DMAxIO) 155, 268, 269 DMAxIO register 155, 268, 269 DMAxSTART register 157, 268, 270 dst 229

# Ε

EI 233 electrical characteristics 201 ADC 215 flash memory and timing 214 GPIO input data sample timing 218 watch-dog timer 214 enable interrupt 233 ER 228 extended addressing register 228 external pin reset 33 external RC oscillator 213 eZ8 CPU features 4 eZ8 CPU instruction classes 231 eZ8 CPU instruction notation 228 eZ8 CPU instruction set 226 eZ8 CPU instruction summary 235

## F

FCTL register 177, 285 features, Z8 Encore! 1

294

increment word 231 **INCW 231** indexed 229 indirect address prefix 229 indirect register 228 indirect register pair 228 indirect working register 228 indirect working register pair 228 infrared encoder/decoder (IrDA) 110 instruction set, ez8 CPU 226 instructions ADC 231 **ADCX 231** ADD 231 **ADDX 231** AND 234 **ANDX 234** arithmetic 231 **BCLR 232** BIT 232 bit manipulation 232 block transfer 232 **BRK 234 BSET 232** BSWAP 232, 235 **BTJ 234** BTJNZ 234 **BTJZ 234 CALL 234** CCF 232, 233 **CLR 233** COM 234 CP 231 CPC 231 **CPCX 231** CPU control 233 **CPX 231** DA 231 **DEC 231 DECW 231** DI 233 **DJNZ 234**

**INC 231 INCW 231 IRET 234** JP 234 LD 233 LDC 233 LDCI 232, 233 LDE 233 **LDEI 232** LDX 233 LEA 233 load 233 logical 234 **MULT 232** NOP 233 OR 234 **ORX 234** POP 233 POPX 233 program control 234 **PUSH 233** PUSHX 233 RCF 232, 233 **RET 234** RL 235 **RLC 235** rotate and shift 235 **RR 235 RRC 235 SBC 232** SCF 232, 233 **SRA 235 SRL 235 SRP 233 STOP 233 SUB 232 SUBX 232 SWAP 235 TCM 232 TCMX 232** TM 232 TMX 232 **TRAP 234** watch-dog timer refresh 233

EI 233

**HALT 233**

296