Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                    |

|----------------------------|-----------------------------------------------------------|

| Core Processor             | eZ8                                                       |

| Core Size                  | 8-Bit                                                     |

| Speed                      | 20MHz                                                     |

| Connectivity               | I²C, IrDA, SPI, UART/USART                                |

| Peripherals                | Brown-out Detect/Reset, DMA, POR, PWM, WDT                |

| Number of I/O              | 29                                                        |

| Program Memory Size        | 64KB (64K x 8)                                            |

| Program Memory Type        | FLASH                                                     |

| EEPROM Size                | -                                                         |

| RAM Size                   | 4K x 8                                                    |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                 |

| Data Converters            | A/D 8x10b                                                 |

| Oscillator Type            | Internal                                                  |

| Operating Temperature      | 0°C ~ 70°C (TA)                                           |

| Mounting Type              | Through Hole                                              |

| Package / Case             | 40-DIP (0.620", 15.75mm)                                  |

| Supplier Device Package    | -                                                         |

| Purchase URL               | https://www.e-xfl.com/product-detail/zilog/z8f6421pm020sg |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

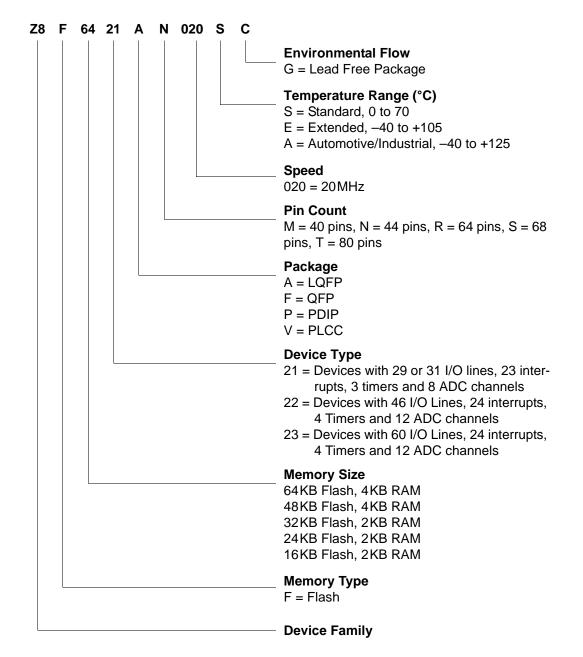

# **Part Selection Guide**

Table 1 identifies the basic features and package styles available for each device within the Z8 Encore! XP product line.

| Part<br>Number | Flash<br>(KB) | RAM<br>(KB) | I/O | 16-bit<br>Timers<br>with PWM | ADC<br>Inputs | UARTs<br>with IrDA | I <sup>2</sup> C | SPI | 40-/<br>44-Pin<br>Package | 64/68-Pin<br>Package | 80-Pin<br>Package |

|----------------|---------------|-------------|-----|------------------------------|---------------|--------------------|------------------|-----|---------------------------|----------------------|-------------------|

| Z8F1621        | 16            | 2           | 31  | 3                            | 8             | 2                  | 1                | 1   | Х                         |                      |                   |

| Z8F1622        | 16            | 2           | 46  | 4                            | 12            | 2                  | 1                | 1   |                           | Х                    |                   |

| Z8F2421        | 24            | 2           | 31  | 3                            | 8             | 2                  | 1                | 1   | Х                         |                      |                   |

| Z8F2422        | 24            | 2           | 46  | 4                            | 12            | 2                  | 1                | 1   |                           | Х                    |                   |

| Z8F3221        | 32            | 2           | 31  | 3                            | 8             | 2                  | 1                | 1   | Х                         |                      |                   |

| Z8F3222        | 32            | 2           | 46  | 4                            | 12            | 2                  | 1                | 1   |                           | Х                    |                   |

| Z8F4821        | 48            | 4           | 31  | 3                            | 8             | 2                  | 1                | 1   | Х                         |                      |                   |

| Z8F4822        | 48            | 4           | 46  | 4                            | 12            | 2                  | 1                | 1   |                           | Х                    |                   |

| Z8F4823        | 48            | 4           | 60  | 4                            | 12            | 2                  | 1                | 1   |                           |                      | Х                 |

| Z8F6421        | 64            | 4           | 31  | 3                            | 8             | 2                  | 1                | 1   | Х                         |                      |                   |

| Z8F6422        | 64            | 4           | 46  | 4                            | 12            | 2                  | 1                | 1   |                           | Х                    |                   |

| Z8F6423        | 64            | 4           | 60  | 4                            | 12            | 2                  | 1                | 1   |                           |                      | Х                 |

Table 1. Z8 Encore! XP F64xx Series Part Selection Guide

### Z8 Encore! XP<sup>®</sup> F64xx Series Product Specification

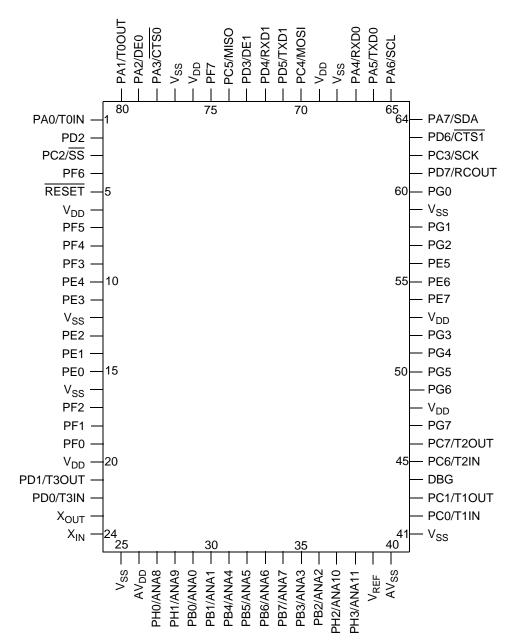

Figure 7. Z8 Encore! XP F64xx Series in 80-Pin Quad Flat Package (QFP)

13

# **Register File Address Map**

Table 7 provides the address map for the Register File of the Z8 Encore! XP F64xx Series products. Not all devices and package styles in the Z8 Encore! XP F64xx Series support Timer 3 and all of the GPIO ports. Consider registers for unimplemented peripherals to be reserved.

| Address (H | ex) Register Description          | Mnemonic | Reset (Hex) | Page      |

|------------|-----------------------------------|----------|-------------|-----------|

| General-Pu | rpose RAM                         |          |             |           |

| 000-EFF    | General-Purpose Register File RAM |          | XX          |           |

| Timer 0    |                                   |          |             |           |

| F00        | Timer 0 High Byte                 | T0H      | 00          | <u>72</u> |

| F01        | Timer 0 Low Byte                  | TOL      | 01          | <u>72</u> |

| F02        | Timer 0 Reload High Byte          | TORH     | FF          | <u>74</u> |

| F03        | Timer 0 Reload Low Byte           | TORL     | FF          | <u>74</u> |

| F04        | Timer 0 PWM High Byte             | TOPWMH   | 00          | <u>75</u> |

| F05        | Timer 0 PWM Low Byte              | TOPWML   | 00          | <u>75</u> |

| F06        | Timer 0 Control 0                 | TOCTLO   | 00          | <u>76</u> |

| F07        | Timer 0 Control 1                 | T0CTL1   | 00          | <u>77</u> |

| Timer 1    |                                   |          |             |           |

| F08        | Timer 1 High Byte                 | T1H      | 00          | <u>72</u> |

| F09        | Timer 1 Low Byte                  | T1L      | 01          | <u>72</u> |

| F0A        | Timer 1 Reload High Byte          | T1RH     | FF          | <u>74</u> |

| F0B        | Timer 1 Reload Low Byte           | T1RL     | FF          | <u>74</u> |

| F0C        | Timer 1 PWM High Byte             | T1PWMH   | 00          | <u>75</u> |

| F0D        | Timer 1 PWM Low Byte              | T1PWML   | 00          | <u>75</u> |

| F0E        | Timer 1 Control 0                 | T1CTL0   | 00          | <u>76</u> |

| F0F        | Timer 1 Control 1                 | T1CTL1   | 00          | <u>77</u> |

| Timer 2    |                                   |          |             |           |

| F10        | Timer 2 High Byte                 | T2H      | 00          | <u>72</u> |

| F11        | Timer 2 Low Byte                  | T2L      | 01          | <u>72</u> |

| F12        | Timer 2 Reload High Byte          | T2RH     | FF          | <u>74</u> |

| F13        | Timer 2 Reload Low Byte           | T2RL     | FF          | <u>74</u> |

#### Table 7. Z8 Encore! XP F64xx Series Register File Address Map

Note: XX = Undefined.

| Address (He      | ex) Register Description             | Mnemonic | Reset (Hex) | Page       |

|------------------|--------------------------------------|----------|-------------|------------|

| UART 1 (coi      | ntinued)                             |          |             |            |

| F4D              | UART1 Address Compare Register       | U1ADDR   | 00          | <u>105</u> |

| F4E              | UART1 Baud Rate High Byte            | U1BRH    | FF          | <u>105</u> |

| F4F              | UART1 Baud Rate Low Byte             | U1BRL    | FF          | <u>105</u> |

| l <sup>2</sup> C |                                      |          |             |            |

| F50              | I <sup>2</sup> C Data                | I2CDATA  | 00          | <u>141</u> |

| F51              | I <sup>2</sup> C Status              | I2CSTAT  | 80          | <u>142</u> |

| F52              | I <sup>2</sup> C Control             | I2CCTL   | 00          | <u>144</u> |

| F53              | I <sup>2</sup> C Baud Rate High Byte | I2CBRH   | FF          | <u>145</u> |

| F54              | I <sup>2</sup> C Baud Rate Low Byte  | I2CBRL   | FF          | <u>145</u> |

| F55              | I <sup>2</sup> C Diagnostic State    | I2CDST   | CO          | <u>147</u> |

| F56              | I <sup>2</sup> C Diagnostic Control  | I2CDIAG  | 00          | <u>149</u> |

| F57–F5F          | Reserved                             | _        | XX          |            |

| Serial Perip     | heral Interface (SPI)                |          |             |            |

| F60              | SPI Data                             | SPIDATA  | XX          | <u>121</u> |

| F61              | SPI Control                          | SPICTL   | 00          | <u>122</u> |

| F62              | SPI Status                           | SPISTAT  | 01          | <u>123</u> |

| F63              | SPI Mode                             | SPIMODE  | 00          | <u>125</u> |

| F64              | SPI Diagnostic State                 | SPIDST   | 00          | <u>126</u> |

| F65              | Reserved                             | _        | XX          |            |

| F66              | SPI Baud Rate High Byte              | SPIBRH   | FF          | <u>126</u> |

| F67              | SPI Baud Rate Low Byte               | SPIBRL   | FF          | <u>126</u> |

| F68–F6F          | Reserved                             |          | XX          |            |

| Analog-to-D      | igital Converter                     |          |             |            |

| F70              | ADC Control                          | ADCCTL   | 20          | <u>165</u> |

| F71              | Reserved                             |          | XX          |            |

| F72              | ADC Data High Byte                   | ADCD_H   | XX          | <u>167</u> |

| F73              | ADC Data Low Bits                    | ADCD_L   | XX          | <u>168</u> |

| F74–FAF          | Reserved                             |          | XX          |            |

| DMA 0            |                                      |          |             |            |

| FB0              | DMA0 Control                         | DMA0CTL  | 00          | <u>153</u> |

| FB1              | DMA0 I/O Address                     | DMA0IO   | XX          | 154        |

Table 7. Z8 Encore! XP F64xx Series Register File Address Map (Continued)

Note: XX = Undefined.

# HALT Mode

Execution of the eZ8 CPU's HALT instruction places the device into HALT Mode. In HALT Mode, the operating characteristics are:

- Primary crystal oscillator is enabled and continues to operate

- System clock is enabled and continues to operate

- eZ8 CPU is stopped

- Program Counter stops incrementing

- Watchdog Timer's internal RC oscillator continues to operate

- The Watchdog Timer continues to operate, if enabled

- All other on-chip peripherals continue to operate

The eZ8 CPU can be brought out of HALT Mode by any of the following operations:

- Interrupt

- Watchdog Timer time-out (interrupt or reset)

- Power-On Reset

- Voltage Brown-Out Reset

- External **RESET** pin assertion

To minimize current in HALT Mode, all GPIO pins which are configured as inputs must be driven to one of the supply rails ( $V_{CC}$  or GND).

# Timer 0–3 Control 1 Registers

The Timer 0–3 Control 1 (TxCTL1) registers enable/disable the timers, set the prescaler value, and determine the timer operating mode.

#### Table 46. Timer 0–3 Control 1 Register (TxCTL1)

| Bit     | 7   | 6    | 5 | 4          | 3         | 2 1 0 |  |  |  |  |

|---------|-----|------|---|------------|-----------|-------|--|--|--|--|

| Field   | TEN | TPOL |   | PRES       |           | TMODE |  |  |  |  |

| RESET   |     | 0    |   |            |           |       |  |  |  |  |

| R/W     |     | R/W  |   |            |           |       |  |  |  |  |

| Address |     |      | F | 07H, F0FH, | F17H, F1F | Н     |  |  |  |  |

| Bit  | Description                                                                                                                                                                                                                                                                                                         |  |  |  |  |  |  |

|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

| [7]  | Timer Enable                                                                                                                                                                                                                                                                                                        |  |  |  |  |  |  |

| TEN  | 0 = Timer is disabled.                                                                                                                                                                                                                                                                                              |  |  |  |  |  |  |

|      | 1 = Timer enabled to count.                                                                                                                                                                                                                                                                                         |  |  |  |  |  |  |

| [6]  | Timer Input/Output Polarity                                                                                                                                                                                                                                                                                         |  |  |  |  |  |  |

| TPOL | Operation of this bit is a function of the current operating mode of the timer.                                                                                                                                                                                                                                     |  |  |  |  |  |  |

|      | ONE-SHOT Mode                                                                                                                                                                                                                                                                                                       |  |  |  |  |  |  |

|      | When the timer is disabled, the timer output signal is set to the value of this bit. When the timer is enabled, the timer output signal is complemented upon timer reload.                                                                                                                                          |  |  |  |  |  |  |

|      | CONTINUOUS Mode                                                                                                                                                                                                                                                                                                     |  |  |  |  |  |  |

|      | When the timer is disabled, the timer output signal is set to the value of this bit. When the timer is enabled, the timer output signal is complemented upon timer reload.                                                                                                                                          |  |  |  |  |  |  |

|      | COUNTER Mode                                                                                                                                                                                                                                                                                                        |  |  |  |  |  |  |

|      | When the timer is disabled, the timer output signal is set to the value of this bit. When the timer is enabled, the timer output signal is complemented upon timer reload.<br>0 = Count occurs on the rising edge of the timer input signal.                                                                        |  |  |  |  |  |  |

|      | 1 = Count occurs on the falling edge of the timer input signal.                                                                                                                                                                                                                                                     |  |  |  |  |  |  |

|      | <ul> <li>PWM Mode</li> <li>0 = timer output is forced Low (0) when the timer is disabled. When enabled, the timer output is forced High (1) upon PWM count match and forced Low (0) upon reload.</li> <li>1 = timer output is forced High (1) when the timer is disabled. When enabled, the timer output</li> </ul> |  |  |  |  |  |  |

|      | is forced Low (0) upon PWM count match and forced High (1) upon reload.                                                                                                                                                                                                                                             |  |  |  |  |  |  |

|      | CAPTURE Mode                                                                                                                                                                                                                                                                                                        |  |  |  |  |  |  |

|      | <ul> <li>0 = Count is captured on the rising edge of the timer input signal.</li> <li>1 = Count is captured on the falling edge of the timer input signal.</li> </ul>                                                                                                                                               |  |  |  |  |  |  |

|      | COMPARE Mode                                                                                                                                                                                                                                                                                                        |  |  |  |  |  |  |

|      | When the timer is disabled, the timer output signal is set to the value of this bit. When the timer is enabled, the timer output signal is complemented upon timer reload.                                                                                                                                          |  |  |  |  |  |  |

|      | <b>GATED Mode</b><br>0 - Timer counts when the timer input signal is High (1) and interrupts are generated on the                                                                                                                                                                                                   |  |  |  |  |  |  |

|      | 0 = Timer counts when the timer input signal is High (1) and interrupts are generated on the falling edge of the timer input.                                                                                                                                                                                       |  |  |  |  |  |  |

|      | 1 = Timer counts when the timer input signal is Low (0) and interrupts are generated on the rising edge of the timer input.                                                                                                                                                                                         |  |  |  |  |  |  |

|      | CAPTURE/COMPARE Mode                                                                                                                                                                                                                                                                                                |  |  |  |  |  |  |

|      | 0 = Counting is started on the first rising edge of the timer input signal. The current count is captured on subsequent rising edges of the timer input signal.                                                                                                                                                     |  |  |  |  |  |  |

|      | 1 = Counting is started on the first falling edge of the timer input signal. The current count is captured on subsequent falling edges of the timer input signal.                                                                                                                                                   |  |  |  |  |  |  |

|      | <b>Caution:</b> When the timer output alternate function TxOUT on a GPIO port pin is enabled, TxOUT will change to whatever state the TPOL bit is in. The timer does not need to be enabled                                                                                                                         |  |  |  |  |  |  |

**Caution:** When the timer output alternate function 1xOUT on a GPIO port pin is enabled, TxOUT will change to whatever state the TPOL bit is in. The timer does not need to be enabled for that to happen. Also, the Port Data Direction Subregister is not needed to be set to output on TxOUT. Changing the TPOL bit with the timer enabled and running does not immediately change the TxOUT.

# **UART Interrupts**

The UART features separate interrupts for the transmitter and the receiver. In addition, when the UART primary functionality is disabled, the Baud Rate Generator can also function as a basic timer with interrupt capability.

# **Transmitter Interrupts**

The transmitter generates a single interrupt when the Transmit Data Register Empty bit (TDRE) is set to 1. This indicates that the transmitter is ready to accept new data for transmission. The TDRE interrupt occurs after the Transmit Shift Register has shifted the first bit of data out. At this point, the Transmit Data Register can be written with the next character to send. This provides 7 bit-periods of latency to load the Transmit Data Register before the Transmit Shift Register completes shifting the current character. Writing to the UART Transmit Data Register clears the TDRE bit to 0.

# **Receiver Interrupts**

The receiver generates an interrupt when any of the following events occurs:

• A data byte has been received and is available in the UART Receive Data Register. This interrupt can be disabled independent of the other receiver interrupt sources. The received data interrupt occurs once the receive character has been received and placed in the Receive Data Register. Software must respond to this received data available condition before the next character is completely received to avoid an overrun error.

**Note:** In MULTIPROCESSOR Mode (MPEN=1), the receive data interrupts are dependent on the multiprocessor configuration and the most recent address byte.

- A break is received

- An overrun is detected

- A data framing error is detected

# **UART Overrun Errors**

When an overrun error condition occurs the UART prevents overwriting of the valid data currently in the Receive Data Register. The Break Detect and Overrun status bits are not displayed until after the valid data has been read.

After the valid data has been read, the UART Status 0 Register is updated to indicate the overrun condition (and Break Detect, if applicable). The RDA bit is set to 1 to indicate that the Receive Data Register contains a data byte. However, because the overrun error occurred, this byte may not contain valid data and should be ignored. The BRKD bit indicates if the overrun was caused by a break condition on the line. After reading the status

>

# **UART Control 0 and Control 1 Registers**

The UART Control 0 and Control 1 Registers, shown in Tables 57 and 58, configure the properties of the UART's transmit and receive operations. The UART Control registers must not been written while the UART is enabled.

#### Table 57. UART Control 0 Register (UxCTL0)

| Bit         | 7                                                          | 6                                                                                                                                                                                                                                                                                                                                                                                            | 5    | 4       | 3       | 2              | 1             | 0    |  |  |

|-------------|------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|---------|---------|----------------|---------------|------|--|--|

| Field       | TEN                                                        | REN                                                                                                                                                                                                                                                                                                                                                                                          | CTSE | PEN     | PSEL    | SBRK           | STOP          | LBEN |  |  |

| RESET       |                                                            | 0                                                                                                                                                                                                                                                                                                                                                                                            |      |         |         |                |               |      |  |  |

| R/W         |                                                            |                                                                                                                                                                                                                                                                                                                                                                                              |      | R/      | W       |                |               |      |  |  |

| Address     |                                                            |                                                                                                                                                                                                                                                                                                                                                                                              |      | F42H ar | nd F4AH |                |               |      |  |  |

| Bit         | Descriptio                                                 | n                                                                                                                                                                                                                                                                                                                                                                                            |      |         |         |                |               |      |  |  |

| [7]<br>TEN  | This bit ena<br>and the CT<br>0 = Transm                   | <b>Transmit Enable</b><br>This bit enables or disables the transmitter. The enable is also controlled by the $\overline{\text{CTS}}$ signal and the CTSE bit. If the $\overline{\text{CTS}}$ signal is low and the CTSE bit is 1, the transmitter is enabled.<br>0 = Transmitter disabled.<br>1 = Transmitter enabled.                                                                       |      |         |         |                |               |      |  |  |

| [6]<br>REN  | This bit ena<br>0 = Receive                                | Receive Enable<br>This bit enables or disables the receiver.<br>0 = Receiver disabled.<br>1 = Receiver enabled.                                                                                                                                                                                                                                                                              |      |         |         |                |               |      |  |  |

| [5]<br>CTSE |                                                            | l <b>e</b><br>S signal has<br>RT recogniz                                                                                                                                                                                                                                                                                                                                                    |      |         |         | ntrol from the | e transmitter | :    |  |  |

| [4]<br>PEN  | This bit ena<br>by the MPE<br>0 = Parity is<br>1 = The tra | <ul> <li>Parity Enable This bit enables or disables parity. Even or odd is determined by the PSEL bit. It is overridden by the MPEN bit. 0 = Parity is disabled. 1 = The transmitter sends data with an additional parity bit and the receiver receives an additional parity bit.</li></ul>                                                                                                  |      |         |         |                |               |      |  |  |

| [3]<br>PSEL |                                                            | arity is trans                                                                                                                                                                                                                                                                                                                                                                               |      |         |         |                |               |      |  |  |

| [2]<br>SBRK | This bit pau<br>progress, s<br>0 = No brea                 | <ul> <li>1 = Odd parity is transmitted and expected on all received data.</li> <li>Send Break</li> <li>This bit pauses or breaks data transmission. Sending a break interrupts any transmission in progress, so ensure that the transmitter has finished sending data before setting this bit.</li> <li>0 = No break is sent.</li> <li>1 = The output of the transmitter is zero.</li> </ul> |      |         |         |                |               |      |  |  |

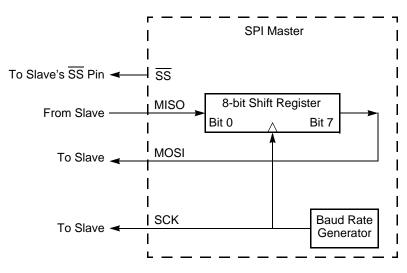

# Serial Peripheral Interface

The Serial Peripheral Interface is a synchronous interface allowing several SPI-type devices to be interconnected. SPI-compatible devices include EEPROMs, Analog-to-Digital Converters, and ISDN devices. Features of the SPI include:

- Full-duplex, synchronous, character-oriented communication

- Four-wire interface

- Data transfers rates up to a maximum of one-half the system clock frequency

- Error detection

- Dedicated Baud Rate Generator

# Architecture

The SPI may be configured as either a Master (in single or multimaster systems) or a Slave as displayed in Figures 22 through 24.

Figure 22. SPI Configured as a Master in a Single-Master, Single-Slave System

### Transfer Format PHASE Equals One

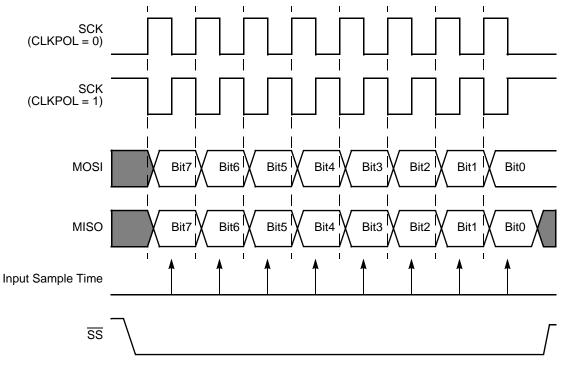

Figure 26 displays the timing diagram for an SPI transfer in which PHASE is 1. Two waveforms are depicted for SCK, one for CLKPOL reset to 0 and another for CLKPOL set to 1.

Figure 26. SPI Timing When PHASE is 1

# **Multimaster Operation**

In a multimaster SPI system, all SCK pins are tied together, all MOSI pins are tied together and all MISO pins are tied together. All SPI pins must then be configured in OPEN-DRAIN mode to prevent bus contention. At any one time, only one SPI device is configured as the Master and all other SPI devices on the bus are configured as Slaves. The Master enables a single Slave by asserting the  $\overline{SS}$  pin on that Slave only. Then, the single Master drives data out its SCK and MOSI pins to the SCK and MOSI pins on the Slaves (including those which are not enabled). The enabled Slave drives data out its MISO pin to the MISO Master pin.

For a Master device operating in a multimaster system, if the  $\overline{SS}$  pin is configured as an input and is driven Low by another Master, the COL bit is set to 1 in the SPI Status Register. The COL bit indicates the occurrence of a multimaster collision (mode fault error condition).

### Table 69. SPI Baud Rate High Byte Register (SPIBRH)

| Bit     | 7   | 6   | 5 | 4  | 3  | 2 | 1 | 0 |  |

|---------|-----|-----|---|----|----|---|---|---|--|

| Field   | BRH |     |   |    |    |   |   |   |  |

| RESET   | 1   |     |   |    |    |   |   |   |  |

| R/W     |     | R/W |   |    |    |   |   |   |  |

| Address |     |     |   | F6 | 6H |   |   |   |  |

| Bit   | Description                                                                      |

|-------|----------------------------------------------------------------------------------|

| [7:0] | SPI Baud Rate High Byte                                                          |

| BRH   | Most significant byte, BRG[15:8], of the SPI Baud Rate Generator's reload value. |

### Table 70. SPI Baud Rate Low Byte Register (SPIBRL)

| Bit     | 7   | 6    | 5 | 4 | 3 | 2 | 1 | 0 |  |

|---------|-----|------|---|---|---|---|---|---|--|

| Field   | BRL |      |   |   |   |   |   |   |  |

| RESET   |     | 1    |   |   |   |   |   |   |  |

| R/W     |     | R/W  |   |   |   |   |   |   |  |

| Address |     | F67H |   |   |   |   |   |   |  |

| Bit   | Description                                                                      |

|-------|----------------------------------------------------------------------------------|

| [7:0] | SPI Baud Rate Low Byte                                                           |

| BRL   | Least significant byte, BRG[7:0], of the SPI Baud Rate Generator's reload value. |

| 148 |  |

|-----|--|

|-----|--|

| Bit                | Description (0                     | Continued)                                                           |  |  |  |  |  |  |

|--------------------|------------------------------------|----------------------------------------------------------------------|--|--|--|--|--|--|

| [4:0]<br>TXRXSTATE | Internal State<br>Value of the int | ternal I <sup>2</sup> C state machine.                               |  |  |  |  |  |  |

|                    | TXRXSTATE                          | State Description                                                    |  |  |  |  |  |  |

| [4:0]              | 0_000                              | Idle State.                                                          |  |  |  |  |  |  |

| TXRXSTATE          | 0_0001                             | Start State.                                                         |  |  |  |  |  |  |

| (continued)        | 0_0010                             | Send/Receive data bit 7.                                             |  |  |  |  |  |  |

|                    | 0_0011                             | Send/Receive data bit 6.                                             |  |  |  |  |  |  |

|                    | 0_0100                             | Send/Receive data bit 5.                                             |  |  |  |  |  |  |

|                    | 0_0101                             | Send/Receive data bit 4.                                             |  |  |  |  |  |  |

|                    | 0_0110                             | Send/Receive data bit 3.                                             |  |  |  |  |  |  |

|                    | 0_0111                             | Send/Receive data bit 2.                                             |  |  |  |  |  |  |

|                    | 0_1000                             | Send/Receive data bit 1.                                             |  |  |  |  |  |  |

|                    | 0_1001                             | Send/Receive data bit 0.                                             |  |  |  |  |  |  |

|                    | 0_1010                             | Data Acknowledge State.                                              |  |  |  |  |  |  |

|                    | 0_1011                             | Second half of data Acknowledge State used only for not acknowledge. |  |  |  |  |  |  |

|                    | 0_1100                             | First part of stop state.                                            |  |  |  |  |  |  |

|                    | 0_1101                             | Second part of stop state.                                           |  |  |  |  |  |  |

|                    | 0_1110                             | 10-bit addressing: Acknowledge State for 2nd address byte            |  |  |  |  |  |  |

|                    | _                                  | 7-bit addressing: Address Acknowledge State.                         |  |  |  |  |  |  |

|                    | 0_1111                             | 10-bit address: Bit 0 (Least significant bit) of 2nd address byte    |  |  |  |  |  |  |

|                    | —                                  | 7-bit address: Bit 0 (Least significant bit) (R/W) of address byte.  |  |  |  |  |  |  |

|                    | 1_0000                             | 10-bit addressing: Bit 7 (Most significant bit) of 1st address byte. |  |  |  |  |  |  |

|                    | 1_0001                             | 10-bit addressing: Bit 6 of 1st address byte.                        |  |  |  |  |  |  |

|                    | 1_0010                             | 10-bit addressing: Bit 5 of 1st address byte.                        |  |  |  |  |  |  |

|                    | 1_0011                             | 10-bit addressing: Bit 4 of 1st address byte.                        |  |  |  |  |  |  |

|                    | 1_0100                             | 10-bit addressing: Bit 3 of 1st address byte.                        |  |  |  |  |  |  |

|                    | 1_0101                             | 10-bit addressing: Bit 2 of 1st address byte.                        |  |  |  |  |  |  |

|                    | 1_0110                             | 10-bit addressing: Bit 1 of 1st address byte.                        |  |  |  |  |  |  |

|                    | 1_0111                             | 10-bit addressing: Bit 0 (R/W) of 1st address byte.                  |  |  |  |  |  |  |

|                    | 1_1000                             | 10-bit addressing: Acknowledge state for 1st address byte.           |  |  |  |  |  |  |

|                    | 1_1001                             | 10-bit addressing: Bit 7 of 2nd address byte                         |  |  |  |  |  |  |

|                    | 1_1001                             | 7-bit addressing: Bit 7 of address byte.                             |  |  |  |  |  |  |

|                    | 1_1010                             | 10-bit addressing: Bit 6 of 2nd address byte                         |  |  |  |  |  |  |

|                    | 1_1010                             | 7-bit addressing: Bit 6 of address byte.                             |  |  |  |  |  |  |

|                    | 1_1011                             | 10-bit addressing: Bit 5 of 2nd address byte                         |  |  |  |  |  |  |

|                    | 1_1011                             | 7-bit addressing: Bit 5 of address byte.                             |  |  |  |  |  |  |

|                    | 1_1100                             | 10-bit addressing: Bit 4 of 2nd address byte                         |  |  |  |  |  |  |

|                    | 1_1100                             | 7-bit addressing: Bit 4 of address byte.                             |  |  |  |  |  |  |

|                    | 1_1101                             |                                                                      |  |  |  |  |  |  |

|                    | 1_1101                             | 10-bit addressing: Bit 3 of 2nd address byte                         |  |  |  |  |  |  |

|                    | 1 1110                             | 7-bit addressing: Bit 3 of address byte.                             |  |  |  |  |  |  |

|                    | 1_1110                             | 10-bit addressing: Bit 2 of 2nd address byte                         |  |  |  |  |  |  |

|                    | 1 1111                             | 7-bit addressing: Bit 2 of address byte.                             |  |  |  |  |  |  |

|                    | 1_1111                             | 10-bit addressing: Bit 1 of 2nd address byte                         |  |  |  |  |  |  |

|                    |                                    | 7-bit addressing: Bit 1 of address byte.                             |  |  |  |  |  |  |

- 2. Determine the 12-bit Start and End Register File addresses. The 12-bit Start Address is provided by {DMAx\_H[3:0], DMA\_START[7:0]}. The 12-bit End Address is provided by {DMAx\_H[7:4], DMA\_END[7:0]}.

- 3. Write the Start and End Register File address high nibbles to the DMAx End/Start Address High Nibble Register.

- 4. Write the lower byte of the Start Address to the DMAx Start/Current Address Register.

- 5. Write the lower byte of the End Address to the DMAx End Address Register.

- 6. Write to the DMAx Control Register to complete the following operations:

- Select loop or single-pass mode operation

- Select the data transfer direction (either from the Register File RAM to the onchip peripheral control register; or from the on-chip peripheral control register to the Register File RAM)

- Enable the DMAx interrupt request, if appropriate

- Select Word or Byte mode

- Select the DMA*x* request trigger

- Enable the DMA*x* channel

# **DMA\_ADC** Operation

DMA\_ADC transfers data from the ADC to the Register File. The sequence of operations in a DMA\_ADC data transfer is:

- 1. ADC completes conversion on the current ADC input channel and signals the DMA controller that two-bytes of ADC data are ready for transfer.

- 2. DMA\_ADC requests control of the system bus (address and data) from the eZ8 CPU.

- 3. After the eZ8 CPU acknowledges the bus request, DMA\_ADC transfers the two-byte ADC output value to the Register File and then returns system bus control back to the eZ8 CPU.

- 4. If the current ADC analog input is the highest-numbered input to be converted:

- The DMA\_ADC resets the ADC analog input number to 0 and initiates data conversion on ADC analog input 0

- If configured to generate an interrupt, the DMA\_ADC sends an interrupt request to the Interrupt Controller

If the current ADC analog input is not the highest-numbered input to be converted, then the DMA\_ADC initiates data conversion in the next higher-numbered ADC analog input.

Observe the following procedure to setup the Flash Sector Protect Register from user code:

- 1. Write 00H to the Flash Control Register to reset the Flash Controller.

- 2. Write 5EH to the Flash Control Register to select the Flash Sector Protect Register.

- 3. Read and/or write the Flash Sector Protect Register which is now at Register File address FF9H.

- 4. Write OOH to the Flash Control Register to return the Flash Controller to its reset state.

#### **Flash Write Protection Option Bit**

The Flash Write Protect option bit can be enabled to block all program and erase operations from user code. For more information, see the <u>Option Bits</u> chapter on page 180.

# **Byte Programming**

When the Flash Controller is unlocked, writes to Flash memory from user code will program a byte into the Flash if the address is located in the unlocked page. An erased Flash byte contains all ones (FFH). The programming operation can only be used to change bits from one to zero. To change a Flash bit (or multiple bits) from zero to one requires a Page Erase or Mass Erase operation.

Byte programming can be accomplished using the eZ8 CPU's LDC or LDCI instructions. For a description of the LDC and LDCI instructions, refer to the <u>eZ8 CPU Core User Manual (UM0128)</u>, which is available for download on <u>www.zilog.com</u>.

While the Flash Controller programs Flash memory, the eZ8 CPU idles but the system clock and on-chip peripherals continue to operate. Interrupts that occur when a programming operation is in progress are serviced after the programming operation is complete. To exit programming mode and lock the Flash Controller, write 00H to the Flash Control Register.

User code cannot program Flash memory on a page that resides in a protected sector. When user code writes memory locations, only addresses located in the unlocked page are programmed. Memory writes outside of the unlocked page are ignored.

#### **Caution:** Each memory location must not be programmed more than twice before an erase occurs.

Observe the following procedure to program the Flash from user code:

- 1. Write 00H to the Flash Control Register to reset the Flash Controller.

- 2. Write the page of memory to be programmed to the Page Select Register.

- 3. Write the first unlock command 73H to the Flash Control Register.

| Parameter                                                       | Minimum                                   | Maximum        | Units         | Notes        |

|-----------------------------------------------------------------|-------------------------------------------|----------------|---------------|--------------|

| 64-pin LQFP maximum ratings at -40°C to 70°C                    |                                           |                |               |              |

| Total power dissipation                                         |                                           | 1000           | mW            |              |

| Maximum current into $V_{DD}$ or out of $V_{SS}$                |                                           | 275            | mA            |              |

| 64-pin LQFP maximum ratings at 70°C to 125°C                    |                                           |                |               |              |

| Total power dissipation                                         |                                           | 540            | mW            |              |

| Maximum current into $V_{DD}$ or out of $V_{SS}$                |                                           | 150            | mA            |              |

| 44-pin PLCC maximum ratings at -40°C to 70°C                    |                                           |                |               |              |

| Total power dissipation                                         |                                           | 750            | mW            |              |

| Maximum current into $V_{DD}$ or out of $V_{SS}$                |                                           | 200            | mA            |              |

| 44-pin PLCC maximum ratings at 70°C to 125°C                    |                                           |                |               |              |

| Total power dissipation                                         |                                           | 295            | mW            |              |

| Maximum current into $V_{DD}$ or out of $V_{SS}$                |                                           | 83             | mA            |              |

| 44-pin LQFP maximum ratings at -40°C to 70°C                    |                                           |                |               |              |

| Total power dissipation                                         |                                           | 750            | mW            |              |

| Maximum current into $V_{DD}$ or out of $V_{SS}$                |                                           | 200            | mA            |              |

| 44-pin LQFP maximum ratings at 70°C to 125°C                    |                                           |                |               |              |

| Total power dissipation                                         |                                           | 360            | mW            |              |

| Maximum current into $V_{DD}$ or out of $V_{SS}$                |                                           | 100            | mA            |              |

| Note: This voltage applies to all pins, with the exception of V | / <sub>DD</sub> , AV <sub>DD</sub> , pins | supporting ana | log input (po | orts B and I |

#### Table 106. Absolute Maximum Ratings (Continued)

Note: This voltage applies to all pins, with the exception of V<sub>DD</sub>, AV<sub>DD</sub>, pins supporting analog input (ports B and H), RESET, and where noted otherwise.

# Hex Address: FBE

## Table 215. DMA\_ADC Control Register (DMAACTL)

| Bit     | 7    | 6     | 5               | 4  | 3  | 2 | 1 | 0 |  |  |  |

|---------|------|-------|-----------------|----|----|---|---|---|--|--|--|

| Field   | DAEN | IRQEN | Reserved ADC_IN |    |    |   |   |   |  |  |  |

| RESET   |      | 0     |                 |    |    |   |   |   |  |  |  |

| R/W     |      | R/W   |                 |    |    |   |   |   |  |  |  |

| Address |      |       |                 | FB | EH |   |   |   |  |  |  |

# Hex Address: FBF

# Table 216. DMA\_ADC Status Register (DMAA\_STAT)

| Bit     | 7 | 6   | 5      | 4  | 3        | 2    | 1    | 0    |  |  |  |

|---------|---|-----|--------|----|----------|------|------|------|--|--|--|

| Field   |   | CAD | C[3:0] |    | Reserved | IRQA | IRQ1 | IRQ0 |  |  |  |

| RESET   |   | 0   |        |    |          |      |      |      |  |  |  |

| R/W     |   | R   |        |    |          |      |      |      |  |  |  |

| Address |   |     |        | FB | FH       |      |      |      |  |  |  |

# Interrupt Request (IRQ)

For more information about these IRQ Control registers, see the <u>Interrupt Control Register</u> <u>Definitions</u> section on page 51.

# Hex Address: FC0

### Table 217. Interrupt Request 0 Register (IRQ0)

| Bit     | 7   | 6   | 5   | 4            | 3     | 2    | 1    | 0    |  |  |  |

|---------|-----|-----|-----|--------------|-------|------|------|------|--|--|--|

| Field   | T2I | T1I | TOI | <b>U0RXI</b> | U0TXI | I2CI | SPII | ADCI |  |  |  |

| RESET   |     | 0   |     |              |       |      |      |      |  |  |  |

| R/W     |     | R/W |     |              |       |      |      |      |  |  |  |

| Address |     |     |     | FC           | 0H    |      |      |      |  |  |  |

## Hex Address: FC5

#### Table 222. IRQ1 Enable Low Bit Register (IRQ1ENL)

| Bit     | 7       | 6       | 5       | 4       | 3       | 2       | 1       | 0       |

|---------|---------|---------|---------|---------|---------|---------|---------|---------|

| Field   | PAD7ENL | PAD6ENL | PAD5ENL | PAD4ENL | PAD3ENL | PAD2ENL | PAD1ENL | PAD0ENL |

| RESET   | 0       | 0       | 0       | 0       | 0       | 0       | 0       | 0       |

| R/W     |

| Address |         | ·       |         | FC      | 5H      |         | *       |         |

# Hex Address: FC6

#### Table 223. Interrupt Request 2 Register (IRQ2)

| Bit     | 7   | 6     | 5     | 4    | 3    | 2    | 1    | 0    |  |  |  |

|---------|-----|-------|-------|------|------|------|------|------|--|--|--|

| Field   | T3I | U1RXI | U1TXI | DMAI | PC3I | PC2I | PC1I | PC0I |  |  |  |

| RESET   |     | 0     |       |      |      |      |      |      |  |  |  |

| R/W     |     | R/W   |       |      |      |      |      |      |  |  |  |

| Address |     |       |       | FC   | 6H   |      |      |      |  |  |  |

# Hex Address: FC7

#### Table 224. IRQ2 Enable High Bit Register (IRQ2ENH)

| Bit     | 7     | 6      | 5      | 4      | 3     | 2     | 1     | 0     |  |  |  |

|---------|-------|--------|--------|--------|-------|-------|-------|-------|--|--|--|

| Field   | T3ENH | U1RENH | U1TENH | DMAENH | C3ENH | C2ENH | C1ENH | C0ENH |  |  |  |

| RESET   |       | 0      |        |        |       |       |       |       |  |  |  |

| R/W     |       | R/W    |        |        |       |       |       |       |  |  |  |

| Address |       |        |        | FC     | 7H    |       |       |       |  |  |  |

#### Hex Address: FC8

#### Table 225. IRQ2 Enable Low Bit Register (IRQ2ENL)

| Bit     | 7     | 6      | 5      | 4      | 3     | 2     | 1     | 0     |  |  |  |

|---------|-------|--------|--------|--------|-------|-------|-------|-------|--|--|--|

| Field   | T3ENL | U1RENL | U1TENL | DMAENL | C3ENL | C2ENL | C1ENL | C0ENL |  |  |  |

| RESET   |       | 0      |        |        |       |       |       |       |  |  |  |

| R/W     |       | R/W    |        |        |       |       |       |       |  |  |  |

| Address |       |        |        | FC     | 8H    |       |       |       |  |  |  |

### Hex Address: FF2

#### Table 263. Watchdog Timer Reload High Byte Register (WDTH)

| Bit        | 7            | 6              | 5            | 4               | 3             | 2             | 1        | 0 |  |  |  |

|------------|--------------|----------------|--------------|-----------------|---------------|---------------|----------|---|--|--|--|

| Field      |              | WDTH           |              |                 |               |               |          |   |  |  |  |

| RESET      |              | 1              |              |                 |               |               |          |   |  |  |  |

| R/W        |              |                |              | R/              | W*            |               |          |   |  |  |  |

| Address    |              | FF2H           |              |                 |               |               |          |   |  |  |  |

| Note: *R/\ | N = Read ret | urns the curre | ent WDT coun | nt value; write | sets the appr | opriate reloa | d value. |   |  |  |  |

### Hex Address: FF3

### Table 264. Watchdog Timer Reload Low Byte Register (WDTL)

| Bit        | 7            | 6              | 5            | 4               | 3             | 2              | 1        | 0 |  |  |  |

|------------|--------------|----------------|--------------|-----------------|---------------|----------------|----------|---|--|--|--|

| Field      |              | WDTL           |              |                 |               |                |          |   |  |  |  |

| RESET      |              | 1              |              |                 |               |                |          |   |  |  |  |

| R/W        |              |                |              | R/              | N*            |                |          |   |  |  |  |

| Address    |              | FF3H           |              |                 |               |                |          |   |  |  |  |

| Note: *R/\ | N = Read ret | urns the curre | ent WDT coun | nt value; write | sets the appr | ropriate reloa | d value. |   |  |  |  |

# Hex Addresses: FF4–FF7

This address range is reserved.

# **Part Number Suffix Designations**

Zilog part numbers consist of a number of component. In the following example, part number Z8F6421AN020SG is an 8-bit Flash MCU with 4KB of program memory in a 44-pin LQFP package, operating with a maximum 20MHz external clock frequency over a 0°C to +70°C temperature range and built using environmentally friendly (lead-free) solder.