Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                    |

|----------------------------|-----------------------------------------------------------|

| Core Processor             | eZ8                                                       |

| Core Size                  | 8-Bit                                                     |

| Speed                      | 20MHz                                                     |

| Connectivity               | I <sup>2</sup> C, IrDA, SPI, UART/USART                   |

| Peripherals                | Brown-out Detect/Reset, DMA, POR, PWM, WDT                |

| Number of I/O              | 31                                                        |

| Program Memory Size        | 64KB (64K x 8)                                            |

| Program Memory Type        | FLASH                                                     |

| EEPROM Size                | -                                                         |

| RAM Size                   | 4K x 8                                                    |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                 |

| Data Converters            | A/D 8x10b                                                 |

| Oscillator Type            | Internal                                                  |

| Operating Temperature      | 0°C ~ 70°C (TA)                                           |

| Mounting Type              | Surface Mount                                             |

| Package / Case             | 44-LCC (J-Lead)                                           |

| Supplier Device Package    | -                                                         |

| Purchase URL               | https://www.e-xfl.com/product-detail/zilog/z8f6421vn020sg |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| Table 70.  | SPI Baud Rate Low Byte Register (SPIBRL)                        | 127 |

|------------|-----------------------------------------------------------------|-----|

| Table 71.  | I <sup>2</sup> C Data Register (I2CDATA)                        | 142 |

| Table 72.  | I2C Status Register (I2CSTAT)                                   | 142 |

| Table 73.  | I2C Control Register (I2CCTL)                                   | 144 |

| Table 74.  | I <sup>2</sup> C Baud Rate Low Byte Register (I2CBRL)           | 146 |

| Table 75.  | I <sup>2</sup> C Baud Rate High Byte Register (I2CBRH)          | 146 |

| Table 76.  | I <sup>2</sup> C Diagnostic State Register (I2CDST)             | 147 |

| Table 77.  | I <sup>2</sup> C Diagnostic Control Register (I2CDIAG)          | 149 |

| Table 78.  | DMAx Control Register (DMAxCTL)                                 | 153 |

| Table 79.  | DMAx I/O Address Register (DMAxIO)                              | 154 |

| Table 80.  | DMAx Address High Nibble Register (DMAxH)                       | 155 |

| Table 81.  | DMAx Start/Current Address Low Byte Register (DMAxSTART)        | 156 |

| Table 82.  | DMAx End Address Low Byte Register (DMAxEND)                    | 156 |

| Table 83.  | DMA_ADC Register File Address Example                           | 157 |

| Table 84.  | DMA_ADC Control Register (DMAACTL)                              | 158 |

| Table 85.  | DMA_ADC Address Register (DMAA_ADDR)                            | 158 |

| Table 86.  | DMA_ADC Status Register (DMAA_STAT)                             | 159 |

| Table 87.  | ADC Control Register (ADCCTL)                                   | 165 |

| Table 88.  | ADC Data High Byte Register (ADCD_H)                            | 167 |

| Table 89.  | ADC Data Low Bits Register (ADCD_L)                             | 168 |

| Table 90.  | Flash Memory Configurations                                     | 169 |

| Table 91.  | Flash Memory Sector Addresses                                   | 169 |

| Table 92.  | Z8 Encore! XP F64xx Series Information Area Map                 | 171 |

| Table 93.  | Flash Control Register (FCTL)                                   | 176 |

| Table 94.  | Flash Status Register (FSTAT)                                   | 177 |

| Table 95.  | Flash Sector Protect Register (FPROT)                           | 178 |

| Table 96.  | Page Select Register (FPS)                                      | 178 |

| Table 97.  | Flash Frequency High Byte Register (FFREQH)                     | 179 |

| Table 98.  | Flash Frequency Low Byte Register (FFREQL)                      | 179 |

| Table 99.  | Flash Option Bits At Flash Memory Address 0000H                 | 181 |

| Table 100. | Options Bits at Flash Memory Address 0001H                      | 182 |

| Table 101. | OCD Baud-Rate Limits                                            | 186 |

| Table 102. | On-Chip Debugger Commands                                       | 189 |

|            | OCD Control Register (OCDCTL)                                   |     |

| Table 104. | OCD Status Register (OCDSTAT)                                   | 194 |

| Table 105. | Recommended Crystal Oscillator Specifications (20MHz Operation) | 197 |

xv

### I<sup>2</sup>C

The I<sup>2</sup>C controller makes the Z8 Encore! XP F64xx Series compatible with the I<sup>2</sup>C protocol. The I<sup>2</sup>C controller consists of two bidirectional bus lines, a serial data (SDA) line and a serial clock (SCL) line.

### Serial Peripheral Interface

The serial peripheral interface allows the Z8 Encore! XP F64xx Series to exchange data between other peripheral devices such as EEPROMs, A/D converters and ISDN devices. The SPI is a full-duplex, synchronous, character-oriented channel that supports a four-wire interface.

### Timers

Up to four 16-bit reloadable timers can be used for timing/counting events or for motor control operations. These timers provide a 16-bit programmable reload counter and operate in ONE-SHOT, CONTINUOUS, GATED, CAPTURE, COMPARE, CAPTURE AND COMPARE and PWM modes. Only 3 timers (Timer 0–2) are available in the 44-pin package.

### Interrupt Controller

The Z8 Encore! XP F64xx Series products support up to 24 interrupts. These interrupts consist of 12 internal and 12 GPIO pins. The interrupts have 3 levels of programmable interrupt priority.

### **Reset Controller**

The Z8 Encore! XP F64xx Series can be reset using the **RESET** pin, Power-On Reset, Watchdog Timer, STOP Mode exit, or Voltage Brown-Out (**VBO**) warning signal.

### **On-Chip Debugger**

The Z8 Encore! XP F64xx Series features an integrated On-Chip Debugger. The OCD provides a rich set of debugging capabilities, such as reading and writing registers, programming the Flash, setting breakpoints and executing code. A single-pin interface provides communication to the OCD.

### Port A–H Address Registers

The Port A–H Address registers, shown in Table 14, select the GPIO port functionality accessible through the Port A–H Control registers. The Port A–H Address and Control registers combine to provide access to all GPIO port control.

#### Table 14. Port A–H GPIO Address Registers (PxADDR)

| Bit     | 7          | 6                                              | 5 | 4 | 3 | 2 | 1 | 0 |  |  |

|---------|------------|------------------------------------------------|---|---|---|---|---|---|--|--|

| Field   | PADDR[7:0] |                                                |   |   |   |   |   |   |  |  |

| RESET   | 00H        |                                                |   |   |   |   |   |   |  |  |

| R/W     | R/W        |                                                |   |   |   |   |   |   |  |  |

| Address |            | FD0H, FD4H, FD8H, FDCH, FE0H, FE4H, FE8H, FECH |   |   |   |   |   |   |  |  |

| <ul> <li>[7:0] Port Address</li> <li>PADDR This port address selects one of the subregisters accessible through the Port A–H Control Registers.</li> <li>00H = No function. Provides some protection against accidental port reconfiguration.</li> <li>01H = Data Direction.</li> </ul> | Bit | Description                                                                                                                                                                                                                                                                                                                                                                                                             |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 02H = Alternate Function.<br>03H = Output Control (Open-Drain).<br>04H = High Drive Enable.<br>05H = Stop Mode Recovery Source Enable.<br>06H–FFH = No function.                                                                                                                        |     | <ul> <li>This port address selects one of the subregisters accessible through the Port A–H Control Registers.</li> <li>00H = No function. Provides some protection against accidental port reconfiguration.</li> <li>01H = Data Direction.</li> <li>02H = Alternate Function.</li> <li>03H = Output Control (Open-Drain).</li> <li>04H = High Drive Enable.</li> <li>05H = Stop Mode Recovery Source Enable.</li> </ul> |

### **Port A–H Control Registers**

The Port A–H Control registers, shown in Table 15, set the GPIO port operation. The value in the corresponding Port A–H Address Register determines the control subregisters accessible using the Port A–H Control Register.

#### Table 15. Port A–H Control Registers (PxCTL)

| Bit     | 7                                              | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

|---------|------------------------------------------------|---|---|---|---|---|---|---|

| Field   | PCTL                                           |   |   |   |   |   |   |   |

| RESET   | 00H                                            |   |   |   |   |   |   |   |

| R/W     | R/W                                            |   |   |   |   |   |   |   |

| Address | FD1H, FD5H, FD9H, FDDH, FE1H, FE5H, FE9H, FEDH |   |   |   |   |   |   |   |

| Bit   | Description                                                                                           |

|-------|-------------------------------------------------------------------------------------------------------|

| [7:0] | <b>Port Control</b>                                                                                   |

| PCTL  | The Port Control Register provides access to all subregisters that configure the GPIO Port operation. |

#### Port A–H Data Direction Subregisters

The Port A–H Data Direction Subregister, shown in Table 16, is accessed through the Port A–H Control Register by writing 01H to the Port A–H Address Register.

| Table 16. | Port A–H | Data Direction | Subregisters |

|-----------|----------|----------------|--------------|

|-----------|----------|----------------|--------------|

| Bit                                                                                                            | 7         | 7 6 5 4 3 2 1 0 |     |     |     |     |     |     |

|----------------------------------------------------------------------------------------------------------------|-----------|-----------------|-----|-----|-----|-----|-----|-----|

| Field                                                                                                          | DD7       | DD6             | DD5 | DD4 | DD3 | DD2 | DD1 | DD0 |

| RESET                                                                                                          | 1         |                 |     |     |     |     |     |     |

| R/W                                                                                                            | R/W       |                 |     |     |     |     |     |     |

| Address                                                                                                        | See note. |                 |     |     |     |     |     |     |

| Note: If a 01H exists in the Port A–H Address Register, it is accessible through the Port A–H Control Register |           |                 |     |     |     |     |     |     |

| 0 |

|---|

|   |

| BIt   | Description                                                                                                                                                                                                                                                                                                                                                                                             |

|-------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| [7:0] | Data Direction                                                                                                                                                                                                                                                                                                                                                                                          |

| DDx   | <ul> <li>These bits control the direction of the associated port pin. Port Alternate Function operation overrides the Data Direction Register setting.</li> <li>0 = Output. Data in the Port A–H Output Data Register is driven onto the port pin.</li> <li>1 = Input. The port pin is sampled and the value written into the Port A–H Input Data Register. The output driver is tri-stated.</li> </ul> |

| Note: | x indicates register bits in the range [7:0].                                                                                                                                                                                                                                                                                                                                                           |

D:4

Decerintien

### 86

#### Table 51. Watchdog Timer Reload High Byte Register (WDTH)

| Bit                                                                                             | 7      | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

|-------------------------------------------------------------------------------------------------|--------|---|---|---|---|---|---|---|

| Field                                                                                           | WDTH   |   |   |   |   |   |   |   |

| RESET                                                                                           | 1      |   |   |   |   |   |   |   |

| R/W                                                                                             | R/W*   |   |   |   |   |   |   |   |

| Address                                                                                         | s FF2H |   |   |   |   |   |   |   |

| Note: *R/W = Read returns the current WDT count value; write sets the appropriate reload value. |        |   |   |   |   |   |   |   |

| Bit   | Description                                             |

|-------|---------------------------------------------------------|

| [7:0] | WDT Reload High Byte                                    |

| WDTH  | Middle byte, bits[15:8] of the 24-bit WDT reload value. |

### Table 52. Watchdog Timer Reload Low Byte Register (WDTL)

| Bit                                                                                             | 7 | 6    | 5 | 4 | 3 | 2 | 1 | 0 |  |

|-------------------------------------------------------------------------------------------------|---|------|---|---|---|---|---|---|--|

| Field                                                                                           |   | WDTL |   |   |   |   |   |   |  |

| RESET                                                                                           |   | 1    |   |   |   |   |   |   |  |

| R/W                                                                                             |   | R/W* |   |   |   |   |   |   |  |

| Address                                                                                         |   | FF3H |   |   |   |   |   |   |  |

| Note: *R/W = Read returns the current WDT count value; write sets the appropriate reload value. |   |      |   |   |   |   |   |   |  |

| Bit   | Description                                                       |

|-------|-------------------------------------------------------------------|

| [7:0] | WDT Reload Low                                                    |

| WDTL  | Least significant byte, bits[7:0] of the 24-bit WDT reload value. |

#### Table 53. UART Transmit Data Register (UxTXD)

| Bit     | 7   | 6             | 5 | 4 | 3 | 2 | 1 | 0 |

|---------|-----|---------------|---|---|---|---|---|---|

| Field   | TXD |               |   |   |   |   |   |   |

| RESET   | X   |               |   |   |   |   |   |   |

| R/W     | W   |               |   |   |   |   |   |   |

| Address |     | F40H and F48H |   |   |   |   |   |   |

| Bit   | Description                                                        |

|-------|--------------------------------------------------------------------|

| [7:0] | Transmit Data                                                      |

| TXD   | UART transmitter data byte to be shifted out through the TXDx pin. |

### **UART Receive Data Register**

Data bytes received through the RXD*x* pin are stored in the UART Receive Data Register, shown in Table 54. The read-only UART Receive Data Register shares a Register File address with the write-only UART Transmit Data Register.

#### Table 54. UART Receive Data Register (UxRXD)

| Bit     | 7             | 6 | 5 | 4 | 3 | 2 | 1 | 0 |  |

|---------|---------------|---|---|---|---|---|---|---|--|

| Field   | RXD           |   |   |   |   |   |   |   |  |

| RESET   | X             |   |   |   |   |   |   |   |  |

| R/W     | R             |   |   |   |   |   |   |   |  |

| Address | F40H and F48H |   |   |   |   |   |   |   |  |

| Bit   | Description                                |

|-------|--------------------------------------------|

| [7:0] | Receive Data                               |

| RXD   | UART receiver data byte from the RXDx pin. |

103

| Bit  | Description (Continued)                                  |

|------|----------------------------------------------------------|

| [1]  | Stop Bit Select                                          |

| STOP | 0 = The transmitter sends one stop bit.                  |

|      | 1 = The transmitter sends two stop bits.                 |

| [0]  | Loop Back Enable                                         |

| LBEN | 0 = Normal operation.                                    |

|      | 1 = All transmitted data is looped back to the receiver. |

### Table 58. UART Control 1 Register (UxCTL1)

| Bit     | 7       | 6             | 5       | 4    | 3     | 2      | 1      | 0    |  |

|---------|---------|---------------|---------|------|-------|--------|--------|------|--|

| Field   | MPMD[1] | MPEN          | MPMD[0] | MPBT | DEPOL | BRGCTL | RDAIRQ | IREN |  |

| RESET   |         | 0             |         |      |       |        |        |      |  |

| R/W     |         | R/W           |         |      |       |        |        |      |  |

| Address |         | F43H and F4BH |         |      |       |        |        |      |  |

| Bit                | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|--------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| [7,5]<br>MPMD[1,0] | <ul> <li>MULTIPROCESSOR Mode</li> <li>If MULTIPROCESSOR (9-Bit) Mode is enabled,</li> <li>00 = The UART generates an interrupt request on all received bytes (data and address).</li> <li>01 = The UART generates an interrupt request only on received address bytes.</li> <li>10 = The UART generates an interrupt request when a received address byte matches the value stored in the Address Compare Register and on all successive data bytes until an address mismatch occurs.</li> <li>11 = The UART generates an interrupt request on all received data bytes for which the most</li> </ul> |

| [6]<br>MPEN        | <ul> <li>me of the generates an interrupt request on an received data bytes for which the most recent address byte matched the value in the Address Compare Register.</li> <li>MULTIPROCESSOR (9-bit) Enable</li> <li>This bit is used to enable MULTIPROCESSOR (9-Bit) Mode.</li> <li>0 = Disable MULTIPROCESSOR (9-Bit) Mode.</li> <li>1 = Enable MULTIPROCESSOR (9-Bit) Mode.</li> </ul>                                                                                                                                                                                                          |

| [4]<br>MPBT        | <ul> <li>MULTIPROCESSOR Bit Transmit</li> <li>This bit is applicable only when MULTIPROCESSOR (9-Bit) Mode is enabled.</li> <li>0 = Send a 0 in the multiprocessor bit location of the data stream (9th bit).</li> <li>1 = Send a 1 in the multiprocessor bit location of the data stream (9th bit).</li> </ul>                                                                                                                                                                                                                                                                                      |

| [3]<br>DEPOL       | Driver Enable Polarity<br>0 = DE signal is Active High.<br>1 = DE signal is Active Low.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

#### Table 60. UART Baud Rate High Byte Register (UxBRH)

| Bit     | 7             | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

|---------|---------------|---|---|---|---|---|---|---|

| Field   | BRH           |   |   |   |   |   |   |   |

| RESET   | 1             |   |   |   |   |   |   |   |

| R/W     | R/W           |   |   |   |   |   |   |   |

| Address | F46H and F4EH |   |   |   |   |   |   |   |

#### Table 61. UART Baud Rate Low Byte Register (UxBRL)

| Bit7    | 7   | 6             | 5 | 4 | 3 | 2 | 1 | 0 |  |

|---------|-----|---------------|---|---|---|---|---|---|--|

| Field   | BRL |               |   |   |   |   |   |   |  |

| RESET   | 1   |               |   |   |   |   |   |   |  |

| R/W     | R/W |               |   |   |   |   |   |   |  |

| Address |     | F47H and F4FH |   |   |   |   |   |   |  |

For a given UART data rate, the integer baud rate divisor value is calculated using the following equation:

UART Baud Rate Divisor Value (BRG) = Round  $\left(\frac{\text{System Clock Frequency (Hz)}}{16 \times \text{UART Data Rate (bits/s)}}\right)$

The baud rate error relative to the appropriate baud rate is calculated using the following equation:

UART Baud Rate Error (%) =

$$100 \times \left(\frac{\text{Actual Data Rate} - \text{Desired Data Rate}}{\text{Desired Data Rate}}\right)$$

For reliable communication, the UART baud rate error must never exceed 5 percent. Table 62 lists data rate errors for popular baud rates and commonly used crystal oscillator frequencies. When configured as a general purpose timer, the interrupt interval is calculated using the following equation:

Interrupt Interval (s) = System Clock Period (s)  $\times$  BRG[15:0]

### **SPI Control Register Definitions**

This section defines the features of the following Serial Peripheral Interface registers.

SPI Data Register: see page 121

SPI Control Register: see page 122

SPI Status Register: see page 123

SPI Mode Register: see page 125

SPI Diagnostic State Register: see page 126

SPI Baud Rate High and Low Byte Registers: see page 126

### **SPI Data Register**

The SPI Data Register, shown in Table 64, stores both the outgoing (transmit) data and the incoming (receive) data. Reads from the SPI Data Register always return the current contents of the 8-bit shift register. Data is shifted out starting with bit 7. The last bit received resides in bit position 0.

With the SPI configured as a Master, writing a data byte to this register initiates the data transmission. With the SPI configured as a Slave, writing a data byte to this register loads the shift register in preparation for the next data transfer with the external Master. In either the Master or Slave modes, if a transmission is already in progress, writes to this register are ignored and the overrun error flag, OVR, is set in the SPI Status Register.

When the character length is less than 8 bits (as set by the NUMBITS field in the SPI Mode Register), the transmit character must be left justified in the SPI Data Register. A received character of less than 8 bits is right justified (last bit received is in bit position 0). For example, if the SPI is configured for 4-bit characters, the transmit characters must be written to SPIDATA[7:4] and the received characters are read from SPIDATA[3:0].

| 1 | 71 |  |

|---|----|--|

|   | 11 |  |

| Function                                                                                    |

|---------------------------------------------------------------------------------------------|

| Reserved                                                                                    |

| Part Number<br>20-character ASCII alphanumeric code<br>Left-justified and filled with zeros |

| Reserved                                                                                    |

|                                                                                             |

Table 92. Z8 Encore! XP F64xx Series Information Area Map

### Operation

The Flash Controller provides the proper signals and timing for the Byte Programming, Page Erase, and Mass Erase operations within Flash memory. The Flash Controller contains a protection mechanism, via the Flash Control Register (FCTL), to prevent accidental programming or erasure. The following subsections provide details about the Lock, Unlock, Sector Protect, Byte Programming, Page Erase and Mass Erase operations.

### **Timing Using the Flash Frequency Registers**

Before performing a program or erase operation in Flash memory, you must first configure the Flash Frequency High and Low Byte registers. The Flash Frequency registers allow programming and erasure of the Flash with system clock frequencies ranging from 20kHz through 20MHz (the valid range is limited to the device operating frequencies).

The Flash Frequency High and Low Byte registers combine to form a 16-bit value, FFREQ, to control timing for Flash program and erase operations. The 16-bit Flash Frequency value must contain the system clock frequency in kHz. This value is calculated using the following equation:.

$FFREQ[15:0] = \frac{System Clock Frequency (Hz)}{1000}$

**Caution:** Flash programming and erasure are not supported for system clock frequencies below 20kHz, above 20MHz, or outside of the devices' operating frequency range. The Flash Frequency High and Low Byte registers must be loaded with the correct value to ensure proper Flash programming and erase operations.

### **Flash Read Protection**

The user code contained within Flash memory can be protected from external access. Programming the Flash Read Protect option bit prevents reading of user code by the On-Chip Debugger or by using the Flash Controller Bypass mode. For more information, see the <u>Option Bits</u> chapter on page 180 and the <u>On-Chip Debugger</u> chapter on page 183.

### **Flash Write/Erase Protection**

The Z8 Encore! XP F64xx Series provides several levels of protection against accidental program and erasure of the Flash memory contents. This protection is provided by the Flash Controller unlock mechanism, the Flash Sector Protect Register, and the Flash Write Protect option bit.

### Flash Controller Unlock Mechanism

At Reset, the Flash Controller locks to prevent accidental program or erasure of Flash memory. To program or erase Flash memory, the Flash Controller must be unlocked. After unlocking the Flash Controller, the Flash can be programmed or erased. Any value written by user code to the Flash Control Register or Page Select Register out of sequence will lock the Flash Controller.

Observe the following procedure to unlock the Flash Controller from user code:

- 1. Write 00H to the Flash Control Register to reset the Flash Controller.

- 2. Write the page to be programmed or erased to the Page Select Register.

- 3. Write the first unlock command 73H to the Flash Control Register.

- 4. Write the second unlock command 8CH to the Flash Control Register.

- 5. Rewrite the page written in <u>Step 2</u> to the Page Select Register.

#### **Flash Sector Protection**

The Flash Sector Protect Register can be configured to prevent sectors from being programmed or erased. After a sector is protected, it cannot be unprotected by user code. The Flash Sector Protect Register is cleared after reset and any previously written protection values is lost. User code must write this register in their initialization routine if they want to enable sector protection.

The Flash Sector Protect Register shares its Register File address with the Page Select Register. The Flash Sector Protect Register is accessed by writing the Flash Control Register with 5EH. After the Flash Sector Protect Register is selected, it can be accessed at the Page Select Register address. When user code writes the Flash Sector Protect Register, bits can only be set to 1. Thus, sectors can be protected, but not unprotected, via register write operations. Writing a value other than 5EH to the Flash Control Register deselects the Flash Sector Protect Register and reenables access to the Page Select Register.

The write-only Flash Control Register shares its Register File address with the read-only Flash Status Register.

| Table 93. | Flash Con | trol Register | (FCTL)  |

|-----------|-----------|---------------|---------|

| 14010 001 |           |               | (·····/ |

| Bit     | 7    | 6 | 5 | 4  | 3  | 2 | 1 | 0 |  |  |

|---------|------|---|---|----|----|---|---|---|--|--|

| Field   | FCMD |   |   |    |    |   |   |   |  |  |

| RESET   | 0    |   |   |    |    |   |   |   |  |  |

| R/W     |      | W |   |    |    |   |   |   |  |  |

| Address |      |   |   | FF | 8H |   |   |   |  |  |

| Bit   | Description                                 |  |

|-------|---------------------------------------------|--|

| [7:0] | Flash Command*                              |  |

| FCMD  | 73H = First unlock command.                 |  |

|       | 8CH = Second unlock command.                |  |

|       | 95H = Page erase command.                   |  |

|       | 63H = Mass erase command                    |  |

|       | 5EH = Flash Sector Protect Register select. |  |

| Bit        | Description (Continued)                                                                                                                                                                                                                                                                      |

|------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| [1]        | <b>Reserved</b><br>This bit is reserved and must be programmed to 0.                                                                                                                                                                                                                         |

| [0]<br>FWP | <ul> <li>Flash Write Protect (Flash version only)</li> <li>0 = Programming, Page Erase, and Mass Erase through User Code is disabled. Mass Erase is available through the On-Chip Debugger.</li> <li>1 = Programming, and Page Erase are enabled for all of Flash program memory.</li> </ul> |

### Flash Memory Address 0001H

| Table 100. Options Bits at Flash Memory Address 0001 |

|------------------------------------------------------|

|------------------------------------------------------|

| Bit       | 7           | 6                    | 5             | 4  | 3 | 2 | 1 | 0 |  |  |  |

|-----------|-------------|----------------------|---------------|----|---|---|---|---|--|--|--|

| Field     | Reserved    |                      |               |    |   |   |   |   |  |  |  |

| RESET     | U           |                      |               |    |   |   |   |   |  |  |  |

| R/W       |             | R/W                  |               |    |   |   |   |   |  |  |  |

| Address   |             | Program Memory 0001H |               |    |   |   |   |   |  |  |  |

| Note: U = | Unchanged b | by Reset. R/W        | / = Read/Writ | e. |   |   |   |   |  |  |  |

## Bit Description

[7:0] Reserved

These option bits are reserved for future use and must always be 1. This setting is the default for unprogrammed (erased) Flash.

## Operation

The following section describes the operation of the OCD.

### **OCD** Interface

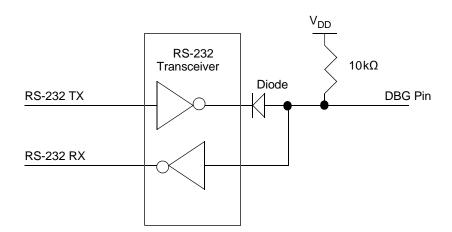

The On-Chip Debugger uses the DBG pin for communication with an external host. This one-pin interface is a bidirectional open-drain interface that transmits and receives data. Data transmission is half-duplex, meaning that transmit and receive operations cannot occur simultaneously. The serial data on the DBG pin is sent using the standard asynchronous data format defined in RS-232. This pin can interface the Z8 Encore! XP F64xx Series products to the serial port of a host PC using minimal external hardware.Two different methods for connecting the DBG pin to an RS-232 interface are depicted in Figures 37 and 38.

**Caution:** For proper operation of the On-Chip Debugger, all power pins (V<sub>DD</sub> and AV<sub>DD</sub>) must be supplied with power, and all ground pins (V<sub>SS</sub> and AV<sub>SS</sub>) must be properly grounded. The DBG pin is open-drain and must always be connected to V<sub>DD</sub> through an external pull-up resistor to ensure proper operation.

|                  |                                                     | T <sub>A</sub> = | <b>-40°C to</b> 1 | 25°C    |       |                                                                 |

|------------------|-----------------------------------------------------|------------------|-------------------|---------|-------|-----------------------------------------------------------------|

| Symbol           | Parameter                                           | Minimum          | Typical           | Maximum | Units | Conditions                                                      |

| I <sub>DDS</sub> | Stop Mode Supply                                    | _                | 520               |         | μA    | VBO and WDT enabled                                             |

|                  | Current; GPIO pins                                  |                  |                   | 700     |       | $V_{DD} = 3.6 V$                                                |

|                  | configured as outputs (see <u>Figure 47</u> on page |                  |                   | 650     |       | $V_{DD} = 3.3 V$                                                |

|                  | 209 and <u>Figure 48</u> on<br>page 210)            | -                | 10                |         | μA    | VBO disabled,<br>WDT enabled,<br>T <sub>A</sub> = 0 to 70°C     |

|                  |                                                     |                  |                   | 25      |       | $V_{DD} = 3.6 V$                                                |

|                  |                                                     |                  |                   | 20      |       | $V_{DD} = 3.3 V$                                                |

|                  |                                                     | -                | _                 |         | μA    | VBO disabled,<br>WDT enabled,<br>T <sub>A</sub> = −40 to +105ºC |

|                  |                                                     |                  |                   | 80      |       | V <sub>DD</sub> = 3.6V                                          |

|                  |                                                     |                  |                   | 70      |       | $V_{DD} = 3.3 V$                                                |

|                  |                                                     | -                | _                 |         | μA    | VBO disabled,<br>WDT enabled,<br>T <sub>A</sub> = −40 to +125ºC |

|                  |                                                     |                  |                   | 250     |       | $V_{DD} = 3.6 V$                                                |

|                  |                                                     |                  |                   | 150     |       | V <sub>DD</sub> = 3.3V                                          |

#### Table 107. DC Characteristics (Continued)

Notes:

1. This condition excludes all pins that have on-chip pull-ups, when driven Low.

2. These values are provided for design guidance only and are not tested in production.

206

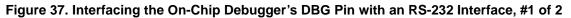

Figure 44 displays the maximum active mode current consumption across the full operating temperature range of the device and plotted opposite the system clock frequency. All GPIO pins are configured as outputs and driven High.

Figure 44. Maximum Active Mode  $\mathsf{I}_{\mathsf{DD}}$  vs. System Clock Frequency

|                  | T <sub>A</sub> = -40°C to 125°C                                |                   |          |         |       |                    |  |  |  |  |  |

|------------------|----------------------------------------------------------------|-------------------|----------|---------|-------|--------------------|--|--|--|--|--|

| Symbol           | Parameter                                                      | Minimum           | Typical* | Maximum | Units | Conditions         |  |  |  |  |  |

| V <sub>DD</sub>  | Operating Voltage<br>Range                                     | 2.70 <sup>1</sup> | -        | _       | V     |                    |  |  |  |  |  |

| R <sub>EXT</sub> | External Resistance<br>from X <sub>IN</sub> to V <sub>DD</sub> | 40                | 45       | 200     | kΩ    | $V_{DD} = V_{VBO}$ |  |  |  |  |  |

| C <sub>EXT</sub> | External Capacitance from $X_{IN}$ to $V_{SS}$                 | 0                 | 20       | 1000    | pF    |                    |  |  |  |  |  |

| F <sub>OSC</sub> | External RC Oscillation<br>Frequency                           | -                 | -        | 4       | MHz   |                    |  |  |  |  |  |

#### Table 109. External RC Oscillator Electrical Characteristics and Timing

tion as soon as the supply voltage exceeds 2.7V.

|                    |                                                     | T <sub>A</sub> = -40°C to 125°C |         |         |                  |                                                                 |  |

|--------------------|-----------------------------------------------------|---------------------------------|---------|---------|------------------|-----------------------------------------------------------------|--|

| Symbol             | Parameter                                           | Minimum                         | Typical | Maximum | Units            | Conditions                                                      |  |

| T <sub>RESET</sub> | RESET pin assertion to initiate a system reset.     | 4                               | -       | -       | T <sub>CLK</sub> | Not in STOP Mode.<br>T <sub>CLK</sub> = System Clock<br>period. |  |

| T <sub>SMR</sub>   | Stop Mode Recovery<br>pin Pulse Rejection<br>Period | 10                              | 20      | 40      | ns               | RESET, DBG, and GPIO<br>pins configured as SMR<br>sources.      |  |

#### Table 110. Reset and Stop Mode Recovery Pin Timing

## Analog-to-Digital Converter (ADC)

For more information about these ADC Control registers, see the <u>ADC Control Register</u> <u>Definitions</u> section on page 165.

### Hex Addresses: F70–F71

This address range is reserved.

### Hex Address: F72

### Table 202. ADC Data High Byte Register (ADCD\_H)

| Bit     | 7      | 6 | 5 | 4  | 3  | 2 | 1 | 0 |  |  |

|---------|--------|---|---|----|----|---|---|---|--|--|

| Field   | ADCD_H |   |   |    |    |   |   |   |  |  |

| RESET   |        | Х |   |    |    |   |   |   |  |  |

| R/W     |        | R |   |    |    |   |   |   |  |  |

| Address |        |   |   | F7 | 2H |   |   |   |  |  |

### Hex Address: F73

### Table 203. ADC Data Low Bits Register (ADCD\_L)

| Bit     | 7   | 6   | 5 4 3 2 1 0 |    |    |  |  |  |  |  |

|---------|-----|-----|-------------|----|----|--|--|--|--|--|

| Field   | ADC | D_L | Reserved    |    |    |  |  |  |  |  |

| RESET   |     | Х   |             |    |    |  |  |  |  |  |

| R/W     |     | R   |             |    |    |  |  |  |  |  |

| Address |     |     |             | F7 | 3H |  |  |  |  |  |

### Hex Addresses: F74–FAF

This address range is reserved.

## **Direct Memory Access (DMA)**

For more information about these DMA Control registers, see the <u>DMA Control Register</u> <u>Definitions</u> section on page 152.

### Flash

For more information about these Flash Control registers, see the <u>Flash Control Register</u> <u>Definitions</u> section on page 175.

### Hex Address: FF8

#### Table 265. Flash Control Register (FCTL)

| Bit     | 7    | 6 | 5 | 4 | 3 | 2 | 1 | 0 |  |

|---------|------|---|---|---|---|---|---|---|--|

| Field   | FCMD |   |   |   |   |   |   |   |  |

| RESET   | 0    |   |   |   |   |   |   |   |  |

| R/W     | W    |   |   |   |   |   |   |   |  |

| Address | FF8H |   |   |   |   |   |   |   |  |

#### Table 266. Flash Status Register (FSTAT)

| Bit     | 7              | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

|---------|----------------|---|---|---|---|---|---|---|

| Field   | Reserved FSTAT |   |   |   |   |   |   |   |

| RESET   | 0              |   |   |   |   |   |   |   |

| R/W     | R              |   |   |   |   |   |   |   |

| Address | FF8H           |   |   |   |   |   |   |   |

#### Hex Address: FF9

#### Table 267. Page Select Register (FPS)

| Bit     | 7            | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

|---------|--------------|---|---|---|---|---|---|---|

| Field   | INFO_EN PAGE |   |   |   |   |   |   |   |

| RESET   | 0            |   |   |   |   |   |   |   |

| R/W     | R/W          |   |   |   |   |   |   |   |

| Address | FF9H         |   |   |   |   |   |   |   |

# **Customer Support**

To share comments, get your technical questions answered or report issues you may be experiencing with our products, please visit Zilog's Technical Support page at <a href="http://support.zilog.com">http://support.zilog.com</a>.

To learn more about this product, find additional documentation or to discover other facets about Zilog product offerings, please visit the Zilog Knowledge Base at <u>http://zilog.com/</u><u>kb</u> or consider participating in the Zilog Forum at <u>http://zilog.com/forum</u>.

This publication is subject to replacement by a later edition. To determine whether a later edition exists, please visit the Zilog website at <u>http://www.zilog.com</u>.