Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                    |

|----------------------------|-----------------------------------------------------------|

| Core Processor             | eZ8                                                       |

| Core Size                  | 8-Bit                                                     |

| Speed                      | 20MHz                                                     |

| Connectivity               | I <sup>2</sup> C, IrDA, SPI, UART/USART                   |

| Peripherals                | Brown-out Detect/Reset, DMA, POR, PWM, WDT                |

| Number of I/O              | 46                                                        |

| Program Memory Size        | 64KB (64K x 8)                                            |

| Program Memory Type        | FLASH                                                     |

| EEPROM Size                | -                                                         |

| RAM Size                   | 4K x 8                                                    |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                 |

| Data Converters            | A/D 12x10b                                                |

| Oscillator Type            | Internal                                                  |

| Operating Temperature      | -40°C ~ 105°C (TA)                                        |

| Mounting Type              | Surface Mount                                             |

| Package / Case             | 64-LQFP                                                   |

| Supplier Device Package    | -                                                         |

| Purchase URL               | https://www.e-xfl.com/product-detail/zilog/z8f6422ar020eg |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# Z8 Encore! XP<sup>®</sup> F64xx Series Product Specification

| Table 141. | Timer 0–3 Reload Low Byte Register (TxRL) 249  | ) |

|------------|------------------------------------------------|---|

| Table 142. | Timer 0–3 PWM High Byte Register (TxPWMH) 249  | ) |

| Table 143. | Timer 0–3 PWM Low Byte Register (TxPWML) 250   | ) |

| Table 144. | Timer 0–3 Control 0 Register (TxCTL0) 250      | ) |

| Table 145. | Timer 0–3 Control 1 Register (TxCTL1) 250      | ) |

| Table 146. | Timer 0–3 High Byte Register (TxH) 250         | ) |

| Table 147. | Timer 0–3 Low Byte Register (TxL) 251          | l |

| Table 148. | Timer 0–3 Reload High Byte Register (TxRH) 251 | l |

| Table 149. | Timer 0–3 Reload Low Byte Register (TxRL) 251  | l |

| Table 150. | Timer 0–3 PWM High Byte Register (TxPWMH) 251  | l |

| Table 151. | Timer 0–3 PWM Low Byte Register (TxPWML) 252   | 2 |

| Table 152. | Timer 0–3 Control 0 Register (TxCTL0)    252   | 2 |

| Table 153. | Timer 0–3 Control 1 Register (TxCTL1) 252      | 2 |

| Table 154. | Timer 0–3 High Byte Register (TxH) 252         | 2 |

| Table 155. | Timer 0–3 Low Byte Register (TxL) 253          | 3 |

| Table 156. | Timer 0–3 Reload High Byte Register (TxRH) 253 | 3 |

| Table 157. | Timer 0–3 Reload Low Byte Register (TxRL) 253  | 3 |

| Table 158. | Timer 0–3 PWM High Byte Register (TxPWMH) 253  | 3 |

| Table 159. | Timer 0–3 PWM Low Byte Register (TxPWML) 254   | 1 |

| Table 160. | Timer 0–3 Control 0 Register (TxCTL0) 254      | 1 |

| Table 161. | Timer 0–3 Control 1 Register (TxCTL1) 254      | 1 |

| Table 162. | Timer 0–3 High Byte Register (TxH) 254         | 1 |

| Table 163. | Timer 0–3 Low Byte Register (TxL) 255          | 5 |

| Table 164. | Timer 0–3 Reload High Byte Register (TxRH) 255 | 5 |

| Table 165. | Timer 0–3 Reload Low Byte Register (TxRL) 255  | 5 |

| Table 166. | Timer 0–3 PWM High Byte Register (TxPWMH) 255  | 5 |

| Table 167. | Timer 0–3 PWM Low Byte Register (TxPWML) 256   | 5 |

| Table 168. | Timer 0–3 Control 0 Register (TxCTL0)256       | 5 |

| Table 169. | Timer 0–3 Control 1 Register (TxCTL1) 256      | 5 |

| Table 170. | UART Transmit Data Register (UxTXD) 257        | 7 |

| Table 171. | UART Receive Data Register (UxRXD) 257         | 7 |

| Table 172. | UART Status 0 Register (UxSTAT0) 257           | 7 |

| Table 173. | UART Control 0 Register (UxCTL0) 257           | 7 |

|            | UART Control 1 Register (UxCTL1) 258           |   |

| Table 175. | UART Status 1 Register (UxSTAT1) 258           | 3 |

| Table 176. | UART Address Compare Register (UxADDR) 258     | 3 |

|            |                                                |   |

# Introduction

Zilog's Z8 Encore! XP F64xx Series MCU family of products are a line of Zilog microcontroller products based upon the 8-bit eZ8 CPU. The Z8 Encore! XP F64xx Series adds Flash memory to Zilog's extensive line of 8-bit microcontrollers. The Flash in-circuit programming capability allows for faster development time and program changes in the field. The new eZ8 CPU is upward-compatible with existing Z8 instructions. The rich-peripheral set of the Z8 Encore! XP F64xx Series makes it suitable for a variety of applications including motor control, security systems, home appliances, personal electronic devices, and sensors.

### Features

The features of Z8 Encore! XP F64xx Series include:

- 20MHz eZ8 CPU

- Up to 64KB Flash with in-circuit programming capability

- Up to 4KB register RAM

- 12-channel, 10-bit Analog-to-Digital Converter (ADC)

- Two full-duplex 9-bit UARTs with bus transceiver Driver Enable control

- Inter-integrated circuit (I<sup>2</sup>C)

- Serial Peripheral Interface (SPI)

- Two Infrared Data Association (IrDA)-compliant infrared encoder/decoders

- Up to four 16-bit timers with capture, compare and PWM capability

- Watchdog Timer (WDT) with internal RC oscillator

- Three-channel DMA

- Up to 60 input/output (I/O) pins

- 24 interrupts with configurable priority

- On-Chip Debugger

- Voltage Brown-Out (VBO) Protection

- Power-On Reset (POR)

- Operating voltage of 3.0V to 3.6V with 5V-tolerant inputs

- $0^{\circ}$ C to  $+70^{\circ}$ C,  $-40^{\circ}$ C to  $+105^{\circ}$ C, and  $-40^{\circ}$ C to  $+125^{\circ}$ C operating temperature ranges

### 6

### **DMA Controller**

The Z8 Encore! XP F64xx Series feature three channels of DMA. Two of the channels are for register RAM to and from I/O operations. The third channel automatically controls the transfer of data from the ADC to the memory.

# Interrupt Edge Select Register

The Interrupt Edge Select (IRQES) Register, shown in Table 36, determines whether an interrupt is generated for the rising edge or falling edge on the selected GPIO port input pin. The Interrupt Port Select Register selects between Port A and Port D for the individual interrupts.

| Bit     | 7    | 6    | 5    | 4    | 3    | 2    | 1    | 0    |

|---------|------|------|------|------|------|------|------|------|

| Field   | IES7 | IES6 | IES5 | IES4 | IES3 | IES2 | IES1 | IES0 |

| RESET   |      | 0    |      |      |      |      |      |      |

| R/W     |      | R/W  |      |      |      |      |      |      |

| Address |      | FCDH |      |      |      |      |      |      |

| Table | 36. | Interrupt | Edae | Select | Register | (IRQES) | 1 |

|-------|-----|-----------|------|--------|----------|---------|---|

| Tubic |     | menupe    | Luge | 001001 | Register |         | , |

| Bit   | Description                                                                                                                                                                                                                                                                                                                                                                 |

|-------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| [7:0] | Interrupt Edge Select <i>x</i>                                                                                                                                                                                                                                                                                                                                              |

| IESx  | <ul> <li>The minimum pulse width should be greater than 1 system clock to guarantee capture of the edge triggered interrupt. Shorter pulses may be captured but not guaranteed.</li> <li>0 = An interrupt request is generated on the falling edge of the PAx/PDx input.</li> <li>1 = An interrupt request is generated on the rising edge of the PAx/PDx input.</li> </ul> |

| Nata  |                                                                                                                                                                                                                                                                                                                                                                             |

Note: x indicates specific GPIO port pins in the range [7:0].

### **Interrupt Port Select Register**

The Port Select (IRQPS) Register, shown in Table 37, determines the port pin that generates the PAx/PDx interrupts. This register allows either Port A or Port D pins to be used as interrupts. The Interrupt Edge Select Register controls the active interrupt edge.

| Bit     | 7     | 6     | 5     | 4     | 3     | 2     | 1     | 0     |

|---------|-------|-------|-------|-------|-------|-------|-------|-------|

| Field   | PAD7S | PAD6S | PAD5S | PAD4S | PAD3S | PAD2S | PAD1S | PAD0S |

| RESET   |       | 0     |       |       |       |       |       |       |

| R/W     |       | R/W   |       |       |       |       |       |       |

| Address |       | FCEH  |       |       |       |       |       |       |

| Bit                                                           | Description                                                      |  |  |  |  |

|---------------------------------------------------------------|------------------------------------------------------------------|--|--|--|--|

| [7:0]                                                         | PAx/PDx Selection                                                |  |  |  |  |

| PADxS                                                         | 0 = PAx is used for the interrupt for PAx/PDx interrupt request. |  |  |  |  |

|                                                               | 1 = PDx is used for the interrupt for PAx/PDx interrupt request. |  |  |  |  |

| Note: x indicates specific GPIO port pins in the range [7:0]. |                                                                  |  |  |  |  |

COMPARE Mode Time (s) =  $\frac{(Compare Value - Start Value) \times Prescale}{System Clock Frequency (Hz)}$

### GATED Mode

In GATED Mode, the timer counts only when the timer input signal is in its active state (asserted), as determined by the TPOL bit in the Timer Control 1 Register. When the timer input signal is asserted, counting begins. A timer interrupt is generated when the timer input signal is deasserted or a timer reload occurs. To determine if a timer input signal deassertion generated the interrupt, read the associated GPIO input value and compare to the value stored in the TPOL bit.

The timer counts up to the 16-bit reload value stored in the Timer Reload High and Low Byte registers. The timer input is the system clock. When reaching the reload value, the timer generates an interrupt, the count value in the Timer High and Low Byte registers is reset to 0001H and counting resumes (assuming the timer input signal is still asserted). Also, if the timer output alternate function is enabled, the timer output pin changes state (from Low to High or from High to Low) at timer reset.

Observe the following procedure for configuring a timer for GATED Mode and initiating the count:

- 1. Write to the Timer Control 1 Register to:

- Disable the timer

- Configure the timer for GATED Mode

- Set the prescale value

- 2. Write to the Timer High and Low Byte registers to set the starting count value. This only affects the first pass in GATED Mode. After the first timer reset in GATED Mode, counting always begins at the reset value of 0001H.

- 3. Write to the Timer Reload High and Low Byte registers to set the reload value.

- 4. If appropriate, enable the timer interrupt and set the timer interrupt priority by writing to the relevant interrupt registers.

- 5. Configure the associated GPIO port pin for the timer input alternate function.

- 6. Write to the Timer Control 1 Register to enable the timer.

- 7. Assert the timer input signal to initiate the counting.

### **CAPTURE/COMPARE Mode**

In CAPTURE/COMPARE Mode, the timer begins counting on the first external timer input transition. The appropriate transition (rising edge or falling edge) is set by the TPOL bit in the Timer Control 1 Register. The timer input is the system clock.

ister. This operation allows accurate reads of the full 16-bit timer count value while enabled. When the timers are not enabled, a read from the Timer Low Byte Register returns the actual value in the counter.

## **Timer Output Signal Operation**

A timer output is a GPIO port pin alternate function. Generally, the timer output is toggled every time the counter is reloaded.

# **Timer Control Register Definitions**

This section defines the features of the following Timer Control registers.

Timer 0-3 High and Low Byte Registers: see page 72

Timer Reload High and Low Byte Registers: see page 74

Timer 0-3 PWM High and Low Byte Registers: see page 75

Timer 0-3 Control 0 Registers: see page 76

Timer 0-3 Control 1 Registers: see page 77

Timers 0–2 are available in all packages. Timer 3 is only available in 64-, 68- and 80-pin packages.

## Timer 0–3 High and Low Byte Registers

The Timer 0–3 High and Low Byte (TxH and TxL) registers, shown in Tables 39 and 40, contain the current 16-bit timer count value. When the timer is enabled, a read from TxH causes the value in TxL to be stored in a temporary holding register. A read from TMRL always returns this temporary register when the timers are enabled. When the timer is disabled, reads from the TMRL read the register directly.

Writing to the Timer High and Low Byte registers while the timer is enabled is not recommended. There are no temporary holding registers available for write operations, so simultaneous 16-bit writes are not possible. If either the Timer High or Low Byte registers are written during counting, the 8-bit written value is placed in the counter (High or Low Byte) at the next clock edge. The counter continues counting from the new value.

Timer 3 is unavailable in 44-pin packages.

112

since the previous pulse was detected). This gives the endec a sampling window of minus four baud rate clocks to plus eight baud rate clocks around the expected time of an incoming pulse. If an incoming pulse is detected inside this window this process is repeated. If the incoming data is a logical 1 (no pulse), the endec returns to the initial state and waits for the next falling edge. As each falling edge is detected, the endec clock counter is reset, resynchronizing the endec to the incoming signal. This action allows the endec to tolerate jitter and baud rate errors in the incoming data stream. Resynchronizing the endec does not alter the operation of the UART, which ultimately receives the data. The UART is only synchronized to the incoming data stream when a start bit is received.

# Infrared Encoder/Decoder Control Register Definitions

All infrared endec configuration and status information is set by the UART control registers as defined in the <u>UART Control Register Definitions</u> section on page 98.

**Caution:** To prevent spurious signals during IrDA data transmission, set the IREN bit in the UARTx Control 1 Register to 1 to enable the Infrared Encoder/Decoder before enabling the GPIO Port alternate function for the corresponding pin.

# Serial Peripheral Interface

The Serial Peripheral Interface is a synchronous interface allowing several SPI-type devices to be interconnected. SPI-compatible devices include EEPROMs, Analog-to-Digital Converters, and ISDN devices. Features of the SPI include:

- Full-duplex, synchronous, character-oriented communication

- Four-wire interface

- Data transfers rates up to a maximum of one-half the system clock frequency

- Error detection

- Dedicated Baud Rate Generator

# Architecture

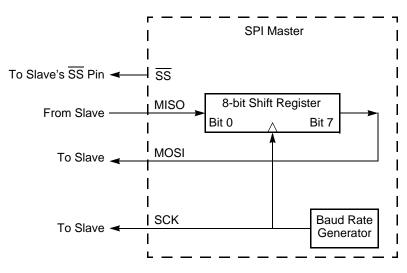

The SPI may be configured as either a Master (in single or multimaster systems) or a Slave as displayed in Figures 22 through 24.

Figure 22. SPI Configured as a Master in a Single-Master, Single-Slave System

### Transfer Format PHASE Equals One

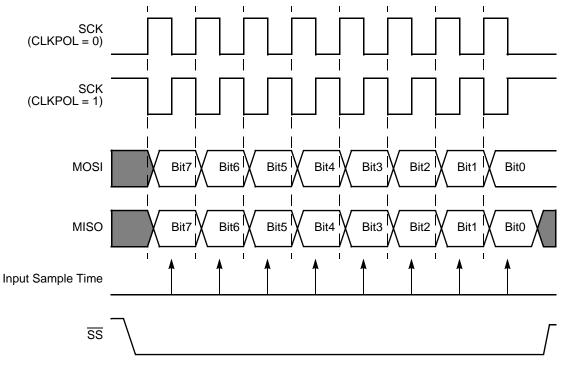

Figure 26 displays the timing diagram for an SPI transfer in which PHASE is 1. Two waveforms are depicted for SCK, one for CLKPOL reset to 0 and another for CLKPOL set to 1.

Figure 26. SPI Timing When PHASE is 1

### **Multimaster Operation**

In a multimaster SPI system, all SCK pins are tied together, all MOSI pins are tied together and all MISO pins are tied together. All SPI pins must then be configured in OPEN-DRAIN mode to prevent bus contention. At any one time, only one SPI device is configured as the Master and all other SPI devices on the bus are configured as Slaves. The Master enables a single Slave by asserting the  $\overline{SS}$  pin on that Slave only. Then, the single Master drives data out its SCK and MOSI pins to the SCK and MOSI pins on the Slaves (including those which are not enabled). The enabled Slave drives data out its MISO pin to the MISO Master pin.

For a Master device operating in a multimaster system, if the  $\overline{SS}$  pin is configured as an input and is driven Low by another Master, the COL bit is set to 1 in the SPI Status Register. The COL bit indicates the occurrence of a multimaster collision (mode fault error condition).

## **SDA and SCL Signals**

$I^2C$  sends all addresses, data and acknowledge signals over the SDA line, most significant bit first. SCL is the common clock for the  $I^2C$  Controller. When the SDA and SCL pin alternate functions are selected for their respective GPIO ports, the pins are automatically configured for open-drain operation.

The master  $(I^2C)$  is responsible for driving the SCL clock signal, although the clock signal can become skewed by a slow slave device. During the low period of the clock, the slave pulls the SCL signal Low to suspend the transaction. The master releases the clock at the end of the low period and notices that the clock remains low instead of returning to a High level. When the slave releases the clock, the I<sup>2</sup>C Controller continues the transaction. All data is transferred in bytes and there is no limit to the amount of data transferred in one operation. When transmitting data or acknowledging read data from the slave, the SDA signal changes in the middle of the low period of SCL and is sampled in the middle of the High period of SCL.

### I<sup>2</sup>C Interrupts

The I<sup>2</sup>C Controller contains four sources of interrupts—Transmit, Receive, Not Acknowledge and baud rate generator. These four interrupt sources are combined into a single interrupt request signal to the Interrupt Controller. The transmit interrupt is enabled by the IEN and TXI bits of the Control Register. The Receive and Not Acknowledge interrupts are enabled by the IEN bit of the Control Register. The baud rate generator interrupt is enabled by the BIRQ and IEN bits of the Control Register.

Not Acknowledge interrupts occur when a Not Acknowledge condition is received from the slave or sent by the I<sup>2</sup>C Controller and neither the start or stop bit is set. The Not Acknowledge event sets the NCKI bit of the I<sup>2</sup>C Status Register and can only be cleared by setting the start or stop bit in the I<sup>2</sup>C Control Register. When this interrupt occurs, the I<sup>2</sup>C Controller waits until either the stop or start bit is set before performing any action. In an interrupt service routine, the NCKI bit should always be checked prior to servicing transmit or receive interrupt conditions because it indicates the transaction is being terminated.

Receive interrupts occur when a byte of data has been received by the  $I^2C$  Controller (master reading data from slave). This procedure sets the RDRF bit of the  $I^2C$  Status Register. The RDRF bit is cleared by reading the  $I^2C$  Data Register. The RDRF bit is set during the acknowledge phase. The  $I^2C$  Controller pauses after the acknowledge phase until the receive interrupt is cleared before performing any other action.

Transmit interrupts occur when the TDRE bit of the  $I^2C$  Status Register sets and the TXI bit in the  $I^2C$  Control Register is set. transmit interrupts occur under the following conditions when the transmit data register is empty:

• The I<sup>2</sup>C Controller is enabled

If the slave were to Not Acknowledge at this point (this should not happen because the slave did acknowledge the first two address bytes), software would respond by setting the stop and flush bits and clearing the TXI bit. The  $I^2C$  Controller sends the stop condition on the bus and clears the stop and NCKI bits. The transaction is complete (ignore the following steps).

- 19. The I<sup>2</sup>C Controller shifts in a byte of data from the I<sup>2</sup>C slave on the SDA signal. The I<sup>2</sup>C Controller sends a Not Acknowledge to the I<sup>2</sup>C slave if the NAK bit is set (last byte), else it sends an Acknowledge.

- 20. The I<sup>2</sup>C Controller asserts the receive interrupt (RDRF bit set in the Status Register).

- 21. Software responds by reading the I<sup>2</sup>C Data Register which clears the RDRF bit. If there is only one more byte to receive, set the NAK bit of the I<sup>2</sup>C Control Register.

- 22. If there are one or more bytes to transfer, return to <u>Step 19</u>.

- 23. After the last byte is shifted in, a Not Acknowledge interrupt is generated by the I<sup>2</sup>C Controller.

- 24. Software responds by setting the stop bit of the  $I^2C$  Control Register.

- 25. A stop condition is sent to the  $I^2C$  slave and the stop and NCKI bits are cleared.

# I<sup>2</sup>C Control Register Definitions

This section defines the features of the following  $I^2C$  Control registers.

I2C Data Register: see page 141

I2C Status Register: see page 142

I2C Control Register: see page 144

I2C Baud Rate High and Low Byte Registers: see page 145

I2C Diagnostic State Register: see page 147

I2C Diagnostic Control Register: see page 149

# I<sup>2</sup>C Data Register

The I<sup>2</sup>C Data Register, shown in Table 71, holds the data that is to be loaded into the I<sup>2</sup>C Shift Register during a write to a slave. This register also holds data that is loaded from the I<sup>2</sup>C Shift Register during a read from a slave. The I<sup>2</sup>C Shift Register is not accessible in the Register File address space, but is used only to buffer incoming and outgoing data.

# Table 74. I<sup>2</sup>C Baud Rate High Byte Register (I2CBRH)

| Bit     | 7   | 6   | 5 | 4  | 3  | 2 | 1 | 0 |

|---------|-----|-----|---|----|----|---|---|---|

| Field   |     |     |   | BF | RH |   |   |   |

| RESET   |     | FFH |   |    |    |   |   |   |

| R/W     | R/W |     |   |    |    |   |   |   |

| Address |     |     |   | F5 | 3H |   |   |   |

| Bit   | Description                                                                                                 |

|-------|-------------------------------------------------------------------------------------------------------------|

| [7:0] | I <sup>2</sup> C Baud Rate High Byte                                                                        |

| BRH   | Most significant byte, BRG[15:8], of the I <sup>2</sup> C Baud Rate Generator's reload value.               |

|       | Note: If the DIAG bit in the I <sup>2</sup> C Diagnostic Control Register is set to 1, a read of the I2CBRH |

|       | Register returns the current value of the I <sup>2</sup> C Baud Rate Counter[15:8].                         |

# Table 75. I<sup>2</sup>C Baud Rate Low Byte Register (I2CBRL)

| Bit     | 7    | 6   | 5 | 4 | 3 | 2 | 1 | 0 |

|---------|------|-----|---|---|---|---|---|---|

| Field   |      | BRL |   |   |   |   |   |   |

| RESET   |      | FFH |   |   |   |   |   |   |

| R/W     |      | R/W |   |   |   |   |   |   |

| Address | F54H |     |   |   |   |   |   |   |

| Bit   | Description                                                                                                 |

|-------|-------------------------------------------------------------------------------------------------------------|

| [7:0] | I <sup>2</sup> C Baud Rate Low Byte                                                                         |

| BRL   | Least significant byte, BRG[7:0], of the I <sup>2</sup> C Baud Rate Generator's reload value.               |

|       | Note: If the DIAG bit in the I <sup>2</sup> C Diagnostic Control Register is set to 1, a read of the I2CBRL |

|       | Register returns the current value of the I <sup>2</sup> C Baud Rate Counter[7:0].                          |

| Bit          | Description (Continued)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|--------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| [3]<br>WSEL  | <ul> <li>Word Select</li> <li>0 = DMAx transfers a single byte per request.</li> <li>1 = DMAx transfers a two-byte word per request. The address for the on-chip peripheral control register must be an even address.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| [2:0]<br>RSS | Request Trigger Source Select         The Request Trigger Source Select field determines the peripheral that can initiate a DMA transfer. The corresponding interrupts do not need to be enabled within the Interrupt Controller to initiate a DMA transfer. However, if the Request Trigger Source can enable or disable the interrupt request sent to the Interrupt Controller, the interrupt request must be enabled within the Request Trigger Source block.         000 = Timer 0.       001 = Timer 1.         010 = Timer 2.       011 = Timer 3.         100 = DMA0 Control Register: UART0 Received Data Register contains valid data. DMA1 Control Register: UART1 Received Data Register contains valid data. DMA1 |

|              | <ul> <li>101 = DMA0 Control Register: DART1 Transmit Data Register empty.</li> <li>110 = DMA0 Control Register: I<sup>2</sup>C Receiver Interrupt. DMA1 Control Register: I<sup>2</sup>C Transmitter<br/>Interrupt Register empty.</li> <li>111 = Decerved</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

111 = Reserved.

## DMAx I/O Address Register

The DMAx I/O Address Register, shown in Table 79, contains the low byte of the on-chip peripheral address for data transfer. The full 12-bit Register File address is provided by {FH, DMAx\_IO[7:0]}. When the DMA is configured for two-byte word transfers, the DMAx I/O Address Register must contain an even-numbered address.

| Bit     | 7      | 6   | 5 | 4     | 3    | 2 | 1 | 0 |  |  |  |

|---------|--------|-----|---|-------|------|---|---|---|--|--|--|

| Field   | DMA_IO |     |   |       |      |   |   |   |  |  |  |

| RESET   |        | X   |   |       |      |   |   |   |  |  |  |

| R/W     |        | R/W |   |       |      |   |   |   |  |  |  |

| Address |        |     |   | FB1H, | FB9H |   |   |   |  |  |  |

### Table 79. DMAx I/O Address Register (DMAxIO)

| Bit    | Description                                                                                     |

|--------|-------------------------------------------------------------------------------------------------|

| [7:0]  | DMA On-Chip Peripheral Control Register Address                                                 |

| DMA_IO | This byte sets the low byte of the on-chip peripheral control register address on Register File |

|        | Page FH (addresses F00H to FFFH).                                                               |

### 216

# **AC Characteristics**

This section provides AC characteristics and timing data which assumes a standard load of 50pF on all outputs. Table 114 lists the Z8 Encore! XP F64xx Series AC characteristics and timing.

|                     |                                    |          | 0V–3.6V<br>C to 125°C |       |                                                                                                            |

|---------------------|------------------------------------|----------|-----------------------|-------|------------------------------------------------------------------------------------------------------------|

| Symbol              | Parameter                          | Minimum  | Maximum               | Units | Conditions                                                                                                 |

| F <sub>SYSCLK</sub> | System Clock Frequency             | -        | 20.0                  | MHz   | Read-only from Flash memory.                                                                               |

|                     |                                    | 0.032768 | 20.0                  | MHz   | Program or erasure of Flash memory.                                                                        |

| F <sub>XTAL</sub>   | Crystal Oscillator Frequency       | 0.032768 | 20.0                  | MHz   | System clock frequencies<br>below the crystal oscillator mini-<br>mum require an external clock<br>driver. |

| T <sub>XIN</sub>    | Crystal Oscillator Clock<br>Period | 50       | -                     | ns    | T <sub>CLK</sub> = 1/F <sub>SYSCLK</sub>                                                                   |

| T <sub>XINH</sub>   | System Clock High Time             | 20       |                       | ns    |                                                                                                            |

| T <sub>XINL</sub>   | System Clock Low Time              | 20       |                       | ns    |                                                                                                            |

| T <sub>XINR</sub>   | System Clock Rise Time             | -        | 3                     | ns    | $T_{CLK}$ = 50 ns. Slower rise times<br>can be tolerated with longer<br>clock periods.                     |

| T <sub>XINF</sub>   | System Clock Fall Time             | -        | 3                     | ns    | $T_{CLK}$ = 50 ns. Slower fall times<br>can be tolerated with longer<br>clock periods.                     |

| Table 114. / | AC Character | istics |

|--------------|--------------|--------|

|--------------|--------------|--------|

| Assembly      |                                                                                                                        |     | lress<br>ode | Opcode(s) |   |   | Fla | ags | i |   | Fetch  | Instr. |

|---------------|------------------------------------------------------------------------------------------------------------------------|-----|--------------|-----------|---|---|-----|-----|---|---|--------|--------|

| Mnemonic      | Symbolic Operation                                                                                                     | dst | src          | (Hex)     | С | Ζ | S   | V   | D | Н | Cycles | Cycles |

| TM dst, src   | dst AND src                                                                                                            | r   | r            | 72        | _ | * | *   | 0   | _ | _ | 2      | 3      |

|               |                                                                                                                        | r   | lr           | 73        | _ |   |     |     |   |   | 2      | 4      |

|               |                                                                                                                        | R   | R            | 74        | - |   |     |     |   |   | 3      | 3      |

|               |                                                                                                                        | R   | IR           | 75        | - |   |     |     |   |   | 3      | 4      |

|               |                                                                                                                        | R   | IM           | 76        | _ |   |     |     |   |   | 3      | 3      |

|               |                                                                                                                        | IR  | IM           | 77        | _ |   |     |     |   |   | 3      | 4      |

| TMX dst, src  | dst AND src                                                                                                            | ER  | ER           | 78        | - | * | *   | 0   | - | - | 4      | 3      |

|               |                                                                                                                        | ER  | IM           | 79        | _ |   |     |     |   |   | 4      | 3      |

| TRAP Vector   | $SP \leftarrow SP - 2$<br>@SP \leftarrow PC<br>$SP \leftarrow SP - 1$<br>@SP \leftarrow FLAGS<br>PC \leftarrow @Vector |     | Vecto<br>r   | F2        | - | - | -   | -   | - | - | 2      | 6      |

| WDT           |                                                                                                                        |     |              | 5F        | - | - | -   | -   | - | - | 1      | 2      |

| XOR dst, src  | $dst \gets dst \ XOR \ src$                                                                                            | r   | r            | B2        | - | * | *   | 0   | - | - | 2      | 3      |

|               |                                                                                                                        | r   | lr           | B3        | _ |   |     |     |   |   | 2      | 4      |

|               |                                                                                                                        | R   | R            | B4        | _ |   |     |     |   |   | 3      | 3      |

|               |                                                                                                                        | R   | IR           | B5        |   |   |     |     |   |   | 3      | 4      |

|               |                                                                                                                        | R   | IM           | B6        |   |   |     |     |   |   | 3      | 3      |

|               |                                                                                                                        | IR  | IM           | B7        |   |   |     |     |   |   | 3      | 4      |

| XORX dst, src | $dst \gets dst \ XOR \ src$                                                                                            | ER  | ER           | B8        | _ | * | *   | 0   | _ | - | 4      | 3      |

|               |                                                                                                                        | ER  | IM           | B9        |   |   |     |     |   |   | 4      | 3      |

### Table 136. eZ8 CPU Instruction Summary (Continued)

Note: Flags Notation:

\* = Value is a function of the result of the operation.

- = Unaffected.

X = Undefined.

0 = Reset to 0.

1 = Set to 1.

### Hex Address: F47

### Table 178. UART Baud Rate Low Byte Register (UxBRL)

| Bit7    | 7 | 6             | 5 | 4 | 3 | 2 | 1 | 0 |  |  |  |

|---------|---|---------------|---|---|---|---|---|---|--|--|--|

| Field   |   | BRL           |   |   |   |   |   |   |  |  |  |

| RESET   |   | 1             |   |   |   |   |   |   |  |  |  |

| R/W     |   | R/W           |   |   |   |   |   |   |  |  |  |

| Address |   | F47H and F4FH |   |   |   |   |   |   |  |  |  |

### Hex Address: F48

### Table 179. UART Transmit Data Register (UxTXD)

| Bit     | 7   | 6 | 5 | 4       | 3       | 2 | 1 | 0 |  |  |  |

|---------|-----|---|---|---------|---------|---|---|---|--|--|--|

| Field   | TXD |   |   |         |         |   |   |   |  |  |  |

| RESET   |     | Х |   |         |         |   |   |   |  |  |  |

| R/W     |     | W |   |         |         |   |   |   |  |  |  |

| Address |     |   |   | F40H ar | nd F48H |   |   |   |  |  |  |

### Table 180. UART Receive Data Register (UxRXD)

| Bit     | 7   | 6 | 5 | 4       | 3       | 2 | 1 | 0 |  |  |  |

|---------|-----|---|---|---------|---------|---|---|---|--|--|--|

| Field   | RXD |   |   |         |         |   |   |   |  |  |  |

| RESET   |     | X |   |         |         |   |   |   |  |  |  |

| R/W     |     | R |   |         |         |   |   |   |  |  |  |

| Address |     |   |   | F40H ar | nd F48H |   |   |   |  |  |  |

### Hex Address: F49

### Table 181. UART Status 0 Register (UxSTAT0)

| Bit     | 7   | 6  | 5  | 4       | 3       | 2    | 1   | 0   |  |  |

|---------|-----|----|----|---------|---------|------|-----|-----|--|--|

| Field   | RDA | PE | OE | FE      | BRKD    | TDRE | TXE | CTS |  |  |

| RESET   |     |    | 0  |         | 1       | Х    |     |     |  |  |

| R/W     |     | R  |    |         |         |      |     |     |  |  |

| Address |     |    |    | F41H ar | nd F49H |      |     |     |  |  |

### Hex Address: FBA

### Table 211. DMAx Address High Nibble Register (DMAxH)

| Bit     | 7 | 6     | 5     | 4     | 3           | 2 1 |  |  |  |  |  |

|---------|---|-------|-------|-------|-------------|-----|--|--|--|--|--|

| Field   |   | DMA_E | END_H |       | DMA_START_H |     |  |  |  |  |  |

| RESET   |   | X     |       |       |             |     |  |  |  |  |  |

| R/W     |   | R/W   |       |       |             |     |  |  |  |  |  |

| Address |   |       |       | FB2H, | FBAH        |     |  |  |  |  |  |

### Hex Address: FBB

### Table 212. DMAx Start/Current Address Low Byte Register (DMAxSTART)

| Bit     | 7 | 6          | 5 | 4 | 3 | 2 | 1 | 0 |  |  |  |

|---------|---|------------|---|---|---|---|---|---|--|--|--|

| Field   |   | DMA_START  |   |   |   |   |   |   |  |  |  |

| RESET   |   | X          |   |   |   |   |   |   |  |  |  |

| R/W     |   | R/W        |   |   |   |   |   |   |  |  |  |

| Address |   | FB3H, FBBH |   |   |   |   |   |   |  |  |  |

### Hex Address: FBC

### Table 213. DMAx End Address Low Byte Register (DMAxEND)

| Bit     | 7          | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

|---------|------------|---|---|---|---|---|---|---|

| Field   | DMA_END    |   |   |   |   |   |   |   |

| RESET   | X          |   |   |   |   |   |   |   |

| R/W     | R/W        |   |   |   |   |   |   |   |

| Address | FB4H, FBCH |   |   |   |   |   |   |   |

### Hex Address: FBD

### Table 214. DMA\_ADC Address Register (DMAA\_ADDR)

| Bit     | 7               | 6 | 5 | 4 | 3 | 2 | 1 | 0 |  |

|---------|-----------------|---|---|---|---|---|---|---|--|

| Field   | DMAA_ADDR Reser |   |   |   |   |   |   |   |  |

| RESET   | X               |   |   |   |   |   |   |   |  |

| R/W     | R/W             |   |   |   |   |   |   |   |  |

| Address | FBDH            |   |   |   |   |   |   |   |  |

| Part Number                                                 | Flash       | RAM    | I/O Lines | Interrupts | 16-Bit Timers w/PWM | 10-Bit A/D Channels | l <sup>2</sup> C | SPI | UARTs with IrDA | Description         |

|-------------------------------------------------------------|-------------|--------|-----------|------------|---------------------|---------------------|------------------|-----|-----------------|---------------------|

| Z8F482x with 48KB Flash, 10-Bit Analog-to-Digital Converter |             |        |           |            |                     |                     |                  |     |                 |                     |

| Standard Temperature                                        |             |        |           |            |                     |                     |                  |     |                 |                     |

| Z8F4821PM020SG                                              | 48KB        | 4KB    | 29        | 23         | 3                   | 8                   | 1                | 1   | 2               | PDIP 40-pin package |

| Z8F4821AN020SG                                              | 48KB        | 4KB    | 31        | 23         | 3                   | 8                   | 1                | 1   | 2               | LQFP 44-pin package |

| Z8F4821VN020SG                                              | 48 KB       | 4KB    | 31        | 23         | 3                   | 8                   | 1                | 1   | 2               | PLCC 44-pin package |

| Z8F4822AR020SG                                              | 48KB        | 4KB    | 46        | 24         | 4                   | 12                  | 1                | 1   | 2               | LQFP 64-pin package |

| Z8F4822VS020SG                                              | 48KB        | 4KB    | 46        | 24         | 4                   | 12                  | 1                | 1   | 2               | PLCC 68-pin package |

| Z8F4823FT020SG                                              | 48KB        | 4KB    | 60        | 24         | 4                   | 12                  | 1                | 1   | 2               | QFP 80-pin package  |

| Extended Temperature                                        | e: -40°C to | +105°C |           |            |                     |                     |                  |     |                 |                     |

| Z8F4821PM020EG                                              | 48 K B      | 4KB    | 29        | 23         | 3                   | 8                   | 1                | 1   | 2               | PDIP 40-pin package |

| Z8F4821AN020EG                                              | 48KB        | 4KB    | 31        | 23         | 3                   | 8                   | 1                | 1   | 2               | LQFP 44-pin package |

| Z8F4821VN020EG                                              | 48KB        | 4KB    | 31        | 23         | 3                   | 8                   | 1                | 1   | 2               | PLCC 44-pin package |

| Z8F4822AR020EG                                              | 48KB        | 4KB    | 46        | 24         | 4                   | 12                  | 1                | 1   | 2               | LQFP 64-pin package |

| Z8F4822VS020EG                                              | 48KB        | 4KB    | 46        | 24         | 4                   | 12                  | 1                | 1   | 2               | PLCC 68-pin package |

| Z8F4823FT020EG                                              | 48KB        | 4KB    | 60        | 24         | 4                   | 12                  | 1                | 1   | 2               | QFP 80-pin package  |

| Automotive/Industrial Temperature: -40°C to +125°C          |             |        |           |            |                     |                     |                  |     |                 |                     |

| Z8F4821PM020AG                                              | 48KB        | 4KB    | 29        | 23         | 3                   | 8                   | 1                | 1   | 2               | PDIP 40-pin package |

| Z8F4821AN020AG                                              | 48KB        | 4KB    | 31        | 23         | 3                   | 8                   | 1                | 1   | 2               | LQFP 44-pin package |

| Z8F4821VN020AG                                              | 48KB        | 4KB    | 31        | 23         | 3                   | 8                   | 1                | 1   | 2               | PLCC 44-pin package |

| Z8F4822AR020AG                                              | 48KB        | 4KB    | 46        | 24         | 4                   | 12                  | 1                | 1   | 2               | LQFP 64-pin package |

| Z8F4822VS020AG                                              | 48KB        | 4KB    | 46        | 24         | 4                   | 12                  | 1                | 1   | 2               | PLCC 68-pin package |

| Z8F4823FT020AG                                              | 48KB        | 4KB    | 60        | 24         | 4                   | 12                  | 1                | 1   | 2               | QFP 80-pin package  |

|                                                             |             |        |           |            |                     |                     |                  |     |                 |                     |

### Table 271. Z8 Encore! XP F64xx Series Ordering Matrix

# Index

### **Numerics**

10-bit ADC 5

# Α

absolute maximum ratings 201 AC characteristics 217 ADC 231 architecture 162 automatic power-down 164 block diagram 163 continuous conversion 165 control register 166 control register definitions 166 data high byte register 168 data low bits register 169 DMA control 166 electrical characteristics and timing 215 operation 164 single-shot conversion 164 ADCCTL register 166 ADCDH register 168 ADCDL register 169 ADCX 231 ADD 231 add - extended addressing 231 add with carry 231 add with carry - extended addressing 231 additional symbols 229 address space 19 ADDX 231 analog signals 16 analog-to-digital converter (ADC) 162 AND 234 ANDX 234 arithmetic instructions 231 assembly language programming 226 assembly language syntax 227

# В

baud rate generator, UART 99 **BCLR 232** binary number suffix 229 **BIT 232** bit 228 clear 232 manipulation instructions 232 set 232 set or clear 232 swap 232 test and jump 234 test and jump if non-zero 234 test and jump if zero 234 bit jump and test if non-zero 234 bit swap 235 block diagram 4 block transfer instructions 232 **BRK 234 BSET 232** BSWAP 232, 235 **BTJ 234** BTJNZ 234 BTJZ 234

# С

CALL procedure 234 capture mode 79 capture/compare mode 79 cc 228 CCF 233 characteristics, electrical 201 clear 233 clock phase (SPI) 117 CLR 233 COM 234 compare 79 compare - extended addressing 231 compare mode 79

SPI status (SPISTAT) 124, 265 status, I2C 143 status, SPI 124 UARTx baud rate high byte (UxBRH) 107, 259, 262 UARTx baud rate low byte (UxBRL) 107, 260, 262 UARTx Control 0 (UxCTL0) 103, 106, 258, 259, 261 UARTx control 1 (UxCTL1) 104, 259, 261 UARTx receive data (UxRXD) 100, 258, 260 UARTx status 0 (UxSTAT0) 101, 258, 260 UARTx status 1 (UxSTAT1) 102, 259, 261 UARTx transmit data (UxTXD) 100, 258, 260 watchdog timer control (WDTCTL) 85, 283 watchdog timer reload high byte (WDTH) 87, 284 watchdog timer reload low byte (WDTL) 87, 284 watchdog timer reload upper byte (WDTU) 86, 283 register file 19 register file address map 23 register pair 229 register pointer 229 reset and STOP mode characteristics 29 carry flag 232 controller 6 sources 30 **RET 234** return 234 RL 235 **RLC 235** rotate and shift instructions 235 rotate left 235 rotate left through carry 235 rotate right 235 rotate right through carry 235 RP 229 RR 229, 235 rr 229 **RRC 235**

# S

**SBC 232** SCF 232. 233 SDA and SCL (IrDA) signals 131 second opcode map after 1FH 248 serial clock 117 serial peripheral interface (SPI) 114 set carry flag 232, 233 set register pointer 233 shift right arithmetic 235 shift right logical 235 signal descriptions 15 single-shot conversion (ADC) 164 SIO 6 slave data transfer formats (I2C) 137 slave select 117 software trap 234 source operand 229 SP 229 SPI architecture 114 baud rate generator 121 baud rate high and low byte register 127 clock phase 117 configured as slave 115 control register 123 control register definitions 122 data register 122 error detection 120 interrupts 121 mode fault error 120 mode register 126 multi-master operation 119 operation 116 overrun error 120 signals 116 single master, multiple slave system 115 single master, single slave system 114 status register 124 timing, PHASE = 0.118timing, PHASE=1 119 SPI controller signals 15 SPI mode (SPIMODE) 126, 265 SPIBRH register 128, 266