Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                                                                         |

|----------------------------|---------------------------------------------------------------------------------------------------------|

| Product Status             | Discontinued at Digi-Key                                                                                |

| Core Processor             | ARM7®                                                                                                   |

| Core Size                  | 16/32-Bit                                                                                               |

| Speed                      | 72MHz                                                                                                   |

| Connectivity               | CANbus, EBI/EMI, Ethernet, I <sup>2</sup> C, Microwire, Memory Card, SPI, SSI, SSP, UART/USART, USB OTG |

| Peripherals                | Brown-out Detect/Reset, DMA, I2S, POR, PWM, WDT                                                         |

| Number of I/O              | 104                                                                                                     |

| Program Memory Size        | 512KB (512K x 8)                                                                                        |

| Program Memory Type        | FLASH                                                                                                   |

| EEPROM Size                | -                                                                                                       |

| RAM Size                   | 98K x 8                                                                                                 |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                                               |

| Data Converters            | A/D 8x10b; D/A 1x10b                                                                                    |

| Oscillator Type            | Internal                                                                                                |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                                       |

| Mounting Type              | Surface Mount                                                                                           |

| Package / Case             | 144-LQFP                                                                                                |

| Supplier Device Package    | 144-LQFP (20x20)                                                                                        |

| Purchase URL               | https://www.e-xfl.com/product-detail/nxp-semiconductors/lpc2388fbd144-551                               |

#### Fast communication chip

- 4 MHz internal RC oscillator trimmed to 1 % accuracy that can optionally be used as the system clock. When used as the CPU clock, does not allow CAN and USB to run.

- On-chip PLL allows CPU operation up to the maximum CPU rate without the need for a high frequency crystal. May be run from the main oscillator, the internal RC oscillator, or the RTC oscillator.

- Boundary scan for simplified board testing.

- Versatile pin function selections allow more possibilities for using on-chip peripheral functions.

# 3. Applications

- Industrial control

- Medical systems

- Protocol converter

- Communications

# 4. Ordering information

Table 1. Ordering information

| Type number   | Package |                                                                         |          |

|---------------|---------|-------------------------------------------------------------------------|----------|

|               | Name    | Description                                                             | Version  |

| LPC2388FBD144 | LQFP144 | plastic low profile quad flat package; 144 leads; body 20 × 20 × 1.4 mm | SOT486-1 |

## 4.1 Ordering options

Table 2. Ordering options

| Type number   | Flash | SRAM (kB) |                 |        | kB) |       | External bus                                         | Ether | USB                                    |              | SD/ | GP  |              |              | Temp                |

|---------------|-------|-----------|-----------------|--------|-----|-------|------------------------------------------------------|-------|----------------------------------------|--------------|-----|-----|--------------|--------------|---------------------|

|               | (kB)  | Local bus | Ethernet buffer | GP/USB | RTC | Total |                                                      | net   | device<br>host<br>OTG+<br>4 kB<br>FIFO | CAN channels | ММС | DMA | ADC channels | DAC channels | range               |

| LPC2388FBD144 | 512   | 64        | 16              | 16     | 2   | 98    | MiniBus: 8 data, 16 address, and 2 chip select lines | RMII  | yes                                    | 2            | yes | yes | 8            | 1            | –40 °C to<br>+85 °C |

#### Fast communication chip

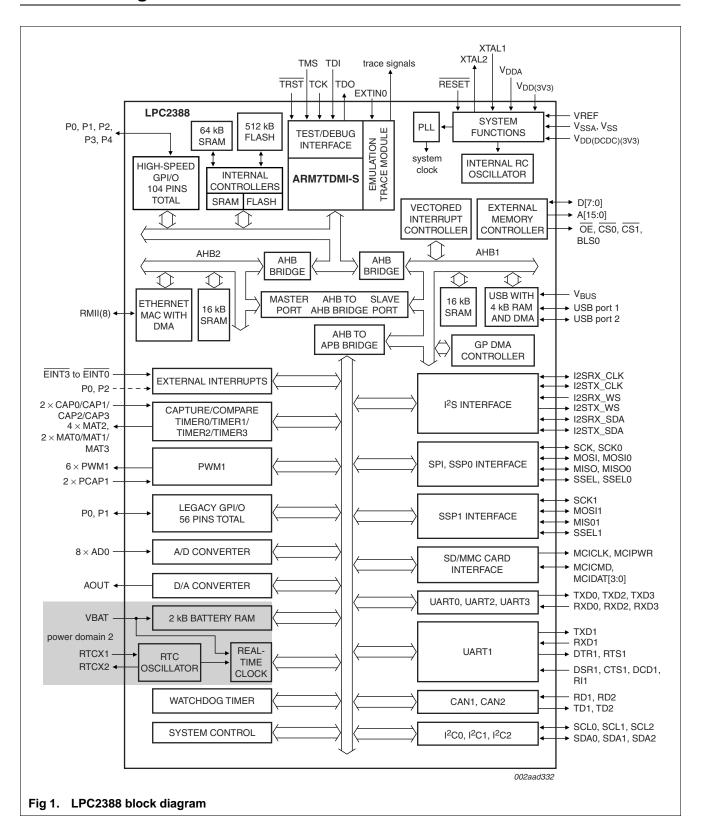

## 5. Block diagram

Table 3. Pin description ...continued

| Symbol                       | Pin           | Type | Description                                                                                                                                                                          |

|------------------------------|---------------|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| P0[14]/                      | 48[1]         | I/O  | P0[14] — General purpose digital input/output pin.                                                                                                                                   |

| USB_HSTEN2/<br>USB_CONNECT2/ |               | 0    | USB_HSTEN2 — Host Enabled status for USB port 2.                                                                                                                                     |

| SSEL1                        |               | 0    | $\mbox{USB\_CONNECT2}$ — SoftConnect control for USB port 2. Signal used to switch an external 1.5 $k\Omega$ resistor under software control. Used with the SoftConnect USB feature. |

|                              |               | I/O  | SSEL1 — Slave Select for SSP1.                                                                                                                                                       |

| P0[15]/TXD1/                 | 89 <u>[1]</u> | I/O  | P0[15] — General purpose digital input/output pin.                                                                                                                                   |

| SCK0/SCK                     |               | 0    | TXD1 — Transmitter output for UART1.                                                                                                                                                 |

|                              |               | I/O  | SCK0 — Serial clock for SSP0.                                                                                                                                                        |

|                              |               | I/O  | SCK — Serial clock for SPI.                                                                                                                                                          |

| P0[16]/RXD1/                 | 90[1]         | I/O  | P0 [16] — General purpose digital input/output pin.                                                                                                                                  |

| SSEL0/SSEL                   |               | I    | <b>RXD1</b> — Receiver input for UART1.                                                                                                                                              |

|                              |               | I/O  | SSEL0 — Slave Select for SSP0.                                                                                                                                                       |

|                              |               | I/O  | SSEL — Slave Select for SPI.                                                                                                                                                         |

| P0[17]/CTS1/                 | 87 <u>[1]</u> | I/O  | P0[17] — General purpose digital input/output pin.                                                                                                                                   |

| MISO0/MISO                   |               | I    | CTS1 — Clear to Send input for UART1.                                                                                                                                                |

|                              |               | I/O  | MISO0 — Master In Slave Out for SSP0.                                                                                                                                                |

|                              |               | I/O  | MISO — Master In Slave Out for SPI.                                                                                                                                                  |

| P0[18]/DCD1/                 | 86 <u>[1]</u> | I/O  | P0[18] — General purpose digital input/output pin.                                                                                                                                   |

| MOSI0/MOSI                   |               | 1    | DCD1 — Data Carrier Detect input for UART1.                                                                                                                                          |

|                              |               | I/O  | MOSI0 — Master Out Slave In for SSP0.                                                                                                                                                |

|                              |               | I/O  | MOSI — Master Out Slave In for SPI.                                                                                                                                                  |

| P0[19]/DSR1/                 | 85 <u>[1]</u> | I/O  | P0[19] — General purpose digital input/output pin.                                                                                                                                   |

| MCICLK/SDA1                  |               | I    | <b>DSR1</b> — Data Set Ready input for UART1.                                                                                                                                        |

|                              |               | 0    | MCICLK — Clock output line for SD/MMC interface.                                                                                                                                     |

|                              |               | I/O  | SDA1 — I <sup>2</sup> C1 data input/output (this is not an open-drain pin).                                                                                                          |

| P0[20]/DTR1/                 | 83[1]         | I/O  | P0[20] — General purpose digital input/output pin.                                                                                                                                   |

| MCICMD/SCL1                  |               | 0    | DTR1 — Data Terminal Ready output for UART1.                                                                                                                                         |

|                              |               | 1    | MCICMD — Command line for SD/MMC interface.                                                                                                                                          |

|                              |               | I/O  | SCL1 — I <sup>2</sup> C1 clock input/output (this is not an open-drain pin).                                                                                                         |

| P0[21]/RI1/                  | 82 <u>[1]</u> | I/O  | P0[21] — General purpose digital input/output pin.                                                                                                                                   |

| MCIPWR/RD1                   |               | I    | RI1 — Ring Indicator input for UART1.                                                                                                                                                |

|                              |               | 0    | MCIPWR — Power Supply Enable for external SD/MMC power supply.                                                                                                                       |

|                              |               | I    | RD1 — CAN1 receiver input.                                                                                                                                                           |

| P0[22]/RTS1/                 | 80 <u>[1]</u> | I/O  | P0[22] — General purpose digital input/output pin.                                                                                                                                   |

| MCIDAT0/TD1                  |               | 0    | RTS1 — Request to Send output for UART1.                                                                                                                                             |

|                              |               | 0    | MCIDAT0 — Data line for SD/MMC interface.                                                                                                                                            |

|                              |               | 0    | TD1 — CAN1 transmitter output.                                                                                                                                                       |

Table 3. Pin description ... continued

| Symbol                           | Pin               | Type | Description                                                                                                                                                                         |

|----------------------------------|-------------------|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| P2[2]/PWM1[3]/                   | 105 <u>[1]</u>    | I/O  | P2[2] — General purpose digital input/output pin.                                                                                                                                   |

| CTS1/<br>PIPESTAT1               |                   | 0    | PWM1[3] — Pulse Width Modulator 1, channel 3 output.                                                                                                                                |

| PIPESTALL                        |                   | I    | CTS1 — Clear to Send input for UART1.                                                                                                                                               |

|                                  |                   | 0    | PIPESTAT1 — Pipeline Status, bit 1.                                                                                                                                                 |

| P2[3]/PWM1[4]/                   | 100[1]            | I/O  | P2[3] — General purpose digital input/output pin.                                                                                                                                   |

| DCD1/<br>PIPESTAT2               |                   | 0    | PWM1[4] — Pulse Width Modulator 1, channel 4 output.                                                                                                                                |

| TILOTATE                         |                   | I    | DCD1 — Data Carrier Detect input for UART1.                                                                                                                                         |

|                                  |                   | 0    | PIPESTAT2 — Pipeline Status, bit 2.                                                                                                                                                 |

| P2[4]/PWM1[5]/                   | 99 <u>[1]</u>     | I/O  | P2[4] — General purpose digital input/output pin.                                                                                                                                   |

| DSR1/<br>TRACESYNC               |                   | 0    | PWM1[5] — Pulse Width Modulator 1, channel 5 output.                                                                                                                                |

| TRACESTING                       |                   | I    | DSR1 — Data Set Ready input for UART1.                                                                                                                                              |

|                                  |                   | 0    | TRACESYNC — Trace Synchronization.                                                                                                                                                  |

| P2[5]/PWM1[6]/                   | 97 <u>[1]</u>     | I/O  | P2[5] — General purpose digital input/output pin.                                                                                                                                   |

| DTR1/<br>TRACEPKT0               |                   | 0    | PWM1[6] — Pulse Width Modulator 1, channel 6 output.                                                                                                                                |

|                                  |                   | 0    | DTR1 — Data Terminal Ready output for UART1.                                                                                                                                        |

|                                  |                   | 0    | TRACEPKT0 — Trace Packet, bit 0.                                                                                                                                                    |

| P2[6]/PCAP1[0]/                  | 96[1]             | I/O  | P2[6] — General purpose digital input/output pin.                                                                                                                                   |

| RI1/<br>TRACEPKT1                |                   | I    | PCAP1[0] — Capture input for PWM1, channel 0.                                                                                                                                       |

| INACLINII                        |                   | I    | RI1 — Ring Indicator input for UART1.                                                                                                                                               |

|                                  |                   | 0    | TRACEPKT1 — Trace Packet, bit 1.                                                                                                                                                    |

| P2[7]/RD2/                       | 95 <u>[1]</u>     | I/O  | P2[7] — General purpose digital input/output pin.                                                                                                                                   |

| RTS1/<br>TRACEPKT2               |                   | I    | RD2 — CAN2 receiver input.                                                                                                                                                          |

| TRACEI RIZ                       |                   | 0    | RTS1 — Request to Send output for UART1.                                                                                                                                            |

|                                  |                   | 0    | TRACEPKT2 — Trace Packet, bit 2.                                                                                                                                                    |

| P2[8]/TD2/                       | 93[1]             | I/O  | P2[8] — General purpose digital input/output pin.                                                                                                                                   |

| TXD2/<br>TRACEPKT3               |                   | 0    | TD2 — CAN2 transmitter output.                                                                                                                                                      |

| TIVIOLI IVIO                     |                   | 0    | TXD2 — Transmitter output for UART2.                                                                                                                                                |

|                                  |                   | 0    | TRACEPKT3 — Trace Packet, bit 3.                                                                                                                                                    |

| P2[9]/                           | 92[1]             | I/O  | P2[9] — General purpose digital input/output pin.                                                                                                                                   |

| USB_CONNECT1/<br>RXD2/<br>EXTIN0 | /                 | 0    | <b>USB_CONNECT1</b> — USB port 1 Soft Connect control. Signal used to switch an external 1.5 k $\Omega$ resistor under the software control. Used with the SoftConnect USB feature. |

|                                  |                   | I    | RXD2 — Receiver input for UART2.                                                                                                                                                    |

|                                  |                   | I    | EXTINO — External Trigger Input.                                                                                                                                                    |

| P2[10]/EINT0                     | 76 <sup>[6]</sup> | I/O  | P2[10] — General purpose digital input/output pin.                                                                                                                                  |

|                                  |                   |      | <b>Note:</b> LOW on this pin while RESET is LOW forces on-chip boot-loader to take over control of the part after a reset.                                                          |

|                                  |                   | I    | EINT0 — External interrupt 0 input.                                                                                                                                                 |

Table 3. Pin description ... continued

| Table 3.             | Pin des      | scription .              |                                           |                                                                                                                                                                                                                                                                 |

|----------------------|--------------|--------------------------|-------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Symbol               |              | Pin                      | Type                                      | Description                                                                                                                                                                                                                                                     |

| P2[11]/EIN           | T1/          | 75 <u>[6]</u>            | I/O                                       | P2[11] — General purpose digital input/output pin.                                                                                                                                                                                                              |

| MCIDAT1/<br>I2STX_CL | K            |                          | ı                                         | EINT1 — External interrupt 1 input.                                                                                                                                                                                                                             |

|                      |              |                          | 0                                         | MCIDAT1 — Data line for SD/MMC interface.                                                                                                                                                                                                                       |

|                      |              |                          | I/O                                       | <b>I2STX_CLK</b> — Transmit Clock. It is driven by the master and received by the slave. Corresponds to the signal SCK in the $\ell$ S-bus specification.                                                                                                       |

| P2[12]/EIN           | IT2/         | 73 <u>[6]</u>            | I/O                                       | P2[12] — General purpose digital input/output pin.                                                                                                                                                                                                              |

| MCIDAT2/<br>I2STX_WS | :            |                          | 1                                         | EINT2 — External interrupt 2 input.                                                                                                                                                                                                                             |

| 12017_110            | ,            |                          | 0                                         | MCIDAT2 — Data line for SD/MMC interface.                                                                                                                                                                                                                       |

|                      |              |                          | I/O                                       | <b>I2STX_WS</b> — Transmit Word Select. It is driven by the master and received by the slave. Corresponds to the signal WS in the $PS$ -bus specification.                                                                                                      |

| P2[13]/EIN           | IT3/         | 71 <u><sup>[6]</sup></u> | I/O                                       | P2[13] — General purpose digital input/output pin.                                                                                                                                                                                                              |

| MCIDAT3/<br>I2STX_SD | Δ            |                          | 1                                         | EINT3 — External interrupt 3 input.                                                                                                                                                                                                                             |

| 1231X_3DA            |              | 0                        | MCIDAT3 — Data line for SD/MMC interface. |                                                                                                                                                                                                                                                                 |

|                      |              |                          | I/O                                       | <b>I2STX_SDA</b> — Transmit data. It is driven by the transmitter and read by the receiver. Corresponds to the signal SD in the $PS$ -bus specification.                                                                                                        |

| P3[0] to P3          | 3[31]        |                          | I/O                                       | <b>Port 3:</b> Port 3 is a 32 bit I/O port with individual direction controls for each bit. The operation of port 3 pins depends upon the pin function selected via the Pin Connect block. Pins 8 through 22, and 27 through 31 of this port are not available. |

| P3[0]/D0             |              | 137 <u>[1]</u>           | I/O                                       | P3[0] — General purpose digital input/output pin.                                                                                                                                                                                                               |

|                      |              |                          | I/O                                       | <b>D0</b> — External memory data line 0.                                                                                                                                                                                                                        |

| P3[1]/D1             |              | 140[1]                   | I/O                                       | P3[1] — General purpose digital input/output pin.                                                                                                                                                                                                               |

|                      |              |                          | I/O                                       | D1 — External memory data line 1.                                                                                                                                                                                                                               |

| P3[2]/D2             |              | 144 <u>[1]</u>           | I/O                                       | P3[2] — General purpose digital input/output pin.                                                                                                                                                                                                               |

|                      |              |                          | I/O                                       | D2 — External memory data line 2.                                                                                                                                                                                                                               |

| P3[3]/D3             |              | 2 <sup>[1]</sup>         | I/O                                       | P3[3] — General purpose digital input/output pin.                                                                                                                                                                                                               |

|                      |              |                          | I/O                                       | D3 — External memory data line 3.                                                                                                                                                                                                                               |

| P3[4]/D4             | 9 <u>[1]</u> | 9 <u>[1]</u>             | I/O                                       | P3[4] — General purpose digital input/output pin.                                                                                                                                                                                                               |

|                      |              |                          | I/O                                       | <b>D4</b> — External memory data line 4.                                                                                                                                                                                                                        |

| P3[5]/D5             |              | 12 <sup>[1]</sup>        | I/O                                       | P3[5] — General purpose digital input/output pin.                                                                                                                                                                                                               |

|                      |              |                          | I/O                                       | <b>D5</b> — External memory data line 5.                                                                                                                                                                                                                        |

| P3[6]/D6             |              | 16 <sup>[1]</sup>        | I/O                                       | P3[6] — General purpose digital input/output pin.                                                                                                                                                                                                               |

|                      |              |                          | I/O                                       | <b>D6</b> — External memory data line 6.                                                                                                                                                                                                                        |

| P3[7]/D7             |              | 19 <sup>[1]</sup>        | I/O                                       | P3[7] — General purpose digital input/output pin.                                                                                                                                                                                                               |

|                      |              |                          | I/O                                       | D7 — External memory data line 7.                                                                                                                                                                                                                               |

| P3[23]/CAI           | P0[0]/       | 45 <u>[1]</u>            | I/O                                       | P3[23] — General purpose digital input/output pin.                                                                                                                                                                                                              |

| PCAP1[0]             |              |                          | I                                         | CAP0[0] — Capture input for Timer 0, channel 0.                                                                                                                                                                                                                 |

|                      |              |                          |                                           | PCAP1[0] — Capture input for PWM1, channel 0.                                                                                                                                                                                                                   |

| P3[24]/CAI           | P0[1]/       | 40 <u>[1]</u>            | I/O                                       | P3[24] — General purpose digital input/output pin.                                                                                                                                                                                                              |

| PWM1[1]              |              |                          | I                                         | CAP0[1] — Capture input for Timer 0, channel 1.                                                                                                                                                                                                                 |

|                      |              |                          | 0                                         | PWM1[1] — Pulse Width Modulator 1, output 1.                                                                                                                                                                                                                    |

#### Fast communication chip

via the EMC, as well as the SRAM located on another AHB, if it is not being used by the USB block. However, using memory other than the Ethernet SRAM, especially off-chip memory, will slow Ethernet access to memory and increase the loading of its AHB.

The Ethernet block interfaces between an off-chip Ethernet PHY using the Reduced MII (RMII) protocol and the on-chip Media Independent Interface Management (MIIM) serial bus.

#### 7.10.1 Features

- Ethernet standards support:

- Supports 10 Mbit/s or 100 Mbit/s PHY devices including 10 Base-T, 100 Base-TX, 100 Base-FX, and 100 Base-T4.

- Fully compliant with IEEE standard 802.3.

- Fully compliant with 802.3x Full Duplex Flow Control and Half Duplex back pressure.

- Flexible transmit and receive frame options.

- Virtual Local Area Network (VLAN) frame support.

#### Memory management:

- Independent transmit and receive buffers memory mapped to shared SRAM.

- DMA managers with scatter/gather DMA and arrays of frame descriptors.

- Memory traffic optimized by buffering and pre-fetching.

#### Enhanced Ethernet features:

- Receive filtering.

- Multicast and broadcast frame support for both transmit and receive.

- Optional automatic Frame Check Sequence (FCS) insertion with Circular Redundancy Check (CRC) for transmit.

- Selectable automatic transmit frame padding.

- Over-length frame support for both transmit and receive allows any length frames.

- Promiscuous receive mode.

- Automatic collision back-off and frame retransmission.

- Includes power management by clock switching.

- Wake-on-LAN power management support allows system wake-up: using the receive filters or a magic frame detection filter.

#### Physical interface:

- Attachment of external PHY chip through standard RMII interface.

- PHY register access is available via the MIIM interface.

#### Fast communication chip

#### 7.11.3 USB OTG Controller

USB OTG (On-The-Go) is a supplement to the USB 2.0 specification that augments the capability of existing mobile devices and USB peripherals by adding host functionality for connection to USB peripherals.

The OTG Controller integrates the Host Controller, device controller, and a master-only I<sup>2</sup>C interface to implement OTG dual-role device functionality. The dedicated I<sup>2</sup>C interface controls an external OTG transceiver.

#### 7.11.3.1 Features

- Fully compliant with On-The-Go supplement to the USB 2.0 Specification, Revision

- Hardware support for Host Negotiation Protocol (HNP).

- Includes a programmable timer required for HNP and Session Request Protocol (SRP).

- Supports any OTG transceiver compliant with the OTG Transceiver Specification (CEA-2011), Rev. 1.0.

## 7.12 CAN controller and acceptance filters

The Controller Area Network (CAN) is a serial communications protocol which efficiently supports distributed real-time control with a very high level of security. Its domain of application ranges from high-speed networks to low cost multiplex wiring.

The CAN block is intended to support multiple CAN buses simultaneously, allowing the device to be used as a gateway, switch, or router among a number of CAN buses in industrial or automotive applications.

Each CAN controller has a register structure similar to the NXP SJA1000 and the PeliCAN Library block, but the 8-bit registers of those devices have been combined in 32-bit words to allow simultaneous access in the ARM environment. The main operational difference is that the recognition of received Identifiers, known in CAN terminology as Acceptance Filtering, has been removed from the CAN controllers and centralized in a global Acceptance Filter.

#### 7.12.1 Features

- Two CAN controllers and buses.

- Data rates to 1 Mbit/s on each bus.

- 32-bit register and RAM access.

- Compatible with CAN specification 2.0B, ISO 11898-1.

- Global Acceptance Filter recognizes 11-bit and 29-bit receive identifiers for all CAN buses.

- Acceptance Filter can provide FullCAN-style automatic reception for selected Standard Identifiers.

- Full CAN messages can generate interrupts.

#### Fast communication chip

- Mono and stereo audio data supported.

- The sampling frequency can range from 16 kHz to 48 kHz ((16, 22.05, 32, 44.1, 48) kHz).

- Configurable word select period in master mode (separately for I<sup>2</sup>S input and output).

- Two 8 word FIFO data buffers are provided, one for transmit and one for receive.

- Generates interrupt requests when buffer levels cross a programmable boundary.

- Two DMA requests, controlled by programmable buffer levels. These are connected to the GPDMA block.

- Controls include reset, stop and mute options separately for I<sup>2</sup>S input and I<sup>2</sup>S output.

## 7.21 General purpose 32-bit timers/external event counters

The LPC2388 includes four 32-bit Timer/Counters. The Timer/Counter is designed to count cycles of the system derived clock or an externally-supplied clock. It can optionally generate interrupts or perform other actions at specified timer values, based on four match registers. The Timer/Counter also includes four capture inputs to trap the timer value when an input signal transitions, optionally generating an interrupt.

#### 7.21.1 Features

- A 32-bit Timer/Counter with a programmable 32-bit prescaler.

- Counter or Timer operation.

- Up to four 32-bit capture channels per timer, that can take a snapshot of the timer

value when an input signal transitions. A capture event may also optionally generate

an interrupt.

- Four 32-bit match registers that allow:

- Continuous operation with optional interrupt generation on match.

- Stop timer on match with optional interrupt generation.

- Reset timer on match with optional interrupt generation.

- Up to four external outputs corresponding to match registers, with the following capabilities:

- Set LOW on match.

- Set HIGH on match.

- Toggle on match.

- Do nothing on match.

### 7.22 Pulse width modulator

The PWM is based on the standard Timer block and inherits all of its features, although only the PWM function is pinned out on the LPC2388. The Timer is designed to count cycles of the system derived clock and optionally switch pins, generate interrupts or perform other actions when specified timer values occur, based on seven match registers. The PWM function is in addition to these features, and is based on match register events.

#### Fast communication chip

The ability to separately control rising and falling edge locations allows the PWM to be used for more applications. For instance, multi-phase motor control typically requires three non-overlapping PWM outputs with individual control of all three pulse widths and positions.

Two match registers can be used to provide a single edge controlled PWM output. One match register (PWMMR0) controls the PWM cycle rate, by resetting the count upon match. The other match register controls the PWM edge position. Additional single edge controlled PWM outputs require only one match register each, since the repetition rate is the same for all PWM outputs. Multiple single edge controlled PWM outputs will all have a rising edge at the beginning of each PWM cycle, when an PWMMR0 match occurs.

Three match registers can be used to provide a PWM output with both edges controlled. Again, the PWMMR0 match register controls the PWM cycle rate. The other match registers control the two PWM edge positions. Additional double edge controlled PWM outputs require only two match registers each, since the repetition rate is the same for all PWM outputs.

With double edge controlled PWM outputs, specific match registers control the rising and falling edge of the output. This allows both positive going PWM pulses (when the rising edge occurs prior to the falling edge), and negative going PWM pulses (when the falling edge occurs prior to the rising edge).

#### **7.22.1 Features**

- LPC2388 has one PWM block with Counter or Timer operation (may use the peripheral clock or one of the capture inputs as the clock source).

- Seven match registers allow up to 6 single edge controlled or 3 double edge controlled PWM outputs, or a mix of both types. The match registers also allow:

- Continuous operation with optional interrupt generation on match.

- Stop timer on match with optional interrupt generation.

- Reset timer on match with optional interrupt generation.

- Supports single edge controlled and/or double edge controlled PWM outputs. Single

edge controlled PWM outputs all go high at the beginning of each cycle unless the

output is a constant low. Double edge controlled PWM outputs can have either edge

occur at any position within a cycle. This allows for both positive going and negative

going pulses.

- Pulse period and width can be any number of timer counts. This allows complete

flexibility in the trade-off between resolution and repetition rate. All PWM outputs will

occur at the same repetition rate.

- Double edge controlled PWM outputs can be programmed to be either positive going or negative going pulses.

- Match register updates are synchronized with pulse outputs to prevent generation of erroneous pulses. Software must 'release' new match values before they can become effective.

- May be used as a standard timer if the PWM mode is not enabled.

- A 32-bit Timer/Counter with a programmable 32-bit Prescaler.

#### Fast communication chip

### 7.23 Watchdog timer

The purpose of the watchdog is to reset the microcontroller within a reasonable amount of time if it enters an erroneous state. When enabled, the watchdog will generate a system reset if the user program fails to 'feed' (or reload) the watchdog within a predetermined amount of time.

#### 7.23.1 Features

- Internally resets chip if not periodically reloaded.

- Debug mode.

- Enabled by software but requires a hardware reset or a watchdog reset/interrupt to be disabled.

- Incorrect/Incomplete feed sequence causes reset/interrupt if enabled.

- Flag to indicate watchdog reset.

- Programmable 32-bit timer with internal prescaler.

- Selectable time period from ( $T_{cy(WDCLK)} \times 256 \times 4$ ) to ( $T_{cy(WDCLK)} \times 2^{32} \times 4$ ) in multiples of  $T_{cy(WDCLK)} \times 4$ .

- The Watchdog Clock (WDCLK) source can be selected from the RTC clock, the

Internal RC oscillator (IRC), or the APB peripheral clock. This gives a wide range of

potential timing choices of Watchdog operation under different power reduction

conditions. It also provides the ability to run the WDT from an entirely internal source

that is not dependent on an external crystal and its associated components and

wiring, for increased reliability.

### 7.24 RTC and battery RAM

The RTC is a set of counters for measuring time when system power is on, and optionally when it is off. It uses little power in Power-down mode. On the LPC2388, the RTC can be clocked by a separate 32.768 kHz oscillator or by a programmable prescale divider based on the APB clock. Also, the RTC is powered by its own power supply pin, VBAT, which can be connected to a battery or to the same 3.3 V supply used by the rest of the device.

The VBAT pin supplies power only to the RTC and the Battery RAM. These two functions require a minimum of power to operate, which can be supplied by an external battery. When the CPU and the rest of chip functions are stopped and power removed, the RTC can supply an alarm output that can be used by external hardware to restore chip power and resume operation.

#### 7.24.1 Features

- Measures the passage of time to maintain a calendar and clock.

- Ultra low power design to support battery powered systems.

- Provides Seconds, Minutes, Hours, Day of Month, Month, Year, Day of Week, and Day of Year.

- Dedicated 32 kHz oscillator or programmable prescaler from APB clock.

- Dedicated power supply pin can be connected to a battery or to the main 3.3 V.

#### Fast communication chip

- An alarm output pin is included to assist in waking up from Power-down mode, or when the chip has had power removed to all functions except the RTC and Battery RAM.

- Periodic interrupts can be generated from increments of any field of the time registers, and selected fractional second values.

- 2 kB data SRAM powered by VBAT.

- RTC and Battery RAM power supply is isolated from the rest of the chip.

### 7.25 Clocking and power control

### 7.25.1 Crystal oscillators

The LPC2388 includes three independent oscillators. These are the Main Oscillator, the Internal RC oscillator, and the RTC oscillator. Each oscillator can be used for more than one purpose as required in a particular application. Any of the three clock sources can be chosen by software to drive the PLL and ultimately the CPU.

Following reset, the LPC2388 will operate from the Internal RC oscillator until switched by software. This allows systems to operate without any external crystal and the bootloader code to operate at a known frequency.

#### 7.25.1.1 Internal RC oscillator

The IRC may be used as the clock source for the WDT, and/or as the clock that drives the PLL and subsequently the CPU. The nominal IRC frequency is 4 MHz. The IRC is trimmed to 1 % accuracy.

Upon power-up or any chip reset, the LPC2388 uses the IRC as the clock source. Software may later switch to one of the other available clock sources.

#### 7.25.1.2 Main oscillator

The main oscillator can be used as the clock source for the CPU, with or without using the PLL. The main oscillator operates at frequencies of 1 MHz to 24 MHz. This frequency can be boosted to a higher frequency, up to the maximum CPU operating frequency, by the PLL. The clock selected as the PLL input is PLLCLKIN. The ARM processor clock frequency is referred to as CCLK elsewhere in this document. The frequencies of PLLCLKIN and CCLK are the same value unless the PLL is active and connected. The clock frequency for each peripheral can be selected individually and is referred to as PCLK. Refer to Section 7.25.2 for additional information.

#### 7.25.1.3 RTC oscillator

The RTC oscillator can be used as the clock source for the RTC and/or the WDT. Also, the RTC oscillator can be used to drive the PLL and the CPU.

#### 7.25.2 PLL

The PLL accepts an input clock frequency in the range of 32 kHz to 50 MHz. The input frequency is multiplied up to a high frequency, then divided down to provide the actual clock used by the CPU and the USB block.

The PLL input, in the range of 32 kHz to 50 MHz, may initially be divided down by a value 'N', which may be in the range of 1 to 256. This input division provides a wide range of output frequencies from the same input frequency.

#### Fast communication chip

## 8. Limiting values

Table 4. Limiting values

In accordance with the Absolute Maximum Rating System (IEC 60134).[1]

| Symbol                     | Parameter                                 | Conditions                                                                                            | Min             | Max                        | Unit |

|----------------------------|-------------------------------------------|-------------------------------------------------------------------------------------------------------|-----------------|----------------------------|------|

| V <sub>DD(3V3)</sub>       | supply voltage (3.3 V)                    | core and external rail                                                                                | 3.0             | 3.6                        | V    |

| V <sub>DD(DCDC)(3V3)</sub> | DC-to-DC converter supply voltage (3.3 V) |                                                                                                       | 3.0             | 3.6                        | V    |

| $V_{DDA}$                  | analog 3.3 V pad supply voltage           |                                                                                                       | -0.5            | +4.6                       | V    |

| V <sub>i(VBAT)</sub>       | input voltage on pin VBAT                 | for the RTC                                                                                           | -0.5            | +4.6                       | V    |

| V <sub>i(VREF)</sub>       | input voltage on pin VREF                 |                                                                                                       | -0.5            | +4.6                       | V    |

| V <sub>IA</sub>            | analog input voltage                      | on ADC related pins                                                                                   | -0.5            | +5.1                       | V    |

| Vı                         | input voltage                             | 5 V tolerant I/O<br>pins; only valid<br>when the V <sub>DD(3V3)</sub><br>supply voltage is<br>present | 2 –0.5          | +6.0                       | V    |

|                            |                                           | other I/O pins                                                                                        | [2][3] -0.5     | V <sub>DD(3V3)</sub> + 0.5 | V    |

| I <sub>DD</sub>            | supply current                            | per supply pin                                                                                        | <u>[4]</u> _    | 100                        | mA   |

| I <sub>SS</sub>            | ground current                            | per ground pin                                                                                        | <u>[4]</u> _    | 100                        | mA   |

| T <sub>stg</sub>           | storage temperature                       |                                                                                                       | [ <u>5]</u> –65 | +150                       | °C   |

| P <sub>tot(pack)</sub>     | total power dissipation (per package)     | based on package<br>heat transfer, not<br>device power<br>consumption                                 | -               | 1.5                        | W    |

| V <sub>esd</sub>           | electrostatic discharge voltage           | human body<br>model; all pins                                                                         | [6] -2000       | +2000                      | V    |

<sup>[1]</sup> The following applies to the Limiting values:

- a) This product includes circuitry specifically designed for the protection of its internal devices from the damaging effects of excessive static charge. Nonetheless, it is suggested that conventional precautions be taken to avoid applying greater than the rated maximum.

- b) Parameters are valid over operating temperature range unless otherwise specified. All voltages are with respect to V<sub>SS</sub> unless otherwise noted.

- [2] Including voltage on outputs in 3-state mode.

- [3] Not to exceed 4.6 V.

- [4] The peak current is limited to 25 times the corresponding maximum current.

- [5] Dependent on package type.

- [6] Human body model: equivalent to discharging a 100 pF capacitor through a 1.5  $k\Omega$  series resistor.

Fast communication chip

# 11. Application information

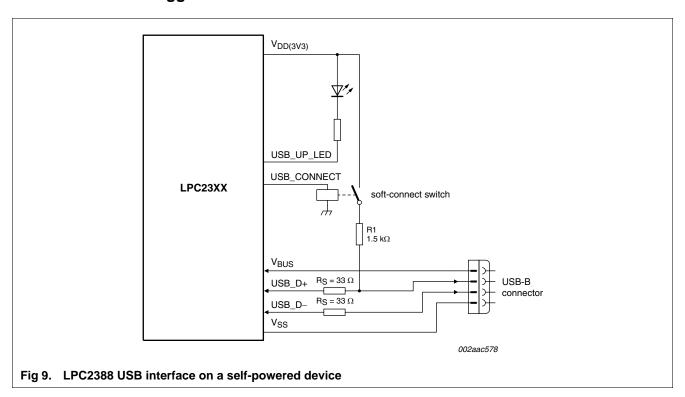

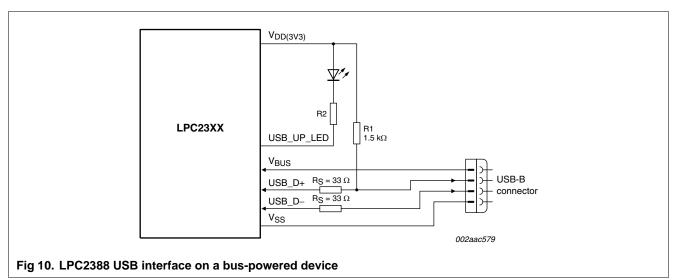

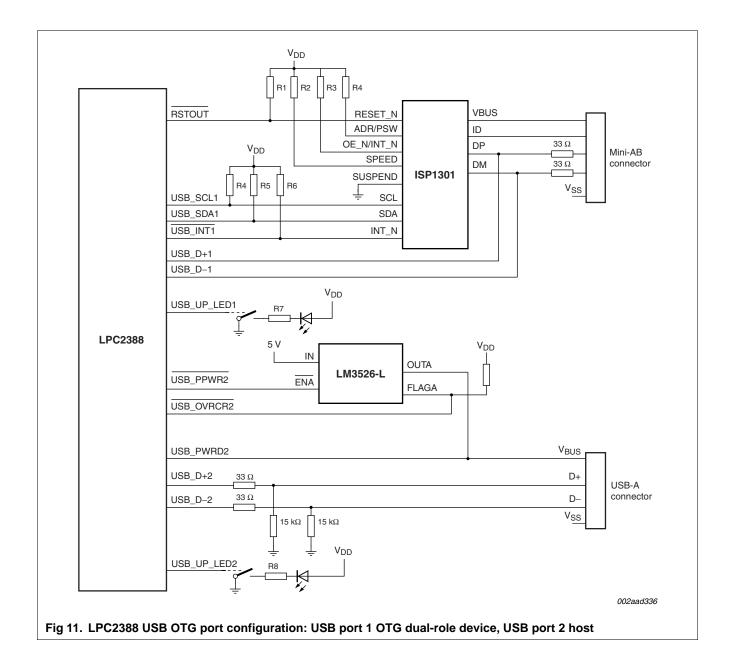

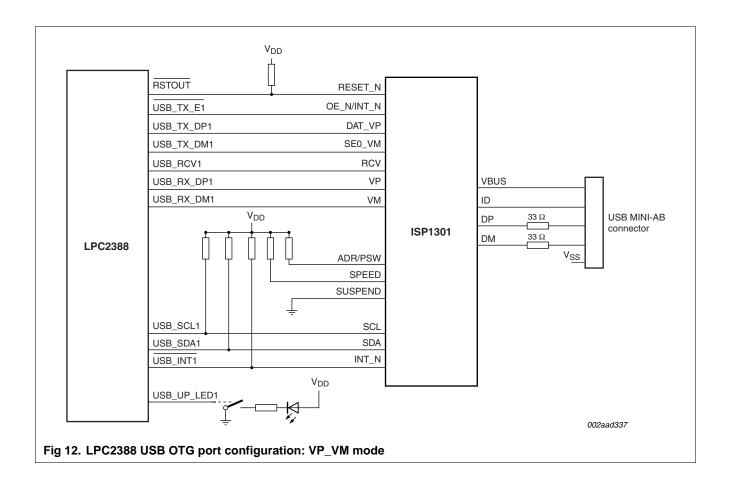

## 11.1 Suggested USB interface solutions

## Fast communication chip

## 13. Abbreviations

Table 9. Acronym list

| Table 9. | Acronym list                                |

|----------|---------------------------------------------|

| Acronym  | Description                                 |

| ADC      | Analog-to-Digital Converter                 |

| AHB      | Advanced High-performance Bus               |

| AMBA     | Advanced Microcontroller Bus Architecture   |

| APB      | Advanced Peripheral Bus                     |

| BLS      | Byte Lane Select                            |

| BOD      | BrownOut Detection                          |

| CAN      | Controller Area Network                     |

| CTS      | Clear To Send                               |

| DAC      | Digital-to-Analog Converter                 |

| DCC      | Debug Communication Channel                 |

| DMA      | Direct Memory Access                        |

| DSP      | Digital Signal Processing                   |

| EOP      | End Of Packet                               |

| ETM      | Embedded Trace Macrocell                    |

| GPIO     | General Purpose Input/Output                |

| IrDA     | Infrared Data Association                   |

| JTAG     | Joint Test Action Group                     |

| MII      | Media Independent Interface                 |

| PHY      | Physical Layer                              |

| PLL      | Phase-Locked Loop                           |

| PWM      | Pulse Width Modulator                       |

| RMII     | Reduced Media Independent Interface         |

| RTS      | Request To Send                             |

| SE0      | Single Ended Zero                           |

| SPI      | Serial Peripheral Interface                 |

| SSI      | Synchronous Serial Interface                |

| SSP      | Synchronous Serial Port                     |

| TTL      | Transistor-Transistor Logic                 |

| UART     | Universal Asynchronous Receiver/Transmitter |

| USB      | Universal Serial Bus                        |

|          |                                             |

#### Fast communication chip

## 15. Legal information

#### 15.1 Data sheet status

| Document status[1][2]          | Product status[3] | Definition                                                                            |

|--------------------------------|-------------------|---------------------------------------------------------------------------------------|

| Objective [short] data sheet   | Development       | This document contains data from the objective specification for product development. |

| Preliminary [short] data sheet | Qualification     | This document contains data from the preliminary specification.                       |

| Product [short] data sheet     | Production        | This document contains the product specification.                                     |

- [1] Please consult the most recently issued document before initiating or completing a design.

- [2] The term 'short data sheet' is explained in section "Definitions".

- [3] The product status of device(s) described in this document may have changed since this document was published and may differ in case of multiple devices. The latest product status information is available on the Internet at URL <a href="http://www.nxp.com">http://www.nxp.com</a>.

#### 15.2 Definitions

Draft — The document is a draft version only. The content is still under internal review and subject to formal approval, which may result in modifications or additions. NXP Semiconductors does not give any representations or warranties as to the accuracy or completeness of information included herein and shall have no liability for the consequences of use of such information.

Short data sheet — A short data sheet is an extract from a full data sheet with the same product type number(s) and title. A short data sheet is intended for quick reference only and should not be relied upon to contain detailed and full information. For detailed and full information see the relevant full data sheet, which is available on request via the local NXP Semiconductors sales office. In case of any inconsistency or conflict with the short data sheet, the full data sheet shall prevail.

#### 15.3 Disclaimers

**General** — Information in this document is believed to be accurate and reliable. However, NXP Semiconductors does not give any representations or warranties, expressed or implied, as to the accuracy or completeness of such information and shall have no liability for the consequences of use of such information.

Right to make changes — NXP Semiconductors reserves the right to make changes to information published in this document, including without limitation specifications and product descriptions, at any time and without notice. This document supersedes and replaces all information supplied prior to the publication hereof.

Suitability for use — NXP Semiconductors products are not designed, authorized or warranted to be suitable for use in medical, military, aircraft, space or life support equipment, nor in applications where failure or malfunction of a NXP Semiconductors product can reasonably be expected to result in personal injury, death or severe property or environmental damage.

NXP Semiconductors accepts no liability for inclusion and/or use of NXP Semiconductors products in such equipment or applications and therefore such inclusion and/or use is at the customer's own risk.

**Applications** — Applications that are described herein for any of these products are for illustrative purposes only. NXP Semiconductors makes no representation or warranty that such applications will be suitable for the specified use without further testing or modification.

Limiting values — Stress above one or more limiting values (as defined in the Absolute Maximum Ratings System of IEC 60134) may cause permanent damage to the device. Limiting values are stress ratings only and operation of the device at these or any other conditions above those given in the Characteristics sections of this document is not implied. Exposure to limiting values for extended periods may affect device reliability.

Terms and conditions of sale — NXP Semiconductors products are sold subject to the general terms and conditions of commercial sale, as published at <a href="http://www.nxp.com/profile/terms">http://www.nxp.com/profile/terms</a>, including those pertaining to warranty, intellectual property rights infringement and limitation of liability, unless explicitly otherwise agreed to in writing by NXP Semiconductors. In case of any inconsistency or conflict between information in this document and such terms and conditions, the latter will prevail.

No offer to sell or license — Nothing in this document may be interpreted or construed as an offer to sell products that is open for acceptance or the grant, conveyance or implication of any license under any copyrights, patents or other industrial or intellectual property rights.

#### 15.4 Trademarks

Notice: All referenced brands, product names, service names and trademarks are the property of their respective owners.

I<sup>2</sup>C-bus — logo is a trademark of NXP B.V.

SoftConnect — is a trademark of NXP B.V.

GoodLink — is a trademark of NXP B.V.

### 16. Contact information

For additional information, please visit: http://www.nxp.com

For sales office addresses, send an email to: salesaddresses@nxp.com

## Fast communication chip

## 17. Contents

| 1              | General description                   | . 1 | 7.19.1               | Features                                     | 27 |

|----------------|---------------------------------------|-----|----------------------|----------------------------------------------|----|

| 2              | Features                              | . 1 | 7.20                 | I <sup>2</sup> S-bus serial I/O controllers  | 27 |

| 3              | Applications                          |     | 7.20.1               | Features                                     | 27 |

| 4              | Ordering information                  |     | 7.21                 | General purpose 32-bit timers/external event |    |

| <b>4</b> .1    | _                                     |     |                      | counters                                     |    |

|                | Ordering options                      |     | 7.21.1               | Features                                     | 28 |

| 5              | Block diagram                         |     | 7.22                 | Pulse width modulator                        | 28 |

| 6              | Pinning information                   | . 5 | 7.22.1               | Features                                     |    |

| 6.1            | Pinning                               |     | 7.23                 | Watchdog timer                               |    |

| 6.2            | Pin description                       | . 5 | 7.23.1               | Features                                     |    |

| 7              | Functional description                | 15  | 7.24                 |                                              |    |

| 7.1            | Architectural overview                | 15  | 7.24.1               | Features                                     |    |

| 7.2            | On-chip flash programming memory      | 16  | 7.25                 | Clocking and power control                   |    |

| 7.3            | On-chip SRAM                          |     | 7.25.1               | Crystal oscillators                          |    |

| 7.4            | Memory map                            | 17  | 7.25.1.1             |                                              |    |

| 7.5            | Interrupt controller                  |     | 7.25.1.2             |                                              |    |

| 7.5.1          | Interrupt sources                     | 19  | 7.25.1.3             |                                              |    |

| 7.6            | Pin connect block                     | 19  | 7.25.2               | PLL                                          |    |

| 7.7            | External memory controller            | 19  | 7.25.3               | Wake-up timer                                |    |

| 7.7.1          | Features                              | 19  | 7.25.4               | Power control                                |    |

| 7.8            | General purpose DMA controller        | 20  | 7.25.4.1             |                                              |    |

| 7.8.1          | Features                              | 20  | 7.25.4.2             |                                              |    |

| 7.9            | Fast general purpose parallel I/O     | 21  | 7.25.4.3<br>7.25.4.4 |                                              |    |

| 7.9.1          | Features                              | 21  |                      |                                              |    |

| 7.10           | Ethernet                              | 21  | 7.26                 | System control                               |    |

| 7.10.1         | Features                              |     | 7.26.1<br>7.26.2     |                                              |    |

| 7.11           | USB interface                         |     | 7.26.2               |                                              | -  |

| 7.11.1         | USB device controller                 |     | 7.26.3               | , ,                                          |    |

| 7.11.1.1       |                                       |     | 7.26.4               |                                              |    |

| 7.11.2         | USB Host Controller                   |     | 7.26.6               | External interrupt inputs                    |    |

| 7.11.2.1       |                                       |     | 7.20.0               | · · · · · ·                                  |    |

| 7.11.3         | USB OTG Controller                    |     | 7.27<br>7.27.1       | Emulation and debugging                      |    |

| 7.11.3.1       |                                       |     | 7.27.1               | Embedded trace                               |    |

| 7.12           | CAN controller and acceptance filters |     | 7.27.3               | RealMonitor                                  |    |

| 7.12.1         | Features                              |     | _                    |                                              |    |

| 7.13           | 10-bit ADC                            |     | 8                    | Limiting values                              |    |

| 7.13.1         | Features                              |     | 9                    | Static characteristics                       |    |

| 7.14           | 10-bit DAC                            |     | 10                   | Dynamic characteristics                      | 45 |

| 7.14.1         | Features                              |     | 10.1                 | Timing                                       | 46 |

| 7.15           | UARTs                                 |     | 11                   | Application information                      | 47 |

| 7.15.1         | Features                              |     | 11.1                 | Suggested USB interface solutions            |    |

| 7.16           | SPI serial I/O controller             |     | 12                   | Package outline                              |    |

| 7.16.1         | Features                              |     |                      | _                                            |    |

| 7.17           | SSP serial I/O controller             |     | 13                   | Abbreviations                                |    |

| 7.17.1         | Features                              |     | 14                   | Revision history                             |    |

| 7.18           | SD/MMC card interface                 |     | 15                   | Legal information                            |    |

| 7.18.1<br>7.19 | Features                              |     | 15.1                 | Data sheet status                            | 55 |

| / 19           | I=C=OOS SEDALIZO CONHONEIS            | //  |                      |                                              |    |

continued >>

## Fast communication chip

| 15.2 | Definitions 55         |

|------|------------------------|

| 15.3 | Disclaimers            |

| 15.4 | Trademarks             |

| 16   | Contact information 55 |

| 17   | Contents 56            |

Please be aware that important notices concerning this document and the product(s) described herein, have been included in section 'Legal information'.

© NXP B.V. 2007.

All rights reserved.

PHILIDS

founded by

For more information, please visit: http://www.nxp.com For sales office addresses, please send an email to: salesaddresses@nxp.com

Date of release: 23 October 2007

Document identifier: LPC2388\_0