## E·XFL

Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                  |

|----------------------------|-------------------------------------------------------------------------|

| Core Processor             | PIC                                                                     |

| Core Size                  | 8-Bit                                                                   |

| Speed                      | 20MHz                                                                   |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                                       |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                   |

| Number of I/O              | 22                                                                      |

| Program Memory Size        | 7KB (4K x 14)                                                           |

| Program Memory Type        | FLASH                                                                   |

| EEPROM Size                |                                                                         |

| RAM Size                   | 192 x 8                                                                 |

| Voltage - Supply (Vcc/Vdd) | 4V ~ 5.5V                                                               |

| Data Converters            | A/D 5x8b                                                                |

| Oscillator Type            | External                                                                |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                      |

| Mounting Type              | Surface Mount                                                           |

| Package / Case             | 28-VQFN Exposed Pad                                                     |

| Supplier Device Package    | 28-QFN (6x6)                                                            |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16f73-e-ml |

|                            |                                                                         |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

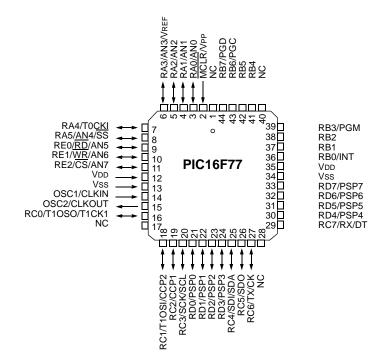

#### **Pin Diagrams (Continued)**

#### 2.2.2 SPECIAL FUNCTION REGISTERS

The Special Function Registers are registers used by the CPU and peripheral modules for controlling the desired operation of the device. These registers are implemented as static RAM. A list of these registers is given in Table 2-1. The Special Function Registers can be classified into two sets: core (CPU) and peripheral. Those registers associated with the core functions are described in detail in this section. Those related to the operation of the peripheral features are described in detail in the peripheral feature section.

#### TABLE 2-1: SPECIAL FUNCTION REGISTER SUMMARY

| Address                   | Name             | Bit 7                | Bit 6          | Bit 5          | Bit 4           | Bit 3         | Bit 2         | Bit 1         | Bit 0        | Value on:<br>POR,<br>BOR | Details<br>on page |

|---------------------------|------------------|----------------------|----------------|----------------|-----------------|---------------|---------------|---------------|--------------|--------------------------|--------------------|

| Bank 0                    |                  |                      |                |                |                 |               |               |               |              |                          |                    |

| 00h <sup>(4)</sup>        | INDF             | Addressing           | this location  | n uses conte   | ents of FSR to  | address data  | a memory (r   | not a physica | al register) | 0000 0000                | 27, 96             |

| 01h                       | TMR0             | Timer0 Mod           | lule Registe   | er             |                 |               |               |               |              | xxxx xxxx                | 45, 96             |

| 02h <sup>(4)</sup>        | PCL              | Program Co           | ounter (PC)    | Least Signif   | icant Byte      |               |               |               |              | 0000 0000                | 26, 96             |

| 03h <sup>(4)</sup>        | STATUS           | IRP                  | RP1            | RP0            | TO              | PD            | Z             | DC            | С            | 0001 1xxx                | 19, 96             |

| 04h <sup>(4)</sup>        | FSR              | Indirect Dat         | a Memory A     | Address Poir   | nter            |               |               |               |              | XXXX XXXX                | 27, 96             |

| 05h                       | PORTA            |                      |                | PORTA Dat      | ta Latch when   | written: POF  | RTA pins wh   | en read       |              | 0x 0000                  | 32, 96             |

| 06h                       | PORTB            | PORTB Dat            | a Latch wh     | en written: F  | ORTB pins w     | hen read      |               |               |              | xxxx xxxx                | 34, 96             |

| 07h                       | PORTC            | PORTC Dat            | ta Latch wh    | en written: F  | PORTC pins w    | hen read      |               |               |              | XXXX XXXX                | 35, 96             |

| 08h <sup>(5)</sup>        | PORTD            | PORTD Dat            | ta Latch wh    | en written: F  | PORTD pins w    | hen read      |               |               |              | XXXX XXXX                | 36, 96             |

| 09h <sup>(5)</sup>        | PORTE            |                      |                |                |                 |               | RE2           | RE1           | RE0          | xxx                      | 39, 96             |

| 0Ah <sup>(1,4)</sup>      | PCLATH           |                      |                |                | Write Buffer    | for the upper | 5 bits of the | Program C     | ounter       | 0 0000                   | 26, 96             |

| 0Bh <b><sup>(4)</sup></b> | INTCON           | GIE                  | PEIE           | TMR0IE         | INTE            | RBIE          | TMR0IF        | INTF          | RBIF         | 0000 000x                | 21, 96             |

| 0Ch                       | PIR1             | PSPIF <sup>(3)</sup> | ADIF           | RCIF           | TXIF            | SSPIF         | CCP1IF        | TMR2IF        | TMR1IF       | 0000 0000                | 23, 96             |

| 0Dh                       | PIR2             |                      |                |                |                 |               |               |               | CCP2IF       | 0                        | 24, 96             |

| 0Eh                       | TMR1L            | Holding Reg          | gister for the | e Least Sign   | ificant Byte of | the 16-bit TM | /IR1 Registe  | er            |              | XXXX XXXX                | 50, 96             |

| 0Fh                       | TMR1H            | Holding Reg          | gister for the | e Most Signi   | ficant Byte of  | the 16-bit TM | IR1 Registe   | r             |              | XXXX XXXX                | 50, 96             |

| 10h                       | T1CON            |                      |                | T1CKPS1        | T1CKPS0         | T1OSCEN       | T1SYNC        | TMR1CS        | TMR10N       | 00 0000                  | 47, 96             |

| 11h                       | TMR2             | Timer2 Mod           | lule Registe   | er             |                 |               |               |               |              | 0000 0000                | 52, 96             |

| 12h                       | T2CON            |                      |                | TOUTPS2        | TOUTPS          | TOUTPS0       | TMR2ON        | T2CKPS1       | T2CKPS0      | -000 0000                | 52, 96             |

| 13h                       | SSPBUF           |                      |                |                | Suffer/Transmi  | 0             |               |               |              | XXXX XXXX                | 64, 68, 96         |

| 14h                       | SSPCON           | WCOL                 | SSPOV          | SSPEN          | CKP             | SSPM3         | SSPM2         | SSPM1         | SSPM0        | 0000 0000                | 61,96              |

| 15h                       | CCPR1L           | •                    | •              | M Register1    | , ,             |               |               |               |              | XXXX XXXX                | 56, 96             |

| 16h                       | CCPR1H           | Capture/Co           | mpare/PWI      | M Register1    | ,               |               |               |               |              | XXXX XXXX                | 56, 96             |

| 17h                       | CCP1CON          | 00511                | 5.44           | CCP1X          | CCP1Y           | CCP1M3        | CCP1M2        | CCP1M1        | CCP1M0       | 00 0000                  | 54, 96             |

| 18h                       | RCSTA            | SPEN                 | RX9            | SREN           | CREN            |               | FERR          | OERR          | RX9D         | 0000 -00x                | 70, 96             |

| 19h                       | TXREG            | USART Tra            |                | 0              |                 |               |               |               |              | 0000 0000                | 74, 96             |

| 1Ah<br>1Ph                | RCREG<br>CCPR2L  | USART Red            |                | •              |                 |               |               |               |              | 0000 0000                | 76, 96             |

| 1Bh<br>1Ch                | CCPR2L<br>CCPR2H | Capture/Co           | •              | VI Register2   | . ,             |               |               |               |              | XXXX XXXX                | 58, 96             |

| 1Dh                       | CCPR2H<br>C1Dxx5 | Capture/CO           | inpare/FWI     | vi ivegistel z |                 |               |               |               |              | XXXX XXXX                | 58, 96             |

|                           | -                |                      |                |                |                 |               |               |               |              |                          |                    |

#### 2.2.2.3 INTCON Register

The INTCON register is a readable and writable register, which contains various enable and flag bits for the TMR0 register overflow, RB Port change and External RB0/INT pin interrupts.

# **Note:** Interrupt flag bits are set when an interrupt condition occurs, regardless of the state of its corresponding enable bit or the global enable bit, GIE (INTCON<7>). User software should ensure the appropriate interrupt flag bits are clear prior to enabling an interrupt.

#### REGISTER 2-3: INTCON REGISTER (ADDRESS 0Bh, 8Bh, 10Bh, 18Bh)

|       | R/W-0                                                              | R/W-0          | R/W-0                          | R/W-0       | R/W-0         | R/W-0         | R/W-0          | R/W-x     |

|-------|--------------------------------------------------------------------|----------------|--------------------------------|-------------|---------------|---------------|----------------|-----------|

|       | GIE                                                                | PEIE           | TMR0IE                         | INTE        | RBIE          | TMR0IF        | INTF           | RBIF      |

|       | bit 7                                                              |                |                                |             |               |               |                | bit 0     |

|       |                                                                    |                |                                |             |               |               |                |           |

| bit 7 |                                                                    | al Interrupt E |                                |             |               |               |                |           |

|       | 1 = Enables all unmasked interrupts<br>0 = Disables all interrupts |                |                                |             |               |               |                |           |

| bit 6 |                                                                    |                | rupt Enable k                  | hit         |               |               |                |           |

| DIT U |                                                                    | •              | ked peripher                   |             |               |               |                |           |

|       |                                                                    |                | eral interrup                  |             |               |               |                |           |

| bit 5 | TMROIE: T                                                          | MR0 Overfl     | ow Interrupt                   | Enable bit  |               |               |                |           |

|       | 1 = Enable                                                         | es the TMRC    | ) interrupt                    |             |               |               |                |           |

|       | 0 = Disable                                                        | es the TMR     | 0 interrupt                    |             |               |               |                |           |

| bit 4 |                                                                    |                | al Interrupt E                 |             |               |               |                |           |

|       |                                                                    |                | NT external                    | •           |               |               |                |           |

|       |                                                                    |                | INT external                   | •           |               |               |                |           |

| bit 3 |                                                                    | •              | e Interrupt E                  |             |               |               |                |           |

|       |                                                                    |                | ort change in<br>ort change ir |             |               |               |                |           |

| bit 2 |                                                                    | •              | ow Interrupt                   |             |               |               |                |           |

| SR 2  |                                                                    |                | overflowed                     | -           | eared in soft | ware)         |                |           |

|       |                                                                    | •              | not overflow                   | •           |               |               |                |           |

| bit 1 | INTF: RB0                                                          | /INT Extern    | al Interrupt F                 | lag bit     |               |               |                |           |

|       | 1 = The RE                                                         | B0/INT exte    | rnal interrupt                 | occurred (n | nust be clea  | red in softwa | are)           |           |

|       | 0 = The RI                                                         | B0/INT exte    | rnal interrupt                 | did not occ | ur            |               |                |           |

| bit 0 |                                                                    |                | e Interrupt Fl                 |             |               |               |                |           |

|       |                                                                    |                | will continue<br>g bit RBIF to |             |               | ding PORTE    | 3 will end the | emismatch |

|       |                                                                    |                | RB7:RB4 pi                     |             |               | he cleared i  | in software)   |           |

|       |                                                                    |                | RB4 pins hav                   |             |               |               | in soltware)   |           |

|       |                                                                    |                | •                              | ũ           |               |               |                |           |

|       | Legend:                                                            |                |                                |             |               |               |                |           |

|       |                                                                    |                |                                |             |               |               |                |           |

| Legend:                  |                  |                    |                    |

|--------------------------|------------------|--------------------|--------------------|

| R = Readable bit         | W = Writable bit | U = Unimplemented  | bit, read as 0     |

| - n = Value at POR reset | 1 = Bit is set   | 0 = Bit is cleared | x = Bit is unknown |

| U-0      | U-0 | U-0       | U-0                              | U-0        | U-0      | U-0       | R/P-1        | U-0    | R/P-1    | R/P-1        | R/P-1 | R/P-1 | R/P-1 |

|----------|-----|-----------|----------------------------------|------------|----------|-----------|--------------|--------|----------|--------------|-------|-------|-------|

|          | _   | _         |                                  | —          | _        | _         | BOREN        | _      | CP0      | PWRTEN       | WDTEN | FOSC1 | FOSC0 |

| bit13    |     |           |                                  |            |          |           |              |        |          |              |       |       | bit0  |

|          |     |           |                                  |            |          |           |              |        |          |              |       |       |       |

| bit 13-7 |     | •         |                                  | I: Read    |          |           |              |        |          |              |       |       |       |

| bit 6    |     | BOREN     | I: Browr                         | n-out Res  | set Ena  | ble bit   |              |        |          |              |       |       |       |

|          |     |           | R enable                         |            |          |           |              |        |          |              |       |       |       |

|          |     | 0 = BO    | R disabl                         | ed         |          |           |              |        |          |              |       |       |       |

| bit 5    |     | Unimple   | emented                          | I: Read    | as '1'   |           |              |        |          |              |       |       |       |

| bit 4    |     | CP0: F    | LASH P                           | rogram I   | Vemory   | Code F    | Protection b | oit    |          |              |       |       |       |

|          |     | 1 = Coo   | de prote                         | ction off  |          |           |              |        |          |              |       |       |       |

|          |     | 0 = AII I | memory                           | location   | s code   | protecte  | ed           |        |          |              |       |       |       |

| bit 3    |     | PWRTE     | EN: Pow                          | er-up Ti   | mer Ena  | able bit  |              |        |          |              |       |       |       |

|          |     | 1 = PW    | 'RT disa                         | bled       |          |           |              |        |          |              |       |       |       |

|          |     | 0 = PW    | 'RT enal                         | oled       |          |           |              |        |          |              |       |       |       |

| bit 2    |     | WDTEN     | WDTEN: Watchdog Timer Enable bit |            |          |           |              |        |          |              |       |       |       |

|          |     | 1 = WD    | T enabl                          | ed         |          |           |              |        |          |              |       |       |       |

|          |     | 0 = WD    | T disab                          | led        |          |           |              |        |          |              |       |       |       |

| bit 1-0  |     | FOSC1     | :FOSCO                           | ): Oscilla | tor Sele | ection bi | ts           |        |          |              |       |       |       |

|          |     | 11 = R0   | C oscilla                        | tor        |          |           |              |        |          |              |       |       |       |

|          |     | -         | 10 = HS oscillator               |            |          |           |              |        |          |              |       |       |       |

|          |     | •••••     | 01 = XT oscillator               |            |          |           |              |        |          |              |       |       |       |

|          |     | 00 = LF   | oscillat                         | or         |          |           |              |        |          |              |       |       |       |

|          |     | Note      | 1. The                           | erased     | lunnrog  | irammo    | d) value of  | the co | ofigurat | tion word is | 3FFFb |       |       |

|          |     | Note      |                                  | Gradeu     | (anpi0)  | Jannie    |              |        | mgura    |              |       |       |       |

#### REGISTER 12-1: CONFIGURATION WORD (ADDRESS 2007h) <sup>(1)</sup>

| Legend:                      |                      |                                     |

|------------------------------|----------------------|-------------------------------------|

| R = Readable bit             | P = Programmable bit | U = Unimplemented bit, read as '0'  |

| - n = Value when device is u | nprogrammed          | u = Unchanged from programmed state |

## PIC16F7X

| MOVF             | Move f                                                                                                                                                                                                                                                                            |

|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [label] MOVF f,d                                                                                                                                                                                                                                                                  |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ d \in \ [0,1] \end{array}$                                                                                                                                                                                                                 |

| Operation:       | (f) $\rightarrow$ (destination)                                                                                                                                                                                                                                                   |

| Status Affected: | Z                                                                                                                                                                                                                                                                                 |

| Description:     | The contents of register f are<br>moved to a destination dependant<br>upon the status of d. If $d = 0$ ,<br>destination is W register. If $d = 1$ ,<br>the destination is file register f itself.<br>d = 1 is useful to test a file register,<br>since status flag Z is affected. |

| NOP              | No Operation  |

|------------------|---------------|

| Syntax:          | [label] NOP   |

| Operands:        | None          |

| Operation:       | No operation  |

| Status Affected: | None          |

| Description:     | No operation. |

| MOVLW            | Move Literal to W                                                                              |  |  |  |  |

|------------------|------------------------------------------------------------------------------------------------|--|--|--|--|

| Syntax:          | [label] MOVLW k                                                                                |  |  |  |  |

| Operands:        | $0 \le k \le 255$                                                                              |  |  |  |  |

| Operation:       | $k \rightarrow (W)$                                                                            |  |  |  |  |

| Status Affected: | None                                                                                           |  |  |  |  |

| Description:     | The eight-bit literal k is loaded<br>into W register. The don t cares<br>will assemble as 0 s. |  |  |  |  |

| RETFIE           | Return from Interrupt                                   |

|------------------|---------------------------------------------------------|

| Syntax:          | [label] RETFIE                                          |

| Operands:        | None                                                    |

| Operation:       | $\begin{array}{l} TOS \to PC, \\ 1 \to GIE \end{array}$ |

| Status Affected: | None                                                    |

| MOVWF            | Move W to f                                |  |  |  |  |  |

|------------------|--------------------------------------------|--|--|--|--|--|

| Syntax:          | [label] MOVWF f                            |  |  |  |  |  |

| Operands:        | $0 \le f \le 127$                          |  |  |  |  |  |

| Operation:       | $(W) \rightarrow (f)$                      |  |  |  |  |  |

| Status Affected: | None                                       |  |  |  |  |  |

| Description:     | Move data from W register to register 'f'. |  |  |  |  |  |

| RETLW            | Return with Literal in W                                                                                                                                                            |  |  |  |  |

|------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| Syntax:          | [label] RETLW k                                                                                                                                                                     |  |  |  |  |

| Operands:        | $0 \le k \le 255$                                                                                                                                                                   |  |  |  |  |

| Operation:       | $k \rightarrow (W);$<br>TOS $\rightarrow$ PC                                                                                                                                        |  |  |  |  |

| Status Affected: | None                                                                                                                                                                                |  |  |  |  |

| Description:     | The W register is loaded with the<br>eight-bit literal 'k'. The program<br>counter is loaded from the top of<br>the stack (the return address).<br>This is a two-cycle instruction. |  |  |  |  |

### PIC16F7X

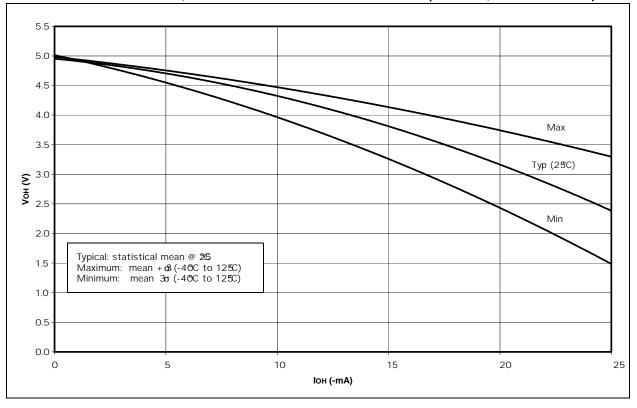

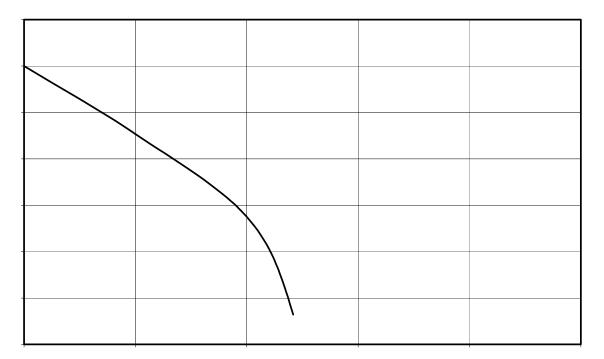

FIGURE 16-15: TYPICAL, MINIMUM AND MAXIMUM VOH vs. IOH (VDD = 5V, -40°C TO 125°C)

#### FIGURE 16-16: TYPICAL, MINIMUM AND MAXIMUM VOH vs. IOH (VDD = 3V, -40°C TO 125°C)

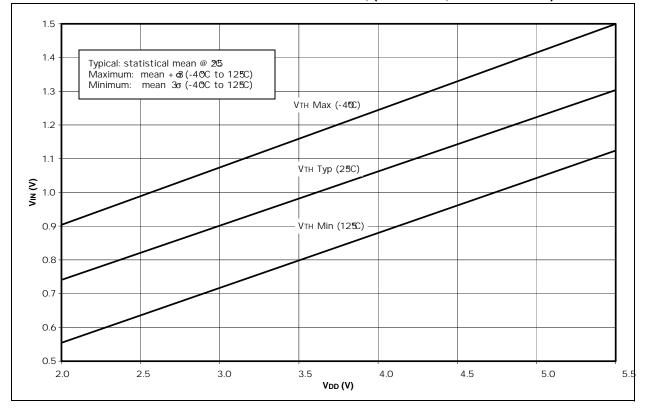

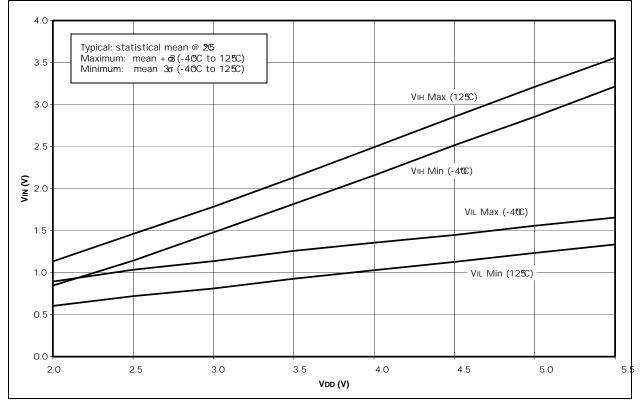

#### FIGURE 16-19: MINIMUM AND MAXIMUM VIN vs. Vdd, (TTL INPUT, -40°C TO 125°C)

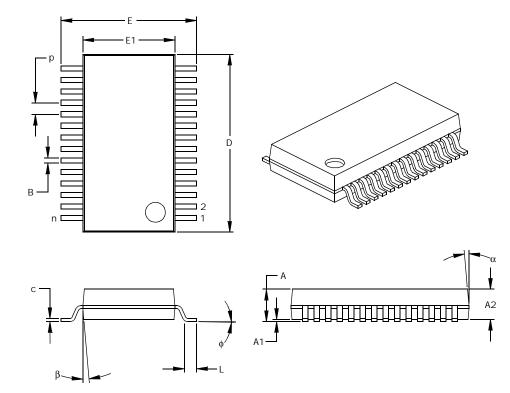

#### 28-Lead Plastic Shrink Small Outline (SS) - 209 mil, 5.30 mm (SSOP)

| Units                    |    | INCHES |      |      | MILLIMETERS* |        |        |

|--------------------------|----|--------|------|------|--------------|--------|--------|

| Dimension Limits         |    | MIN    | NOM  | MAX  | MIN          | NOM    | MAX    |

| Number of Pins           | n  |        | 28   |      |              | 28     |        |

| Pitch                    | р  |        | .026 |      |              | 0.65   |        |

| Overall Height           | Α  | .068   | .073 | .078 | 1.73         | 1.85   | 1.98   |

| Molded Package Thickness | A2 | .064   | .068 | .072 | 1.63         | 1.73   | 1.83   |

| Standoff §               | A1 | .002   | .006 | .010 | 0.05         | 0.15   | 0.25   |

| Overall Width            | E  | .299   | .309 | .319 | 7.59         | 7.85   | 8.10   |

| Molded Package Width     | E1 | .201   | .207 | .212 | 5.11         | 5.25   | 5.38   |

| Overall Length           | D  | .396   | .402 | .407 | 10.06        | 10.20  | 10.34  |

| Foot Length              | L  | .022   | .030 | .037 | 0.56         | 0.75   | 0.94   |

| Lead Thickness           | С  | .004   | .007 | .010 | 0.10         | 0.18   | 0.25   |

| Foot Angle               | ¢  | 0      | 4    | 8    | 0.00         | 101.60 | 203.20 |

| Lead Width               | В  | .010   | .013 | .015 | 0.25         | 0.32   | 0.38   |

| Mold Draft Angle Top     | α  | 0      | 5    | 10   | 0            | 5      | 10     |

| Mold Draft Angle Bottom  | β  | 0      | 5    | 10   | 0            | 5      | 10     |

\* Controlling Parameter § Significant Characteristic

Notes:

Dimensions D and E1 do not include mold flash or protrusions. Mold flash or protrusions shall not exceed .010 (0.254mm) per side. JEDEC Equivalent: MS-150 Drawing No. C04-073