Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                         |

|----------------------------|-------------------------------------------------------------------------|

| Product Status             | Active                                                                  |

| Core Processor             | PIC                                                                     |

| Core Size                  | 8-Bit                                                                   |

| Speed                      | 20MHz                                                                   |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                                       |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                   |

| Number of I/O              | 22                                                                      |

| Program Memory Size        | 7KB (4K x 14)                                                           |

| Program Memory Type        | FLASH                                                                   |

| EEPROM Size                | -                                                                       |

| RAM Size                   | 192 x 8                                                                 |

| Voltage - Supply (Vcc/Vdd) | 4V ~ 5.5V                                                               |

| Data Converters            | A/D 5x8b                                                                |

| Oscillator Type            | External                                                                |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                      |

| Mounting Type              | Surface Mount                                                           |

| Package / Case             | 28-SOIC (0.295", 7.50mm Width)                                          |

| Supplier Device Package    | 28-SOIC                                                                 |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16f73-e-so |

|                            |                                                                         |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### 2.2.2.2 OPTION\_REG Register

The OPTION\_REG register is a readable and writable register, which contains various control bits to configure the TMR0 prescaler/WDT postscaler (single assignable register known also as the prescaler), the External INT Interrupt, TMR0 and the weak pull-ups on PORTB.

Note: To achieve a 1:1 prescaler assignment for the TMR0 register, assign the prescaler to the Watchdog Timer.

## **REGISTER 2-2: OPTION\_REG REGISTER (ADDRESS 81h, 181h)**

|                 | R/W-1                                                                                                                         | R/W-1                                | R/W-1        | R/W-1            | R/W-1        | R/W-1     | R/W-1        | R/W-1   |

|-----------------|-------------------------------------------------------------------------------------------------------------------------------|--------------------------------------|--------------|------------------|--------------|-----------|--------------|---------|

|                 | RBPU                                                                                                                          | INTEDG                               | TOCS         | T0SE             | PSA          | PS2       | PS1          | PS0     |

|                 | bit 7                                                                                                                         |                                      |              |                  |              |           |              | bit 0   |

|                 |                                                                                                                               |                                      |              |                  |              |           |              |         |

| bit 7           |                                                                                                                               | DRTB Pull-up I                       |              |                  |              |           |              |         |

|                 |                                                                                                                               | B pull-ups are                       |              | مرامينا ماريما م |              |           |              |         |

| <b>h</b> it C   | <ul> <li>0 = PORTB pull-ups are enabled by individual port latch values</li> <li>INTEDG: Interrupt Edge Select bit</li> </ul> |                                      |              |                  |              |           |              |         |

| bit 6           |                                                                                                                               |                                      |              |                  |              |           |              |         |

|                 |                                                                                                                               | ipt on rising eo<br>ipt on falling e | •            | •                |              |           |              |         |

| bit 5           | TOCS: TM                                                                                                                      | IR0 Clock Sou                        | rce Select b | bit              |              |           |              |         |

|                 |                                                                                                                               | tion on RA4/T                        |              |                  |              |           |              |         |

|                 |                                                                                                                               | al instruction c                     |              | -                |              |           |              |         |

| bit 4           |                                                                                                                               | R0 Source Ed                         | •            |                  |              |           |              |         |

|                 |                                                                                                                               | nent on high-to<br>nent on low-to-   |              |                  | •            |           |              |         |

| bit 3           |                                                                                                                               | scaler Assignm                       | -            |                  |              |           |              |         |

|                 | 1 = Presca                                                                                                                    | aler is assigne                      | d to the WE  |                  |              |           |              |         |

| <b>h</b> it 0 0 |                                                                                                                               | aler is assigne                      |              |                  |              |           |              |         |

| bit 2-0         |                                                                                                                               | Prescaler Rat                        |              | -                |              |           |              |         |

|                 | Bit V                                                                                                                         | alue TMR0 I                          | Rate WDT     | Rate             |              |           |              |         |

|                 | 00                                                                                                                            | 1.4                                  | 1:1          |                  |              |           |              |         |

|                 | 00<br>01                                                                                                                      |                                      | 1:2          |                  |              |           |              |         |

|                 | 01                                                                                                                            | 1.0                                  |              |                  |              |           |              |         |

|                 | 10                                                                                                                            | 1.0                                  |              |                  |              |           |              |         |

|                 | 10<br>11                                                                                                                      | 1.0                                  |              |                  |              |           |              |         |

|                 | 11                                                                                                                            | 1.14                                 |              |                  |              |           |              |         |

|                 |                                                                                                                               |                                      |              |                  |              |           |              |         |

|                 | Legend:                                                                                                                       |                                      |              |                  |              |           |              |         |

|                 | R = Reada                                                                                                                     | able bit                             | W = W        | ritable bit      | U = Unimp    | olemented | bit, read as | '0'     |

|                 | - n = Value                                                                                                                   | e at POR rese                        | t '1' = Bi   | t is set         | '0' = Bit is | cleared   | x = Bit is ι | unknown |

|                 | L                                                                                                                             |                                      |              |                  |              |           |              |         |

NOTES:

| Name         | Bit# | Buffer | Function                                                                        |

|--------------|------|--------|---------------------------------------------------------------------------------|

| RA0/AN0      | bit0 | TTL    | Input/output or analog input.                                                   |

| RA1/AN1      | bit1 | TTL    | Input/output or analog input.                                                   |

| RA2/AN2      | bit2 | TTL    | Input/output or analog input.                                                   |

| RA3/AN3/VREF | bit3 | TTL    | Input/output or analog input or VREF.                                           |

| RA4/T0CKI    | bit4 | ST     | Input/output or external clock input for Timer0. Output is open drain type.     |

| RA5/SS/AN4   | bit5 | TTL    | Input/output or slave select input for synchronous serial port or analog input. |

#### TABLE 4-1: PORTA FUNCTIONS

Legend: TTL = TTL input, ST = Schmitt Trigger input

#### TABLE 4-2: SUMMARY OF REGISTERS ASSOCIATED WITH PORTA

| Address | Name   | Bit 7 | Bit 6 | Bit 5 | Bit 4                         | Bit 3 | Bit 2 | Bit 1 | Bit 0 | Value on:<br>POR,<br>BOR | Value on all<br>other<br>RESETS |

|---------|--------|-------|-------|-------|-------------------------------|-------|-------|-------|-------|--------------------------|---------------------------------|

| 05h     | PORTA  | _     | _     | RA5   | RA4                           | RA3   | RA2   | RA1   | RA0   | 0x 0000                  | 0u 0000                         |

| 85h     | TRISA  | _     | _     | PORTA | PORTA Data Direction Register |       |       |       |       | 11 1111                  | 11 1111                         |

| 9Fh     | ADCON1 |       | _     | _     | _                             | _     | PCFG2 | PCFG1 | PCFG0 | 000                      | 000                             |

Legend: x = unknown, u = unchanged, - = unimplemented locations read as '0'. Shaded cells are not used by PORTA.

**Note:** When using the SSP module in SPI Slave mode and  $\overline{SS}$  enabled, the A/D converter must be set to one of the following modes where PCFG2:PCFG0 = 100, 101, 11x.

## 6.0 TIMER1 MODULE

The Timer1 module is a 16-bit timer/counter consisting of two 8-bit registers (TMR1H and TMR1L), which are readable and writable. The TMR1 Register pair (TMR1H:TMR1L) increments from 0000h to FFFFh and rolls over to 0000h. The TMR1 Interrupt, if enabled, is generated on overflow, which is latched in interrupt flag bit TMR1IF (PIR1<0>). This interrupt can be enabled/disabled by setting/clearing TMR1 interrupt enable bit TMR1IE (PIE1<0>).

Timer1 can operate in one of two modes:

- As a timer

- · As a counter

The operating mode is determined by the clock select bit, TMR1CS (T1CON<1>).

In Timer mode, Timer1 increments every instruction cycle. In Counter mode, it increments on every rising edge of the external clock input.

Timer1 can be enabled/disabled by setting/clearing control bit TMR1ON (T1CON<0>).

Timer1 also has an internal "RESET input". This RESET can be generated by either of the two CCP modules as the special event trigger (see Sections 8.1 and 8.2). Register 6-1 shows the Timer1 Control register.

When the Timer1 oscillator is enabled (T1OSCEN is set), the RC1/T1OSI/CCP2 and RC0/T1OSO/T1CKI pins become inputs. That is, the TRISC<1:0> value is ignored and these pins read as '0'.

Additional information on timer modules is available in the PICmicro<sup>™</sup> Mid-Range MCU Family Reference Manual (DS33023).

### REGISTER 6-1: T1CON: TIMER1 CONTROL REGISTER (ADDRESS 10h)

|         |             |                                |                |                | •                                                                       | ,            |              |         |

|---------|-------------|--------------------------------|----------------|----------------|-------------------------------------------------------------------------|--------------|--------------|---------|

|         | U-0         | U-0                            | R/W-0          | R/W-0          | R/W-0                                                                   | R/W-0        | R/W-0        | R/W-0   |

|         | _           | —                              | T1CKPS1        | T1CKPS0        | T1OSCEN                                                                 | T1SYNC       | TMR1CS       | TMR10N  |

|         | bit 7       |                                |                |                |                                                                         |              |              | bit 0   |

|         |             |                                |                |                |                                                                         |              |              |         |

| bit 7-6 | Unimplem    | nented: Rea                    | d as '0'       |                |                                                                         |              |              |         |

| bit 5-4 |             |                                | •              | ut Clock Pres  | scale Select I                                                          | bits         |              |         |

|         |             | rescale valu                   |                |                |                                                                         |              |              |         |

|         |             | rescale valu<br>rescale valu   |                |                |                                                                         |              |              |         |

|         |             | rescale valu                   |                |                |                                                                         |              |              |         |

| bit 3   | T1OSCEN     | l: Timer1 Os                   | cillator Ena   | ble Control b  | oit                                                                     |              |              |         |

|         | 1 = Oscilla | tor is enable                  | ed             |                |                                                                         |              |              |         |

|         | 0 = Oscilla | tor is shut-o                  | off (the oscil | ator inverter  | is turned off                                                           | to eliminate | power draii  | า)      |

| bit 2   | T1SYNC:     | Timer1 Exte                    | rnal Clock I   | nput Synchr    | onization Co                                                            | ntrol bit    |              |         |

|         | TMR1CS :    |                                |                | I.a. a. l      |                                                                         |              |              |         |

|         |             | synchronize                    |                | •              |                                                                         |              |              |         |

|         | TMR1CS :    |                                |                | Jul            |                                                                         |              |              |         |

|         |             |                                | ner1 uses th   | e internal clo | ock when TM                                                             | IR1CS = 0.   |              |         |

| bit 1   | TMR1CS:     | Timer1 Cloc                    | k Source S     | elect bit      |                                                                         |              |              |         |

|         |             | al clock fron<br>al clock (Fos | •              | 10SO/T1Cł      | <i (on="" risi<="" td="" the=""><td>ng edge)</td><td></td><td></td></i> | ng edge)     |              |         |

| bit 0   | TMR10N:     | Timer1 On I                    | bit            |                |                                                                         |              |              |         |

|         | 1 = Enable  | es Timer1                      |                |                |                                                                         |              |              |         |

|         | 0 = Stops   | Timer1                         |                |                |                                                                         |              |              |         |

|         | r           |                                |                |                |                                                                         |              |              |         |

|         | Legend:     |                                |                |                |                                                                         |              |              |         |

|         | R = Reada   | able bit                       | W = V          | Nritable bit   | U = Unin                                                                | nplemented   | bit, read as | '0'     |

|         | - n = Value | e at POR res                   | set '1' =      | Bit is set     | '0' = Bit i                                                             | s cleared    | x = Bit is ι | unknown |

|         |             |                                |                |                |                                                                         |              |              |         |

#### 8.4.1 CCP PIN CONFIGURATION

The user must configure the RC2/CCP1 pin as an output by clearing the TRISC<2> bit.

| Note: | Clearing the CCP1CON register will force |

|-------|------------------------------------------|

|       | the RC2/CCP1 compare output latch to the |

|       | default low level. This is not the PORTC |

|       | I/O data latch.                          |

#### 8.4.2 TIMER1 MODE SELECTION

Timer1 must be running in Timer mode or Synchronized Counter mode if the CCP module is using the compare feature. In Asynchronous Counter mode, the compare operation may not work.

#### 8.4.3 SOFTWARE INTERRUPT MODE

When Generate Software Interrupt mode is chosen, the CCP1 pin is not affected. The CCP1IF or CCP2IF bit is set, causing a CCP interrupt (if enabled).

### 8.4.4 SPECIAL EVENT TRIGGER

In this mode, an internal hardware trigger is generated, which may be used to initiate an action.

The special event trigger output of CCP1 resets the TMR1 register pair. This allows the CCPR1 register to effectively be a 16-bit programmable period register for Timer1.

The special event trigger output of CCP2 resets the TMR1 register pair and starts an A/D conversion (if the A/D module is enabled).

**Note:** The special event trigger from the CCP1 and CCP2 modules will not set interrupt flag bit TMR1IF (PIR1<0>).

| Address               | Name    | Bit 7                               | Bit 6                               | Bit 5        | Bit 4         | Bit 3          | Bit 2      | Bit 1      | Bit 0     | Value on:<br>POR,<br>BOR | Value on<br>all other<br>RESETS |

|-----------------------|---------|-------------------------------------|-------------------------------------|--------------|---------------|----------------|------------|------------|-----------|--------------------------|---------------------------------|

| 0Bh,8Bh,<br>10Bh,18Bh | INTCON  | GIE                                 | PEIE                                | TMR0IE       | INTE          | RBIE           | TMR0IF     | INTF       | RBIF      | 0000 000x                | 0000 000u                       |

| 0Ch                   | PIR1    | PSPIF <sup>(1)</sup>                | ADIF                                | RCIF         | TXIF          | SSPIF          | CCP1IF     | TMR2IF     | TMR1IF    | 0000 0000                | 0000 0000                       |

| 0Dh                   | PIR2    | —                                   | —                                   | —            | —             | _              | _          | _          | CCP2IF    | 0                        | 0                               |

| 8Ch                   | PIE1    | PSPIE <sup>(1)</sup>                | ADIE                                | RCIE         | TXIE          | SSPIE          | CCP1IE     | TMR2IE     | TMR1IE    | 0000 0000                | 0000 0000                       |

| 8Dh                   | PIE2    | —                                   | _                                   | —            | _             | _              | —          | _          | CCP2IE    | 0                        | 0                               |

| 87h                   | TRISC   | PORTC D                             | ata Direc                           | tion Registe | er            |                |            |            |           | 1111 1111                | 1111 1111                       |

| 0Eh                   | TMR1L   | Holding R                           | egister fo                          | r the Least  | Significant   | Byte of the 1  | 6-bit TMR  | 1 Register |           | xxxx xxxx                | uuuu uuuu                       |

| 0Fh                   | TMR1H   | Holding R                           | egister fo                          | r the Most S | Significant E | Byte of the 16 | 6-bit TMR1 | Register   |           | xxxx xxxx                | uuuu uuuu                       |

| 10h                   | T1CON   | —                                   |                                     | T1CKPS1      | T1CKPS0       | T1OSCEN        | T1SYNC     | TMR1CS     | TMR10N    | 00 0000                  | uu uuuu                         |

| 15h                   | CCPR1L  | Capture/C                           | ompare/l                            | PWM Regis    | ster1 (LSB)   |                |            |            |           | xxxx xxxx                | uuuu uuuu                       |

| 16h                   | CCPR1H  | Capture/C                           | ompare/l                            | PWM Regis    | ster1 (MSB)   |                |            |            |           | xxxx xxxx                | uuuu uuuu                       |

| 17h                   | CCP1CON | —                                   |                                     | CCP1X        | CCP1Y         | CCP1M3         | CCP1M2     | CCP1M1     | CCP1M0    | 00 0000                  | 00 0000                         |

| 1Bh                   | CCPR2L  | Capture/Compare/PWM Register2 (LSB) |                                     |              |               |                |            |            | xxxx xxxx | uuuu uuuu                |                                 |

| 1Ch                   | CCPR2H  | Capture/C                           | Capture/Compare/PWM Register2 (MSB) |              |               |                |            |            | uuuu uuuu |                          |                                 |

| 1Dh                   | CCP2CON | —                                   | _                                   | CCP2X        | CCP2Y         | CCP2M3         | CCP2M2     | CCP2M1     | CCP2M0    | 00 0000                  | 00 0000                         |

### TABLE 8-3: REGISTERS ASSOCIATED WITH CAPTURE, COMPARE, AND TIMER1

Legend: x = unknown, u = unchanged, - = unimplemented, read as '0'. Shaded cells are not used by Capture and Timer1.

**Note 1:** The PSP is not implemented on the PIC16F73/76; always maintain these bits clear.

| REGISTER 9-1: SSPSTAT: SYNC SERIAL PORT STATUS REGISTER (ADDRESS 94                                                                                   | SSPSTAT: SYNC SERIAL PORT STATUS REGISTER (ADDRESS 94h) |  |  |  |  |  |  |  |

|-------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------|--|--|--|--|--|--|--|

| R/W-0 R/W-0 R-0 R-0 R-0 R-0 R-0 R-0 R-0 R-0 R-0 R                                                                                                     | -0 R-0                                                  |  |  |  |  |  |  |  |

| SMP CKE D/A P S R/W U                                                                                                                                 | A BF                                                    |  |  |  |  |  |  |  |

| bit 7                                                                                                                                                 | bit C                                                   |  |  |  |  |  |  |  |

| bit 7 SMP: SPI Data Input Sample Phase bit                                                                                                            |                                                         |  |  |  |  |  |  |  |

| SPI Master mode:                                                                                                                                      |                                                         |  |  |  |  |  |  |  |

| 1 = Input data sampled at end of data output time                                                                                                     |                                                         |  |  |  |  |  |  |  |

| 0 = Input data sampled at middle of data output time (Microwire®)                                                                                     |                                                         |  |  |  |  |  |  |  |

| <u>SPI Slave mode:</u><br>SMP must be cleared when SPI is used in Slave mode                                                                          |                                                         |  |  |  |  |  |  |  |

| I <sup>2</sup> C mode:                                                                                                                                |                                                         |  |  |  |  |  |  |  |

| This bit must be maintained clear                                                                                                                     |                                                         |  |  |  |  |  |  |  |

| bit 6 <b>CKE</b> : SPI Clock Edge Select bit (Figure 9-2, Figure 9-3, and Figure 9-4)                                                                 |                                                         |  |  |  |  |  |  |  |

| <u>SPI mode, CKP = 0:</u>                                                                                                                             |                                                         |  |  |  |  |  |  |  |

| <ul> <li>1 = Data transmitted on rising edge of SCK (Microwire<sup>®</sup> alternate)</li> <li>0 = Data transmitted on falling edge of SCK</li> </ul> |                                                         |  |  |  |  |  |  |  |

| SPI mode, $CKP = 1$ :                                                                                                                                 |                                                         |  |  |  |  |  |  |  |

| 1 = Data transmitted on falling edge of SCK (Microwire <sup>®</sup> default)                                                                          |                                                         |  |  |  |  |  |  |  |

| 0 = Data transmitted on rising edge of SCK                                                                                                            |                                                         |  |  |  |  |  |  |  |

| I <sup>2</sup> C mode:<br>This bit must be maintained clear                                                                                           |                                                         |  |  |  |  |  |  |  |

| bit 5 <b>D/A</b> : Data/Address bit (I <sup>2</sup> C mode only)                                                                                      |                                                         |  |  |  |  |  |  |  |

| 1 = Indicates that the last byte received or transmitted was data                                                                                     |                                                         |  |  |  |  |  |  |  |

| 0 = Indicates that the last byte received or transmitted was address                                                                                  |                                                         |  |  |  |  |  |  |  |

| bit 4 <b>P</b> : STOP bit (I <sup>2</sup> C mode only)                                                                                                |                                                         |  |  |  |  |  |  |  |

| This bit is cleared when the SSP module is disabled, or when the START bit is<br>SSPEN is cleared.                                                    | s detected last.                                        |  |  |  |  |  |  |  |

| 1 = Indicates that a STOP bit has been detected last (this bit is '0' on RESET)                                                                       |                                                         |  |  |  |  |  |  |  |

| 0 = STOP bit was not detected last                                                                                                                    |                                                         |  |  |  |  |  |  |  |

| bit 3 <b>S</b> : START bit (I <sup>2</sup> C mode only)                                                                                               |                                                         |  |  |  |  |  |  |  |

| This bit is cleared when the SSP module is disabled, or when the STOP bit is SSPEN is cleared.                                                        | detected last.                                          |  |  |  |  |  |  |  |

| 1 = Indicates that a START bit has been detected last (this bit is '0' on RESET                                                                       | )                                                       |  |  |  |  |  |  |  |

| 0 = START bit was not detected last                                                                                                                   |                                                         |  |  |  |  |  |  |  |

| bit 2 <b>R/W</b> : Read/Write bit Information (I <sup>2</sup> C mode only)                                                                            |                                                         |  |  |  |  |  |  |  |

| This bit holds the R/W bit information following the last address match. This bit i<br>the address match to the next START bit, STOP bit, or ACK bit. | s only valid from                                       |  |  |  |  |  |  |  |

| 1 = Read                                                                                                                                              |                                                         |  |  |  |  |  |  |  |

| 0 = Write                                                                                                                                             |                                                         |  |  |  |  |  |  |  |

| bit 1 <b>UA</b> : Update Address bit (10-bit I <sup>2</sup> C mode only)                                                                              |                                                         |  |  |  |  |  |  |  |

| 1 = Indicates that the user needs to update the address in the SSPADD regist                                                                          | er                                                      |  |  |  |  |  |  |  |

| <ul> <li>0 = Address does not need to be updated</li> <li>bit 0</li> <li><b>BF</b>: Buffer Full Status bit</li> </ul>                                 |                                                         |  |  |  |  |  |  |  |

| Receive (SPI and I <sup>2</sup> C modes):                                                                                                             |                                                         |  |  |  |  |  |  |  |

| 1 = Receive complete, SSPBUF is full                                                                                                                  |                                                         |  |  |  |  |  |  |  |

| 0 = Receive not complete, SSPBUF is empty                                                                                                             |                                                         |  |  |  |  |  |  |  |

| Transmit (I <sup>2</sup> C mode only):                                                                                                                |                                                         |  |  |  |  |  |  |  |

| 1 = Transmit in progress, SSPBUF is full                                                                                                              |                                                         |  |  |  |  |  |  |  |

| 0 = Iransmit complete, SSPBUF is empty                                                                                                                | 0 = Transmit complete, SSPBUF is empty                  |  |  |  |  |  |  |  |

| Legend:                                                                                                                                               |                                                         |  |  |  |  |  |  |  |

| R = Readable bit W = Writable bit U = Unimplemented bit, rea                                                                                          | id as '0'                                               |  |  |  |  |  |  |  |

| - n = Value at POR reset $'1'$ = Bit is set $'0'$ = Bit is cleared x = B                                                                              | Bit is unknown                                          |  |  |  |  |  |  |  |

\_

|                                                                                                                                                                                                                                                | R/W-0                                                                                                                                                                                                                                                                                                                                                                                                                                     | R/W-0                                                                                                                                                                            | R/W-0           | R/W-0                                              | R/W-0                                              | R/W-0                                 | R/W-0          | R/W-0  |  |  |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------|----------------------------------------------------|----------------------------------------------------|---------------------------------------|----------------|--------|--|--|

|                                                                                                                                                                                                                                                | WCOL                                                                                                                                                                                                                                                                                                                                                                                                                                      | SSPOV                                                                                                                                                                            | SSPEN           | CKP                                                | SSPM3                                              | SSPM2                                 | SSPM1          | SSPM0  |  |  |

|                                                                                                                                                                                                                                                | bit 7                                                                                                                                                                                                                                                                                                                                                                                                                                     | 331 0 1                                                                                                                                                                          |                 | UN                                                 | 30F 1013                                           |                                       | 301 101        | bit 0  |  |  |

| 1 : 1 - 7                                                                                                                                                                                                                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                                                                                                  |                 |                                                    |                                                    |                                       |                |        |  |  |

| bit 7                                                                                                                                                                                                                                          | 1 = The S<br>(must                                                                                                                                                                                                                                                                                                                                                                                                                        | <pre>WCOL: Write Collision Detect bit 1 = The SSPBUF register is written while it is still transmitting the previous word   (must be cleared in software) 0 = No collision</pre> |                 |                                                    |                                                    |                                       |                |        |  |  |

| bit 6                                                                                                                                                                                                                                          | SSPOV: F                                                                                                                                                                                                                                                                                                                                                                                                                                  | Receive Ove                                                                                                                                                                      | rflow Indicate  | or bit                                             |                                                    |                                       |                |        |  |  |

|                                                                                                                                                                                                                                                | In SPI mo                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                                                                                                  |                 |                                                    |                                                    |                                       |                |        |  |  |

|                                                                                                                                                                                                                                                | <ul> <li>1 = A new byte is received while the SSPBUF register is still holding the previous data. of overflow, the data in SSPSR is lost. Overflow can only occur in Slave mode. Th must read the SSPBUF, even if only transmitting data, to avoid setting overflow. In Master mode, the overflow bit is not set since each new reception (and transmiss initiated by writing to the SSPBUF register.</li> <li>0 = No overflow</li> </ul> |                                                                                                                                                                                  |                 |                                                    |                                                    |                                       |                |        |  |  |

|                                                                                                                                                                                                                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                           | e is received<br>don't care" ir                                                                                                                                                  |                 | SPBUF registe<br>ode. SSPOV r                      |                                                    |                                       |                |        |  |  |

| bit 5                                                                                                                                                                                                                                          | <b>SSPEN</b> : S                                                                                                                                                                                                                                                                                                                                                                                                                          | Svnchronous                                                                                                                                                                      | Serial Port     | Enable bit                                         |                                                    |                                       |                |        |  |  |

|                                                                                                                                                                                                                                                | In SPI mode:<br>1 = Enables serial port and configures SCK, SDO, and SDI as serial port pins<br>0 = Disables serial port and configures these pins as I/O port pins<br>In I <sup>2</sup> C mode:                                                                                                                                                                                                                                          |                                                                                                                                                                                  |                 |                                                    |                                                    |                                       |                |        |  |  |

|                                                                                                                                                                                                                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                                                                                                  |                 | nfigures the SI<br>ures these pin                  |                                                    |                                       | rial port pine | 6      |  |  |

|                                                                                                                                                                                                                                                | In both mo                                                                                                                                                                                                                                                                                                                                                                                                                                | odes, when a                                                                                                                                                                     | enabled, the    | se pins must b                                     | e properly o                                       | configured a                          | as input or o  | utput. |  |  |

| bit 4                                                                                                                                                                                                                                          | CKP: Clor                                                                                                                                                                                                                                                                                                                                                                                                                                 | ck Polarity S                                                                                                                                                                    | elect bit       |                                                    |                                                    |                                       |                |        |  |  |

|                                                                                                                                                                                                                                                | <u>In SPI mo</u><br>1 = IDLE s                                                                                                                                                                                                                                                                                                                                                                                                            | de:<br>state for cloc                                                                                                                                                            | ck is a high le | evel (Microwire<br>vel (Microwire <sup>∉</sup>     | e <sup>®</sup> default)<br><sup>®</sup> alternate) |                                       |                |        |  |  |

| In I <sup>2</sup> C mode:<br>SCK release control<br>1 = Enable clock                                                                                                                                                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                                                                                                  |                 |                                                    |                                                    |                                       |                |        |  |  |

|                                                                                                                                                                                                                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                                                                                                  | lock stretch)   | . (Used to ens                                     | ure data se                                        | tup time.)                            |                |        |  |  |

| bit 3-0                                                                                                                                                                                                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                                                                                                  | -               | -                                                  |                                                    | , , , , , , , , , , , , , , , , , , , |                |        |  |  |

| bit 3-0 SSPM3:SSPM0: Synchronous Serial Port Mode Select bits<br>0000 = SPI Master mode, clock = Fosc/4<br>0001 = SPI Master mode, clock = Fosc/16<br>0010 = SPI Master mode, clock = Fosc/64<br>0011 = SPI Master mode, clock = TMR2 output/2 |                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                                                                                                  |                 |                                                    |                                                    |                                       |                |        |  |  |

|                                                                                                                                                                                                                                                | 0101 = SF<br>$0110 = I^{2}(0111 = I^{2})$                                                                                                                                                                                                                                                                                                                                                                                                 | PI Slave moo<br>C Slave moo<br>C Slave moo                                                                                                                                       | dress           | n control dis                                      |                                                    | an be used                            | as I/O pin.    |        |  |  |

|                                                                                                                                                                                                                                                | $1110 = I^{2}$                                                                                                                                                                                                                                                                                                                                                                                                                            | C Slave mod                                                                                                                                                                      | de, 7-bit addr  | laster mode (s<br>ress with STAF<br>dress with STA | RT and STC                                         |                                       |                |        |  |  |

|                                                                                                                                                                                                                                                | Legend:                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                                                                                                  |                 |                                                    |                                                    |                                       |                |        |  |  |

|                                                                                                                                                                                                                                                | R = Reada                                                                                                                                                                                                                                                                                                                                                                                                                                 | able bit                                                                                                                                                                         | VV = V          | Nritable bit                                       | U = Unim                                           | plemented                             | bit, read as   | '0'    |  |  |

| Legend:                  |                  |                      |                    |

|--------------------------|------------------|----------------------|--------------------|

| R = Readable bit         | W = Writable bit | U = Unimplemented    | bit, read as '0'   |

| - n = Value at POR reset | '1' = Bit is set | '0' = Bit is cleared | x = Bit is unknown |

# 9.3 SSP I<sup>2</sup>C Operation

The SSP module in  $l^2C$  mode, fully implements all slave functions, except general call support, and provides interrupts on START and STOP bits in hardware to facilitate firmware implementations of the master functions. The SSP module implements the standard mode specifications as well as 7-bit and 10-bit addressing.

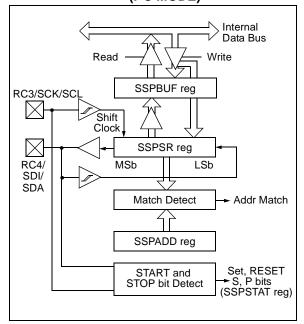

Two pins are used for data transfer. These are the RC3/ SCK/SCL pin, which is the clock (SCL), and the RC4/ SDI/SDA pin, which is the data (SDA). The user must configure these pins as inputs or outputs through the TRISC<4:3> bits.

The SSP module functions are enabled by setting SSP enable bit SSPEN (SSPCON<5>).

FIGURE 9-5: SSP BLOCK DIAGRAM (I<sup>2</sup>C MODE)

The SSP module has five registers for  $\mathsf{I}^2\mathsf{C}$  operation. These are the:

- SSP Control Register (SSPCON)

- SSP Status Register (SSPSTAT)

- Serial Receive/Transmit Buffer (SSPBUF)

- SSP Shift Register (SSPSR) Not directly accessible

- SSP Address Register (SSPADD)

The SSPCON register allows control of the  $I^2C$  operation. Four mode selection bits (SSPCON<3:0>) allow one of the following  $I^2C$  modes to be selected:

- I<sup>2</sup>C Slave mode (7-bit address)

- I<sup>2</sup>C Slave mode (10-bit address)

- I<sup>2</sup>C Slave mode (7-bit address), with START and STOP bit interrupts enabled to support Firmware Master mode

- I<sup>2</sup>C Slave mode (10-bit address), with START and STOP bit interrupts enabled to support Firmware Master mode

- I<sup>2</sup>C START and STOP bit interrupts enabled to support Firmware Master mode, Slave is IDLE

Selection of any  $I^2C$  mode with the SSPEN bit set, forces the SCL and SDA pins to be open drain, provided these pins are programmed to inputs by setting the appropriate TRISC bits. Pull-up resistors must be provided externally to the SCL and SDA pins for proper operation of the  $I^2C$  module.

Additional information on SSP I<sup>2</sup>C operation can be found in the PICmicro<sup>™</sup> Mid-Range MCU Family Reference Manual (DS33023A).

### 9.3.1 SLAVE MODE

In Slave mode, the SCL and SDA pins must be configured as inputs (TRISC<4:3> set). The SSP module will override the input state with the output data when required (slave-transmitter).

When an address is matched, or the data transfer after an address match is received, the hardware automatically will generate the Acknowledge ( $\overline{ACK}$ ) pulse, and then load the SSPBUF register with the received value currently in the SSPSR register.

There are certain conditions that will cause the SSP module not to give this ACK pulse. They include (either or both):

- a) The buffer full bit BF (SSPSTAT<0>) was set before the transfer was received.

- b) The overflow bit SSPOV (SSPCON<6>) was set before the transfer was received.

In this case, the SSPSR register value is not loaded into the SSPBUF, but bit SSPIF (PIR1<3>) is set. Table 9-2 shows what happens when a data transfer byte is received, given the status of bits BF and SSPOV. The shaded cells show the condition where user software did not properly clear the overflow condition. Flag bit BF is cleared by reading the SSPBUF register, while bit SSPOV is cleared through software.

The SCL clock input must have a minimum high and low for proper operation. The high and low times of the  $I^2C$  specification, as well as the requirements of the SSP module, are shown in timing parameter #100 and parameter #101.

### 9.3.1.1 Addressing

Once the SSP module has been enabled, it waits for a START condition to occur. Following the START condition, the 8-bits are shifted into the SSPSR register. All incoming bits are sampled with the rising edge of the clock (SCL) line. The value of register SSPSR<7:1> is compared to the value of the SSPADD register. The address is compared on the falling edge of the eighth clock (SCL) pulse. If the addresses match, and the BF and SSPOV bits are clear, the following events occur:

- a) The SSPSR register value is loaded into the SSPBUF register.

- b) The buffer full bit, BF is set.

- c) An ACK pulse is generated.

- d) SSP interrupt flag bit, SSPIF (PIR1<3>) is set (interrupt is generated if enabled) - on the falling edge of the ninth SCL pulse.

In 10-bit Address mode, two address bytes need to be received by the slave (Figure 9-7). The five Most Significant bits (MSbs) of the first address byte specify if this is a 10-bit address. Bit R/W (SSPSTAT<2>) must specify a write so the slave device will receive the second address byte. For a 10-bit address, the first byte would equal '1111 0 A9 A8 0', where A9 and A8 are the two MSbs of the address. The sequence of events for 10-bit address is as follows, with steps 7 - 9 for slave-transmitter:

- 1. Receive first (high) byte of address (bits SSPIF, BF, and bit UA (SSPSTAT<1>) are set).

- Update the SSPADD register with second (low) byte of address (clears bit UA and releases the SCL line).

- 3. Read the SSPBUF register (clears bit BF) and clear flag bit SSPIF.

- 4. Receive second (low) byte of address (bits SSPIF, BF, and UA are set).

- 5. Update the SSPADD register with the first (high) byte of address, if match releases SCL line, this will clear bit UA.

- 6. Read the SSPBUF register (clears bit BF) and clear flag bit SSPIF.

- 7. Receive Repeated START condition.

- 8. Receive first (high) byte of address (bits SSPIF and BF are set).

- 9. Read the SSPBUF register (clears bit BF) and clear flag bit SSPIF.

|    | its as Data<br>s Received | $SSPSR \to SSPBUF$ | Generate ACK<br>Pulse | Set bit SSPIF<br>(SSP Interrupt occurs |  |  |

|----|---------------------------|--------------------|-----------------------|----------------------------------------|--|--|

| BF | SSPOV                     |                    | Fuise                 | if enabled)                            |  |  |

| 0  | 0                         | Yes                | Yes                   | Yes                                    |  |  |

| 1  | 0                         | No                 | No                    | Yes                                    |  |  |

| 1  | 1                         | No                 | No                    | Yes                                    |  |  |

| 0  | 1                         | No                 | No                    | Yes                                    |  |  |

## TABLE 9-2: DATA TRANSFER RECEIVED BYTE ACTIONS

**Note:** Shaded cells show the conditions where the user software did not properly clear the overflow condition.

#### 9.3.1.2 Reception

When the R/W bit of the address byte is clear and an address match occurs, the R/W bit of the SSPSTAT register is cleared. The received address is loaded into the SSPBUF register.

When the address byte overflow condition exists, then no Acknowledge (ACK) pulse is given. An overflow condition is defined as either bit BF (SSPSTAT<0>) is set, or bit SSPOV (SSPCON<6>) is set. This is an error condition due to the user's firmware. An SSP interrupt is generated for each data transfer byte. Flag bit SSPIF (PIR1<3>) must be cleared in software. The SSPSTAT register is used to determine the status of the byte.

| FIGURE 9-6: I <sup>2</sup> C WAVEFO                                                                                                                                                                                                                                                      | DRMS FOR RECEPTION (7-BIT ADDRESS)                                           |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------|

| Receiving Address $R\overline{W}$<br>SDA $\overline{\sqrt{1}}$ $\overline{A7} \overline{A6} \overline{A5} \overline{A4} \overline{A3} \overline{A2} \overline{A1}$<br>SCL $\frac{1}{1} S^{1} \sqrt{1} \sqrt{2} \sqrt{3} \sqrt{4} \sqrt{5} \sqrt{6} \sqrt{7} \sqrt{8}$<br>SSPIF (PIR1<3>) | =0 Receiving Data ACK Receiving Data ACK |

| BF (SSPSTAT<0>)                                                                                                                                                                                                                                                                          | SSPBUF register is read                                                      |

| SSPOV (SSPCON<6>)                                                                                                                                                                                                                                                                        | Bit SSPOV is set because the SSPBUF register is still full.                  |

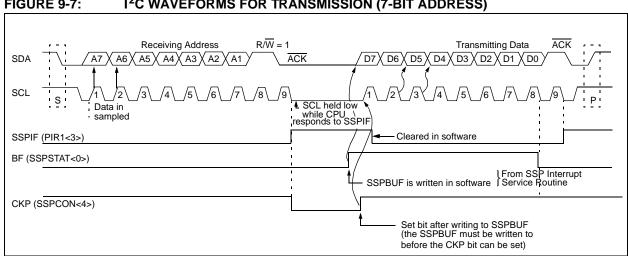

#### 9.3.1.3 Transmission

When the R/W bit of the incoming address byte is set and an address match occurs, the R/W bit of the SSPSTAT register is set. The received address is loaded into the SSPBUF register. The ACK pulse will be sent on the ninth bit, and pin RC3/SCK/SCL is held low. The transmit data must be loaded into the SSPBUF register, which also loads the SSPSR register. Then, pin RC3/SCK/SCL should be enabled by setting bit CKP (SSPCON<4>). The master must monitor the SCL pin prior to asserting another clock pulse. The slave devices may be holding off the master by stretching the clock. The eight data bits are shifted out on the falling edge of the SCL input. This ensures that the SDA signal is valid during the SCL high time (Figure 9-7).

An SSP interrupt is generated for each data transfer byte. Flag bit SSPIF must be cleared in software, and the SSPSTAT register is used to determine the status of the byte. Flag bit SSPIF is set on the falling edge of the ninth clock pulse.

As a slave-transmitter, the ACK pulse from the masterreceiver is latched on the rising edge of the ninth SCL input pulse. If the SDA line was high (not ACK), then the data transfer is complete. When the  $\overline{ACK}$  is latched by the slave, the slave logic is reset (resets SSPSTAT register) and the slave then monitors for another occurrence of the START bit. If the SDA line was low (ACK), the transmit data must be loaded into the SSPBUF reqister, which also loads the SSPSR register. Then pin RC3/SCK/SCL should be enabled by setting bit CKP.

#### I<sup>2</sup>C WAVEFORMS FOR TRANSMISSION (7-BIT ADDRESS) FIGURE 9-7:

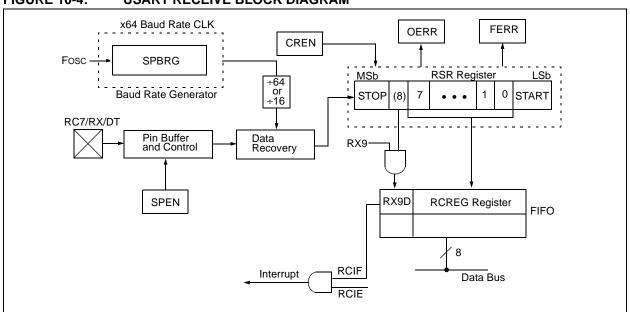

### 10.2.2 USART ASYNCHRONOUS RECEIVER

The receiver block diagram is shown in Figure 10-4. The data is received on the RC7/RX/DT pin and drives the data recovery block. The data recovery block is actually a high speed shifter operating at x16 times the baud rate, whereas the main receive serial shifter operates at the bit rate, or at FOSC.

Once Asynchronous mode is selected, reception is enabled by setting bit CREN (RCSTA<4>).

The heart of the receiver is the receive (serial) shift register (RSR). After sampling the STOP bit, the received data in the RSR is transferred to the RCREG register (if it is empty). If the transfer is complete, flag bit RCIF (PIR1<5>) is set. The actual interrupt can be enabled/ disabled by setting/clearing enable bit RCIE (PIE1<5>). Flag bit RCIF is a read only bit which is cleared by the hardware. It is cleared when the RCREG register has been read and is empty. The RCREG is a double buffered register (i.e., it is a two deep FIFO). It is possible for two bytes of data to be received and transferred to the RCREG FIFO and a third byte to begin shifting to the RSR register. On the detection of the STOP bit of the third byte, if the RCREG register is still full, the overrun error bit OERR (RCSTA<1>) will be set. The word in the RSR will be lost. The RCREG register can be read twice to retrieve the two bytes in the FIFO. Overrun bit OERR has to be cleared in software. This is done by resetting the receive logic (CREN is cleared and then set). If bit OERR is set, transfers from the RSR register to the RCREG register are inhibited and no further data will be received, therefore, it is essential to clear error bit OERR if it is set. Framing error bit FERR (RCSTA<2>) is set if a STOP bit is detected as clear. Bit FERR and the 9th receive bit are buffered the same way as the receive data. Reading the RCREG will load bits RX9D and FERR with new values, therefore, it is essential for the user to read the RCSTA register before reading RCREG register, in order not to lose the old FERR and RX9D information.

| Address                | Name   | Bit 7                                            | Bit 6                                       | Bit 5  | Bit 4 | Bit 3 | Bit 2  | Bit 1  | Bit 0  | Value on:<br>POR,<br>BOR | Value on<br>all other<br>RESETS |

|------------------------|--------|--------------------------------------------------|---------------------------------------------|--------|-------|-------|--------|--------|--------|--------------------------|---------------------------------|

| 0Bh, 8Bh,<br>10Bh,18Bh | INTCON | GIE                                              | PEIE                                        | TMR0IE | INTE  | RBIE  | TMR0IF | INTF   | RBIF   | 0000 000x                | 0000 000u                       |

| 0Ch                    | PIR1   | PSPIF <sup>(1)</sup>                             | ADIF                                        | RCIF   | TXIF  | SSPIF | CCP1IF | TMR2IF | TMR1IF | 0000 0000                | 0000 0000                       |

| 18h                    | RCSTA  | SPEN                                             | RX9                                         | SREN   | CREN  | ADDEN | FERR   | OERR   | RX9D   | 0000 000x                | 0000 000x                       |

| 19h                    | TXREG  | USART Tr                                         | USART Transmit Register 0000 0000 0000 0000 |        |       |       |        |        |        |                          |                                 |

| 8Ch                    | PIE1   | PSPIE <sup>(1)</sup>                             | ADIE                                        | RCIE   | TXIE  | SSPIE | CCP1IE | TMR2IE | TMR1IE | 0000 0000                | 0000 0000                       |