Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                         |

|----------------------------|-------------------------------------------------------------------------|

| Product Status             | Active                                                                  |

| Core Processor             | PIC                                                                     |

| Core Size                  | 8-Bit                                                                   |

| Speed                      | 20MHz                                                                   |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                                       |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                   |

| Number of I/O              | 22                                                                      |

| Program Memory Size        | 7KB (4K x 14)                                                           |

| Program Memory Type        | FLASH                                                                   |

| EEPROM Size                | -                                                                       |

| RAM Size                   | 192 x 8                                                                 |

| Voltage - Supply (Vcc/Vdd) | 4V ~ 5.5V                                                               |

| Data Converters            | A/D 5x8b                                                                |

| Oscillator Type            | External                                                                |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                      |

| Mounting Type              | Through Hole                                                            |

| Package / Case             | 28-DIP (0.300", 7.62mm)                                                 |

| Supplier Device Package    | 28-SPDIP                                                                |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16f73-e-sp |

|                            |                                                                         |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# 2.0 MEMORY ORGANIZATION

There are two memory blocks in each of these PICmicro<sup>®</sup> MCUs. The Program Memory and Data Memory have separate buses so that concurrent access can occur and is detailed in this section. The Program Memory can be read internally by user code (see Section 3.0).

Additional information on device memory may be found in the PICmicro<sup>™</sup> Mid-Range Reference Manual (DS33023).

# 2.1 Program Memory Organization

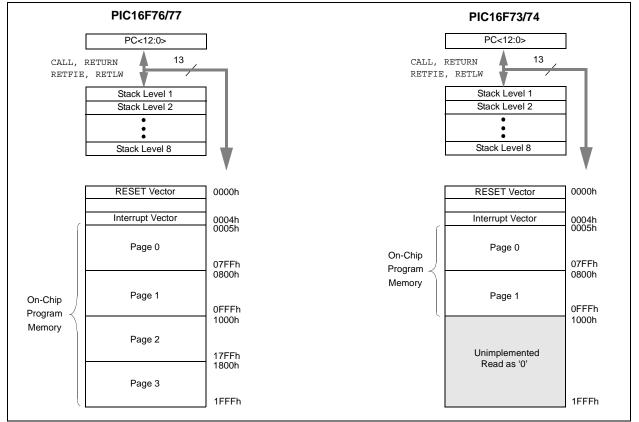

The PIC16F7X devices have a 13-bit program counter capable of addressing an 8K word x 14-bit program memory space. The PIC16F77/76 devices have 8K words of FLASH program memory and the PIC16F73/74 devices have 4K words. The program memory maps for PIC16F7X devices are shown in Figure 2-1. Accessing a location above the physically implemented address will cause a wraparound.

The RESET Vector is at 0000h and the Interrupt Vector is at 0004h.

# 2.2 Data Memory Organization

The Data Memory is partitioned into multiple banks, which contain the General Purpose Registers and the Special Function Registers. Bits RP1 (STATUS<6>) and RP0 (STATUS<5>) are the bank select bits:

| RP1:RP0 | Bank |

|---------|------|

| 00      | 0    |

| 01      | 1    |

| 10      | 2    |

| 11      | 3    |

Each bank extends up to 7Fh (128 bytes). The lower locations of each bank are reserved for the Special Function Registers. Above the Special Function Registers are General Purpose Registers, implemented as static RAM. All implemented banks contain Special Function Registers. Some frequently used Special Function Registers from one bank may be mirrored in another bank for code reduction and quicker access.

#### 2.2.1 GENERAL PURPOSE REGISTER FILE

The register file (shown in Figure 2-2 and Figure 2-3) can be accessed either directly, or indirectly, through the File Select Register FSR.

# FIGURE 2-1: PROGRAM MEMORY MAPS AND STACKS FOR PIC16F7X DEVICES

# PIC16F7X

| FIGL | JRE | 2-3: |

|------|-----|------|

|      |     |      |

# PIC16F74/73 REGISTER FILE MAP

| ŀ                                                                      | File<br>Address |                                           | File<br>Address |                           | File<br>Address | ļ                 | File<br>Addre |

|------------------------------------------------------------------------|-----------------|-------------------------------------------|-----------------|---------------------------|-----------------|-------------------|---------------|

| Indirect addr.(*)                                                      | 00h             | Indirect addr.(*)                         | 80h             | Indirect addr.(*)         | 100h            | Indirect addr.(*) | 180           |

| TMR0                                                                   | 01h             | OPTION_REG                                | 81h             | TMR0                      | 101h            | OPTION_REG        | 181           |

| PCL                                                                    | 02h             | PCL                                       | 82h             | PCL                       | 102h            | PCL               | 182           |

| STATUS                                                                 | 03h             | STATUS                                    | 83h             | STATUS                    | 103h            | STATUS            | 183           |

| FSR                                                                    | 04h             | FSR                                       | 84h             | FSR                       | 104h            | FSR               | 184           |

| PORTA                                                                  | 05h             | TRISA                                     | 85h             |                           | 105h            |                   | 185           |

| PORTB                                                                  | 06h             | TRISB                                     | 86h             | PORTB                     | 106h            | TRISB             | 186           |

| PORTC                                                                  | 07h             | TRISC                                     | 87h             |                           | 107h            |                   | 187           |

| PORTD <sup>(1)</sup>                                                   | 08h             | TRISD <sup>(1)</sup>                      | 88h             |                           | 108h            |                   | 188           |

| PORTE <sup>(1)</sup>                                                   | 09h             | TRISE <sup>(1)</sup>                      | 89h             |                           | 109h            |                   | 189           |

| PCLATH                                                                 | 0Ah             | PCLATH                                    | 8Ah             | PCLATH                    | 10Ah            | PCLATH            | 18A           |

| INTCON                                                                 | 0Bh             | INTCON                                    | 8Bh             | INTCON                    | 10Bh            | INTCON            | 18E           |

| PIR1                                                                   | 0Ch             | PIE1                                      | 8Ch             | PMDATA                    | 10Ch            | PMCON1            | 180           |

| PIR2                                                                   | 0Dh             | PIE2                                      | 8Dh             | PMADR                     | 10Dh            |                   | 180           |

| TMR1L                                                                  | 0Eh             | PCON                                      | 8Eh             | PMDATH                    | 10Eh            |                   | 18E           |

| TMR1H                                                                  | 0Fh             |                                           | 8Fh             | PMADRH                    | 10Fh            |                   | 18F           |

| T1CON                                                                  | 10h             |                                           | 90h             |                           | 110h            |                   | 190           |

| TMR2                                                                   | 11h             |                                           | 91h             |                           |                 |                   |               |

| T2CON                                                                  | 12h             | PR2                                       | 92h             |                           |                 |                   |               |

| SSPBUF                                                                 | 13h             | SSPADD                                    | 93h             |                           |                 |                   |               |

| SSPCON                                                                 | 14h             | SSPSTAT                                   | 94h             |                           |                 |                   |               |

| CCPR1L                                                                 | 15h             |                                           | 95h             |                           |                 |                   |               |

| CCPR1H                                                                 | 16h             |                                           | 96h             |                           |                 |                   |               |

| CCP1CON                                                                | 17h             |                                           | 97h             |                           |                 |                   |               |

| RCSTA                                                                  | 18h             | TXSTA                                     | 98h             |                           |                 |                   |               |

| TXREG                                                                  | 19h             | SPBRG                                     | 99h             |                           |                 |                   |               |

| RCREG                                                                  | 1Ah             |                                           | 9Ah             |                           |                 |                   |               |

| CCPR2L                                                                 | 1Bh             |                                           | 9Bh             |                           |                 |                   |               |

| CCPR2H                                                                 | 1Ch             |                                           | 9Ch             |                           |                 |                   |               |

| CCP2CON                                                                | 1Dh             |                                           | 9Dh             |                           |                 |                   |               |

| ADRES                                                                  | 1Eh             |                                           | 9Eh             |                           |                 |                   |               |

| ADCON0                                                                 | 1Fh             | ADCON1                                    | 9Fh             |                           | 1001            |                   | 4.4.0         |

|                                                                        | 20h             |                                           | A0h             |                           | 120h            |                   | 1A0           |

|                                                                        |                 |                                           | 7,011           |                           |                 |                   |               |

| General                                                                |                 | General                                   |                 |                           |                 |                   |               |

|                                                                        |                 | Purpose<br>Register                       |                 | accesses                  |                 | accesses          |               |

| -                                                                      |                 | -                                         |                 | 20h-7Fh                   |                 | A0h - FFh         | 4             |

| 96 Bytes                                                               |                 | 96 Bytes                                  |                 |                           | 16Fh<br>170b    |                   | 1EF<br>1FC    |

|                                                                        |                 |                                           |                 |                           | 17011           |                   |               |

| Bank 0                                                                 | 7Fh             | Bank 1                                    | FFh             | Bank 2                    | 17Fh            | Bank 3            | 1FF           |

| Purpose<br>Register<br>96 Bytes<br>Bank 0<br>Unimpleme<br>* Not a phys | ented data      | Purpose<br>Register<br>96 Bytes<br>Bank 1 | s, read as      | 20h-7Fh<br>Bank 2<br>'0'. | 170h            | A0h - FFh         |               |

x = Bit is unknown

#### **PCON Register** 2.2.2.8

The Power Control (PCON) register contains flag bits to allow differentiation between a Power-on Reset (POR), a Brown-out Reset (BOR), a Watchdog Reset (WDT) and an external MCLR Reset.

BOR is unknown on POR. It must be set by Note: the user and checked on subsequent RESETS to see if BOR is clear, indicating a brown-out has occurred. The BOR status bit is not predictable if the brown-out circuit is disabled (by clearing the BODEN bit in the configuration word).

#### **REGISTER 2-8:** PCON REGISTER (ADDRESS 8Eh)

- n = Value at POR reset

|         | U-0                                                                                   | U-0         | U-0           | U-0            | U-0         | U-0         | R/W-0         | R/W-1   |  |  |  |  |

|---------|---------------------------------------------------------------------------------------|-------------|---------------|----------------|-------------|-------------|---------------|---------|--|--|--|--|

|         | _                                                                                     | _           | _             |                | —           |             | POR           | BOR     |  |  |  |  |

|         | bit 7                                                                                 |             |               |                |             |             |               | bit 0   |  |  |  |  |

|         |                                                                                       |             |               |                |             |             |               |         |  |  |  |  |

| bit 7-2 | Unimplem                                                                              | ented: Rea  | d as '0'      |                |             |             |               |         |  |  |  |  |

| bit 1   | POR: Power-on Reset Status bit                                                        |             |               |                |             |             |               |         |  |  |  |  |

|         | 1 = No Power-on Reset occurred                                                        |             |               |                |             |             |               |         |  |  |  |  |

|         | 0 = A Power-on Reset occurred (must be set in software after a Power-on Reset occurs) |             |               |                |             |             |               |         |  |  |  |  |

| bit 0   | BOR: Brov                                                                             | vn-out Rese | t Status bit  |                |             |             |               |         |  |  |  |  |

|         | 1 = No Bro                                                                            | wn-out Res  | et occurred   |                |             |             |               |         |  |  |  |  |

|         | 0 = A Brow                                                                            | n-out Rese  | t occurred (m | lust be set in | software af | ter a Brown | -out Reset of | occurs) |  |  |  |  |

|         |                                                                                       |             |               |                |             |             |               |         |  |  |  |  |

|         | Legend:                                                                               |             |               |                |             |             |               |         |  |  |  |  |

|         | R = Reada                                                                             | ble bit     | W = W         | ritable bit    | U = Unim    | plemented l | bit, read as  | '0'     |  |  |  |  |

'0' = Bit is cleared

'1' = Bit is set

NOTES:

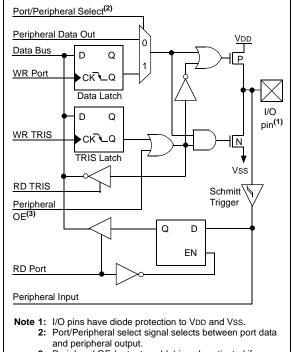

# 4.3 PORTC and the TRISC Register

PORTC is an 8-bit wide, bi-directional port. The corresponding data direction register is TRISC. Setting a TRISC bit (= '1') will make the corresponding PORTC pin an input (i.e., put the corresponding output driver in a Hi-Impedance mode). Clearing a TRISC bit (= '0') will make the corresponding PORTC pin an output (i.e., put the contents of the output latch on the selected pin).

PORTC is multiplexed with several peripheral functions (Table 4-5). PORTC pins have Schmitt Trigger input buffers.

When enabling peripheral functions, care should be taken in defining TRIS bits for each PORTC pin. Some peripherals override the TRIS bit to make a pin an output, while other peripherals override the TRIS bit to make a pin an input. Since the TRIS bit override is in effect while the peripheral is enabled, read-modify-write instructions (BSF, BCF, XORWF) with TRISC as destination should be avoided. The user should refer to the corresponding peripheral section for the correct TRIS bit settings, and to Section 13.1 for additional information on read-modify-write operations.

## FIGURE 4-5:

#### PORTC BLOCK DIAGRAM (PERIPHERAL OUTPUT OVERRIDE)

**3:** Peripheral OE (output enable) is only activated if peripheral select is active.

| Name            | Bit# | Buffer Type | Function                                                                                        |

|-----------------|------|-------------|-------------------------------------------------------------------------------------------------|

| RC0/T1OSO/T1CKI | bit0 | ST          | Input/output port pin or Timer1 oscillator output/Timer1 clock input.                           |

| RC1/T1OSI/CCP2  | bit1 | ST          | Input/output port pin or Timer1 oscillator input or Capture2 input/Compare2 output/PWM2 output. |

| RC2/CCP1        | bit2 | ST          | Input/output port pin or Capture1 input/Compare1 output/PWM1 output.                            |

| RC3/SCK/SCL     | bit3 | ST          | RC3 can also be the synchronous serial clock for both SPI and $I^2C$ modes.                     |

| RC4/SDI/SDA     | bit4 | ST          | RC4 can also be the SPI Data In (SPI mode) or Data I/O (I <sup>2</sup> C mode).                 |

| RC5/SDO         | bit5 | ST          | Input/output port pin or Synchronous Serial Port data output.                                   |

| RC6/TX/CK       | bit6 | ST          | Input/output port pin or USART Asynchronous Transmit or<br>Synchronous Clock.                   |

| RC7/RX/DT       | bit7 | ST          | Input/output port pin or USART Asynchronous Receive or Synchronous Data.                        |

# TABLE 4-5: PORTC FUNCTIONS

Legend: ST = Schmitt Trigger input

# TABLE 4-6: SUMMARY OF REGISTERS ASSOCIATED WITH PORTC

| Address | Name  | Bit 7 | Bit 6     | Bit 5     | Bit 4 | Bit 3     | Bit 2     | Bit 1 | Bit 0 | Value on:<br>POR,<br>BOR | Value on<br>all other<br>RESETS |

|---------|-------|-------|-----------|-----------|-------|-----------|-----------|-------|-------|--------------------------|---------------------------------|

| 07h     | PORTC | RC7   | RC6       | RC5       | RC4   | RC3       | RC2       | RC1   | RC0   | xxxx xxxx                | uuuu uuuu                       |

| 87h     | TRISC | PORTC | Data Dire | ection Re |       | 1111 1111 | 1111 1111 |       |       |                          |                                 |

Legend: x = unknown, u = unchanged

| Name       | Bit# | Buffer Type           | Function                                                                                                                                                                                                                          |

|------------|------|-----------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| RE0/RD/AN5 | bit0 | ST/TTL <sup>(1)</sup> | Input/output port pin or read control input in Parallel Slave Port mode or<br>analog input.<br>For RD (PSP mode):<br>1 = IDLE<br>0 = Read operation. Contents of PORTD register output to PORTD I/O<br>pins (if chip selected).   |

| RE1/WR/AN6 | bit1 | ST/TTL <sup>(1)</sup> | Input/output port pin or write control input in Parallel Slave Port mode<br>or analog input.<br>For WR (PSP mode):<br>1 = IDLE<br>0 = Write operation. Value of PORTD I/O pins latched into PORTD<br>register (if chip selected). |

| RE2/CS/AN7 | bit2 | ST/TTL <sup>(1)</sup> | Input/output port pin or chip select control input in Parallel Slave Port<br>mode or analog input.<br>For CS (PSP mode):<br>1 = Device is not selected<br>0 = Device is selected                                                  |

Legend: ST = Schmitt Trigger input, TTL = TTL input **Note 1:** Input buffers are Schmitt Triggers when in I/O mode and TTL buffers when in Parallel Slave Port mode.

| TABLE 4-10: SUMMARY OF REGISTERS ASSOCIATED WITH PORTE | <b>TABLE 4-10</b> : | SUMMARY OF REGISTERS ASSOCIATED WITH PORTE |

|--------------------------------------------------------|---------------------|--------------------------------------------|

|--------------------------------------------------------|---------------------|--------------------------------------------|

| Addr | Name   | Bit 7 | Bit 6 | Bit 5 | Bit 4   | Bit 3 | Bit 2                     | Bit 1 | Bit 0 | Value on:<br>POR,<br>BOR | Value on all<br>other<br>RESETS |

|------|--------|-------|-------|-------|---------|-------|---------------------------|-------|-------|--------------------------|---------------------------------|

| 09h  | PORTE  | —     | —     |       | —       | _     | RE2                       | RE1   | RE0   | xxx                      | uuu                             |

| 89h  | TRISE  | IBF   | OBF   | IBOV  | PSPMODE | _     | PORTE Data Direction bits |       |       | 0000 -111                | 0000 -111                       |

| 9Fh  | ADCON1 | —     | _     |       | _       | _     | PCFG2                     | PCFG1 | PCFG0 | 000                      | 000                             |

Legend: x = unknown, u = unchanged, - = unimplemented, read as '0'. Shaded cells are not used by PORTE.

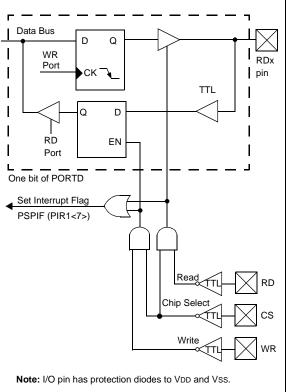

# 4.6 Parallel Slave Port

The Parallel Slave Port (PSP) is not implemented on the PIC16F73 or PIC16F76.

PORTD operates as an 8-bit wide Parallel Slave Port, or Microprocessor Port, when control bit PSPMODE (TRISE<4>) is set. In Slave mode, it is asynchronously readable and writable by an external system using the read control input pin RE0/RD, the write control input pin RE1/WR, and the chip select control input pin RE2/CS.

The PSP can directly interface to an 8-bit microprocessor data bus. The external microprocessor can read or write the PORTD latch as an 8-bit latch. Setting bit PSPMODE enables port pin RE0/RD to be the RD input, RE1/WR to be the WR input and RE2/CS to be the CS (chip select) input. For this functionality, the corresponding data direction bits of the TRISE register (TRISE<2:0>) must be configured as inputs (i.e., set). The A/D port configuration bits PCFG3:PCFG0 (ADCON1<3:0>) must be set to configure pins RE2:RE0 as digital I/O.

There are actually two 8-bit latches, one for data output (external reads) and one for data input (external writes). The firmware writes 8-bit data to the PORTD output data latch and reads data from the PORTD input data latch (note that they have the same address). In this mode, the TRISD register is ignored, since the external device is controlling the direction of data flow.

An external write to the PSP occurs when the  $\overline{CS}$  and  $\overline{WR}$  lines are both detected low. Firmware can read the actual data on the PORTD pins during this time. When either the CS or WR lines become high (level triggered), the data on the PORTD pins is latched, and the Input Buffer Full (IBF) status flag bit (TRISE<7>) and interrupt flag bit PSPIF (PIR1<7>) are set on the Q4 clock cycle, following the next Q2 cycle to signal the write is complete (Figure 4-9). Firmware clears the IBF flag by reading the latched PORTD data, and clears the PSPIF bit.

The Input Buffer Overflow (IBOV) status flag bit (TRISE<5>) is set if an external write to the PSP occurs while the IBF flag is set from a previous external write. The previous PORTD data is overwritten with the new data. IBOV is cleared by reading PORTD and clearing IBOV.

A read from the PSP occurs when both the  $\overline{CS}$  and  $\overline{RD}$  lines are detected low. The data in the PORTD output latch is output to the PORTD pins. The Output Buffer Full (OBF) status flag bit (TRISE<6>) is cleared immediately (Figure 4-10), indicating that the PORTD latch is being read, or has been read by the external bus. If firmware writes new data to the output latch during this time, it is immediately output to the PORTD pins, but OBF will remain cleared.

When either the  $\overline{CS}$  or  $\overline{RD}$  pins are detected high, the PORTD outputs are disabled, and the interrupt flag bit PSPIF is set on the Q4 clock cycle following the next Q2 cycle, indicating that the read is complete. OBF remains low until firmware writes new data to PORTD.

When not in PSP mode, the IBF and OBF bits are held clear. Flag bit IBOV remains unchanged. The PSPIF bit must be cleared by the user in firmware; the interrupt can be disabled by clearing the interrupt enable bit PSPIE (PIE1<7>).

# FIGURE 4-8:

## PORTD AND PORTE BLOCK DIAGRAM (PARALLEL SLAVE PORT)

## 9.3.2 MASTER MODE

Master mode of operation is supported in firmware using interrupt generation on the detection of the START and STOP conditions. The STOP (P) and START (S) bits are cleared from a RESET or when the SSP module is disabled. The STOP (P) and START (S) bits will toggle based on the START and STOP conditions. Control of the I<sup>2</sup>C bus may be taken when the P bit is set, or the bus is IDLE and both the S and P bits are clear.

In Master mode, the SCL and SDA lines are manipulated by clearing the corresponding TRISC<4:3> bit(s). The output level is always low, irrespective of the value(s) in PORTC<4:3>. So when transmitting data, a '1' data bit must have the TRISC<4> bit set (input) and a '0' data bit must have the TRISC<4> bit cleared (output). The same scenario is true for the SCL line with the TRISC<3> bit. Pull-up resistors must be provided externally to the SCL and SDA pins for proper operation of the I<sup>2</sup>C module.

The following events will cause SSP Interrupt Flag bit, SSPIF, to be set (SSP Interrupt will occur if enabled):

- START condition

- STOP condition

- Data transfer byte transmitted/received

Master mode of operation can be done with either the Slave mode IDLE (SSPM3:SSPM0 = 1011), or with the Slave active. When both Master and Slave modes are enabled, the software needs to differentiate the source(s) of the interrupt.

#### 9.3.3 MULTI-MASTER MODE

In Multi-Master mode, the interrupt generation on the detection of the START and STOP conditions, allows the determination of when the bus is free. The STOP (P) and START (S) bits are cleared from a RESET or when the SSP module is disabled. The STOP (P) and START (S) bits will toggle based on the START and STOP conditions. Control of the  $I^2C$  bus may be taken when bit P (SSPSTAT<4>) is set, or the bus is IDLE and both the S and P bits clear. When the bus is busy, enabling the SSP Interrupt will generate the interrupt when the STOP condition occurs.

In Multi-Master operation, the SDA line must be monitored to see if the signal level is the expected output level. This check only needs to be done when a high level is output. If a high level is expected and a low level is present, the device needs to release the SDA and SCL lines (set TRISC<4:3>). There are two stages where this arbitration can be lost, these are:

- Address Transfer

- Data Transfer

When the slave logic is enabled, the slave continues to receive. If arbitration was lost during the address transfer stage, communication to the device may be in progress. If addressed, an ACK pulse will be generated. If arbitration was lost during the data transfer stage, the device will need to retransfer the data at a later time.

| Address                | Name    | Bit 7                | Bit 6              | Bit 5                  | Bit 4     | Bit 3     | Bit 2       | Bit 1  | Bit 0  | Value on:<br>POR,<br>BOR | Value on<br>all other<br>RESETS |

|------------------------|---------|----------------------|--------------------|------------------------|-----------|-----------|-------------|--------|--------|--------------------------|---------------------------------|

| 0Bh, 8Bh,<br>10Bh,18Bh | INTCON  | GIE                  | PEIE               | TMR0IE                 | INTE      | RBIE      | TMR0IF      | INTF   | RBIF   | 0000 000x                | 0000 000u                       |

| 0Ch                    | PIR1    | PSPIF <sup>(1)</sup> | ADIF               | RCIF                   | TXIF      | SSPIF     | CCP1IF      | TMR2IF | TMR1IF | 0000 0000                | 0000 0000                       |

| 8Ch                    | PIE1    | PSPIE <sup>(1)</sup> | ADIE               | RCIE                   | TXIE      | SSPIE     | CCP1IE      | TMR2IE | TMR1IE | 0000 0000                | 0000 0000                       |

| 13h                    | SSPBUF  | Synchrono            | us Serial          | Port Rece              | eive Buff | er/Transn | nit Registe | ər     |        | xxxx xxxx                | uuuu uuuu                       |

| 93h                    | SSPADD  | Synchrono            | us Serial          | Port (I <sup>2</sup> C | mode) A   | ddress R  | egister     |        |        | 0000 0000                | 0000 0000                       |

| 14h                    | SSPCON  | WCOL                 | SSPOV              | SSPEN                  | CKP       | SSPM3     | SSPM2       | SSPM1  | SSPM0  | 0000 0000                | 0000 0000                       |

| 94h                    | SSPSTAT | SMP <sup>(2)</sup>   | CKE <sup>(2)</sup> | D/A                    | Р         | S         | R/W         | UA     | BF     | 0000 0000                | 0000 0000                       |

| 87h                    | TRISC   | PORTC Da             | ata Direct         | ion Regist             | ter       | •         | •           |        | •      | 1111 1111                | 1111 1111                       |

TABLE 9-3:

REGISTERS ASSOCIATED WITH I<sup>2</sup>C OPERATION

Legend: x = unknown, u = unchanged, - = unimplemented locations read as '0'. Shaded cells are not used by SSP module in I<sup>2</sup>C mode. **Note 1:** PSPIF and PSPIE are reserved on the PIC16F73/76; always maintain these bits clear.

2: Maintain these bits clear in I<sup>2</sup>C mode.

# 10.1 USART Baud Rate Generator (BRG)

The BRG supports both the Asynchronous and Synchronous modes of the USART. It is a dedicated 8-bit baud rate generator. The SPBRG register controls the period of a free running 8-bit timer. In Asynchronous mode, bit BRGH (TXSTA<2>) also controls the baud rate. In Synchronous mode, bit BRGH is ignored. Table 10-1 shows the formula for computation of the baud rate for different USART modes which only apply in Master mode (internal clock).

Given the desired baud rate and FOSC, the nearest integer value for the SPBRG register can be calculated using the formula in Table 10-1. From this, the error in baud rate can be determined. It may be advantageous to use the high baud rate (BRGH = 1), even for slower baud clocks. This is because the FOSC/(16(X + 1)) equation can reduce the baud rate error in some cases.

Writing a new value to the SPBRG register causes the BRG timer to be reset (or cleared). This ensures the BRG does not wait for a timer overflow before outputting the new baud rate.

# 10.1.1 SAMPLING

The data on the RC7/RX/DT pin is sampled three times by a majority detect circuit to determine if a high or a low level is present at the RX pin.

# TABLE 10-1: BAUD RATE FORMULA

| SYNC | BRGH = 0 (Low Speed)                      | BRGH = 1 (High Speed)      |

|------|-------------------------------------------|----------------------------|

| 0    | (Asynchronous) Baud Rate = FOSC/(64(X+1)) | Baud Rate = Fosc/(16(X+1)) |

| 1    | (Synchronous) Baud Rate = Fosc/(4(X+1))   | N/A                        |

X = value in SPBRG (0 to 255)

# TABLE 10-2: REGISTERS ASSOCIATED WITH BAUD RATE GENERATOR

| Address | Name  | Bit 7                             | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 | Value on:<br>POR,<br>BOR | Value on<br>all other<br>RESETS |

|---------|-------|-----------------------------------|-------|-------|-------|-------|-------|-------|-------|--------------------------|---------------------------------|

| 98h     | TXSTA | CSRC                              | TX9   | TXEN  | SYNC  | _     | BRGH  | TRMT  | TX9D  | 0000 -010                | 0000 -010                       |

| 18h     | RCSTA | SPEN                              | RX9   | SREN  | CREN  | —     | FERR  | OERR  | RX9D  | 0000 -00x                | 0000 -00x                       |

| 99h     | SPBRG | PBRG Baud Rate Generator Register |       |       |       |       |       |       |       | 0000 0000                | 0000 0000                       |

Legend: x = unknown, - = unimplemented, read as '0'. Shaded cells are not used by the BRG.

# 10.2 USART Asynchronous Mode

In this mode, the USART uses standard non-return-tozero (NRZ) format (one START bit, eight or nine data bits, and one STOP bit). The most common data format is 8-bits. An on-chip, dedicated, 8-bit baud rate generator can be used to derive standard baud rate frequencies from the oscillator. The USART transmits and receives the LSb first. The USART's transmitter and receiver are functionally independent, but use the same data format and baud rate. The baud rate generator produces a clock, either x16 or x64 of the bit shift rate, depending on bit BRGH (TXSTA<2>). Parity is not supported by the hardware, but can be implemented in software (and stored as the ninth data bit). Asynchronous mode is stopped during SLEEP.

Asynchronous mode is selected by clearing bit SYNC (TXSTA<4>).

The USART Asynchronous module consists of the following important elements:

- · Baud Rate Generator

- Sampling Circuit

- Asynchronous Transmitter

- Asynchronous Receiver

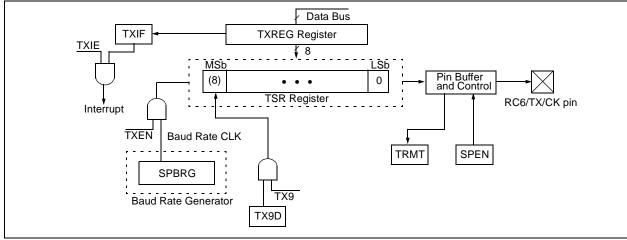

## 10.2.1 USART ASYNCHRONOUS TRANSMITTER

The USART transmitter block diagram is shown in Figure 10-1. The heart of the transmitter is the transmit (serial) shift register (TSR). The shift register obtains its data from the read/write transmit buffer, TXREG. The TXREG register is loaded with data by firmware. The TSR register is not loaded until the STOP bit has been transmitted from the previous load. As soon as the STOP bit is transmitted, the TSR is loaded with new data from the TXREG register (if available). Once the TXREG register transfers the data to the TSR register, the TXREG register is empty. One instruction cycle later, flag bit TXIF (PIR1<4>) and flag bit TRMT (TXSTA<1>)

are set. The TXIF interrupt can be enabled/disabled by setting/clearing enable bit TXIE (PIE1<4>). Flag bit TXIF will be set, regardless of the state of enable bit TXIE and cannot be cleared in software. It will reset only when new data is loaded into the TXREG register. While flag bit TXIF indicates the status of the TXREG register, another bit TRMT (TXSTA<1>) shows the status of the TSR register. Status bit TRMT is a read only bit, which is set one instruction cycle after the TSR register becomes empty, and is cleared one instruction cycle after the TSR register is loaded. No interrupt logic is tied to this bit, so the user has to poll this bit in order to determine if the TSR register is empty.

| Note 1: | The TSR register is not mapped in data      |

|---------|---------------------------------------------|

|         | memory, so it is not available to the user. |

| 2:      | Flag bit TXIF is set when enable bit TXEN   |

is set. TXIF is cleared by loading TXREG.

Transmission is enabled by setting enable bit TXEN (TXSTA<5>). The actual transmission will not occur until the TXREG register has been loaded with data and the baud rate generator (BRG) has produced a shift clock (Figure 10-2). The transmission can also be started by first loading the TXREG register and then setting enable bit TXEN. Normally, when transmission is first started, the TSR register is empty. At that point, transfer to the TXREG register will result in an immediate transfer to TSR, resulting in an empty TXREG. A back-to-back transfer is thus possible (Figure 10-3). Clearing enable bit TXEN during a transmission will cause the transmission to be aborted and will reset the transmitter. As a result, the RC6/TX/CK pin will revert to hi-impedance.

In order to select 9-bit transmission, transmit bit TX9 (TXSTA<6>) should be set and the ninth bit should be written to TX9D (TXSTA<0>). The ninth bit must be written before writing the 8-bit data to the TXREG register. This is because a data write to the TXREG register can result in an immediate transfer of the data to the TSR register (if the TSR is empty). In such a case, an incorrect ninth data bit may be loaded in the TSR register.

# FIGURE 10-1: USART TRANSMIT BLOCK DIAGRAM

# 10.3 USART Synchronous Master Mode

In Synchronous Master mode, the data is transmitted in a half-duplex manner (i.e., transmission and reception do not occur at the same time). When transmitting data, the reception is inhibited and vice versa. Synchronous mode is entered by setting bit SYNC (TXSTA<4>). In addition, enable bit SPEN (RCSTA<7>) is set in order to configure the RC6/TX/CK and RC7/RX/DT I/O pins to CK (clock) and DT (data) lines, respectively. The Master mode indicates that the processor transmits the master clock on the CK line. The Master mode is entered by setting bit CSRC (TXSTA<7>).

#### 10.3.1 USART SYNCHRONOUS MASTER TRANSMISSION

The USART transmitter block diagram is shown in Figure 10-1. The heart of the transmitter is the transmit (serial) shift register (TSR). The shift register obtains its data from the read/write transmit buffer register TXREG. The TXREG register is loaded with data in software. The TSR register is not loaded until the last bit has been transmitted from the previous load. As soon as the last bit is transmitted, the TSR is loaded with new data from the TXREG (if available). Once the TXREG register transfers the data to the TSR register (occurs in one TCYCLE), the TXREG is empty and interrupt bit TXIF (PIR1<4>) is set. The interrupt can be enabled/disabled by setting/clearing enable bit TXIE (PIE1<4>). Flag bit TXIF will be set, regardless of the state of enable bit TXIE and cannot be cleared in software. It will reset only when new data is loaded into the TXREG register. While flag bit TXIF indicates the status of the TXREG register, another bit TRMT (TXSTA<1>) shows the status of the TSR register. TRMT is a read only bit, which is set when the TSR is empty. No interrupt logic is tied to this bit, so the user has to poll this bit in order to determine if the TSR register is empty. The TSR is not mapped in data memory, so it is not available to the user.

Transmission is enabled by setting enable bit TXEN (TXSTA<5>). The actual transmission will not occur until the TXREG register has been loaded with data. The first data bit will be shifted out on the next available rising edge of the clock on the CK line. Data out is stable around the falling edge of the synchronous clock (Figure 10-6). The transmission can also be started by first loading the TXREG register and then setting bit TXEN (Figure 10-7). This is advantageous when slow baud rates are selected, since the BRG is kept in RESET when bits TXEN, CREN and SREN are clear. Setting enable bit TXEN will start the BRG, creating a shift clock immediately. Normally, when transmission is first started, the TSR register is empty, so a transfer to the TXREG register will result in an immediate transfer to TSR, resulting in an empty TXREG. Back-to-back transfers are possible.

Clearing enable bit TXEN during a transmission will cause the transmission to be aborted and will reset the transmitter. The DT and CK pins will revert to hiimpedance. If either bit CREN or bit SREN is set during a transmission, the transmission is aborted and the DT pin reverts to a hi-impedance state (for a reception). The CK pin will remain an output if bit CSRC is set (internal clock). The transmitter logic, however, is not reset, although it is disconnected from the pins. In order to reset the transmitter, the user has to clear bit TXEN. If bit SREN is set (to interrupt an on-going transmission and receive a single word), then after the single word is received, bit SREN will be cleared and the serial port will revert back to transmitting, since bit TXEN is still set. The DT line will immediately switch from Hiimpedance Receive mode to transmit and start driving. To avoid this, bit TXEN should be cleared.

In order to select 9-bit transmission, the TX9 (TXSTA<6>) bit should be set and the ninth bit should be written to bit TX9D (TXSTA<0>). The ninth bit must be written before writing the 8-bit data to the TXREG register. This is because a data write to the TXREG can result in an immediate transfer of the data to the TSR register (if the TSR is empty). If the TSR was empty and the TXREG was written before writing the "new" TX9D, the "present" value of bit TX9D is loaded.

Steps to follow when setting up a Synchronous Master Transmission:

- 1. Initialize the SPBRG register for the appropriate baud rate (Section 10.1).

- 2. Enable the synchronous master serial port by setting bits SYNC, SPEN and CSRC.

- 3. If interrupts are desired, set enable bit TXIE.

- 4. If 9-bit transmission is desired, set bit TX9.

- 5. Enable the transmission by setting bit TXEN.

- 6. If 9-bit transmission is selected, the ninth bit should be loaded in bit TX9D.

- 7. Start transmission by loading data to the TXREG register.

- 8. If using interrupts, ensure that GIE and PEIE in the INTCON register are set.

| Address                | Name                               | Bit 7                | Bit 6    | Bit 5   | Bit 4 | Bit 3 | Bit 2  | Bit 1  | Bit 0  | Value on:<br>POR,<br>BOR | Value on<br>all other<br>RESETS |

|------------------------|------------------------------------|----------------------|----------|---------|-------|-------|--------|--------|--------|--------------------------|---------------------------------|

| 0Bh, 8Bh,<br>10Bh,18Bh | INTCON                             | GIE                  | PEIE     | TMR0IE  | INTE  | RBIE  | TMR0IF | INTF   | RBIF   | 0000 000x                | 0000 000u                       |

| 0Ch                    | PIR1                               | PSPIF <sup>(1)</sup> | ADIF     | RCIF    | TXIF  | SSPIF | CCP1IF | TMR2IF | TMR1IF | 0000 0000                | 0000 0000                       |

| 18h                    | RCSTA                              | SPEN                 | RX9      | SREN    | CREN  | ADDEN | FERR   | OERR   | RX9D   | 0000 000x                | 0000 000x                       |

| 19h                    | TXREG                              | USART Tr             | ansmit R | egister |       |       |        |        |        | 0000 0000                | 0000 0000                       |

| 8Ch                    | PIE1                               | PSPIE <sup>(1)</sup> | ADIE     | RCIE    | TXIE  | SSPIE | CCP1IE | TMR2IE | TMR1IE | 0000 0000                | 0000 0000                       |

| 98h                    | TXSTA                              | CSRC                 | TX9      | TXEN    | SYNC  | —     | BRGH   | TRMT   | TX9D   | 0000 -010                | 0000 -010                       |

| 99h                    | SPBRG Baud Rate Generator Register |                      |          |         |       |       |        |        |        | 0000 0000                | 0000 0000                       |

Legend: x = unknown, - = unimplemented, read as '0'. Shaded cells are not used for synchronous slave transmission.

Note 1: Bits PSPIE and PSPIF are reserved on the PIC16F73/76 devices; always maintain these bits clear.

## 10.4.2 USART SYNCHRONOUS SLAVE RECEPTION

The operation of the Synchronous Master and Slave modes is identical, except in the case of the SLEEP mode. Bit SREN is a "don't care" in Slave mode.

If receive is enabled by setting bit CREN prior to the SLEEP instruction, then a word may be received during SLEEP. On completely receiving the word, the RSR register will transfer the data to the RCREG register and if enable bit RCIE bit is set, the interrupt generated will wake the chip from SLEEP. If the global interrupt is enabled, the program will branch to the interrupt vector (0004h).

Follow these steps when setting up a Synchronous Slave Reception:

- Enable the synchronous master serial port by setting bits SYNC and SPEN and clearing bit CSRC.

- 2. If interrupts are desired, set enable bit RCIE.

- 3. If 9-bit reception is desired, set bit RX9.

- 4. To enable reception, set enable bit CREN.

- 5. Flag bit RCIF will be set when reception is complete and an interrupt will be generated, if enable bit RCIE was set.

- Read the RCSTA register to get the ninth bit (if enabled) and determine if any error occurred during reception.

- 7. Read the 8-bit received data by reading the RCREG register.

- 8. If any error occurred, clear the error by clearing bit CREN.

- 9. If using interrupts, ensure that GIE and PEIE in the INTCON register are set.

| Address                | Name                                 | Bit 7                | Bit 6    | Bit 5   | Bit 4 | Bit 3 | Bit 2  | Bit 1  | Bit 0  | Value on:<br>POR,<br>BOR | Value on<br>all other<br>RESETS |

|------------------------|--------------------------------------|----------------------|----------|---------|-------|-------|--------|--------|--------|--------------------------|---------------------------------|

| 0Bh, 8Bh,<br>10Bh,18Bh | INTCON                               | GIE                  | PEIE     | TMR0IE  | INTE  | RBIE  | TMR0IF | INTF   | RBIF   | 0000 000x                | 0000 000u                       |

| 0Ch                    | PIR1                                 | PSPIF <sup>(1)</sup> | ADIF     | RCIF    | TXIF  | SSPIF | CCP1IF | TMR2IF | TMR1IF | 0000 0000                | 0000 0000                       |

| 18h                    | RCSTA                                | SPEN                 | RX9      | SREN    | CREN  | ADDEN | FERR   | OERR   | RX9D   | x000 0000x               | 0000 000x                       |

| 1Ah                    | RCREG                                | USART R              | eceive R | egister |       |       |        |        |        | 0000 0000                | 0000 0000                       |

| 8Ch                    | PIE1                                 | PSPIE <sup>(1)</sup> | ADIE     | RCIE    | TXIE  | SSPIE | CCP1IE | TMR2IE | TMR1IE | 0000 0000                | 0000 0000                       |

| 98h                    | TXSTA                                | CSRC                 | TX9      | TXEN    | SYNC  | —     | BRGH   | TRMT   | TX9D   | 0000 -010                | 0000 -010                       |

| 99h                    | h SPBRG Baud Rate Generator Register |                      |          |         |       |       |        |        |        | 0000 0000                | 0000 0000                       |

## TABLE 10-10: REGISTERS ASSOCIATED WITH SYNCHRONOUS SLAVE RECEPTION

Legend: x = unknown, - = unimplemented, read as '0'. Shaded cells are not used for synchronous slave reception. **Note 1:** Bits PSPIE and PSPIF are reserved on the PIC16F73/76 devices, always maintain these bits clear.

#### TABLE 12-2: CAPACITOR SELECTION FOR CRYSTAL OSCILLATOR (FOR DESIGN GUIDANCE ONLY)

| Osc Type | Crystal<br>Freq | Typical Capacitor Values<br>Tested: |       |  |  |  |

|----------|-----------------|-------------------------------------|-------|--|--|--|

|          | ITEG            | C1                                  | C2    |  |  |  |

| LP       | 32 kHz          | 33 pF                               | 33 pF |  |  |  |

|          | 200 kHz         | 15 pF                               | 15 pF |  |  |  |

| XT       | 200 kHz         | 56 pF                               | 56 pF |  |  |  |

|          | 1 MHz           | 15 pF                               | 15 pF |  |  |  |

|          | 4 MHz           | 15 pF                               | 15 pF |  |  |  |

| HS       | 4 MHz           | 15 pF                               | 15 pF |  |  |  |

|          | 8 MHz           | 15 pF                               | 15 pF |  |  |  |

|          | 20 MHz          | 15 pF                               | 15 pF |  |  |  |

#### Capacitor values are for design guidance only.

These capacitors were tested with the crystals listed below for basic start-up and operation. These values were not optimized.

Different capacitor values may be required to produce acceptable oscillator operation. The user should test the performance of the oscillator over the expected VDD and temperature range for the application.

See the notes following this table for additional information.

|                              | Crystals Used:         |  |  |  |  |  |  |  |

|------------------------------|------------------------|--|--|--|--|--|--|--|

| 32 kHz Epson C-001R32.768K-A |                        |  |  |  |  |  |  |  |

| 200 kHz                      | STD XTL 200.000KHz     |  |  |  |  |  |  |  |

| 1 MHz                        | ECS ECS-10-13-1        |  |  |  |  |  |  |  |

| 4 MHz                        | ECS ECS-40-20-1        |  |  |  |  |  |  |  |

| 8 MHz                        | EPSON CA-301 8.000M-C  |  |  |  |  |  |  |  |

| 20 MHz                       | EPSON CA-301 20.000M-C |  |  |  |  |  |  |  |

- **Note 1:** Higher capacitance increases the stability of oscillator, but also increases the start-up time.

- 2: Since each resonator/crystal has its own characteristics, the user should consult the resonator/crystal manufacturer for appropriate values of external components.

- 3: Rs may be required in HS mode, as well as XT mode, to avoid overdriving crystals with low drive level specification.

- **4:** Always verify oscillator performance over the VDD and temperature range that is expected for the application.

#### 12.2.3 RC OSCILLATOR

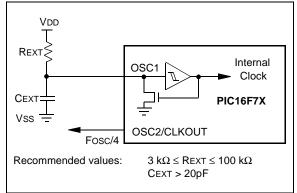

For timing insensitive applications, the "RC" device option offers additional cost savings. The RC oscillator frequency is a function of the supply voltage, the resistor (REXT) and capacitor (CEXT) values, and the operating temperature. In addition to this, the oscillator frequency will vary from unit to unit due to normal process parameter variation. Furthermore, the difference in lead frame capacitance between package types will also affect the oscillation frequency, especially for low CEXT values. The user also needs to take into account variation due to tolerance of external R and C components used. Figure 12-3 shows how the R/C combination is connected to the PIC16F7X.

# 13.0 INSTRUCTION SET SUMMARY

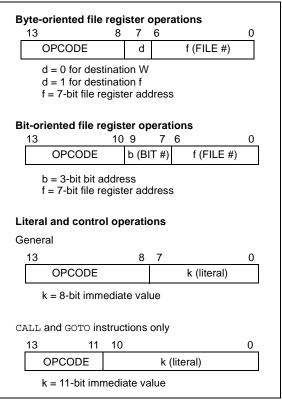

The PIC16 instruction set is highly orthogonal and is comprised of three basic categories:

- Byte-oriented operations

- Bit-oriented operations

- Literal and control operations

Each PIC16 instruction is a 14-bit word divided into an **opcode**, which specifies the instruction type and one or more **operands**, which further specify the operation of the instruction. The formats for each of the categories are presented in Figure 13-1, while the various opcode fields are summarized in Table 13-1.

Table 13-2 lists the instructions recognized by the MPASM<sup>™</sup> Assembler. A complete description of each instruction is also available in the PICmicro<sup>™</sup> Mid-Range Reference Manual (DS33023).

For **byte-oriented** instructions, ' $\pm$ ' represents a file register designator and 'a' represents a destination designator. The file register designator specifies which file register is to be used by the instruction.

The destination designator specifies where the result of the operation is to be placed. If 'd' is zero, the result is placed in the W register. If 'd' is one, the result is placed in the file register specified in the instruction.

For **bit-oriented** instructions, 'b' represents a bit field designator, which selects the bit affected by the operation, while 'f' represents the address of the file in which the bit is located.

For **literal and control** operations, 'k' represents an eight- or eleven-bit constant or literal value

One instruction cycle consists of four oscillator periods; for an oscillator frequency of 4 MHz, this gives a normal instruction execution time of 1  $\mu$ s. All instructions are executed within a single instruction cycle, unless a conditional test is true, or the program counter is changed as a result of an instruction. When this occurs, the execution takes two instruction cycles, with the second cycle executed as a NOP.

| Note: | To maintain upward compatibility with    |  |  |  |  |  |  |  |  |

|-------|------------------------------------------|--|--|--|--|--|--|--|--|

|       | future PIC16F7X products, do not use the |  |  |  |  |  |  |  |  |

|       | OPTION and TRIS instructions.            |  |  |  |  |  |  |  |  |

All instruction examples use the format '0xhh' to represent a hexadecimal number, where 'h' signifies a hexadecimal digit.

# 13.1 READ-MODIFY-WRITE OPERATIONS

Any instruction that specifies a file register as part of the instruction performs a Read-Modify-Write (R-M-W) operation. The register is read, the data is modified, and the result is stored according to either the instruction, or the destination designator 'd'. A read operation is performed on a register even if the instruction writes to that register. For example, a "clrf PORTB" instruction will read PORTB, clear all the data bits, then write the result back to PORTB. This example would have the unintended result that the condition that sets the RBIF flag would be cleared for pins configured as inputs and using the PORTB interrupt-on-change feature.

# TABLE 13-1: OPCODE FIELD DESCRIPTIONS

| Field | Description                                                                                                                                                                     |

|-------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| f     | Register file address (0x00 to 0x7F)                                                                                                                                            |

| W     | Working register (accumulator)                                                                                                                                                  |

| b     | Bit address within an 8-bit file register                                                                                                                                       |

| k     | Literal field, constant data or label                                                                                                                                           |

| x     | Don't care location (= 0 or 1).<br>The assembler will generate code with $x = 0$ .<br>It is the recommended form of use for<br>compatibility with all Microchip software tools. |

| d     | Destination select; $d = 0$ : store result in W,<br>d = 1: store result in file register f.<br>Default is $d = 1$ .                                                             |

| PC    | Program Counter                                                                                                                                                                 |

| TO    | Time-out bit                                                                                                                                                                    |

| PD    | Power-down bit                                                                                                                                                                  |

# FIGURE 13-1: GENERAL FORMAT FOR INSTRUCTIONS

| Param<br>No. | Symbol                | Characteristic                                                        | Min                                           | Тур†        | Max      | Units     | Conditions |  |

|--------------|-----------------------|-----------------------------------------------------------------------|-----------------------------------------------|-------------|----------|-----------|------------|--|

| 70*          | TssL2scH,<br>TssL2scL | $\overline{SS}\downarrow$ to SCK $\downarrow$ or SCK $\uparrow$ input | Тсү                                           |             | —        | ns        |            |  |

| 71*          | TscH                  | SCK input high time (Slave mo                                         | de)                                           | TCY + 20    | _        | —         | ns         |  |

| 72*          | TscL                  | SCK input low time (Slave mod                                         | le)                                           | TCY + 20    | _        | —         | ns         |  |

| 73*          | TdiV2scH,<br>TdiV2scL | Setup time of SDI data input to                                       | SCK edge                                      | 100         | _        | —         | ns         |  |

| 74*          | TscH2diL,<br>TscL2diL | Hold time of SDI data input to S                                      | 100                                           |             | —        | ns        |            |  |

| 75*          | TdoR                  | SDO data output rise time                                             | Standard( <b>F</b> )<br>Extended( <b>LF</b> ) | _           | 10<br>25 | 25<br>50  | ns<br>ns   |  |

| 76*          | TdoF                  | SDO data output fall time                                             | ·                                             | —           | 10       | 25        | ns         |  |

| 77*          | TssH2doZ              | SS↑ to SDO output hi-impedan                                          | се                                            | 10          | _        | 50        | ns         |  |

| 78*          | TscR                  | SCK output rise time<br>(Master mode)                                 | Standard( <b>F</b> )<br>Extended( <b>LF</b> ) | _           | 10<br>25 | 25<br>50  | ns<br>ns   |  |

| 79*          | TscF                  | SCK output fall time (Master m                                        | ode)                                          | _           | 10       | 25        | ns         |  |

| 80*          | TscH2doV,<br>TscL2doV | SDO data output valid after<br>SCK edge                               | Standard( <b>F</b> )<br>Extended( <b>LF</b> ) | _           |          | 50<br>145 | ns<br>ns   |  |

| 81*          | TdoV2scH,<br>TdoV2scL | SDO data output setup to SCK                                          | Тсу                                           |             |          | ns        |            |  |

| 82*          | TssL2doV              | SDO data output valid after SS                                        | —                                             | _           | 50       | ns        |            |  |

| 83*          | TscH2ssH,<br>TscL2ssH | SS ↑ after SCK edge                                                   |                                               | 1.5Tcy + 40 |          | —         | ns         |  |

#### TABLE 15-7: SPI MODE REQUIREMENTS

† Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

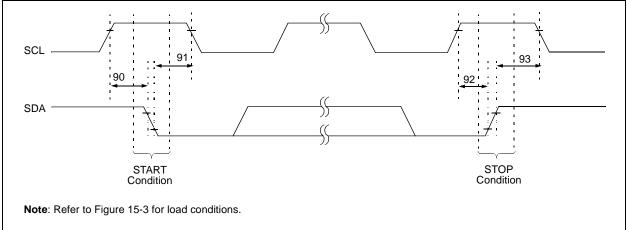

#### FIGURE 15-15: I<sup>2</sup>C BUS START/STOP BITS TIMING

| Param.<br>No. | Symbol  | Characte               | eristic      | Min        | Max  | Units | Conditions                                  |

|---------------|---------|------------------------|--------------|------------|------|-------|---------------------------------------------|

| 100*          | Тнідн   | Clock high time        | 100 kHz mode | 4.0        |      | μs    | Device must operate at a minimum of 1.5 MHz |

|               |         |                        | 400 kHz mode | 0.6        |      | μs    | Device must operate at a minimum of 10 MHz  |

|               |         |                        | SSP Module   | 1.5Tcy     |      |       |                                             |

| 101*          | TLOW    | Clock low time         | 100 kHz mode | 4.7        |      | μs    | Device must operate at a minimum of 1.5 MHz |

|               |         |                        | 400 kHz mode | 1.3        |      | μs    | Device must operate at a minimum of 10 MHz  |

|               |         |                        | SSP Module   | 1.5Tcy     | _    |       |                                             |

| 102*          | Tr      | SDA and SCL rise       | 100 kHz mode | —          | 1000 | ns    |                                             |

|               |         | time                   | 400 kHz mode | 20 + 0.1Св | 300  | ns    | CB is specified to be from 10 - 400 pF      |

| 103* TF       | TF      | SDA and SCL fall       | 100 kHz mode | —          | 300  | ns    |                                             |

|               | ti      | time                   | 400 kHz mode | 20 + 0.1Св | 300  | ns    | CB is specified to be from 10 - 400 pF      |

| 90*           | TSU:STA | START condition        | 100 kHz mode | 4.7        |      | μs    | Only relevant for                           |

|               |         | setup time             | 400 kHz mode | 0.6        |      | μs    | Repeated START condition                    |

| 91*           | THD:STA | START condition        | 100 kHz mode | 4.0        | _    | μs    | After this period the first                 |

|               |         | hold time              | 400 kHz mode | 0.6        | _    | μs    | clock pulse is generated                    |

| 106*          | THD:DAT | Data input hold time   | 100 kHz mode | 0          | —    | ns    |                                             |

|               |         |                        | 400 kHz mode | 0          | 0.9  | μs    |                                             |

| 107*          | TSU:DAT | Data input setup       | 100 kHz mode | 250        | —    | ns    | (Note 2)                                    |

|               |         | time                   | 400 kHz mode | 100        | —    | ns    |                                             |

| 92*           | Tsu:sto | STOP condition         | 100 kHz mode | 4.7        | —    | μs    |                                             |

|               |         | setup time             | 400 kHz mode | 0.6        | _    | μs    |                                             |

| 109*          | ΤΑΑ     | Output valid from      | 100 kHz mode | —          | 3500 | ns    | (Note 1)                                    |

|               |         | clock                  | 400 kHz mode | —          | —    | ns    |                                             |

| 110*          | TBUF    | Bus free time          | 100 kHz mode | 4.7        | _    | μs    | Time the bus must be free                   |

|               |         |                        | 400 kHz mode | 1.3        | —    | μs    | before a new transmission<br>can start      |

|               | Св      | Bus capacitive loading | ng           | -          | 400  | pF    |                                             |

# TABLE 15-9: I<sup>2</sup>C BUS DATA REQUIREMENTS

\* These parameters are characterized but not tested.

**Note 1:** As a transmitter, the device must provide this internal minimum delay time to bridge the undefined region (min. 300 ns) of the falling edge of SCL to avoid unintended generation of START or STOP conditions.

2: A Fast mode (400 kHz) I<sup>2</sup>C bus device can be used in a Standard mode (100 kHz) I<sup>2</sup>C bus system, but the requirement TsU:DAT ≥ 250 ns must then be met. This will automatically be the case if the device does not stretch the LOW period of the SCL signal. If such a device does stretch the LOW period of the SCL signal, it must output the next data bit to the SDA line TR max. + TSU:DAT = 1000 + 250 = 1250 ns (according to the Standard mode I<sup>2</sup>C bus specification), before the SCL line is released.

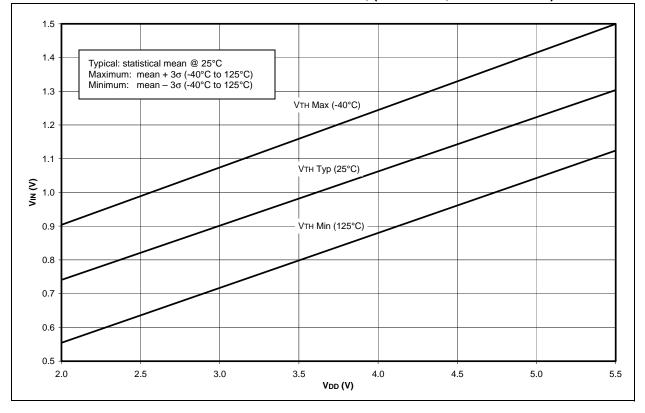

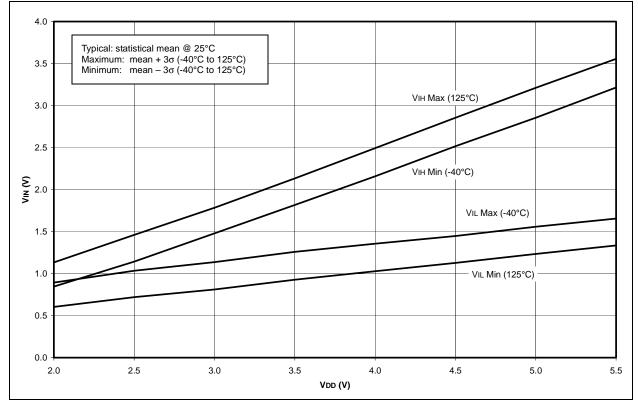

#### FIGURE 16-19: MINIMUM AND MAXIMUM VIN vs. VDD, (TTL INPUT, -40°C TO 125°C)

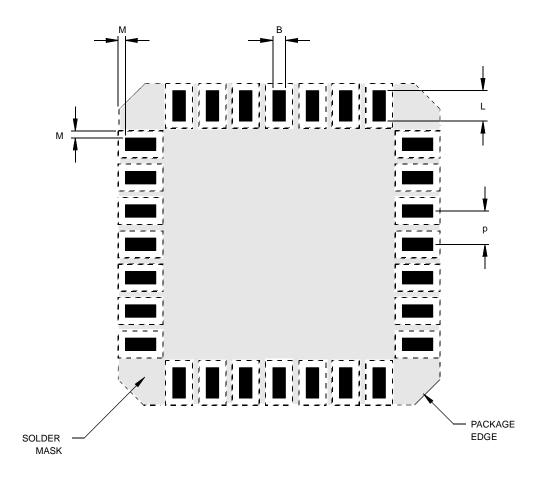

28-Lead Plastic Micro Leadframe Package (MF) 6x6 mm Body (MLF) (Continued)

|                    | ι             | Units |      | INCHES   |      | М    | ILLIMETERS* |      |

|--------------------|---------------|-------|------|----------|------|------|-------------|------|

|                    | Dimension Lim | nits  | MIN  | NOM      | MAX  | MIN  | NOM         | MAX  |

| Pitch              |               | р     |      | .026 BSC |      |      | 0.65 BSC    |      |

| Pad Width          |               | В     | .009 | .011     | .014 | 0.23 | 0.28        | 0.35 |

| Pad Length         |               | L     | .020 | .024     | .030 | 0.50 | 0.60        | 0.75 |

| Pad to Solder Mask |               | М     | .005 |          | .006 | 0.13 |             | 0.15 |

\*Controlling Parameter

Drawing No. C04-2114

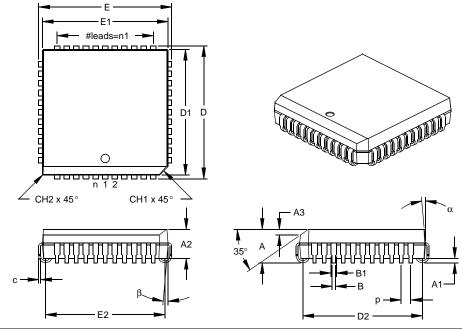

# 44-Lead Plastic Leaded Chip Carrier (L) – Square (PLCC)

|                          | Units     |      | INCHES* |      | Μ     | IILLIMETERS | 5     |

|--------------------------|-----------|------|---------|------|-------|-------------|-------|

| Dimensi                  | on Limits | MIN  | NOM     | MAX  | MIN   | NOM         | MAX   |

| Number of Pins           | n         |      | 44      |      |       | 44          |       |

| Pitch                    | р         |      | .050    |      |       | 1.27        |       |

| Pins per Side            | n1        |      | 11      |      |       | 11          |       |

| Overall Height           | Α         | .165 | .173    | .180 | 4.19  | 4.39        | 4.57  |

| Molded Package Thickness | A2        | .145 | .153    | .160 | 3.68  | 3.87        | 4.06  |

| Standoff §               | A1        | .020 | .028    | .035 | 0.51  | 0.71        | 0.89  |

| Side 1 Chamfer Height    | A3        | .024 | .029    | .034 | 0.61  | 0.74        | 0.86  |

| Corner Chamfer 1         | CH1       | .040 | .045    | .050 | 1.02  | 1.14        | 1.27  |

| Corner Chamfer (others)  | CH2       | .000 | .005    | .010 | 0.00  | 0.13        | 0.25  |

| Overall Width            | Е         | .685 | .690    | .695 | 17.40 | 17.53       | 17.65 |

| Overall Length           | D         | .685 | .690    | .695 | 17.40 | 17.53       | 17.65 |

| Molded Package Width     | E1        | .650 | .653    | .656 | 16.51 | 16.59       | 16.66 |

| Molded Package Length    | D1        | .650 | .653    | .656 | 16.51 | 16.59       | 16.66 |

| Footprint Width          | E2        | .590 | .620    | .630 | 14.99 | 15.75       | 16.00 |

| Footprint Length         | D2        | .590 | .620    | .630 | 14.99 | 15.75       | 16.00 |

| Lead Thickness           | С         | .008 | .011    | .013 | 0.20  | 0.27        | 0.33  |

| Upper Lead Width         | B1        | .026 | .029    | .032 | 0.66  | 0.74        | 0.81  |

| Lower Lead Width         | В         | .013 | .020    | .021 | 0.33  | 0.51        | 0.53  |

| Mold Draft Angle Top     | α         | 0    | 5       | 10   | 0     | 5           | 10    |

| Mold Draft Angle Bottom  | β         | 0    | 5       | 10   | 0     | 5           | 10    |

\* Controlling Parameter § Significant Characteristic

Notes:

Dimensions D and E1 do not include mold flash or protrusions. Mold flash or protrusions shall not exceed

.010" (0.254mm) per side. JEDEC Equivalent: MO-047 Drawing No. C04-048

# Μ

| Master Clear (MCLR)                             | 8,     | 10   |

|-------------------------------------------------|--------|------|

| MCLR Reset, Normal Operation93                  | 8, 95, | 96   |

| MCLR Reset, SLEEP                               | 3, 95, | 96   |

| Operation and ESD Protection                    |        |      |

| MCLR/VPP Pin                                    |        | 8    |

| MCLR/VPP Pin                                    |        | . 10 |

| Memory Organization                             |        | . 13 |

| Data Memory                                     |        | . 13 |

| Program Memory                                  |        | . 13 |

| Program Memory and Stack Maps                   |        | . 13 |

| MPLAB C17 and MPLAB C18 C Compilers             | 1      | 113  |

| MPLAB ICD In-Circuit Debugger                   | 1      | 115  |

| MPLAB ICE High Performance Universal In-Circuit |        |      |

| Emulator with MPLAB IDE                         | 1      | 114  |

| MPLAB Integrated Development                    |        |      |

| Environment Software                            | 1      | 113  |

| MPLINK Object Linker/MPLIB Object Librarian     | 1      | 114  |

# 0

| ODCODE Field Descriptions             | 405 |

|---------------------------------------|-----|

| OPCODE Field Descriptions             |     |

| OPTION_REG Register                   |     |

| INTEDG bit                            |     |

| PS2:PS0 bits                          |     |

| PSA bit                               |     |

| RBPU bit                              |     |

| T0CS bit                              |     |

| T0SE bit                              |     |

| OSC1/CLKI Pin                         |     |

| OSC2/CLKO Pin                         |     |

| Oscillator Configuration              |     |

| Oscillator Configurations             |     |

| Crystal Oscillator/Ceramic Resonators |     |

| НŚ                                    |     |

| LP                                    |     |

| RC                                    |     |

| ХТ                                    |     |

| Oscillator, WDT                       | ,   |

# Ρ

| P (STOP) bit                  | 60     |

|-------------------------------|--------|

| Packaging                     |        |

| Paging, Program Memory        |        |

| Parallel Slave Port           | -      |

| Associated Registers          | 41     |

| Parallel Slave Port (PSP)     | 36, 40 |

| RE0/RD/AN5 Pin                |        |

| RE1/WR/AN6 Pin                | 12, 39 |

| RE2/CS/AN7 Pin                |        |

| Select (PSPMODE bit)          |        |

| PCFG0 bit                     |        |

| PCFG1 bit                     |        |

| PCFG2 bit                     |        |

| PCL Register                  |        |

| PCLATH Register               |        |

| PCO <u>N Reg</u> ister        | 25, 95 |

| POR Bit                       | 25     |

| PICDEM 1 Low Cost PICmicro    |        |

| Demonstration Board           | 115    |

| PICDEM 17 Demonstration Board | 116    |

| PICDEM 2 Low Cost PIC16CXX    |        |

| Demonstration Board           | 115    |

| PICDEM 3 Low Cost PIC16CXXX   |        |

| Demonstration Board           | 116    |

|                               |        |

| PICSTART Plus Entry Level                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|