Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                  |

|----------------------------|-------------------------------------------------------------------------|

| Core Processor             | PIC                                                                     |

| Core Size                  | 8-Bit                                                                   |

| Speed                      | 20MHz                                                                   |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                                       |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                   |

| Number of I/O              | 22                                                                      |

| Program Memory Size        | 7KB (4K x 14)                                                           |

| Program Memory Type        | FLASH                                                                   |

| EEPROM Size                | -                                                                       |

| RAM Size                   | 192 x 8                                                                 |

| Voltage - Supply (Vcc/Vdd) | 4V ~ 5.5V                                                               |

| Data Converters            | A/D 5x8b                                                                |

| Oscillator Type            | External                                                                |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                      |

| Mounting Type              | Surface Mount                                                           |

| Package / Case             | 28-SSOP (0.209", 5.30mm Width)                                          |

| Supplier Device Package    | 28-SSOP                                                                 |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16f73-e-ss |

|                            |                                                                         |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

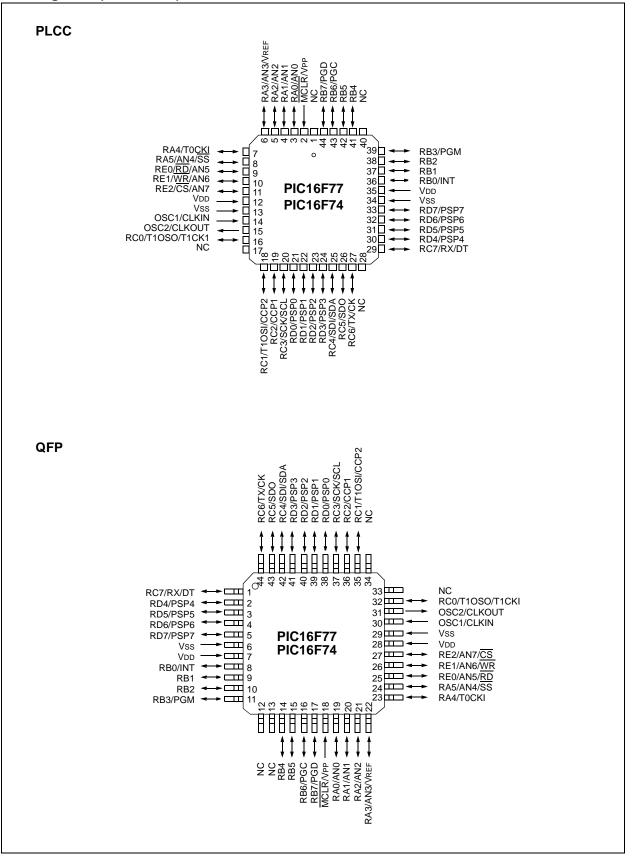

#### **Pin Diagrams (Continued)**

#### 1.0 **DEVICE OVERVIEW**

This document contains device specific information about the following devices:

- PIC16F73

- PIC16F74

- PIC16F76

- PIC16F77

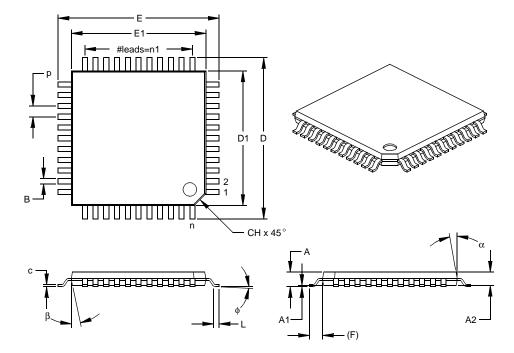

PIC16F73/76 devices are available only in 28-pin packages, while PIC16F74/77 devices are available in 40-pin and 44-pin packages. All devices in the PIC16F7X family share common architecture, with the following differences:

- The PIC16F73 and PIC16F76 have one-half of the total on-chip memory of the PIC16F74 and **PIC16F77**

- The 28-pin devices have 3 I/O ports, while the 40/44-pin devices have 5

- · The 28-pin devices have 11 interrupts, while the 40/44-pin devices have 12

- The 28-pin devices have 5 A/D input channels, while the 40/44-pin devices have 8

- The Parallel Slave Port is implemented only on the 40/44-pin devices

PIC16F7X DEVICE FEATURES **PIC16F74 PIC16F76 Key Features PIC16F73 PIC16F77 Operating Frequency** DC - 20 MHz DC - 20 MHz DC - 20 MHz DC - 20 MHz **RESETS** (and Delays) POR, BOR POR. BOR POR. BOR POR, BOR (PWRT, OST) (PWRT, OST) (PWRT, OST) (PWRT, OST) FLASH Program Memory 4K 4K 8K 8K (14-bit words) Data Memory (bytes) 368 192 192 368 Interrupts 11 12 11 12 I/O Ports Ports A,B,C Ports A,B,C Ports A,B,C,D,E Ports A,B,C,D,E Timers 3 3 3 3 Capture/Compare/PWM Modules 2 2 2 2 SSP, USART Serial Communications SSP, USART SSP. USART SSP, USART Parallel Communications PSP PSP 8-bit Analog-to-Digital Module **5 Input Channels** 8 Input Channels 5 Input Channels 8 Input Channels Instruction Set **35 Instructions 35 Instructions** 35 Instructions **35 Instructions** Packaging 28-pin DIP 40-pin PDIP 28-pin DIP 40-pin PDIP 28-pin SOIC 44-pin PLCC 28-pin SOIC 44-pin PLCC 28-pin SSOP 44-pin TQFP 28-pin SSOP 44-pin TQFP 28-pin MLF 28-pin MLF

#### **TABLE 1-1:**

The available features are summarized in Table 1-1. Block diagrams of the PIC16F73/76 and PIC16F74/77 devices are provided in Figure 1-1 and Figure 1-2, respectively. The pinouts for these device families are listed in Table 1-2 and Table 1-3.

Additional information may be found in the PICmicro™ Mid-Range Reference Manual (DS33023), which may be obtained from your local Microchip Sales Representative or downloaded from the Microchip website. The Reference Manual should be considered a complementary document to this data sheet, and is highly recommended reading for a better understanding of the device architecture and operation of the peripheral modules.

#### TABLE 1-3:PIC16F74 AND PIC16F77 PINOUT DESCRIPTION

| OSC1/CLKI<br>OSC1<br>CLKI<br>OSC2/CLKO<br>OSC2<br>CLKO<br>MCLR/VPP<br>MCLR<br>VPP | 13 | 14<br>15 | 30<br>31 | 1        | ST/CMOS <sup>(4)</sup> | Oscillator crystal or external clock input.<br>Oscillator crystal input or external clock source input.<br>ST buffer when configured in RC mode. Otherwise<br>CMOS.<br>External clock source input. Always associated with pin |

|-----------------------------------------------------------------------------------|----|----------|----------|----------|------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| CLKI<br>OSC2/CLKO<br>OSC2<br>CLKO<br><u>MCLR/VPP</u><br>MCLR                      | 14 | 15       | 31       | I        |                        | Oscillator crystal input or external clock source input.<br>ST buffer when configured in RC mode. Otherwise<br>CMOS.<br>External clock source input. Always associated with pin                                                |

| OSC2/CLKO<br>OSC2<br>CLKO<br>MCLR/VPP<br>MCLR                                     | 14 | 15       | 31       |          |                        | CMOS.<br>External clock source input. Always associated with pin                                                                                                                                                               |

| OSC2/CLKO<br>OSC2<br>CLKO<br>MCLR/VPP<br>MCLR                                     | 14 | 15       | 31       |          |                        | External clock source input. Always associated with pin                                                                                                                                                                        |

| OSC2<br>CLKO<br>MCLR/VPP<br>MCLR                                                  | 14 | 15       | 31       |          |                        |                                                                                                                                                                                                                                |

| OSC2<br>CLKO<br>MCLR/VPP<br>MCLR                                                  | 14 | 15       | 31       | 0        |                        | function OSC1 (see OSC1/CLKI, OSC2/CLKO pins).                                                                                                                                                                                 |

| CLKO<br>MCLR/VPP<br>MCLR                                                          |    |          |          | <u> </u> | I —                    | Oscillator crystal or clock output.                                                                                                                                                                                            |

| MCLR/Vpp<br>MCLR                                                                  |    |          |          | 0        |                        | Oscillator crystal output.                                                                                                                                                                                                     |

| MCLR/Vpp<br>MCLR                                                                  |    |          |          |          |                        | Connects to crystal or resonator in Crystal Oscillator                                                                                                                                                                         |

| MCLR/Vpp<br>MCLR                                                                  |    |          |          |          |                        | mode.                                                                                                                                                                                                                          |

| MCLR                                                                              |    |          |          | 0        |                        | In RC mode, OSC2 pin outputs CLKO, which has 1/4                                                                                                                                                                               |

| MCLR                                                                              |    |          |          |          |                        | the frequency of OSC1 and denotes the instruction                                                                                                                                                                              |

| MCLR                                                                              |    |          |          |          |                        | cycle rate.                                                                                                                                                                                                                    |

|                                                                                   | 1  | 2        | 18       |          | ST                     | Master Clear (input) or programming voltage (output).                                                                                                                                                                          |

| Vpp                                                                               |    |          |          | I        |                        | Master Clear (Reset) input. This pin is an active low                                                                                                                                                                          |

| VPP                                                                               |    |          |          |          |                        | RESET to the device.                                                                                                                                                                                                           |

|                                                                                   |    |          |          | Р        |                        | Programming voltage input.                                                                                                                                                                                                     |

|                                                                                   |    |          |          |          |                        | PORTA is a bi-directional I/O port.                                                                                                                                                                                            |

| RA0/AN0                                                                           | 2  | 3        | 19       |          | TTL                    |                                                                                                                                                                                                                                |

| RA0                                                                               |    |          |          | I/O      |                        | Digital I/O.                                                                                                                                                                                                                   |

| AN0                                                                               |    |          |          | I        |                        | Analog input 0.                                                                                                                                                                                                                |

| RA1/AN1                                                                           | 3  | 4        | 20       |          | TTL                    |                                                                                                                                                                                                                                |

| RA1                                                                               |    |          |          | I/O      |                        | Digital I/O.                                                                                                                                                                                                                   |

| AN1                                                                               |    |          |          | I        |                        | Analog input 1.                                                                                                                                                                                                                |

| RA2/AN2                                                                           | 4  | 5        | 21       |          | TTL                    |                                                                                                                                                                                                                                |

| RA2                                                                               |    |          |          | I/O      |                        | Digital I/O.                                                                                                                                                                                                                   |

| AN2                                                                               |    |          |          | I        |                        | Analog input 2.                                                                                                                                                                                                                |

| RA3/AN3/Vref                                                                      | 5  | 6        | 22       |          | TTL                    |                                                                                                                                                                                                                                |

| RA3                                                                               |    |          |          | I/O      |                        | Digital I/O.                                                                                                                                                                                                                   |

| AN3                                                                               |    |          |          | I        |                        | Analog input 3.                                                                                                                                                                                                                |

| VREF                                                                              |    |          |          | I        |                        | A/D reference voltage input.                                                                                                                                                                                                   |

| RA4/T0CKI                                                                         | 6  | 7        | 23       |          | ST                     |                                                                                                                                                                                                                                |

| RA4                                                                               |    |          |          | I/O      |                        | Digital I/O – Open drain when configured as output.                                                                                                                                                                            |

| TOCKI                                                                             |    |          |          | I        |                        | Timer0 external clock input.                                                                                                                                                                                                   |

| RA5/SS/AN4                                                                        | 7  | 8        | 24       |          | TTL                    |                                                                                                                                                                                                                                |

| RA5                                                                               |    | -        |          | I/O      |                        | Digital I/O.                                                                                                                                                                                                                   |

| SS                                                                                | 1  |          |          | 1        |                        | SPI slave select input.                                                                                                                                                                                                        |

| AN4                                                                               |    |          |          |          | 1                      |                                                                                                                                                                                                                                |

| Legend: I = inpu                                                                  |    | 1        |          |          |                        | Analog input 4.                                                                                                                                                                                                                |

— = Not used TTL = TTL input ST = Schmitt Trigger input

**Note 1:** This buffer is a Schmitt Trigger input when configured as an external interrupt.

2: This buffer is a Schmitt Trigger input when used in Serial Programming mode.

**3:** This buffer is a Schmitt Trigger input when configured as general purpose I/O and a TTL input when used in the Parallel Slave Port mode (for interfacing to a microprocessor bus).

4: This buffer is a Schmitt Trigger input when configured in RC Oscillator mode and a CMOS input otherwise.

| Pin Name          | DIP<br>Pin# | PLCC<br>Pin# | QFP<br>Pin#               | I/O/P<br>Type | Buffer<br>Type        | Description                                                   |

|-------------------|-------------|--------------|---------------------------|---------------|-----------------------|---------------------------------------------------------------|

|                   |             |              |                           |               |                       | PORTD is a bi-directional I/O port or parallel slave port     |

|                   |             |              |                           |               |                       | when interfacing to a microprocessor bus.                     |

| RD0/PSP0          | 19          | 21           | 38                        |               | ST/TTL <sup>(3)</sup> |                                                               |

| RD0               |             |              |                           | I/O           |                       | Digital I/O.                                                  |

| PSP0              |             |              | 00                        | I/O           | ot (3)                | Parallel Slave Port data.                                     |

| RD1/PSP1<br>RD1   | 20          | 22           | 39                        | і<br>І/О      | ST/TTL <sup>(3)</sup> | Digital I/O.                                                  |

| PSP1              |             |              |                           | 1/O           |                       | Parallel Slave Port data.                                     |

| RD2/PSP2          | 21          | 23           | 40                        | 1,'C          | ST/TTL <sup>(3)</sup> |                                                               |

| RD2               | 21          | 20           | 40                        | ı/O           | OI/TIE                | Digital I/O.                                                  |

| PSP2              |             |              |                           | I/O           |                       | Parallel Slave Port data.                                     |

| RD3/PSP3          | 22          | 24           | 41                        |               | ST/TTL <sup>(3)</sup> |                                                               |

| RD3               |             |              |                           | I/O           |                       | Digital I/O.                                                  |

| PSP3              |             |              |                           | I/O           |                       | Parallel Slave Port data.                                     |

| RD4/PSP4          | 27          | 30           | 2                         |               | ST/TTL <sup>(3)</sup> |                                                               |

| RD4               |             |              |                           | I/O           |                       | Digital I/O.                                                  |

| PSP4 I/O          |             |              | Parallel Slave Port data. |               |                       |                                                               |

| RD5/PSP5          | 28          | 31           | 3                         |               | ST/TTL <sup>(3)</sup> |                                                               |

| RD5               |             |              |                           | I/O           |                       | Digital I/O.                                                  |

| PSP5              |             |              |                           | I/O           | · · · · · · (2)       | Parallel Slave Port data.                                     |

| RD6/PSP6          | 29          | 32           | 4                         |               | ST/TTL <sup>(3)</sup> | District I/O                                                  |

| RD6<br>PSP6       |             |              |                           | I/O<br>I/O    |                       | Digital I/O.<br>Parallel Slave Port data.                     |

| RD7/PSP7          | 30          | 33           | 5                         | 1/0           | ST/TTL <sup>(3)</sup> | Faraller Slave Folt data.                                     |

| RD7/PSP7          | 30          | - 33         | Э                         | I/O           | 51/11L*/              | Digital I/O.                                                  |

| PSP7              |             |              |                           | 1/O           |                       | Parallel Slave Port data.                                     |

| -                 |             |              |                           |               |                       | PORTE is a bi-directional I/O port.                           |

| RE0/RD/AN5        | 8           | 9            | 25                        |               | ST/TTL <sup>(3)</sup> |                                                               |

| RE0               | -           | -            |                           | I/O           |                       | Digital I/O.                                                  |

| RD                |             |              |                           | I             |                       | Read control for parallel slave port .                        |

| AN5               |             |              |                           | I             |                       | Analog input 5.                                               |

| RE1/WR/AN6        | 9           | 10           | 26                        |               | ST/TTL <sup>(3)</sup> |                                                               |

| RE1               |             |              |                           | I/O           |                       | Digital I/O.                                                  |

| WR                |             |              |                           | 1             |                       | Write control for parallel slave port .                       |

| AN6               |             |              |                           | I             | o <i></i> (3)         | Analog input 6.                                               |

| RE2/CS/AN7        | 10          | 11           | 27                        |               | ST/TTL <sup>(3)</sup> |                                                               |

| RE2<br>CS         |             |              |                           | I/O<br>I      |                       | Digital I/O.<br>Chip select control for parallel slave port . |

| AN7               |             |              |                           | 1             |                       | Analog input 7.                                               |

| Vss               | 12,31       | 13,34        | 6,29                      | P             | _                     | Ground reference for logic and I/O pins.                      |

| VDD               | 11,32       | 12,35        | 7,28                      | Р             | _                     | Positive supply for logic and I/O pins.                       |

| NC                | · -         | 1,17,2       | 12,13,                    |               | _                     | These pins are not internally connected. These pins should    |

|                   |             | 8, 40        | 33, 34                    |               |                       | be left unconnected.                                          |

| Legend: I = input |             | O = 0        |                           | I/C           | ) = input/outpu       | ut P = power                                                  |

#### **TABLE 1-3:** PIC16F74 AND PIC16F77 PINOUT DESCRIPTION (CONTINUED)

**Note 1:** This buffer is a Schmitt Trigger input when configured as an external interrupt.

2: This buffer is a Schmitt Trigger input when used in Serial Programming mode.

3: This buffer is a Schmitt Trigger input when configured as general purpose I/O and a TTL input when used in the Parallel Slave Port mode (for interfacing to a microprocessor bus).

4: This buffer is a Schmitt Trigger input when configured in RC Oscillator mode and a CMOS input otherwise.

| <b>TABLE 2-1:</b> | SPECIAL FUNCTION REGISTER SUMMARY | (CONTINUED) |

|-------------------|-----------------------------------|-------------|

|-------------------|-----------------------------------|-------------|

| Address                    | Name       | Bit 7                                       | Bit 6          | Bit 5         | Bit 4          | Bit 3          | Bit 2         | Bit 1         | Bit 0        | Value on:<br>POR,<br>BOR | Details<br>on page |

|----------------------------|------------|---------------------------------------------|----------------|---------------|----------------|----------------|---------------|---------------|--------------|--------------------------|--------------------|

| Bank 2                     |            |                                             |                |               |                |                |               |               |              |                          |                    |

| 100h <sup>(4)</sup>        | INDF       | Addressin                                   | g this locatio | n uses conte  | ents of FSR to | address data   | a memory (r   | not a physica | al register) | 0000 0000                | 27, 96             |

| 101h                       | TMR0       | Timer0 Mc                                   | dule Registe   |               | xxxx xxxx      | 45, 96         |               |               |              |                          |                    |

| 102h <sup>(4)</sup>        | PCL        | Program Counter (PC) Least Significant Byte |                |               |                |                |               |               |              | 0000 0000                | 26, 96             |

| 103h <sup>(4)</sup>        | STATUS     | IRP                                         | RP1            | RP0           | ТО             | PD             | Z             | DC            | С            | 0001 1xxx                | 19, 96             |

| 104h <sup>(4)</sup>        | FSR        | Indirect Da                                 | ata Memory /   | Address Poir  | nter           |                |               |               |              | xxxx xxxx                | 27, 96             |

| 105h                       | —          | Unimplem                                    | ented          |               |                |                |               |               |              | _                        | —                  |

| 106h                       | PORTB      | PORTB D                                     | ata Latch wh   | en written: F | ORTB pins w    | hen read       |               |               |              | xxxx xxxx                | 34, 96             |

| 107h                       | _          | Unimplem                                    | ented          |               |                |                |               |               |              | —                        | —                  |

| 108h                       | —          | Unimplem                                    | ented          |               |                |                |               |               |              | —                        | —                  |

| 109h                       | —          | Unimplem                                    | ented          |               |                |                |               |               |              | _                        | —                  |

| 10Ah <sup>(1,4)</sup>      | PCLATH     | —                                           | _              | _             | Write Buffer   | for the upper  | 5 bits of the | Program C     | ounter       | 0 0000                   | 21, 96             |

| 10Bh <b><sup>(4)</sup></b> | INTCON     | GIE                                         | PEIE           | TMR0IE        | INTE           | RBIE           | TMR0IF        | INTF          | RBIF         | 0000 000x                | 23, 96             |

| 10Ch                       | PMDATA     | Data Regi                                   | ster Low Byte  | e             |                | •              | •             |               | -            | XXXX XXXX                | 29, 97             |

| 10Dh                       | PMADR      | Address R                                   | egister Low    | Byte          |                |                |               |               |              | xxxx xxxx                | 29, 97             |

| 10Eh                       | PMDATH     | —                                           | _              | Data Regist   | ter High Byte  |                |               |               |              | xxxx xxxx                | 29, 97             |

| 10Fh                       | PMADRH     |                                             | _              | _             | Address Reg    | gister High By | /te           |               |              | XXXX XXXX                | 29, 97             |

| Bank 3                     |            |                                             |                |               |                |                |               |               |              |                          |                    |

| 180h <sup>(4)</sup>        | INDF       | Addressin                                   | g this locatio | n uses conte  | ents of FSR to | address data   | a memory (r   | not a physica | al register) | 0000 0000                | 27, 96             |

| 181h                       | OPTION_REG | RBPU                                        | INTEDG         | TOCS          | TOSE           | PSA            | PS2           | PS1           | PS0          | 1111 1111                | 20, 44, 96         |

| 182h <sup>(4)</sup>        | PCL        | Program C                                   | Counter (PC)   | Least Signif  | icant Byte     |                |               |               |              | 0000 0000                | 26, 96             |

| 183h <sup>(4)</sup>        | STATUS     | IRP                                         | RP1            | RP0           | TO             | PD             | Z             | DC            | С            | 0001 1xxx                | 19, 96             |

| 184h <sup>(4)</sup>        | FSR        | Indirect Da                                 | ata Memory /   | Address Poir  | nter           |                |               |               |              | xxxx xxxx                | 27, 96             |

| 185h                       | —          | Unimplem                                    | ented          |               |                |                |               |               |              | _                        | _                  |

| 186h                       | TRISB      | PORTB Data Direction Register               |                |               |                |                |               | 1111 1111     | 34, 96       |                          |                    |

| 187h                       | —          | Unimplemented                               |                |               |                |                |               | _             | _            |                          |                    |

| 188h                       | —          | Unimplemented                               |                |               |                |                |               |               | _            | _                        |                    |

| 189h                       | —          | Unimplemented                               |                |               |                |                |               | _             | _            |                          |                    |

| 18Ah <sup>(1,4)</sup>      | PCLATH     | _                                           |                | _             | Write Buffer   | for the upper  | 5 bits of the | Program C     | ounter       | 0 0000                   | 21, 96             |

| 18Bh <sup>(4)</sup>        | INTCON     | GIE                                         | PEIE           | TMR0IE        | INTE           | RBIE           | TMR0IF        | INTF          | RBIF         | 0000 000x                | 23, 96             |

| 18Ch                       | PMCON1     | (6)                                         | _              | —             | —              | —              | _             | —             | RD           | 10                       | 29, 97             |

| 18Dh                       | —          | Unimplem                                    | ented          |               |                |                |               |               |              | _                        |                    |

| 18Eh                       | —          | Reserved                                    | maintain clea  | ar            |                |                |               |               |              | 0000 0000                |                    |

| 18Fh                       | _          | Reserved                                    | maintain clea  | ar            |                |                |               |               |              | 0000 0000                |                    |

Legend: x = unknown, u = unchanged, q = value depends on condition, - = unimplemented, read as '0', r = reserved. Shaded locations are unimplemented, read as '0'.

**Note** 1: The upper byte of the program counter is not directly accessible. PCLATH is a holding register for the PC<12:8>, whose contents are transferred to the upper byte of the program counter during branches (CALL or GOTO).

2: Other (non power-up) RESETS include external RESET through MCLR and Watchdog Timer Reset.

3: Bits PSPIE and PSPIF are reserved on the 28-pin devices; always maintain these bits clear.

4: These registers can be addressed from any bank.

5: PORTD, PORTE, TRISD, and TRISE are not physically implemented on the 28-pin devices, read as '0'.

6: This bit always reads as a '1'.

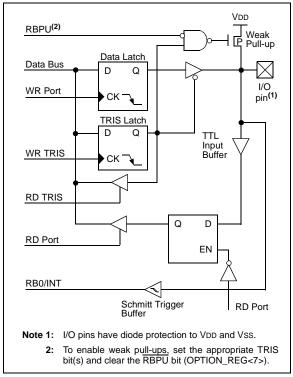

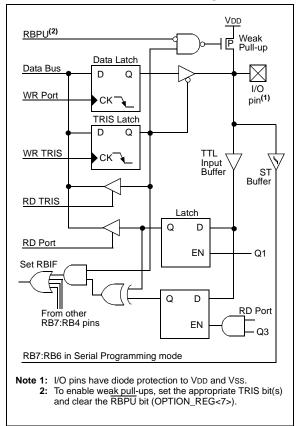

## 4.2 PORTB and the TRISB Register

PORTB is an 8-bit wide, bi-directional port. The corresponding data direction register is TRISB. Setting a TRISB bit (= '1') will make the corresponding PORTB pin an input (i.e., put the corresponding output driver in a Hi-Impedance mode). Clearing a TRISB bit (= '0') will make the corresponding PORTB pin an output (i.e., put the contents of the output latch on the selected pin).

Each of the PORTB pins has a weak internal pull-up. A single control bit can turn on all the pull-ups. This is performed by clearing bit RBPU (OPTION\_REG<7>). The weak pull-up is automatically turned off when the port pin is configured as an output. The pull-ups are disabled on a Power-on Reset.

Four of the PORTB pins (RB7:RB4) have an interrupt-on-change feature. Only pins configured as inputs can cause this interrupt to occur (i.e., any RB7:RB4 pin configured as an output is excluded from the interrupt-on-change comparison). The input pins (of RB7:RB4) are compared with the old value latched on the last read of PORTB. The "mismatch" outputs of RB7:RB4 are ORed together to generate the RB Port Change Interrupt with flag bit RBIF (INTCON<0>). This interrupt can wake the device from SLEEP. The user, in the Interrupt Service Routine, can clear the interrupt in the following manner:

- a) Any read or write of PORTB. This will end the mismatch condition.

- b) Clear flag bit RBIF.

A mismatch condition will continue to set flag bit RBIF. Reading PORTB will end the mismatch condition and allow flag bit RBIF to be cleared.

The interrupt-on-change feature is recommended for wake-up on key depression operation and operations where PORTB is only used for the interrupt-on-change feature. Polling of PORTB is not recommended while using the interrupt-on-change feature.

This interrupt on mismatch feature, together with software configureable pull-ups on these four pins, allow easy interface to a keypad and make it possible for wake-up on key depression. Refer to the Embedded Control Handbook, "Implementing Wake-up on Key Stroke" (AN552).

RB0/INT is an external interrupt input pin and is configured using the INTEDG bit (OPTION\_REG<6>).

RB0/INT is discussed in detail in Section 12.11.1.

#### FIGURE 4-4: BLOCK DIAGRAM OF RB7:RB4 PINS

#### 5.2 Using Timer0 with an External Clock

When no prescaler is used, the external clock input is the same as the prescaler output. The synchronization of T0CKI, with the internal phase clocks, is accomplished by sampling the prescaler output on the Q2 and Q4 cycles of the internal phase clocks. Therefore, it is necessary for T0CKI to be high for at least 2Tosc (and a small RC delay of 20 ns) and low for at least 2Tosc (and a small RC delay of 20 ns). Refer to the electrical specification of the desired device.

| REGISTER 5-1: | <b>OPTION_REG REGISTER</b> |

|---------------|----------------------------|

|---------------|----------------------------|

|         | R/W-1       | R/W-1                                                              | R/W-1        | R/W-1        | R/W-1      | R/W-1      | R/W-1        | R/W-1   |  |  |

|---------|-------------|--------------------------------------------------------------------|--------------|--------------|------------|------------|--------------|---------|--|--|

|         | RBPU        | INTEDG                                                             | TOCS         | T0SE         | PSA        | PS2        | PS1          | PS0     |  |  |

|         | bit 7       |                                                                    |              |              |            |            |              | bit 0   |  |  |

|         |             |                                                                    |              |              |            |            |              |         |  |  |

| bit 7   | RBPU: PC    | ORTB Pull-up                                                       | Enable bit   | (see Sectior | n 2.2.2.2) |            |              |         |  |  |

| bit 6   | INTEDG:     | Interrupt Edg                                                      | e Select bit | (see Section | n 2.2.2.2) |            |              |         |  |  |

| bit 5   | TOCS: TM    | TMR0 Clock Source Select bit                                       |              |              |            |            |              |         |  |  |

|         |             | ransition on T0CKI pin<br>iternal instruction cycle clock (CLKOUT) |              |              |            |            |              |         |  |  |

| bit 4   | TOSE: TM    | R0 Source E                                                        | Edge Select  | bit          |            |            |              |         |  |  |

|         | 1 = Incren  | nent on high-                                                      | to-low trans | ition on TOC | KI pin     |            |              |         |  |  |

|         | 0 = Incren  | nent on low-t                                                      | o-high trans | ition on TOC | KI pin     |            |              |         |  |  |

| bit 3   | PSA: Pres   | scaler Assigr                                                      | nment bit    |              |            |            |              |         |  |  |

|         |             | aler is assign<br>aler is assign                                   |              |              | е          |            |              |         |  |  |

| bit 2-0 | PS2:PS0:    | Prescaler R                                                        | ate Select b | its          |            |            |              |         |  |  |

|         | Bit Value   | TMR0 Rate                                                          | WDT Rate     |              |            |            |              |         |  |  |

|         | 000         | 1:2                                                                | 1:1          |              |            |            |              |         |  |  |

|         | 001         | 1:4<br>1:8                                                         | 1:2<br>1:4   |              |            |            |              |         |  |  |

|         | 010<br>011  | 1:16                                                               | 1:4          |              |            |            |              |         |  |  |

|         | 100         | 1:32                                                               | 1:16         |              |            |            |              |         |  |  |

|         | 101         | 1:64                                                               | 1:32         |              |            |            |              |         |  |  |

|         | 110         | 1:128                                                              | 1:64         |              |            |            |              |         |  |  |

|         | 111         | 1 : 256                                                            | 1 : 128      |              |            |            |              |         |  |  |

|         | Legend:     |                                                                    |              |              |            |            |              |         |  |  |

|         | R = Reada   | able bit                                                           | W = V        | Vritable bit | U = Unii   | mplemented | bit, read as | '0'     |  |  |

|         | - n = Value | e at POR res                                                       | et '1' = B   | Bit is set   | '0' = Bit  | is cleared | x = Bit is ι | unknown |  |  |

|         |             |                                                                    |              |              |            |            |              |         |  |  |

|         |             | To avoid ar                                                        |              |              |            |            |              |         |  |  |

|         |             | Example 5-1<br>caler assigni<br>even if the W                      | ment betwee  | en Timer0 a  |            |            |              |         |  |  |

#### 6.4 Timer1 Operation in Asynchronous Counter Mode

If control bit T1SYNC (T1CON<2>) is set, the external clock input is not synchronized. The timer continues to increment asynchronous to the internal phase clocks. The timer will continue to run during SLEEP and can generate an interrupt on overflow, which will wake-up the processor. However, special precautions in software are needed to read/write the timer (Section 6.4.1).

In Asynchronous Counter mode, Timer1 cannot be used as a time-base for capture or compare operations.

#### 6.4.1 READING AND WRITING TIMER1 IN ASYNCHRONOUS COUNTER MODE

Reading TMR1H or TMR1L, while the timer is running from an external asynchronous clock, will ensure a valid read (taken care of in hardware). However, the user should keep in mind that reading the 16-bit timer in two 8-bit values itself, poses certain problems, since the timer may overflow between the reads.

For writes, it is recommended that the user simply stop the timer and write the desired values. A write contention may occur by writing to the timer registers, while the register is incrementing. This may produce an unpredictable value in the timer register.

Reading the 16-bit value requires some care. The example code provided in Example 6-1 and Example 6-2 demonstrates how to write to and read Timer1 while it is running in Asynchronous mode.

#### EXAMPLE 6-1: WRITING A 16-BIT FREE-RUNNING TIMER

| ; All  | interrupts | are disabled                                     |  |

|--------|------------|--------------------------------------------------|--|

| CLRF   | TMR1L      | ; Clear Low byte, Ensures no rollover into TMR1H |  |

| MOVLW  | HI_BYTE    | ; Value to load into TMR1H                       |  |

| MOVWF  | TMR1H, F   | ; Write High byte                                |  |

| MOVLW  | LO_BYTE    | ; Value to load into TMR1L                       |  |

| MOVWF  | TMR1H, F   | ; Write Low byte                                 |  |

| ; Re-0 | enable the | Interrupt (if required)                          |  |

| CONTI  | NUE        | ; Continue with your code                        |  |

| 1      |            |                                                  |  |

#### EXAMPLE 6-2: READING A 16-BIT FREE-RUNNING TIMER

| ; All  | interrupts an | ce | disabled                                             |

|--------|---------------|----|------------------------------------------------------|

| MOVF   | TMR1H, W      | ;  | Read high byte                                       |

| MOVWF  | TMPH          |    |                                                      |

| MOVF   | TMR1L, W      | ;  | Read low byte                                        |

| MOVWF  | TMPL          |    |                                                      |

| MOVF   | TMR1H, W      | ;  | Read high byte                                       |

| SUBWF  | TMPH, W       | ;  | Sub 1st read with 2nd read                           |

| BTFSC  | STATUS,Z      | ;  | Is result = 0                                        |

| GOTO   | CONTINUE      | ;  | Good 16-bit read                                     |

| ; TMR1 | L may have ro | 51 | led over between the read of the high and low bytes. |

| ; Read | ing the high  | a  | nd low bytes now will read a good value.             |

| MOVF   | TMR1H, W      | ;  | Read high byte                                       |

| MOVWF  | TMPH          |    |                                                      |

| MOVF   | TMR1L, W      | ;  | Read low byte                                        |

| MOVWF  | TMPL          | ;  | Re-enable the Interrupt (if required)                |

| CONTIN | UE            | ;  | Continue with your code                              |

|        |               |    | -                                                    |

## 6.5 Timer1 Oscillator

A crystal oscillator circuit is built-in between pins T1OSI (input) and T1OSO (amplifier output). It is enabled by setting control bit T1OSCEN (T1CON<3>). The oscillator is a low power oscillator rated up to 200 kHz. It will continue to run during SLEEP. It is primarily intended for use with a 32 kHz crystal. Table 6-1 shows the capacitor selection for the Timer1 oscillator.

The Timer1 oscillator is identical to the LP oscillator. The user must provide a software time delay to ensure proper oscillator start-up.

#### 6.6 Resetting Timer1 using a CCP Trigger Output

If the CCP1 or CCP2 module is configured in Compare mode to generate a "special event trigger" (CCP1M3:CCP1M0 = '1011'), this signal will reset Timer1.

| Note: | The special event triggers from the CCP1 |

|-------|------------------------------------------|

|       | and CCP2 modules will not set interrupt  |

|       | flag bit TMR1IF (PIR1<0>).               |

Timer1 must be configured for either Timer or Synchronized Counter mode, to take advantage of this feature. If Timer1 is running in Asynchronous Counter mode, this RESET operation may not work.

In the event that a write to Timer1 coincides with a special event trigger from CCP1 or CCP2, the write will take precedence.

In this mode of operation, the CCPRxH:CCPRxL register pair effectively becomes the period register for Timer1.

#### 6.7 Resetting of Timer1 Register Pair (TMR1H, TMR1L)

TMR1H and TMR1L registers are not reset to 00h on a POR, or any other RESET, except by the CCP1 and CCP2 special event triggers.

# TABLE 6-1:CAPACITOR SELECTION FOR<br/>THE TIMER1 OSCILLATOR

|          | Frequency | Capacitors Used: |       |  |  |  |

|----------|-----------|------------------|-------|--|--|--|

| Osc Type | Frequency | OSC1             | OSC2  |  |  |  |

| LP       | 32 kHz    | 47 pF            | 47 pF |  |  |  |

|          | 100 kHz   | 33 pF            | 33 pF |  |  |  |

|          | 200 kHz   | 15 pF            | 15 pF |  |  |  |

| • •      |           |                  |       |  |  |  |

Capacitor values are for design guidance only.

These capacitors were tested with the crystals listed below for basic start-up and operation. These values were not optimized.

Different capacitor values may be required to produce acceptable oscillator operation. The user should test the performance of the oscillator over the expected VDD and temperature range for the application.

| See the notes (below) table for additional information. |

|---------------------------------------------------------|

|---------------------------------------------------------|

| Commonly Used Crystals:             |                                                                                                                                                                                                                                                                            |  |  |  |  |  |  |  |

|-------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|--|

| 32.768 kHz                          | Epson C-001R32.768K-A                                                                                                                                                                                                                                                      |  |  |  |  |  |  |  |

| 100 kHz                             | Epson C-2 100.00 KC-P                                                                                                                                                                                                                                                      |  |  |  |  |  |  |  |

| 200 kHz                             | STD XTL 200.000 kHz                                                                                                                                                                                                                                                        |  |  |  |  |  |  |  |

| of t<br>sta<br>2: Sin<br>cha<br>res | the capacitance increases the stability<br>the oscillator, but also increases the<br>rt-up time.<br>Ince each resonator/crystal has its own<br>aracteristics, the user should consult the<br>onator/crystal manufacturer for appro-<br>tate values of external components. |  |  |  |  |  |  |  |

T1CON register is reset to 00h on a Power-on Reset or a Brown-out Reset, which shuts off the timer and leaves a 1:1 prescale. In all other RESETS, the register is unaffected.

#### 6.8 Timer1 Prescaler

The prescaler counter is cleared on writes to the TMR1H or TMR1L registers.

| Address               | Name   | Bit 7                                                                       | Bit 6 | Bit 5   | Bit 4   | Bit 3   | Bit 2  | Bit 1  | Bit 0  | Value<br>PC<br>BC | DR,  |      | e on<br>other<br>ETS |

|-----------------------|--------|-----------------------------------------------------------------------------|-------|---------|---------|---------|--------|--------|--------|-------------------|------|------|----------------------|

| 0Bh,8Bh,<br>10Bh,18Bh | INTCON | GIE                                                                         | PEIE  | TMR0IE  | INTE    | RBIE    | TMR0IF | INTF   | RBIF   | 0000              | 000x | 0000 | 000u                 |

| 0Ch                   | PIR1   | PSPIF <sup>(1)</sup>                                                        | ADIF  | RCIF    | TXIF    | SSPIF   | CCP1IF | TMR2IF | TMR1IF | 0000              | 0000 | 0000 | 0000                 |

| 8Ch                   | PIE1   | PSPIE <sup>(1)</sup>                                                        | ADIE  | RCIE    | TXIE    | SSPIE   | CCP1IE | TMR2IE | TMR1IE | 0000              | 0000 | 0000 | 0000                 |

| 0Eh                   | TMR1L  | Holding register for the Least Significant Byte of the 16-bit TMR1 Register |       |         |         |         |        |        | r      | xxxx              | xxxx | uuuu | uuuu                 |

| 0Fh                   | TMR1H  | Holding register for the Most Significant Byte of the 16-bit TMR1 Register  |       |         |         |         |        |        |        | xxxx              | xxxx | uuuu | uuuu                 |

| 10h                   | T1CON  | _                                                                           | _     | T1CKPS1 | T1CKPS0 | T1OSCEN | T1SYNC | TMR1CS | TMR10N | 00                | 0000 | uu   | uuuu                 |

#### TABLE 6-2: REGISTERS ASSOCIATED WITH TIMER1 AS A TIMER/COUNTER

Legend: x = unknown, u = unchanged, - = unimplemented, read as '0'. Shaded cells are not used by the Timer1 module.

Note 1: Bits PSPIE and PSPIF are reserved on the PIC16F73/76; always maintain these bits clear.

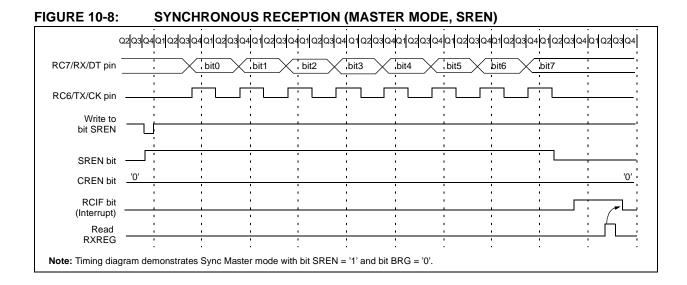

#### 10.3.2 USART SYNCHRONOUS MASTER RECEPTION

Once synchronous mode is selected, reception is enabled by setting either enable bit SREN (RCSTA<5>), or enable bit CREN (RCSTA<4>). Data is sampled on the RC7/RX/DT pin on the falling edge of the clock. If enable bit SREN is set, then only a single word is received. If enable bit CREN is set, the reception is continuous until CREN is cleared. If both bits are set, CREN takes precedence. After clocking the last bit, the received data in the Receive Shift Register (RSR) is transferred to the RCREG register (if it is empty). When the transfer is complete, interrupt flag bit RCIF (PIR1<5>) is set. The actual interrupt can be enabled/ disabled by setting/clearing enable bit RCIE (PIE1<5>). Flag bit RCIF is a read only bit, which is reset by the hardware. In this case, it is reset when the RCREG register has been read and is empty. The RCREG is a double buffered register (i.e., it is a two deep FIFO). It is possible for two bytes of data to be received and transferred to the RCREG FIFO and a third byte to begin shifting into the RSR register. On the clocking of the last bit of the third byte, if the RCREG register is still full, then overrun error bit OERR (RCSTA<1>) is set. The word in the RSR will be lost. The RCREG register can be read twice to retrieve the two bytes in the FIFO. Bit OERR has to be cleared in software (by clearing bit CREN). If bit OERR is set, transfers from the RSR to the RCREG are inhibited, so it is essential to clear bit OERR if it is set. The ninth receive bit is buffered the same way as the

receive data. Reading the RCREG register will load bit RX9D with a new value, therefore, it is essential for the user to read the RCSTA register before reading RCREG, in order not to lose the old RX9D information.

Steps to follow when setting up a Synchronous Master Reception:

- 1. Initialize the SPBRG register for the appropriate baud rate (Section 10.1).

- 2. Enable the synchronous master serial port by setting bits SYNC, SPEN and CSRC.

- 3. Ensure bits CREN and SREN are clear.

- 4. If interrupts are desired, then set enable bit RCIE.

- 5. If 9-bit reception is desired, then set bit RX9.

- 6. If a single reception is required, set bit SREN. For continuous reception set bit CREN.

- Interrupt flag bit RCIF will be set when reception is complete and an interrupt will be generated if enable bit RCIE was set.

- 8. Read the RCSTA register to get the ninth bit (if enabled) and determine if any error occurred during reception.

- 9. Read the 8-bit received data by reading the RCREG register.

- 10. If any error occurred, clear the error by clearing bit CREN.

- 11. If using interrupts, ensure that GIE and PEIE in the INTCON register are set.

#### 11.2 Selecting the A/D Conversion Clock

The A/D conversion time per bit is defined as TAD. The A/D conversion requires 9.0 TAD per 8-bit conversion. The source of the A/D conversion clock is software selectable. The four possible options for TAD are:

- 2 Tosc (Fosc/2)

- 8 Tosc (Fosc/8)

- 32 Tosc (Fosc/32)

- Internal RC oscillator (2-6 μs)

For correct A/D conversions, the A/D conversion clock (TAD) must be selected to ensure a minimum TAD time as small as possible, but no less than  $1.6 \,\mu s$ .

## 11.3 Configuring Analog Port Pins

The ADCON1, TRISA and TRISE registers control the operation of the A/D port pins. The port pins that are desired as analog inputs must have their corresponding TRIS bits set (input). If the TRIS bit is cleared (output), the digital output level (VOH or VOL) will be converted.

The A/D operation is independent of the state of the CHS2:CHS0 bits and the TRIS bits.

- Note 1: When reading the port register, all pins configured as analog input channels will read as cleared (a low level). Pins configured as digital inputs will convert an analog input. Analog levels on a digitally configured input will not affect the conversion accuracy.

- 2: Analog levels on any pin that is defined as a digital input, but not as an analog input, may cause the digital input buffer to consume current that is out of the device's specification.

# 11.4 A/D Conversions

**Note:** The GO/DONE bit should **NOT** be set in the same instruction that turns on the A/D.

Setting the GO/DONE bit begins an A/D conversion. When the conversion completes, the 8-bit result is placed in the ADRES register, the GO/DONE bit is cleared, and the ADIF flag (PIR<6>) is set.

If both the A/D interrupt bit ADIE (PIE1<6>) and the peripheral interrupt enable bit PEIE (INTCON<6>) are set, the device will wake from SLEEP whenever ADIF is set by hardware. In addition, an interrupt will also occur if the global interrupt bit GIE (INTCON<7>) is set.

Clearing the GO/DONE bit during a conversion will abort the current conversion. The ADRES register will NOT be changed, and the ADIF flag will not be set.

After the GO/DONE bit is cleared at either the end of a conversion, or by firmware, another conversion can be initiated by setting the GO/DONE bit. Users must still take into account the appropriate acquisition time for the application.

# 11.5 A/D Operation During SLEEP

The A/D module can operate during SLEEP mode. This requires that the A/D clock source be set to RC (ADCS1:ADCS0 = '11'). When the RC clock source is selected, the A/D module waits one instruction cycle before starting the conversion. This allows the SLEEP instruction to be executed, which eliminates all digital switching noise from the conversion. When the conversion is completed, the GO/DONE bit will be cleared, and the result loaded into the ADRES register. If the A/D interrupt is enabled, the device will wake-up from SLEEP. If the A/D interrupt is not enabled, the ADON bit will remain set.

When the A/D clock source is another clock option (not RC), a SLEEP instruction will cause the present conversion to be aborted and the A/D module to be turned off, though the ADON bit will remain set.

Turning off the A/D places the A/D module in its lowest current consumption state.

Note: For the A/D module to operate in SLEEP, the A/D clock source must be set to RC (ADCS1:ADCS0 = 11). To perform an A/D conversion in SLEEP, ensure the SLEEP instruction immediately follows the instruction that sets the GO/DONE bit.

# 11.6 Effects of a RESET

A device RESET forces all registers to their RESET state. The A/D module is disabled and any conversion in progress is aborted. All A/D input pins are configured as analog inputs.

The ADRES register will contain unknown data after a Power-on Reset.

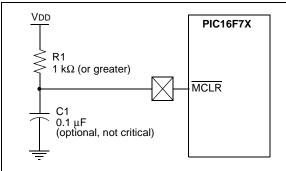

# 12.4 MCLR

PIC16F7X devices have a noise filter in the  $\overline{\text{MCLR}}$ Reset path. The filter will detect and ignore small pulses.

It should be noted that a WDT Reset does not drive MCLR pin low.

The behavior of the ESD protection on the  $\overline{\text{MCLR}}$  pin has been altered from previous devices of this family. Voltages applied to the pin that exceed its specification can result in both  $\overline{\text{MCLR}}$  Resets and excessive current beyond the device specification during the ESD event. For this reason, Microchip recommends that the  $\overline{\text{MCLR}}$ pin no longer be tied directly to VDD. The use of an RC network, as shown in Figure 12-5, is suggested.

#### 12.5 Power-on Reset (POR)

A Power-on Reset pulse is generated on-chip when VDD rise is detected (in the range of 1.2V - 1.7V). To take advantage of the POR, tie the MCLR pin to VDD as described in Section 12.4. A maximum rise time for VDD is specified. See the Electrical Specifications for details.

When the device starts normal operation (exits the RESET condition), device operating parameters (voltage, frequency, temperature,...) must be met to ensure operation. If these conditions are not met, the device must be held in RESET until the operating conditions are met. For additional information, refer to Application Note, AN607, "Power-up Trouble Shooting" (DS00607).

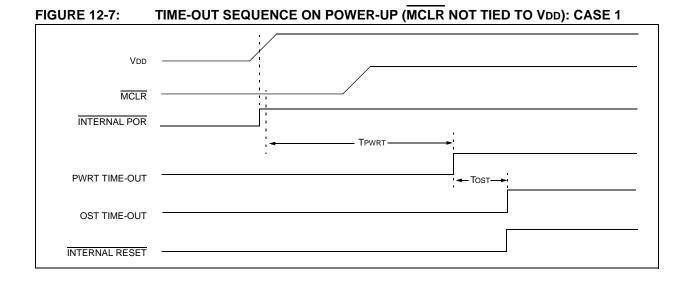

## 12.6 Power-up Timer (PWRT)

The Power-up Timer provides a fixed 72 ms nominal time-out on power-up only from the POR. The Power-up Timer operates on an internal RC oscillator. The chip is kept in RESET as long as the PWRT is active. The PWRT's time delay allows VDD to rise to an accept-able level. A configuration bit is provided to enable/ disable the PWRT.

The power-up time delay will vary from chip to chip, due to VDD, temperature and process variation. See DC parameters for details (TPWRT, parameter #33).

# 12.7 Oscillator Start-up Timer (OST)

The Oscillator Start-up Timer (OST) provides 1024 oscillator cycles (from OSC1 input) delay after the PWRT delay is over (if enabled). This helps to ensure that the crystal oscillator or resonator has started and stabilized.

The OST time-out is invoked only for XT, LP and HS modes and only on Power-on Reset, or wake-up from SLEEP.

## 12.8 Brown-out Reset (BOR)

The configuration bit, BODEN, can enable or disable the Brown-out Reset circuit. If VDD falls below VBOR (parameter D005, about 4V) for longer than TBOR (parameter #35, about 100  $\mu$ S), the brown-out situation will reset the device. If VDD falls below VBOR for less than TBOR, a RESET may not occur.

Once the brown-out occurs, the device will remain in Brown-out Reset until VDD rises above VBOR. The Power-up Timer then keeps the device in RESET for TPWRT (parameter #33, about 72 mS). If VDD should fall below VBOR during TPWRT, the Brown-out Reset process will restart when VDD rises above VBOR, with the Power-up Timer Reset. The Power-up Timer is always enabled when the Brown-out Reset circuit is enabled, regardless of the state of the PWRT configuration bit.

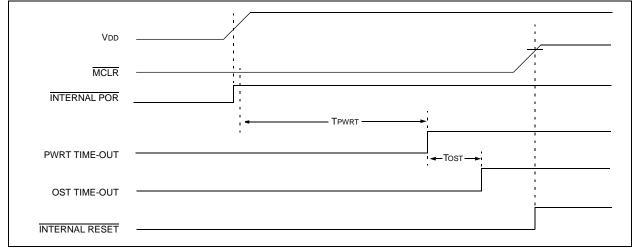

#### 12.9 Time-out Sequence

On power-up, the time-out sequence is as follows: the PWRT delay starts (if enabled) when a POR Reset occurs. Then, OST starts counting 1024 oscillator cycles when PWRT ends (LP, XT, HS). When the OST ends, the device comes out of RESET.

If MCLR is kept low long enough, all delays will expire. Bringing MCLR high will begin execution immediately. This is useful for testing purposes or to synchronize more than one PIC16F7X device operating in parallel.

Table 12-5 shows the RESET conditions for the STATUS, PCON and PC registers, while Table 12-6 shows the RESET conditions for all the registers.

# PIC16F7X

# FIGURE 12-8: TIME-OUT SEQUENCE ON POWER-UP (MCLR NOT TIED TO VDD): CASE 2

# FIGURE 12-9: SLOW RISE TIME (MCLR TIED TO VDD THROUGH RC NETWORK)

## 14.13 PICDEM 3 Low Cost PIC16CXXX Demonstration Board

The PICDEM 3 demonstration board is a simple demonstration board that supports the PIC16C923 and PIC16C924 in the PLCC package. It will also support future 44-pin PLCC microcontrollers with an LCD Module. All the necessary hardware and software is included to run the basic demonstration programs. The user can program the sample microcontrollers provided with the PICDEM 3 demonstration board on a PRO MATE II device programmer, or a PICSTART Plus development programmer with an adapter socket, and easily test firmware. The MPLAB ICE in-circuit emulator may also be used with the PICDEM 3 demonstration board to test firmware. A prototype area has been provided to the user for adding hardware and connecting it to the microcontroller socket(s). Some of the features include a RS-232 interface, push button switches, a potentiometer for simulated analog input, a thermistor and separate headers for connection to an external LCD module and a keypad. Also provided on the PICDEM 3 demonstration board is a LCD panel, with 4 commons and 12 segments, that is capable of displaying time, temperature and day of the week. The PICDEM 3 demonstration board provides an additional RS-232 interface and Windows software for showing the demultiplexed LCD signals on a PC. A simple serial interface allows the user to construct a hardware demultiplexer for the LCD signals.

## 14.14 PICDEM 17 Demonstration Board

The PICDEM 17 demonstration board is an evaluation board that demonstrates the capabilities of several Microchip microcontrollers, including PIC17C752, PIC17C756A, PIC17C762 and PIC17C766. All necessary hardware is included to run basic demo programs, which are supplied on a 3.5-inch disk. A programmed sample is included and the user may erase it and program it with the other sample programs using the PRO MATE II device programmer, or the PICSTART Plus development programmer, and easily debug and test the sample code. In addition, the PICDEM 17 demonstration board supports downloading of programs to and executing out of external FLASH memory on board. The PICDEM 17 demonstration board is also usable with the MPLAB ICE in-circuit emulator, or the PICMASTER emulator and all of the sample programs can be run and modified using either emulator. Additionally, a generous prototype area is available for user hardware.

#### 14.15 KEELOQ Evaluation and Programming Tools

KEELOQ evaluation and programming tools support Microchip's HCS Secure Data Products. The HCS evaluation kit includes a LCD display to show changing codes, a decoder to decode transmissions and a programming interface to program test transmitters.

#### 15.2 DC Characteristics: PIC16F73/74/76/77 (Industrial, Extended) PIC16LF73/74/76/77 (Industrial) (Continued)

| DC CHA       | ARACT | ERISTICS                                     | $\begin{array}{l} \mbox{Standard Operating Conditions (unless otherwise stated)} \\ \mbox{Operating temperature} & -40^{\circ}C \leq TA \leq +85^{\circ}C \mbox{ for industrial} \\ -40^{\circ}C \leq TA \leq +125^{\circ}C \mbox{ for extended} \end{array}$ |      |     |     |                                                                        |  |  |  |

|--------------|-------|----------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|-----|-----|------------------------------------------------------------------------|--|--|--|

|              |       |                                              | Operating voltage VDD range as described in DC Specification,<br>Section 15.1.                                                                                                                                                                                |      |     |     |                                                                        |  |  |  |

| Param<br>No. | Sym   | Characteristic Min Typ† Max Units Conditions |                                                                                                                                                                                                                                                               |      |     |     |                                                                        |  |  |  |

|              | Vol   | Output Low Voltage                           |                                                                                                                                                                                                                                                               |      |     |     |                                                                        |  |  |  |

| D080         |       | I/O ports                                    |                                                                                                                                                                                                                                                               | —    | 0.6 | V   | IOL = 8.5 mA, VDD = 4.5V,<br>-40°C to +125°C                           |  |  |  |

| D083         |       | OSC2/CLKOUT (RC osc config)                  |                                                                                                                                                                                                                                                               | —    | 0.6 | V   | IoL = 1.6 mA, VDD = 4.5V,<br>-40°C to +125°C                           |  |  |  |

|              |       |                                              |                                                                                                                                                                                                                                                               | —    | 0.6 | V   | IOL = 1.2 mA, VDD = 4.5V,<br>-40°C to +125°C                           |  |  |  |

|              | Vон   | Output High Voltage                          |                                                                                                                                                                                                                                                               |      |     |     |                                                                        |  |  |  |

| D090         |       | I/O ports (Note 3)                           | Vdd - 0.7                                                                                                                                                                                                                                                     | _    | _   | V   | IOH = -3.0 mA, VDD = 4.5V,<br>-40°С to +125°С                          |  |  |  |

| D092         |       | OSC2/CLKOUT (RC osc config)                  | Vdd - 0.7                                                                                                                                                                                                                                                     | —    | —   | V   | ІОН = -1.3 mA, VDD = 4.5V,<br>-40°С to +125°С                          |  |  |  |

|              |       |                                              | Vdd - 0.7                                                                                                                                                                                                                                                     | —    | —   | V   | IOH = -1.0 mA, VDD = 4.5V,<br>-40°С to +125°С                          |  |  |  |

| D150*        | Vod   | Open Drain High Voltage                      |                                                                                                                                                                                                                                                               | _    | 12  | V   | RA4 pin                                                                |  |  |  |

|              |       | Capacitive Loading Specs on (                | Dutput Pir                                                                                                                                                                                                                                                    | IS   |     |     |                                                                        |  |  |  |