Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                  |

|----------------------------|-------------------------------------------------------------------------|

| Core Processor             | PIC                                                                     |

| Core Size                  | 8-Bit                                                                   |

| Speed                      | 20MHz                                                                   |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                                       |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                   |

| Number of I/O              | 22                                                                      |

| Program Memory Size        | 7KB (4K x 14)                                                           |

| Program Memory Type        | FLASH                                                                   |

| EEPROM Size                | -                                                                       |

| RAM Size                   | 192 x 8                                                                 |

| Voltage - Supply (Vcc/Vdd) | 4V ~ 5.5V                                                               |

| Data Converters            | A/D 5x8b                                                                |

| Oscillator Type            | External                                                                |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                       |

| Mounting Type              | Surface Mount                                                           |

| Package / Case             | 28-SSOP (0.209", 5.30mm Width)                                          |

| Supplier Device Package    | 28-SSOP                                                                 |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16f73-i-ss |

|                            |                                                                         |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

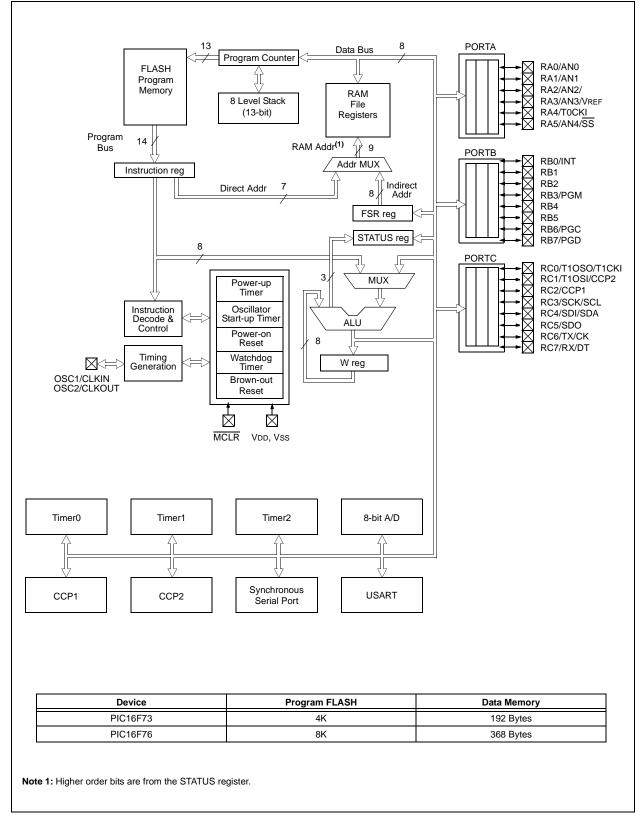

# PIC16F7X

# TABLE 1-3:PIC16F74 AND PIC16F77 PINOUT DESCRIPTION

| OSC1/CLKI<br>OSC1<br>CLKI<br>OSC2/CLKO<br>OSC2<br>CLKO<br>MCLR/VPP<br>MCLR<br>VPP | 13 | 14<br>15 | 30<br>31 | 1        | ST/CMOS <sup>(4)</sup> | Oscillator crystal or external clock input.<br>Oscillator crystal input or external clock source input.<br>ST buffer when configured in RC mode. Otherwise<br>CMOS.<br>External clock source input. Always associated with pin |

|-----------------------------------------------------------------------------------|----|----------|----------|----------|------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| CLKI<br>OSC2/CLKO<br>OSC2<br>CLKO<br><u>MCLR/VPP</u><br>MCLR                      | 14 | 15       | 31       | I        |                        | Oscillator crystal input or external clock source input.<br>ST buffer when configured in RC mode. Otherwise<br>CMOS.<br>External clock source input. Always associated with pin                                                |

| OSC2/CLKO<br>OSC2<br>CLKO<br>MCLR/VPP<br>MCLR                                     | 14 | 15       | 31       |          |                        | CMOS.<br>External clock source input. Always associated with pin                                                                                                                                                               |

| OSC2/CLKO<br>OSC2<br>CLKO<br>MCLR/VPP<br>MCLR                                     | 14 | 15       | 31       |          |                        | External clock source input. Always associated with pin                                                                                                                                                                        |

| OSC2<br>CLKO<br>MCLR/VPP<br>MCLR                                                  | 14 | 15       | 31       |          |                        |                                                                                                                                                                                                                                |

| OSC2<br>CLKO<br>MCLR/VPP<br>MCLR                                                  | 14 | 15       | 31       | 0        |                        | function OSC1 (see OSC1/CLKI, OSC2/CLKO pins).                                                                                                                                                                                 |

| CLKO<br>MCLR/VPP<br>MCLR                                                          |    |          |          | <u> </u> | I —                    | Oscillator crystal or clock output.                                                                                                                                                                                            |

| MCLR/Vpp<br>MCLR                                                                  |    |          |          | 0        |                        | Oscillator crystal output.                                                                                                                                                                                                     |

| MCLR/Vpp<br>MCLR                                                                  |    |          |          |          |                        | Connects to crystal or resonator in Crystal Oscillator                                                                                                                                                                         |

| MCLR/Vpp<br>MCLR                                                                  |    |          |          |          |                        | mode.                                                                                                                                                                                                                          |

| MCLR                                                                              |    |          |          | 0        |                        | In RC mode, OSC2 pin outputs CLKO, which has 1/4                                                                                                                                                                               |

| MCLR                                                                              |    |          |          |          |                        | the frequency of OSC1 and denotes the instruction                                                                                                                                                                              |

| MCLR                                                                              |    |          |          |          |                        | cycle rate.                                                                                                                                                                                                                    |

|                                                                                   | 1  | 2        | 18       |          | ST                     | Master Clear (input) or programming voltage (output).                                                                                                                                                                          |

| Vpp                                                                               |    |          |          | I        |                        | Master Clear (Reset) input. This pin is an active low                                                                                                                                                                          |

| VPP                                                                               |    |          |          |          |                        | RESET to the device.                                                                                                                                                                                                           |

|                                                                                   |    |          |          | Р        |                        | Programming voltage input.                                                                                                                                                                                                     |

|                                                                                   |    |          |          |          |                        | PORTA is a bi-directional I/O port.                                                                                                                                                                                            |

| RA0/AN0                                                                           | 2  | 3        | 19       |          | TTL                    |                                                                                                                                                                                                                                |

| RA0                                                                               |    |          |          | I/O      |                        | Digital I/O.                                                                                                                                                                                                                   |

| AN0                                                                               |    |          |          | I        |                        | Analog input 0.                                                                                                                                                                                                                |

| RA1/AN1                                                                           | 3  | 4        | 20       |          | TTL                    |                                                                                                                                                                                                                                |

| RA1                                                                               |    |          |          | I/O      |                        | Digital I/O.                                                                                                                                                                                                                   |

| AN1                                                                               |    |          |          | I        |                        | Analog input 1.                                                                                                                                                                                                                |

| RA2/AN2                                                                           | 4  | 5        | 21       |          | TTL                    |                                                                                                                                                                                                                                |

| RA2                                                                               |    |          |          | I/O      |                        | Digital I/O.                                                                                                                                                                                                                   |

| AN2                                                                               |    |          |          | I        |                        | Analog input 2.                                                                                                                                                                                                                |

| RA3/AN3/Vref                                                                      | 5  | 6        | 22       |          | TTL                    |                                                                                                                                                                                                                                |

| RA3                                                                               |    |          |          | I/O      |                        | Digital I/O.                                                                                                                                                                                                                   |

| AN3                                                                               |    |          |          | I        |                        | Analog input 3.                                                                                                                                                                                                                |

| VREF                                                                              |    |          |          | I        |                        | A/D reference voltage input.                                                                                                                                                                                                   |

| RA4/T0CKI                                                                         | 6  | 7        | 23       |          | ST                     |                                                                                                                                                                                                                                |

| RA4                                                                               |    |          |          | I/O      |                        | Digital I/O – Open drain when configured as output.                                                                                                                                                                            |

| TOCKI                                                                             |    |          |          | I        |                        | Timer0 external clock input.                                                                                                                                                                                                   |

| RA5/SS/AN4                                                                        | 7  | 8        | 24       |          | TTL                    |                                                                                                                                                                                                                                |

| RA5                                                                               |    | -        |          | I/O      |                        | Digital I/O.                                                                                                                                                                                                                   |

| SS                                                                                | 1  |          |          | 1        |                        | SPI slave select input.                                                                                                                                                                                                        |

| AN4                                                                               |    |          |          |          | 1                      |                                                                                                                                                                                                                                |

| Legend: I = inpu                                                                  |    | 1        |          |          |                        | Analog input 4.                                                                                                                                                                                                                |

— = Not used TTL = TTL input ST = Schmitt Trigger input

**Note 1:** This buffer is a Schmitt Trigger input when configured as an external interrupt.

2: This buffer is a Schmitt Trigger input when used in Serial Programming mode.

**3:** This buffer is a Schmitt Trigger input when configured as general purpose I/O and a TTL input when used in the Parallel Slave Port mode (for interfacing to a microprocessor bus).

4: This buffer is a Schmitt Trigger input when configured in RC Oscillator mode and a CMOS input otherwise.

x = Bit is unknown

#### **PCON Register** 2.2.2.8

The Power Control (PCON) register contains flag bits to allow differentiation between a Power-on Reset (POR), a Brown-out Reset (BOR), a Watchdog Reset (WDT) and an external MCLR Reset.

BOR is unknown on POR. It must be set by Note: the user and checked on subsequent RESETS to see if BOR is clear, indicating a brown-out has occurred. The BOR status bit is not predictable if the brown-out circuit is disabled (by clearing the BODEN bit in the configuration word).

#### **REGISTER 2-8:** PCON REGISTER (ADDRESS 8Eh)

- n = Value at POR reset

|         | U-0                            | U-0         | U-0           | U-0            | U-0          | U-0         | R/W-0         | R/W-1   |  |  |  |  |

|---------|--------------------------------|-------------|---------------|----------------|--------------|-------------|---------------|---------|--|--|--|--|

|         | _                              | _           | _             |                | —            |             | POR           | BOR     |  |  |  |  |

|         | bit 7                          |             |               |                |              |             |               | bit 0   |  |  |  |  |

|         |                                |             |               |                |              |             |               |         |  |  |  |  |

| bit 7-2 | Unimplem                       | ented: Rea  | d as '0'      |                |              |             |               |         |  |  |  |  |

| bit 1   | POR: Pow                       | er-on Reset | Status bit    |                |              |             |               |         |  |  |  |  |

|         | 1 = No Power-on Reset occurred |             |               |                |              |             |               |         |  |  |  |  |

|         | 0 = A Pow                      | er-on Reset | occurred (m   | ust be set in  | software aft | er a Power- | on Reset or   | ccurs)  |  |  |  |  |

| bit 0   | BOR: Brov                      | vn-out Rese | t Status bit  |                |              |             |               |         |  |  |  |  |

|         | 1 = No Bro                     | wn-out Res  | et occurred   |                |              |             |               |         |  |  |  |  |

|         | 0 = A Brow                     | n-out Rese  | t occurred (m | lust be set in | software af  | ter a Brown | -out Reset of | occurs) |  |  |  |  |

|         |                                |             |               |                |              |             |               |         |  |  |  |  |

|         | Legend:                        |             |               |                |              |             |               |         |  |  |  |  |

|         | R = Reada                      | ble bit     | W = W         | ritable bit    | U = Unim     | plemented l | bit, read as  | '0'     |  |  |  |  |

'0' = Bit is cleared

'1' = Bit is set

| Name         | Bit# | Buffer | Function                                                                        |

|--------------|------|--------|---------------------------------------------------------------------------------|

| RA0/AN0      | bit0 | TTL    | Input/output or analog input.                                                   |

| RA1/AN1      | bit1 | TTL    | Input/output or analog input.                                                   |

| RA2/AN2      | bit2 | TTL    | Input/output or analog input.                                                   |

| RA3/AN3/VREF | bit3 | TTL    | Input/output or analog input or VREF.                                           |

| RA4/T0CKI    | bit4 | ST     | Input/output or external clock input for Timer0. Output is open drain type.     |

| RA5/SS/AN4   | bit5 | TTL    | Input/output or slave select input for synchronous serial port or analog input. |

### TABLE 4-1: PORTA FUNCTIONS

Legend: TTL = TTL input, ST = Schmitt Trigger input

# TABLE 4-2: SUMMARY OF REGISTERS ASSOCIATED WITH PORTA

| Address | Name   | Bit 7 | Bit 6 | Bit 5 | Bit 4   | Bit 3      | Bit 2   | Bit 1 | Bit 0 | Value on:<br>POR,<br>BOR | Value on all<br>other<br>RESETS |

|---------|--------|-------|-------|-------|---------|------------|---------|-------|-------|--------------------------|---------------------------------|

| 05h     | PORTA  | _     | _     | RA5   | RA4     | RA3        | RA2     | RA1   | RA0   | 0x 0000                  | 0u 0000                         |

| 85h     | TRISA  | _     | _     | PORTA | Data Di | rection Re | egister |       |       | 11 1111                  | 11 1111                         |

| 9Fh     | ADCON1 |       | _     | _     | _       | _          | PCFG2   | PCFG1 | PCFG0 | 000                      | 000                             |

Legend: x = unknown, u = unchanged, - = unimplemented locations read as '0'. Shaded cells are not used by PORTA.

**Note:** When using the SSP module in SPI Slave mode and  $\overline{SS}$  enabled, the A/D converter must be set to one of the following modes where PCFG2:PCFG0 = 100, 101, 11x.

# 6.0 TIMER1 MODULE

The Timer1 module is a 16-bit timer/counter consisting of two 8-bit registers (TMR1H and TMR1L), which are readable and writable. The TMR1 Register pair (TMR1H:TMR1L) increments from 0000h to FFFFh and rolls over to 0000h. The TMR1 Interrupt, if enabled, is generated on overflow, which is latched in interrupt flag bit TMR1IF (PIR1<0>). This interrupt can be enabled/disabled by setting/clearing TMR1 interrupt enable bit TMR1IE (PIE1<0>).

Timer1 can operate in one of two modes:

- As a timer

- · As a counter

The operating mode is determined by the clock select bit, TMR1CS (T1CON<1>).

In Timer mode, Timer1 increments every instruction cycle. In Counter mode, it increments on every rising edge of the external clock input.

Timer1 can be enabled/disabled by setting/clearing control bit TMR1ON (T1CON<0>).

Timer1 also has an internal "RESET input". This RESET can be generated by either of the two CCP modules as the special event trigger (see Sections 8.1 and 8.2). Register 6-1 shows the Timer1 Control register.

When the Timer1 oscillator is enabled (T1OSCEN is set), the RC1/T1OSI/CCP2 and RC0/T1OSO/T1CKI pins become inputs. That is, the TRISC<1:0> value is ignored and these pins read as '0'.

Additional information on timer modules is available in the PICmicro<sup>™</sup> Mid-Range MCU Family Reference Manual (DS33023).

# REGISTER 6-1: T1CON: TIMER1 CONTROL REGISTER (ADDRESS 10h)

|         |                                                                                             |                                                    |              |                | •                                                                       | ,          |              |         |  |  |  |  |  |  |

|---------|---------------------------------------------------------------------------------------------|----------------------------------------------------|--------------|----------------|-------------------------------------------------------------------------|------------|--------------|---------|--|--|--|--|--|--|

|         | U-0                                                                                         | U-0                                                | R/W-0        | R/W-0          | R/W-0                                                                   | R/W-0      | R/W-0        | R/W-0   |  |  |  |  |  |  |

|         | _                                                                                           | —                                                  | T1CKPS1      | T1CKPS0        | T1OSCEN                                                                 | T1SYNC     | TMR1CS       | TMR10N  |  |  |  |  |  |  |

|         | bit 7                                                                                       |                                                    |              |                |                                                                         |            |              | bit 0   |  |  |  |  |  |  |

|         |                                                                                             |                                                    |              |                |                                                                         |            |              |         |  |  |  |  |  |  |

| bit 7-6 | Unimplem                                                                                    | nented: Rea                                        | d as '0'     |                |                                                                         |            |              |         |  |  |  |  |  |  |

| bit 5-4 |                                                                                             |                                                    | •            | ut Clock Pres  | scale Select I                                                          | bits       |              |         |  |  |  |  |  |  |

|         |                                                                                             | rescale valu                                       |              |                |                                                                         |            |              |         |  |  |  |  |  |  |

|         |                                                                                             | 10 = 1:4 Prescale value<br>01 = 1:2 Prescale value |              |                |                                                                         |            |              |         |  |  |  |  |  |  |

|         |                                                                                             | rescale valu                                       |              |                |                                                                         |            |              |         |  |  |  |  |  |  |

| bit 3   | T1OSCEN                                                                                     | T1OSCEN: Timer1 Oscillator Enable Control bit      |              |                |                                                                         |            |              |         |  |  |  |  |  |  |

|         | 1 = Oscilla                                                                                 | 1 = Oscillator is enabled                          |              |                |                                                                         |            |              |         |  |  |  |  |  |  |

|         | 0 = Oscillator is shut-off (the oscillator inverter is turned off to eliminate power drain) |                                                    |              |                |                                                                         |            |              |         |  |  |  |  |  |  |

| bit 2   | T1SYNC: Timer1 External Clock Input Synchronization Control bit                             |                                                    |              |                |                                                                         |            |              |         |  |  |  |  |  |  |

|         | TMR1CS :                                                                                    |                                                    |              | I.a. a. l      |                                                                         |            |              |         |  |  |  |  |  |  |

|         |                                                                                             | synchronize                                        |              |                |                                                                         |            |              |         |  |  |  |  |  |  |

|         | TMR1CS :                                                                                    |                                                    |              | Jul            |                                                                         |            |              |         |  |  |  |  |  |  |

|         |                                                                                             |                                                    | ner1 uses th | e internal clo | ock when TM                                                             | IR1CS = 0. |              |         |  |  |  |  |  |  |

| bit 1   | TMR1CS:                                                                                     | Timer1 Cloc                                        | k Source S   | elect bit      |                                                                         |            |              |         |  |  |  |  |  |  |

|         |                                                                                             | al clock fron<br>al clock (Fos                     | •            | 10SO/T1Cł      | <i (on="" risi<="" td="" the=""><td>ng edge)</td><td></td><td></td></i> | ng edge)   |              |         |  |  |  |  |  |  |

| bit 0   | TMR10N:                                                                                     | Timer1 On I                                        | bit          |                |                                                                         |            |              |         |  |  |  |  |  |  |

|         | 1 = Enable                                                                                  | es Timer1                                          |              |                |                                                                         |            |              |         |  |  |  |  |  |  |

|         | 0 = Stops                                                                                   | Timer1                                             |              |                |                                                                         |            |              |         |  |  |  |  |  |  |

|         | r                                                                                           |                                                    |              |                |                                                                         |            |              |         |  |  |  |  |  |  |

|         | Legend:                                                                                     |                                                    |              |                |                                                                         |            |              |         |  |  |  |  |  |  |

|         | R = Reada                                                                                   | able bit                                           | W = V        | Nritable bit   | U = Unin                                                                | nplemented | bit, read as | '0'     |  |  |  |  |  |  |

|         | - n = Value                                                                                 | e at POR res                                       | set '1' =    | Bit is set     | '0' = Bit i                                                             | s cleared  | x = Bit is ι | unknown |  |  |  |  |  |  |

|         |                                                                                             |                                                    |              |                |                                                                         |            |              |         |  |  |  |  |  |  |

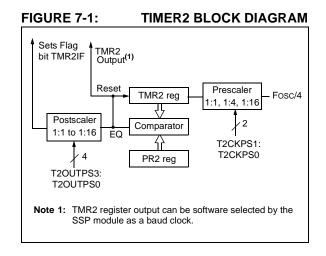

# 7.0 TIMER2 MODULE

Timer2 is an 8-bit timer with a prescaler and a postscaler. It can be used as the PWM time-base for the PWM mode of the CCP module(s). The TMR2 register is readable and writable, and is cleared on any device RESET.

The input clock (Fosc/4) has a prescale option of 1:1, 1:4 or 1:16, selected by control bits T2CKPS1:T2CKPS0 (T2CON<1:0>).

The Timer2 module has an 8-bit period register, PR2. Timer2 increments from 00h until it matches PR2 and then resets to 00h on the next increment cycle. PR2 is a readable and writable register. The PR2 register is initialized to FFh upon RESET.

The match output of TMR2 goes through a 4-bit postscaler (which gives a 1:1 to 1:16 scaling inclusive) to generate a TMR2 interrupt (latched in flag bit TMR2IF, (PIR1<1>)).

Timer2 can be shut-off by clearing control bit TMR2ON (T2CON<2>) to minimize power consumption.

Register 7-1 shows the Timer2 control register.

Additional information on timer modules is available in the PICmicro<sup>™</sup> Mid-Range MCU Family Reference Manual (DS33023).

# 7.1 Timer2 Prescaler and Postscaler

The prescaler and postscaler counters are cleared when any of the following occurs:

- a write to the TMR2 register

- a write to the T2CON register

- any device RESET (POR, MCLR Reset, WDT Reset or BOR)

TMR2 is not cleared when T2CON is written.

# 7.2 Output of TMR2

The output of TMR2 (before the postscaler) is fed to the SSP module, which optionally uses it to generate shift clock.

# 8.5.3 SETUP FOR PWM OPERATION

The following steps should be taken when configuring the CCP module for PWM operation:

- 1. Set the PWM period by writing to the PR2 register.

- 2. Set the PWM duty cycle by writing to the CCPR1L register and CCP1CON<5:4> bits.

- 3. Make the CCP1 pin an output by clearing the TRISC<2> bit.

- 4. Set the TMR2 prescale value and enable Timer2 by writing to T2CON.

- 5. Configure the CCP1 module for PWM operation.

# TABLE 8-4: EXAMPLE PWM FREQUENCIES AND RESOLUTIONS (Fosc = 20 MHz)

| PWM Frequency             | 1.22 kHz | 4.88 kHz | 19.53 kHz | 78.12 kHz | 156.3 kHz | 208.3 kHz |

|---------------------------|----------|----------|-----------|-----------|-----------|-----------|

| Timer Prescale (1, 4, 16) | 16       | 4        | 1         | 1         | 1         | 1         |

| PR2 Value                 | 0xFF     | 0xFF     | 0xFF      | 0x3F      | 0x1F      | 0x17      |

| Maximum Resolution (bits) | 10       | 10       | 10        | 8         | 7         | 5.5       |

# TABLE 8-5: REGISTERS ASSOCIATED WITH PWM AND TIMER2

| Address               | Name    | Bit 7                                      | Bit 6                                                          | Bit 5       | Bit 4     | Bit 3   | Bit 2  | Bit 1   | Bit 0   | PC   | e on:<br>DR,<br>DR | Value on<br>all other<br>RESETS |      |

|-----------------------|---------|--------------------------------------------|----------------------------------------------------------------|-------------|-----------|---------|--------|---------|---------|------|--------------------|---------------------------------|------|

| 0Bh,8Bh,<br>10Bh,18Bh | INTCON  | GIE PEIE TMROIE INTE RBIE TMROIF INTF RBIF |                                                                |             |           |         |        |         |         |      |                    | 0000                            | 000u |

| 0Ch                   | PIR1    | PSPIF <sup>(1)</sup>                       | PSPIF <sup>(1)</sup> ADIF RCIF TXIF SSPIF CCP1IF TMR2IF TMR1IF |             |           |         |        |         |         |      |                    | 0000                            | 0000 |

| 0Dh                   | PIR2    | _                                          | —                                                              | —           |           | _       | —      |         | CCP2IF  |      | 0                  |                                 | 0    |

| 8Ch                   | PIE1    | PSPIE <sup>(1)</sup>                       | ADIE                                                           | RCIE        | TXIE      | SSPIE   | CCP1IE | TMR2IE  | TMR1IE  | 0000 | 0000               | 0000                            | 0000 |

| 8Dh                   | PIE2    | —                                          | CCP2IE                                                         |             |           |         |        |         |         |      | 0                  |                                 | 0    |

| 87h                   | TRISC   | PORTC D                                    | Data Directi                                                   | on Register |           |         |        |         |         | 1111 | 1111               | 1111                            | 1111 |

| 11h                   | TMR2    | Timer2 M                                   | odule Regi                                                     | ster        |           |         |        |         |         | 0000 | 0000               | 0000                            | 0000 |

| 92h                   | PR2     | Timer2 M                                   | odule Peric                                                    | d Register  |           |         |        |         |         | 1111 | 1111               | 1111                            | 1111 |

| 12h                   | T2CON   | _                                          | TOUTPS3                                                        | TOUTPS2     | TOUTPS1   | TOUTPS0 | TMR2ON | T2CKPS1 | T2CKPS0 | -000 | 0000               | -000                            | 0000 |

| 15h                   | CCPR1L  | Capture/C                                  | Compare/P                                                      | VM Registe  | er1 (LSB) |         |        |         |         | xxxx | xxxx               | uuuu                            | uuuu |

| 16h                   | CCPR1H  | Capture/C                                  | Compare/P                                                      | VM Registe  | er1 (MSB) |         |        |         |         | xxxx | xxxx               | uuuu                            | uuuu |

| 17h                   | CCP1CON | _                                          | — — ССР1X ССР1Y ССР1M3 ССР1M2 ССР1M1 ССР1M0                    |             |           |         |        |         |         |      | 0000               | 00                              | 0000 |

| 1Bh                   | CCPR2L  | Capture/Compare/PWM Register2 (LSB)        |                                                                |             |           |         |        |         |         |      | xxxx               | uuuu                            | uuuu |

| 1Ch                   | CCPR2H  | Capture/C                                  | Compare/P                                                      | WM Registe  | er2 (MSB) |         |        |         |         | xxxx | xxxx               | uuuu                            | uuuu |

| 1Dh                   | CCP2CON | —                                          | —                                                              | CCP2X       | CCP2Y     | CCP2M3  | CCP2M2 | CCP2M1  | CCP2M0  | 00   | 0000               | 00                              | 0000 |

Legend: x = unknown, u = unchanged, - = unimplemented, read as '0'. Shaded cells are not used by PWM and Timer2.

Note 1: Bits PSPIE and PSPIF are reserved on the PIC16F73/76; always maintain these bits clear.

# 9.0 SYNCHRONOUS SERIAL PORT (SSP) MODULE

# 9.1 SSP Module Overview

The Synchronous Serial Port (SSP) module is a serial interface useful for communicating with other peripheral or microcontroller devices. These peripheral devices may be Serial EEPROMs, shift registers, display drivers, A/D converters, etc. The SSP module can operate in one of two modes:

- Serial Peripheral Interface (SPI)

- Inter-Integrated Circuit (I<sup>2</sup>C)

An overview of I<sup>2</sup>C operations and additional information on the SSP module can be found in the PICmicro<sup>™</sup> Mid-Range MCU Family Reference Manual (DS33023).

Refer to Application Note AN578, "Use of the SSP Module in the I<sup>2</sup>C Multi-Master Environment" (DS00578).

# 9.2 SPI Mode

This section contains register definitions and operational characteristics of the SPI module. Additional information on the SPI module can be found in the PICmicro<sup>™</sup> Mid-Range MCU Family Reference Manual (DS33023A).

SPI mode allows 8 bits of data to be synchronously transmitted and received simultaneously. To accomplish communication, typically three pins are used:

- Serial Data Out (SDO) RC5/SDO

- Serial Data In (SDI) RC4/SDI/SDA

- Serial Clock (SCK) RC3/SCK/SCL

Additionally, a fourth pin may be used when in a Slave mode of operation:

Slave Select (SS) RA5/SS/AN4

When initializing the SPI, several options need to be specified. This is done by programming the appropriate control bits in the SSPCON register (SSPCON<5:0>) and SSPSTAT<7:6>. These control bits allow the following to be specified:

- Master mode (SCK is the clock output)

- Slave mode (SCK is the clock input)

- Clock Polarity (IDLE state of SCK)

- Clock edge (output data on rising/falling edge of SCK)

- Clock Rate (Master mode only)

- Slave Select mode (Slave mode only)

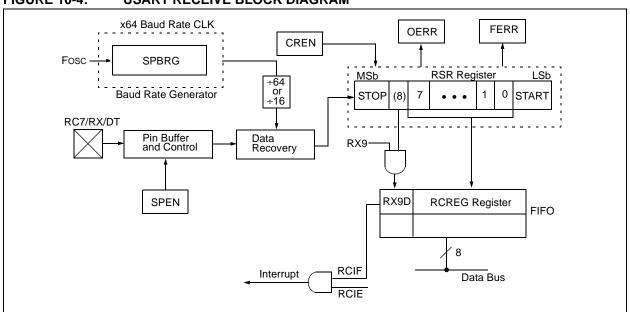

# 10.2.2 USART ASYNCHRONOUS RECEIVER

The receiver block diagram is shown in Figure 10-4. The data is received on the RC7/RX/DT pin and drives the data recovery block. The data recovery block is actually a high speed shifter operating at x16 times the baud rate, whereas the main receive serial shifter operates at the bit rate, or at FOSC.

Once Asynchronous mode is selected, reception is enabled by setting bit CREN (RCSTA<4>).

The heart of the receiver is the receive (serial) shift register (RSR). After sampling the STOP bit, the received data in the RSR is transferred to the RCREG register (if it is empty). If the transfer is complete, flag bit RCIF (PIR1<5>) is set. The actual interrupt can be enabled/ disabled by setting/clearing enable bit RCIE (PIE1<5>). Flag bit RCIF is a read only bit which is cleared by the hardware. It is cleared when the RCREG register has been read and is empty. The RCREG is a double buffered register (i.e., it is a two deep FIFO). It is possible for two bytes of data to be received and transferred to the RCREG FIFO and a third byte to begin shifting to the RSR register. On the detection of the STOP bit of the third byte, if the RCREG register is still full, the overrun error bit OERR (RCSTA<1>) will be set. The word in the RSR will be lost. The RCREG register can be read twice to retrieve the two bytes in the FIFO. Overrun bit OERR has to be cleared in software. This is done by resetting the receive logic (CREN is cleared and then set). If bit OERR is set, transfers from the RSR register to the RCREG register are inhibited and no further data will be received, therefore, it is essential to clear error bit OERR if it is set. Framing error bit FERR (RCSTA<2>) is set if a STOP bit is detected as clear. Bit FERR and the 9th receive bit are buffered the same way as the receive data. Reading the RCREG will load bits RX9D and FERR with new values, therefore, it is essential for the user to read the RCSTA register before reading RCREG register, in order not to lose the old FERR and RX9D information.

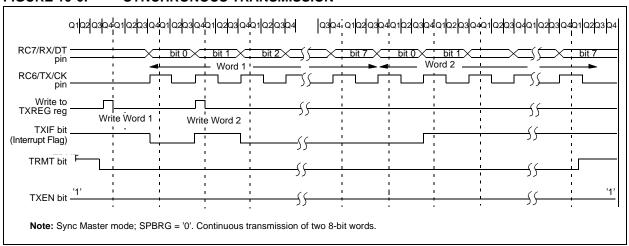

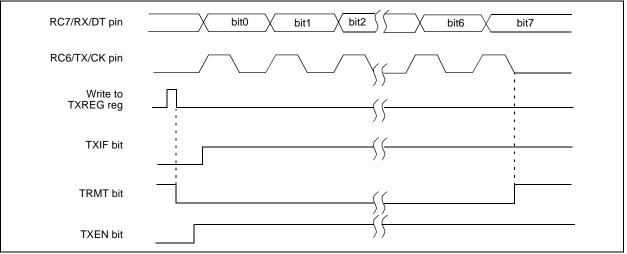

# FIGURE 10-6: SYNCHRONOUS TRANSMISSION

# FIGURE 10-7: SYNCHRONOUS TRANSMISSION (THROUGH TXEN)

# TABLE 10-7: REGISTERS ASSOCIATED WITH SYNCHRONOUS MASTER TRANSMISSION

| Address                | Name   | Bit 7                | Bit 6     | Bit 5      | Bit 4 | Bit 3 | Bit 2  | Bit 1  | Bit 0  | Value on:<br>POR,<br>BOR | Value on<br>all other<br>RESETS |

|------------------------|--------|----------------------|-----------|------------|-------|-------|--------|--------|--------|--------------------------|---------------------------------|

| 0Bh, 8Bh,<br>10Bh,18Bh | INTCON | GIE                  | PEIE      | TMR0IE     | INTE  | RBIE  | TMR0IF | INTF   | RBIF   | 0000 000x                | 0000 000u                       |

| 0Ch                    | PIR1   | PSPIF <sup>(1)</sup> | ADIF      | RCIF       | TXIF  | SSPIF | CCP1IF | TMR2IF | TMR1IF | 0000 0000                | 0000 0000                       |

| 18h                    | RCSTA  | SPEN                 | RX9       | SREN       | CREN  | _     | FERR   | OERR   | RX9D   | 0000 -00x                | 0000 -00x                       |

| 19h                    | TXREG  | USART Tr             | ansmit Re | egister    |       |       |        |        |        | 0000 0000                | 0000 0000                       |

| 8Ch                    | PIE1   | PSPIE <sup>(1)</sup> | ADIE      | RCIE       | TXIE  | SSPIE | CCP1IE | TMR2IE | TMR1IE | 0000 0000                | 0000 0000                       |

| 98h                    | TXSTA  | CSRC                 | TX9       | TXEN       | SYNC  | _     | BRGH   | TRMT   | TX9D   | 0000 -010                | 0000 -010                       |

| 99h                    | SPBRG  | Baud Rate            | Generat   | or Registe | r     |       |        |        |        | 0000 0000                | 0000 0000                       |

Legend: x = unknown, - = unimplemented, read as '0'. Shaded cells are not used for synchronous master transmission.

Note 1: Bits PSPIE and PSPIF are reserved on the PIC16F73/76 devices; always maintain these bits clear.

| Address                | Name   | Bit 7                | Bit 6    | Bit 5      | Bit 4 | Bit 3     | Bit 2     | Bit 1  | Bit 0  | Value on:<br>POR,<br>BOR | Value on<br>all other<br>RESETS |

|------------------------|--------|----------------------|----------|------------|-------|-----------|-----------|--------|--------|--------------------------|---------------------------------|

| 0Bh, 8Bh,<br>10Bh,18Bh | INTCON | GIE                  | PEIE     | TMR0IE     | INTE  | RBIE      | TMR0IF    | INTF   | RBIF   | 0000 000x                | 0000 000u                       |

| 0Ch                    | PIR1   | PSPIF <sup>(1)</sup> | ADIF     | RCIF       | TXIF  | SSPIF     | CCP1IF    | TMR2IF | TMR1IF | 0000 0000                | 0000 0000                       |

| 18h                    | RCSTA  | SPEN                 | RX9      | SREN       | CREN  | ADDEN     | FERR      | OERR   | RX9D   | 0000 000x                | 0000 000x                       |

| 19h                    | TXREG  | USART Tr             | ansmit R | egister    |       |           |           |        |        | 0000 0000                | 0000 0000                       |

| 8Ch                    | PIE1   | PSPIE <sup>(1)</sup> | ADIE     | RCIE       | TXIE  | SSPIE     | CCP1IE    | TMR2IE | TMR1IE | 0000 0000                | 0000 0000                       |

| 98h                    | TXSTA  | CSRC                 | TX9      | TXEN       | SYNC  | —         | BRGH      | TRMT   | TX9D   | 0000 -010                | 0000 -010                       |

| 99h                    | SPBRG  | Baud Rate            | Generat  | or Registe |       | 0000 0000 | 0000 0000 |        |        |                          |                                 |

Legend: x = unknown, - = unimplemented, read as '0'. Shaded cells are not used for synchronous slave transmission.

Note 1: Bits PSPIE and PSPIF are reserved on the PIC16F73/76 devices; always maintain these bits clear.

# 10.4.2 USART SYNCHRONOUS SLAVE RECEPTION

The operation of the Synchronous Master and Slave modes is identical, except in the case of the SLEEP mode. Bit SREN is a "don't care" in Slave mode.

If receive is enabled by setting bit CREN prior to the SLEEP instruction, then a word may be received during SLEEP. On completely receiving the word, the RSR register will transfer the data to the RCREG register and if enable bit RCIE bit is set, the interrupt generated will wake the chip from SLEEP. If the global interrupt is enabled, the program will branch to the interrupt vector (0004h).

Follow these steps when setting up a Synchronous Slave Reception:

- Enable the synchronous master serial port by setting bits SYNC and SPEN and clearing bit CSRC.

- 2. If interrupts are desired, set enable bit RCIE.

- 3. If 9-bit reception is desired, set bit RX9.

- 4. To enable reception, set enable bit CREN.

- 5. Flag bit RCIF will be set when reception is complete and an interrupt will be generated, if enable bit RCIE was set.

- Read the RCSTA register to get the ninth bit (if enabled) and determine if any error occurred during reception.

- 7. Read the 8-bit received data by reading the RCREG register.

- 8. If any error occurred, clear the error by clearing bit CREN.

- 9. If using interrupts, ensure that GIE and PEIE in the INTCON register are set.

| Address                | Name   | Bit 7                | Bit 6    | Bit 5        | Bit 4 | Bit 3 | Bit 2  | Bit 1  | Bit 0  | Value on:<br>POR,<br>BOR | Value on<br>all other<br>RESETS |

|------------------------|--------|----------------------|----------|--------------|-------|-------|--------|--------|--------|--------------------------|---------------------------------|

| 0Bh, 8Bh,<br>10Bh,18Bh | INTCON | GIE                  | PEIE     | TMR0IE       | INTE  | RBIE  | TMR0IF | INTF   | RBIF   | 0000 000x                | 0000 000u                       |

| 0Ch                    | PIR1   | PSPIF <sup>(1)</sup> | ADIF     | RCIF         | TXIF  | SSPIF | CCP1IF | TMR2IF | TMR1IF | 0000 0000                | 0000 0000                       |

| 18h                    | RCSTA  | SPEN                 | RX9      | SREN         | CREN  | ADDEN | FERR   | OERR   | RX9D   | 0000 000x                | 0000 000x                       |

| 1Ah                    | RCREG  | USART R              | eceive R | egister      |       |       |        |        |        | 0000 0000                | 0000 0000                       |

| 8Ch                    | PIE1   | PSPIE <sup>(1)</sup> | ADIE     | RCIE         | TXIE  | SSPIE | CCP1IE | TMR2IE | TMR1IE | 0000 0000                | 0000 0000                       |

| 98h                    | TXSTA  | CSRC                 | TX9      | TXEN         | SYNC  | _     | BRGH   | TRMT   | TX9D   | 0000 -010                | 0000 -010                       |

| 99h                    | SPBRG  | Baud Rate            | e Genera | ator Registe | er    |       |        |        |        | 0000 0000                | 0000 0000                       |

# TABLE 10-10: REGISTERS ASSOCIATED WITH SYNCHRONOUS SLAVE RECEPTION

Legend: x = unknown, - = unimplemented, read as '0'. Shaded cells are not used for synchronous slave reception. Note 1: Bits PSPIE and PSPIF are reserved on the PIC16F73/76 devices, always maintain these bits clear.

# **12.2** Oscillator Configurations

# 12.2.1 OSCILLATOR TYPES

The PIC16F7X can be operated in four different oscillator modes. The user can program two configuration bits (FOSC1 and FOSC0) to select one of these four modes:

- LP Low Power Crystal

- XT Crystal/Resonator

- HS High Speed Crystal/Resonator

- RC Resistor/Capacitor

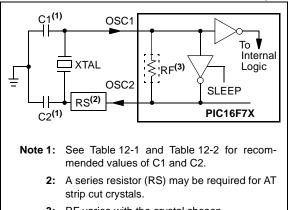

# 12.2.2 CRYSTAL OSCILLATOR/CERAMIC RESONATORS

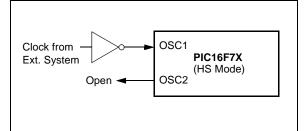

In XT, LP or HS modes, a crystal or ceramic resonator is connected to the OSC1/CLKIN and OSC2/CLKOUT pins to establish oscillation (Figure 12-1). The PIC16F7X oscillator design requires the use of a parallel cut crystal. Use of a series cut crystal may give a frequency out of the crystal manufacturers specifications. When in HS mode, the device can accept an external clock source to drive the OSC1/CLKIN pin (Figure 12-2). See Figure 15-1 or Figure 15-2 (depending on the part number and VDD range) for valid external clock frequencies.

### FIGURE 12-1: CRYSTAL/CERAMIC RESONATOR OPERATION (HS, XT OR LP OSC CONFIGURATION)

3: RF varies with the crystal chosen.

# FIGURE 12-2:

#### EXTERNAL CLOCK INPUT OPERATION (HS OSC CONFIGURATION)

### TABLE 12-1: CERAMIC RESONATORS (FOR DESIGN GUIDANCE ONLY)

| Typical Capacitor Values Used: |          |       |       |  |  |  |  |

|--------------------------------|----------|-------|-------|--|--|--|--|

| Mode Freq OSC1 OSC2            |          |       |       |  |  |  |  |

| XT                             | 455 kHz  | 56 pF | 56 pF |  |  |  |  |

|                                | 2.0 MHz  | 47 pF | 47 pF |  |  |  |  |

|                                | 4.0 MHz  | 33 pF | 33 pF |  |  |  |  |

| HS                             | 8.0 MHz  | 27 pF | 27 pF |  |  |  |  |

|                                | 16.0 MHz | 22 pF | 22 pF |  |  |  |  |

Capacitor values are for design guidance only.

These capacitors were tested with the resonators listed below for basic start-up and operation. These values were not optimized.

Different capacitor values may be required to produce acceptable oscillator operation. The user should test the performance of the oscillator over the expected VDD and temperature range for the application.

See the notes at the bottom of page 92 for additional information.

| Resonators Used: |                        |  |

|------------------|------------------------|--|

| 455 kHz          | Panasonic EFO-A455K04B |  |

| 2.0 MHz          | Murata Erie CSA2.00MG  |  |

| 4.0 MHz          | Murata Erie CSA4.00MG  |  |

| 8.0 MHz          | Murata Erie CSA8.00MT  |  |

| 16.0 MHz         | Murata Erie CSA16.00MX |  |

### TABLE 12-2: CAPACITOR SELECTION FOR CRYSTAL OSCILLATOR (FOR DESIGN GUIDANCE ONLY)

| Osc Type | Crystal<br>Freq | Typical Capacitor Values<br>Tested: |       |  |

|----------|-----------------|-------------------------------------|-------|--|

|          | ITEG            | C1                                  | C2    |  |

| LP       | 32 kHz          | 33 pF                               | 33 pF |  |

|          | 200 kHz         | 15 pF                               | 15 pF |  |

| XT       | 200 kHz         | 56 pF                               | 56 pF |  |

|          | 1 MHz           | 15 pF                               | 15 pF |  |

|          | 4 MHz           | 15 pF                               | 15 pF |  |

| HS       | 4 MHz           | 15 pF                               | 15 pF |  |

|          | 8 MHz           | 15 pF                               | 15 pF |  |

|          | 20 MHz          | 15 pF                               | 15 pF |  |

#### Capacitor values are for design guidance only.

These capacitors were tested with the crystals listed below for basic start-up and operation. These values were not optimized.

Different capacitor values may be required to produce acceptable oscillator operation. The user should test the performance of the oscillator over the expected VDD and temperature range for the application.

See the notes following this table for additional information.

| Crystals Used: |                        |  |

|----------------|------------------------|--|

| 32 kHz         | Epson C-001R32.768K-A  |  |

| 200 kHz        | STD XTL 200.000KHz     |  |

| 1 MHz          | ECS ECS-10-13-1        |  |

| 4 MHz          | ECS ECS-40-20-1        |  |

| 8 MHz          | EPSON CA-301 8.000M-C  |  |

| 20 MHz         | EPSON CA-301 20.000M-C |  |

- **Note 1:** Higher capacitance increases the stability of oscillator, but also increases the start-up time.

- 2: Since each resonator/crystal has its own characteristics, the user should consult the resonator/crystal manufacturer for appropriate values of external components.

- 3: Rs may be required in HS mode, as well as XT mode, to avoid overdriving crystals with low drive level specification.

- **4:** Always verify oscillator performance over the VDD and temperature range that is expected for the application.

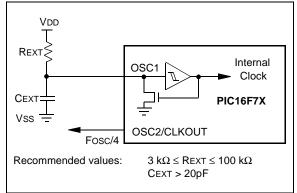

### 12.2.3 RC OSCILLATOR

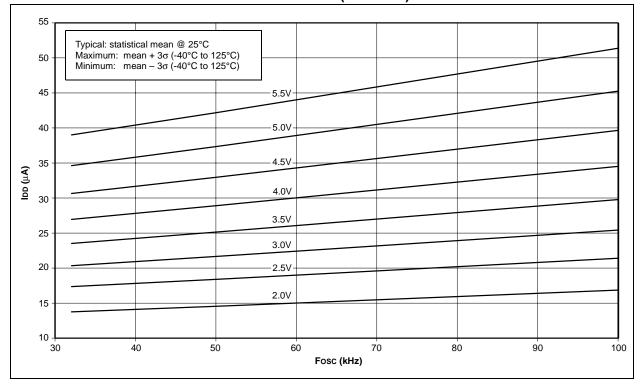

For timing insensitive applications, the "RC" device option offers additional cost savings. The RC oscillator frequency is a function of the supply voltage, the resistor (REXT) and capacitor (CEXT) values, and the operating temperature. In addition to this, the oscillator frequency will vary from unit to unit due to normal process parameter variation. Furthermore, the difference in lead frame capacitance between package types will also affect the oscillation frequency, especially for low CEXT values. The user also needs to take into account variation due to tolerance of external R and C components used. Figure 12-3 shows how the R/C combination is connected to the PIC16F7X.

# PIC16F7X

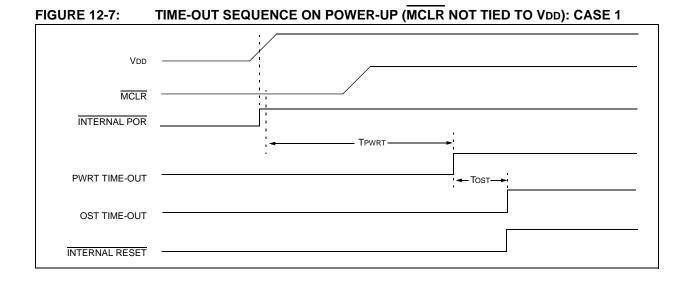

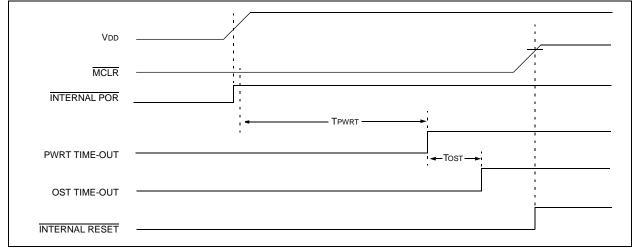

# FIGURE 12-8: TIME-OUT SEQUENCE ON POWER-UP (MCLR NOT TIED TO VDD): CASE 2

# FIGURE 12-9: SLOW RISE TIME (MCLR TIED TO VDD THROUGH RC NETWORK)

| RLF              | Rotate Left f through Carry                                                                                                                                                                                   |  |  |  |  |

|------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| Syntax:          | [ <i>label</i> ] RLF f,d                                                                                                                                                                                      |  |  |  |  |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ d \in \left[0,1\right] \end{array}$                                                                                                                                    |  |  |  |  |

| Operation:       | See description below                                                                                                                                                                                         |  |  |  |  |

| Status Affected: | С                                                                                                                                                                                                             |  |  |  |  |

| Description:     | The contents of register 'f' are rotated<br>one bit to the left through the Carry<br>Flag. If 'd' is 0, the result is placed in<br>the W register. If 'd' is 1, the result is<br>stored back in register 'f'. |  |  |  |  |

# SLEEP

| Syntax:          | [label] SLEEP                                                                                                                                                                                                                        |

|------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Operands:        | None                                                                                                                                                                                                                                 |

| Operation:       | $\begin{array}{l} 00h \rightarrow WDT, \\ 0 \rightarrow WDT \text{ prescaler,} \\ 1 \rightarrow \overline{TO}, \\ 0 \rightarrow \overline{PD} \end{array}$                                                                           |

| Status Affected: | TO, PD                                                                                                                                                                                                                               |

| Description:     | The power-down status bit, $\overline{\text{PD}}$ is cleared. Time-out status bit, $\overline{\text{TO}}$ is set. Watchdog Timer and its prescaler are cleared.<br>The processor is put into SLEEP mode with the oscillator stopped. |

| RETURN           | Return from Subroutine                                                                                                                                     |  |  |  |  |

|------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| Syntax:          | [label] RETURN                                                                                                                                             |  |  |  |  |

| Operands:        | None                                                                                                                                                       |  |  |  |  |

| Operation:       | $TOS\toPC$                                                                                                                                                 |  |  |  |  |

| Status Affected: | None                                                                                                                                                       |  |  |  |  |

| Description:     | Return from subroutine. The stack<br>is POPed and the top of the stack<br>(TOS) is loaded into the program<br>counter. This is a two-cycle<br>instruction. |  |  |  |  |

| RRF              | Rotate Right f through Carry                                                                                                                                                                                      |  |  |  |

|------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| Syntax:          | [ <i>label</i> ] RRF f,d                                                                                                                                                                                          |  |  |  |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ d \in \ [0,1] \end{array}$                                                                                                                                                 |  |  |  |

| Operation:       | See description below                                                                                                                                                                                             |  |  |  |

| Status Affected: | С                                                                                                                                                                                                                 |  |  |  |

| Description:     | The contents of register 'f' are<br>rotated one bit to the right through<br>the Carry Flag. If 'd' is 0, the result<br>is placed in the W register. If 'd' is<br>1, the result is placed back in<br>register 'f'. |  |  |  |

|                  | C Register f                                                                                                                                                                                                      |  |  |  |

| SUBLW            | Subtract W from Literal                                                                                                      |  |  |  |

|------------------|------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| Syntax:          | [ <i>label</i> ] SUBLW k                                                                                                     |  |  |  |

| Operands:        | $0 \le k \le 255$                                                                                                            |  |  |  |

| Operation:       | $k \text{ - (W)} \rightarrow (W)$                                                                                            |  |  |  |

| Status Affected: | C, DC, Z                                                                                                                     |  |  |  |

| Description:     | The W register is subtracted (2's complement method) from the eight-bit literal 'k'. The result is placed in the W register. |  |  |  |

| SUBWF            | Subtract W from f                                                                                                                                                                       |  |  |  |

|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| Syntax:          | [ <i>label</i> ] SUBWF f,d                                                                                                                                                              |  |  |  |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ d \in \ [0,1] \end{array}$                                                                                                                       |  |  |  |

| Operation:       | (f) - (W) $\rightarrow$ (destination)                                                                                                                                                   |  |  |  |

| Status Affected: | C, DC, Z                                                                                                                                                                                |  |  |  |

| Description:     | Subtract (2's complement method)<br>W register from register 'f'. If 'd' is 0,<br>the result is stored in the W<br>register. If 'd' is 1, the result is<br>stored back in register 'f'. |  |  |  |

#### 15.2 **DC Characteristics:** PIC16F73/74/76/77 (Industrial, Extended) PIC16LF73/74/76/77 (Industrial)

| DC CHARACTERISTICS |       | $\begin{array}{llllllllllllllllllllllllllllllllllll$ |                   |     |         |    |                                                             |

|--------------------|-------|------------------------------------------------------|-------------------|-----|---------|----|-------------------------------------------------------------|

| Param<br>No.       | Sym   | Characteristic Min Typ† Max Units Conditions         |                   |     |         |    |                                                             |

|                    | VIL   | Input Low Voltage                                    |                   |     |         |    |                                                             |

|                    |       | I/O ports:                                           |                   |     |         |    |                                                             |

| D030               |       | with TTL buffer                                      | Vss               | _   | 0.15Vdd | V  | For entire VDD range                                        |

| D030A              |       |                                                      | Vss               | _   | 0.8V    | V  | $4.5V \le VDD \le 5.5V$                                     |

| D031               |       | with Schmitt Trigger buffer                          | Vss               | —   | 0.2Vdd  | V  |                                                             |

| D032               |       | MCLR, OSC1 (in RC mode)                              | Vss               | _   | 0.2Vdd  | V  | (Note 1)                                                    |

| D033               |       | OSC1 (in XT and LP mode)                             | Vss               | _   | 0.3V    | V  |                                                             |

|                    |       | OSC1 (in HS mode)                                    | Vss               | _   | 0.3Vdd  | V  |                                                             |

|                    | Vih   | Input High Voltage                                   |                   |     |         |    |                                                             |

|                    |       | I/O ports:                                           |                   |     |         |    |                                                             |

| D040               |       | with TTL buffer                                      | 2.0               | —   | Vdd     | V  | $4.5V \le VDD \le 5.5V$                                     |

| D040A              |       |                                                      | 0.25Vdd<br>+ 0.8V | —   | Vdd     | V  | For entire VDD range                                        |

| D041               |       | with Schmitt Trigger buffer                          | 0.8Vdd            | —   | Vdd     | V  | For entire VDD range                                        |

| D042               |       | MCLR                                                 | 0.8Vdd            | _   | Vdd     | V  |                                                             |

| D042A              |       | OSC1 (in XT and LP mode)                             | 1.6V              | _   | Vdd     | V  |                                                             |

|                    |       | OSC1 (in HS mode)                                    | 0.7Vdd            | —   | Vdd     | V  |                                                             |

| D043               |       | OSC1 (in RC mode)                                    | 0.9Vdd            |     | Vdd     | V  | (Note 1)                                                    |

| D070               | IPURB | PORTB Weak Pull-up Current                           | 50                | 250 | 400     | μΑ | VDD = 5V, VPIN = VSS                                        |

|                    | lı∟   | Input Leakage Current (Notes 2                       | 2, 3)             |     |         |    |                                                             |

| D060               |       | I/O ports                                            | _                 |     | ±1      | μA | $Vss \leq VPIN \leq VDD$ , pin at hi-impedance              |

| D061               |       | MCLR, RA4/T0CKI                                      | —                 | —   | ±5      | μA | $Vss \leq VPIN \leq VDD$                                    |

| D063               |       | OSC1                                                 | —                 | —   | ±5      | μA | Vss $\leq$ VPIN $\leq$ VDD, XT, HS and LP osc configuration |

These parameters are characterized but not tested.

Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance † only and are not tested.

Note 1: In RC oscillator configuration, the OSC1/CLKIN pin is a Schmitt Trigger input. It is not recommended that the PIC16F7X be driven with external clock in RC mode.

2: The leakage current on the MCLR pin is strongly dependent on the applied voltage level. The specified levels represent normal operating conditions. Higher leakage current may be measured at different input voltages.

3: Negative current is defined as current sourced by the pin.

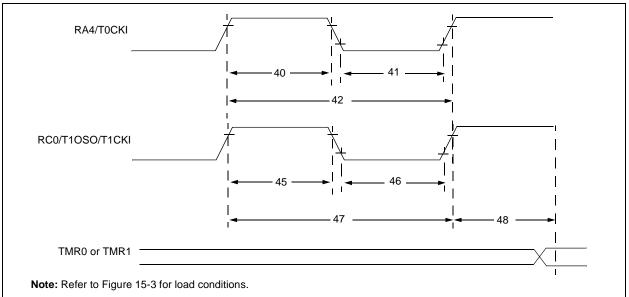

FIGURE 15-8: TIMER0 AND TIMER1 EXTERNAL CLOCK TIMINGS

| <b>TABLE 15-4</b> : | TIMER0 AND TIMER1 EXTERNAL CLOCK REQUIREMENTS |

|---------------------|-----------------------------------------------|

|                     |                                               |

| Param<br>No. | Symbol    |                                            | Characteristic                    |                       |                                           |     | Max    | Units | Conditions                         |  |

|--------------|-----------|--------------------------------------------|-----------------------------------|-----------------------|-------------------------------------------|-----|--------|-------|------------------------------------|--|

| 40*          | Tt0H      | T0CKI High Pulse Width                     |                                   | No Prescaler          | 0.5Tcy + 20                               | —   |        | ns    | Must also meet parameter 42        |  |

|              |           |                                            |                                   | With Prescaler        | 10                                        | —   | _      | ns    |                                    |  |

| 41*          | Tt0L      | T0CKI Low Pulse Width                      |                                   | No Prescaler          | 0.5Tcy + 20                               | —   | _      | ns    | Must also meet                     |  |

|              |           |                                            |                                   | With Prescaler        | 10                                        | —   | _      | ns    | parameter 42                       |  |

| 42*          | Tt0P      | T0CKI Period                               |                                   | No Prescaler          | Tcy + 40                                  | —   | _      | ns    |                                    |  |

|              |           |                                            |                                   | With Prescaler        | /ith Prescaler Greater of: —              |     | —      | ns    | N = prescale value<br>(2, 4,, 256) |  |

|              |           |                                            |                                   |                       | 20 or <u>Tcy + 40</u>                     |     |        |       |                                    |  |

|              |           |                                            |                                   |                       | N                                         |     |        |       |                                    |  |

| 45*          | Tt1H      | T1CKI High Time                            | Synchronous, Pr                   |                       | 0.5Tcy + 20                               | —   | —      | ns    | Must also meet                     |  |

|              |           |                                            | Synchronous,<br>Prescaler = 2,4,8 | Standard(F)           | 15                                        | —   | —      | ns    | parameter 47                       |  |

|              |           |                                            |                                   | Extended(LF)          | 25                                        | —   | —      | ns    |                                    |  |

|              |           |                                            | Asynchronous                      | Standard(F)           | 30                                        | —   | _      | ns    |                                    |  |

|              |           |                                            |                                   | Extended(LF)          | 50                                        | -   | —      | ns    |                                    |  |