Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                                          |

|----------------------------|--------------------------------------------------------------------------|

| Product Status             | Active                                                                   |

| Core Processor             | PIC                                                                      |

| Core Size                  | 8-Bit                                                                    |

| Speed                      | 20MHz                                                                    |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                                        |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                    |

| Number of I/O              | 22                                                                       |

| Program Memory Size        | 7KB (4K x 14)                                                            |

| Program Memory Type        | FLASH                                                                    |

| EEPROM Size                | -                                                                        |

| RAM Size                   | 192 x 8                                                                  |

| Voltage - Supply (Vcc/Vdd) | 4V ~ 5.5V                                                                |

| Data Converters            | A/D 5x8b                                                                 |

| Oscillator Type            | External                                                                 |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                       |

| Mounting Type              | Surface Mount                                                            |

| Package / Case             | 28-SSOP (0.209", 5.30mm Width)                                           |

| Supplier Device Package    | 28-SSOP                                                                  |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16f73t-e-ss |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### Note the following details of the code protection feature on PICmicro® MCUs.

- The PICmicro family meets the specifications contained in the Microchip Data Sheet.

- Microchip believes that its family of PICmicro microcontrollers is one of the most secure products of its kind on the market today, when used in the intended manner and under normal conditions.

- There are dishonest and possibly illegal methods used to breach the code protection feature. All of these methods, to our knowledge, require using the PICmicro microcontroller in a manner outside the operating specifications contained in the data sheet. The person doing so may be engaged in theft of intellectual property.

- Microchip is willing to work with the customer who is concerned about the integrity of their code.

- Neither Microchip nor any other semiconductor manufacturer can guarantee the security of their code. Code protection does not

mean that we are guaranteeing the product as "unbreakable".

- Code protection is constantly evolving. We at Microchip are committed to continuously improving the code protection features of our product.

If you have any further questions about this matter, please contact the local sales office nearest to you.

Information contained in this publication regarding device applications and the like is intended through suggestion only and may be superseded by updates. It is your responsibility to ensure that your application meets with your specifications. No representation or warranty is given and no liability is assumed by Microchip Technology Incorporated with respect to the accuracy or use of such information, or infringement of patents or other intellectual property rights arising from such use or otherwise. Use of Microchip's products as critical components in life support systems is not authorized except with express written approval by Microchip. No licenses are conveyed, implicitly or otherwise, under any intellectual property rights.

#### **Trademarks**

The Microchip name and logo, the Microchip logo, FilterLab, KEELOQ, MPLAB, PIC, PICmicro, PICMASTER, PICSTART, PRO MATE, SEEVAL and The Embedded Control Solutions Company are registered trademarks of Microchip Technology Incorporated in the U.S.A. and other countries.

dsPIC, ECONOMONITOR, FanSense, FlexROM, fuzzyLAB, In-Circuit Serial Programming, ICSP, ICEPIC, microID, microPort, Migratable Memory, MPASM, MPLIB, MPLINK, MPSIM, MXDEV, PICC, PICDEM, PICDEM.net, rfPIC, Select Mode and Total Endurance are trademarks of Microchip Technology Incorporated in the U.S.A.

Serialized Quick Term Programming (SQTP) is a service mark of Microchip Technology Incorporated in the U.S.A.

All other trademarks mentioned herein are property of their respective companies.

© 2002, Microchip Technology Incorporated, Printed in the U.S.A., All Rights Reserved.

Microchip received QS-9000 quality system certification for its worldwide headquarters, design and wafer fabrication facilities in Chandler and Tempe, Arizona in July 1999. The Company's quality system processes and procedures are QS-9000 compliant for its PICmicro® 8-bit MCUs, KEELO® code hopping devices, Serial EEPROMs and microperipheral products. In addition, Microchip's quality system for the design and manufacture of development systems is ISO 9001 certified.

TABLE 1-3: PIC16F74 AND PIC16F77 PINOUT DESCRIPTION (CONTINUED)

| Pin Name          | DIP<br>Pin# | PLCC<br>Pin# | QFP<br>Pin# | I/O/P<br>Type | Buffer<br>Type        | Description                                                                                                          |

|-------------------|-------------|--------------|-------------|---------------|-----------------------|----------------------------------------------------------------------------------------------------------------------|

|                   |             |              |             |               |                       | PORTB is a bi-directional I/O port. PORTB can be software programmed for internal weak pull-up on all inputs.        |

| RB0/INT           | 33          | 36           | 8           |               | TTL/ST <sup>(1)</sup> |                                                                                                                      |

| RB0<br>INT        |             |              |             | I/O<br>I      |                       | Digital I/O. External interrupt.                                                                                     |

| RB1               | 34          | 37           | 9           | I/O           | TTL                   | Digital I/O.                                                                                                         |

| RB2               | 35          | 38           | 10          | I/O           | TTL                   | Digital I/O.                                                                                                         |

| RB3/PGM           | 36          | 39           | 11          |               | TTL                   |                                                                                                                      |

| RB3               |             |              |             | I/O           |                       | Digital I/O.                                                                                                         |

| PGM               |             |              |             | I/O           |                       | Low voltage ICSP programming enable pin.                                                                             |

| RB4               | 37          | 41           | 14          | I/O           | TTL                   | Digital I/O.                                                                                                         |

| RB5               | 38          | 42           | 15          | I/O           | TTL                   | Digital I/O.                                                                                                         |

| RB6/PGC           | 39          | 43           | 16          |               | TTL/ST <sup>(2)</sup> |                                                                                                                      |

| RB6               |             |              |             | I/O           |                       | Digital I/O.                                                                                                         |

| PGC               |             |              |             | I/O           | 4-1                   | In-Circuit Debugger and ICSP programming clock.                                                                      |

| RB7/PGD           | 40          | 44           | 17          |               | TTL/ST <sup>(2)</sup> |                                                                                                                      |

| RB7               |             |              |             | I/O           |                       | Digital I/O.                                                                                                         |

| PGD               |             |              |             | I/O           |                       | In-Circuit Debugger and ICSP programming data.                                                                       |

|                   |             |              |             |               |                       | PORTC is a bi-directional I/O port.                                                                                  |

| RC0/T1OSO/T1CKI   | 15          | 16           | 32          |               | ST                    | 5: :: 11/0                                                                                                           |

| RC0<br>T1OSO      |             |              |             | I/O<br>O      |                       | Digital I/O.                                                                                                         |

| T1CKI             |             |              |             | ı             |                       | Timer1 oscillator output. Timer1 external clock input.                                                               |

| RC1/T1OSI/CCP2    | 16          | 18           | 35          | '             | ST                    | Time i external desix inpat.                                                                                         |

| RC1               | 10          | '0           | 33          | I/O           | 01                    | Digital I/O.                                                                                                         |

| T1OSI             |             |              |             | I             |                       | Timer1 oscillator input.                                                                                             |

| CCP2              |             |              |             | I/O           |                       | Capture2 input, Compare2 output, PWM2 output.                                                                        |

| RC2/CCP1          | 17          | 19           | 36          |               | ST                    |                                                                                                                      |

| RC2               |             |              |             | I/O           |                       | Digital I/O.                                                                                                         |

| CCP1              |             |              |             | I/O           |                       | Capture1 input/Compare1 output/PWM1 output                                                                           |

| RC3/SCK/SCL       | 18          | 20           | 37          |               | ST                    | 51.1.110                                                                                                             |

| RC3<br>SCK        |             |              |             | I/O<br>I/O    |                       | Digital I/O                                                                                                          |

| SCL               |             |              |             | 1/0           |                       | Synchronous serial clock input/output for SPI mode. Synchronous serial clock input/output for I <sup>2</sup> C mode. |

| RC4/SDI/SDA       | 23          | 25           | 42          | 1/0           | ST                    | Cyricinolous schal clock inputoutput for 1 o mode.                                                                   |

| RC4               | 23          | 23           | 42          | I/O           | 31                    | Digital I/O.                                                                                                         |

| SDI               |             |              |             | ı, ü          |                       | SPI data in.                                                                                                         |

| SDA               |             |              |             | I/O           |                       | I <sup>2</sup> C data I/O.                                                                                           |

| RC5/SDO           | 24          | 26           | 43          |               | ST                    |                                                                                                                      |

| RC5               |             |              |             | I/O           |                       | Digital I/O.                                                                                                         |

| SDO               |             |              |             | 0             |                       | SPI data out.                                                                                                        |

| RC6/TX/CK         | 25          | 27           | 44          |               | ST                    |                                                                                                                      |

| RC6               |             |              |             | I/O           |                       | Digital I/O.                                                                                                         |

| TX<br>CK          |             |              |             | O<br>I/O      |                       | USART asynchronous transmit.                                                                                         |

|                   | 20          | 20           |             | 1/0           | C.T.                  | USART 1 synchronous clock.                                                                                           |

| RC7/RX/DT<br>RC7  | 26          | 29           | 1           | I/O           | ST                    | Digital I/O.                                                                                                         |

| RX<br>RX          |             |              |             | 1,0           |                       | USART asynchronous receive.                                                                                          |

| DT                |             |              |             | I/O           |                       | USART synchronous data.                                                                                              |

| Legend: L = input |             | 0 - 0        | L           |               | ) – innut/outni       | 1                                                                                                                    |

Legend: I = input O

O = output TTL = TTL input I/O = input/output

P = power

ST = Schmitt Trigger input

Note 1: This buffer is a Schmitt Trigger input when configured as an external interrupt.

<sup>2:</sup> This buffer is a Schmitt Trigger input when used in Serial Programming mode.

<sup>3:</sup> This buffer is a Schmitt Trigger input when configured as general purpose I/O and a TTL input when used in the Parallel Slave Port mode (for interfacing to a microprocessor bus).

<sup>4:</sup> This buffer is a Schmitt Trigger input when configured in RC Oscillator mode and a CMOS input otherwise.

#### 2.2.2 SPECIAL FUNCTION REGISTERS

The Special Function Registers are registers used by the CPU and peripheral modules for controlling the desired operation of the device. These registers are implemented as static RAM. A list of these registers is given in Table 2-1. The Special Function Registers can be classified into two sets: core (CPU) and peripheral. Those registers associated with the core functions are described in detail in this section. Those related to the operation of the peripheral features are described in detail in the peripheral feature section.

TABLE 2-1: SPECIAL FUNCTION REGISTER SUMMARY

| Address              | Name    | Bit 7                | Bit 6                                                                      | Bit 5         | Bit 4          | Bit 3         | Bit 2         | Bit 1         | Bit 0        | Value on:<br>POR,<br>BOR | Details<br>on page |

|----------------------|---------|----------------------|----------------------------------------------------------------------------|---------------|----------------|---------------|---------------|---------------|--------------|--------------------------|--------------------|

| Bank 0               |         |                      |                                                                            |               |                |               |               |               |              |                          |                    |

| 00h <sup>(4)</sup>   | INDF    | Addressin            | g this locatio                                                             | n uses conte  | nts of FSR to  | address data  | a memory (r   | not a physica | al register) | 0000 0000                | 27, 96             |

| 01h                  | TMR0    | Timer0 Mo            | mer0 Module Register                                                       |               |                |               |               |               |              | xxxx xxxx                | 45, 96             |

| 02h <sup>(4)</sup>   | PCL     | Program C            | Counter (PC)                                                               | Least Signif  | icant Byte     |               |               |               |              | 0000 0000                | 26, 96             |

| 03h <sup>(4)</sup>   | STATUS  | IRP                  | RP1                                                                        | RP0           | TO             | PD            | Z             | DC            | С            | 0001 1xxx                | 19, 96             |

| 04h <sup>(4)</sup>   | FSR     | Indirect Da          | ata Memory /                                                               | Address Poir  | nter           | •             |               |               | •            | xxxx xxxx                | 27, 96             |

| 05h                  | PORTA   | _                    | _                                                                          | PORTA Dat     | a Latch when   | written: POF  | RTA pins wh   | en read       |              | 0x 0000                  | 32, 96             |

| 06h                  | PORTB   | PORTB D              | ata Latch wh                                                               | en written: P | ORTB pins w    | hen read      | •             |               |              | xxxx xxxx                | 34, 96             |

| 07h                  | PORTC   | PORTC D              | ata Latch wh                                                               | en written: P | ORTC pins w    | hen read      |               |               |              | xxxx xxxx                | 35, 96             |

| 08h <sup>(5)</sup>   | PORTD   | PORTD D              | ata Latch wh                                                               | en written: P | ORTD pins w    | hen read      |               |               |              | xxxx xxxx                | 36, 96             |

| 09h <sup>(5)</sup>   | PORTE   | _                    | _                                                                          | _             | _              | _             | RE2           | RE1           | RE0          | xxx                      | 39, 96             |

| 0Ah <sup>(1,4)</sup> | PCLATH  | _                    | _                                                                          | _             | Write Buffer   | for the upper | 5 bits of the | Program C     | ounter       | 0 0000                   | 26, 96             |

| 0Bh <sup>(4)</sup>   | INTCON  | GIE                  | PEIE                                                                       | TMR0IE        | INTE           | RBIE          | TMR0IF        | INTF          | RBIF         | 0000 000x                | 21, 96             |

| 0Ch                  | PIR1    | PSPIF <sup>(3)</sup> | ADIF                                                                       | RCIF          | TXIF           | SSPIF         | CCP1IF        | TMR2IF        | TMR1IF       | 0000 0000                | 23, 96             |

| 0Dh                  | PIR2    | _                    | _                                                                          | _             | _              | _             | _             | _             | CCP2IF       | 0                        | 24, 96             |

| 0Eh                  | TMR1L   | Holding Re           | olding Register for the Least Significant Byte of the 16-bit TMR1 Register |               |                |               |               |               |              |                          | 50, 96             |

| 0Fh                  | TMR1H   | Holding Re           | egister for th                                                             | e Most Signi  | ficant Byte of | the 16-bit TM | IR1 Registe   | r             |              | xxxx xxxx                | 50, 96             |

| 10h                  | T1CON   |                      | -                                                                          | T1CKPS1       | T1CKPS0        | T10SCEN       | T1SYNC        | TMR1CS        | TMR10N       | 00 0000                  | 47, 96             |

| 11h                  | TMR2    | Timer2 Mo            | dule Registe                                                               | er            |                |               | •             |               | •            | 0000 0000                | 52, 96             |

| 12h                  | T2CON   | _                    | TOUTPS3                                                                    | TOUTPS2       | TOUTPS         | TOUTPS0       | TMR2ON        | T2CKPS1       | T2CKPS0      | -000 0000                | 52, 96             |

| 13h                  | SSPBUF  | Synchrono            | ous Serial Po                                                              | rt Receive B  | uffer/Transmi  | t Register    |               |               |              | xxxx xxxx                | 64, 68, 96         |

| 14h                  | SSPCON  | WCOL                 | SSPOV                                                                      | SSPEN         | CKP            | SSPM3         | SSPM2         | SSPM1         | SSPM0        | 0000 0000                | 61, 96             |

| 15h                  | CCPR1L  | Capture/C            | ompare/PWI                                                                 | M Register1   | (LSB)          |               |               |               |              | xxxx xxxx                | 56, 96             |

| 16h                  | CCPR1H  | Capture/C            | ompare/PWI                                                                 | M Register1   | (MSB)          |               |               |               |              | xxxx xxxx                | 56, 96             |

| 17h                  | CCP1CON | _                    | _                                                                          | CCP1X         | CCP1Y          | CCP1M3        | CCP1M2        | CCP1M1        | CCP1M0       | 00 0000                  | 54, 96             |

| 18h                  | RCSTA   | SPEN                 | RX9                                                                        | SREN          | CREN           | _             | FERR          | OERR          | RX9D         | 0000 -00x                | 70, 96             |

| 19h                  | TXREG   | USART Tr             | ansmit Data                                                                | Register      |                |               |               |               |              | 0000 0000                | 74, 96             |

| 1Ah                  | RCREG   | USART R              | eceive Data                                                                | Register      |                |               |               |               |              | 0000 0000                | 76, 96             |

| 1Bh                  | CCPR2L  | Capture/C            | ompare/PWI                                                                 | M Register2   | (LSB)          |               |               |               |              | xxxx xxxx                | 58, 96             |

| 1Ch                  | CCPR2H  | Capture/C            | ompare/PWI                                                                 | M Register2   | (MSB)          | <b>.</b>      |               |               | <u> </u>     | xxxx xxxx                | 58, 96             |

| 1Dh                  | CCP2CON | _                    | _                                                                          | CCP2X         | CCP2Y          | CCP2M3        | CCP2M2        | CCP2M1        | CCP2M0       | 00 0000                  | 54, 96             |

| 1Eh                  | ADRES   | A/D Resul            | t Register By                                                              | rte           | T              | T             | ı             | 1             | 1            | xxxx xxxx                | 88, 96             |

| 1Fh                  | ADCON0  | ADCS1                | ADCS0                                                                      | CHS2          | CHS1           | CHS0          | GO/<br>DONE   | _             | ADON         | 0000 00-0                | 83, 96             |

Legend: x = unknown, u = unchanged, q = value depends on condition, -= unimplemented, read as '0', r = reserved. Shaded locations are unimplemented, read as '0'.

Note 1: The upper byte of the program counter is not directly accessible. PCLATH is a holding register for the PC<12:8>, whose contents are transferred to the upper byte of the program counter during branches (CALL or GOTO).

- 2: Other (non power-up) RESETS include external RESET through MCLR and Watchdog Timer Reset.

- 3: Bits PSPIE and PSPIF are reserved on the 28-pin devices; always maintain these bits clear.

- 4: These registers can be addressed from any bank.

- 5: PORTD, PORTE, TRISD, and TRISE are not physically implemented on the 28-pin devices, read as '0'.

- 6: This bit always reads as a '1'.

#### 2.2.2.2 OPTION\_REG Register

The OPTION\_REG register is a readable and writable register, which contains various control bits to configure the TMR0 prescaler/WDT postscaler (single assignable register known also as the prescaler), the External INT Interrupt, TMR0 and the weak pull-ups on PORTB.

Note: To achieve a 1:1 prescaler assignment for the TMR0 register, assign the prescaler to the Watchdog Timer.

#### REGISTER 2-2: OPTION\_REG REGISTER (ADDRESS 81h, 181h)

| R/W-1 | R/W-1  | R/W-1 | R/W-1 | R/W-1 | R/W-1 | R/W-1 | R/W-1 |

|-------|--------|-------|-------|-------|-------|-------|-------|

| RBPU  | INTEDG | T0CS  | T0SE  | PSA   | PS2   | PS1   | PS0   |

| bit 7 |        |       |       |       |       |       | hit 0 |

bit 7 RBPU: PORTB Pull-up Enable bit

1 = PORTB pull-ups are disabled

0 = PORTB pull-ups are enabled by individual port latch values

bit 6 INTEDG: Interrupt Edge Select bit

1 = Interrupt on rising edge of RB0/INT pin0 = Interrupt on falling edge of RB0/INT pin

bit 5 TOCS: TMR0 Clock Source Select bit

1 = Transition on RA4/T0CKI pin

0 = Internal instruction cycle clock (CLKOUT)

bit 4 T0SE: TMR0 Source Edge Select bit

1 = Increment on high-to-low transition on RA4/T0CKI pin

0 = Increment on low-to-high transition on RA4/T0CKI pin

bit 3 **PSA**: Prescaler Assignment bit

1 = Prescaler is assigned to the WDT

0 = Prescaler is assigned to the Timer0 module

bit 2-0 **PS2:PS0**: Prescaler Rate Select bits

| Bit Value | TMR0 Rate | WDT Rate |

|-----------|-----------|----------|

| 000       | 1:2       | 1:1      |

| 001       | 1:4       | 1:2      |

| 010       | 1:8       | 1:4      |

| 011       | 1:16      | 1:8      |

| 100       | 1:32      | 1:16     |

| 101       | 1:64      | 1:32     |

| 110       | 1:128     | 1:64     |

| 111       | 1:256     | 1 : 128  |

| egend: |  |

|--------|--|

|--------|--|

$R = Readable \ bit \qquad \qquad W = Writable \ bit \qquad \qquad U = Unimplemented \ bit, read \ as '0'$

- n = Value at POR reset '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

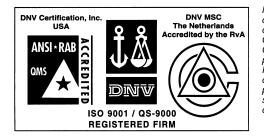

#### 4.6 Parallel Slave Port

The Parallel Slave Port (PSP) is not implemented on the PIC16F73 or PIC16F76.

PORTD operates as an 8-bit wide Parallel Slave Port, or Microprocessor Port, when control bit PSPMODE (TRISE<4>) is set. In Slave mode, it is asynchronously readable and writable by an external system using the read control input pin RE0/RD, the write control input pin RE1/WR, and the chip select control input pin RE2/CS.

The PSP can directly interface to an 8-bit microprocessor data bus. The external microprocessor can read or write the PORTD latch as an 8-bit latch. Setting bit PSPMODE enables port pin RE0/RD to be the  $\overline{RD}$  input, RE1/WR to be the  $\overline{WR}$  input and RE2/ $\overline{CS}$  to be the  $\overline{CS}$  (chip select) input. For this functionality, the corresponding data direction bits of the TRISE register (TRISE<2:0>) must be configured as inputs (i.e., set). The A/D port configuration bits PCFG3:PCFG0 (ADCON1<3:0>) must be set to configure pins RE2:RE0 as digital I/O.

There are actually two 8-bit latches, one for data output (external reads) and one for data input (external writes). The firmware writes 8-bit data to the PORTD output data latch and reads data from the PORTD input data latch (note that they have the same address). In this mode, the TRISD register is ignored, since the external device is controlling the direction of data flow.

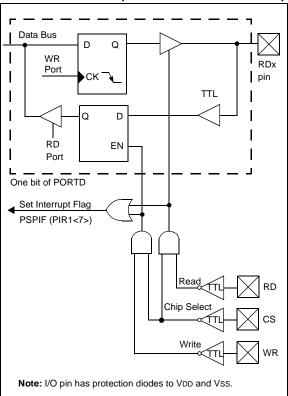

An external write to the PSP occurs when the  $\overline{\text{CS}}$  and  $\overline{\text{WR}}$  lines are both detected low. Firmware can read the actual data on the PORTD pins during this time. When either the CS or WR lines become high (level triggered), the data on the PORTD pins is latched, and the Input Buffer Full (IBF) status flag bit (TRISE<7>) and interrupt flag bit PSPIF (PIR1<7>) are set on the Q4 clock cycle, following the next Q2 cycle to signal the write is complete (Figure 4-9). Firmware clears the IBF flag by reading the latched PORTD data, and clears the PSPIF bit.

The Input Buffer Overflow (IBOV) status flag bit (TRISE<5>) is set if an external write to the PSP occurs while the IBF flag is set from a previous external write. The previous PORTD data is overwritten with the new data. IBOV is cleared by reading PORTD and clearing IBOV.

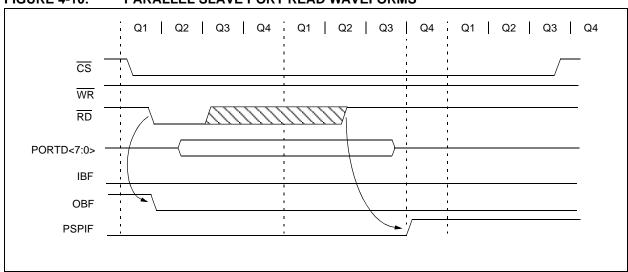

A read from the PSP occurs when both the  $\overline{CS}$  and  $\overline{RD}$  lines are detected low. The data in the PORTD output latch is output to the PORTD pins. The Output Buffer Full (OBF) status flag bit (TRISE<6>) is cleared immediately (Figure 4-10), indicating that the PORTD latch is being read, or has been read by the external bus. If firmware writes new data to the output latch during this time, it is immediately output to the PORTD pins, but OBF will remain cleared.

When either the  $\overline{\text{CS}}$  or  $\overline{\text{RD}}$  pins are detected high, the PORTD outputs are disabled, and the interrupt flag bit PSPIF is set on the Q4 clock cycle following the next Q2 cycle, indicating that the read is complete. OBF remains low until firmware writes new data to PORTD.

When not in PSP mode, the IBF and OBF bits are held clear. Flag bit IBOV remains unchanged. The PSPIF bit must be cleared by the user in firmware; the interrupt can be disabled by clearing the interrupt enable bit PSPIE (PIE1<7>).

FIGURE 4-8: PORTD AND PORTE

BLOCK DIAGRAM

(PARALLEL SLAVE PORT)

FIGURE 4-10: PARALLEL SLAVE PORT READ WAVEFORMS

TABLE 4-11: REGISTERS ASSOCIATED WITH PARALLEL SLAVE PORT

| Address | Name   | Bit 7                | Bit 6   | Bit 5      | Bit 4         | Bit 3    | Bit 2   | Bit 1       | Bit 0    | Value on:<br>POR,<br>BOR | Value on<br>all other<br>RESETS |

|---------|--------|----------------------|---------|------------|---------------|----------|---------|-------------|----------|--------------------------|---------------------------------|

| 08h     | PORTD  | Port data I          | atch wh | nen writte | en: Port pins | when rea | d       |             |          | xxxx xxxx                | uuuu uuuu                       |

| 09h     | PORTE  | _                    | _       | _          | _             | _        | RE2     | RE1         | RE0      | xxx                      | uuu                             |

| 89h     | TRISE  | IBF                  | OBF     | IBOV       | PSPMODE       | _        | PORTE D | Data Direct | ion Bits | 0000 -111                | 0000 -111                       |

| 0Ch     | PIR1   | PSPIF <sup>(1)</sup> | ADIF    | RCIF       | TXIF          | SSPIF    | CCP1IF  | TMR2IF      | TMR1IF   | 0000 0000                | 0000 0000                       |

| 8Ch     | PIE1   | PSPIE <sup>(1)</sup> | ADIE    | RCIE       | TXIE          | SSPIE    | CCP1IE  | TMR2IE      | TMR1IE   | 0000 0000                | 0000 0000                       |

| 9Fh     | ADCON1 | _                    | _       | _          | _             | _        | PCFG2   | PCFG1       | PCFG0    | 000                      | 000                             |

$\label{eq:local_equation} \textbf{Legend:} \quad \textbf{x} = \textbf{unknown}, \ \textbf{u} = \textbf{unchanged}, \ \textbf{-} = \textbf{unimplemented}, \ \textbf{read as '0'}. \ \textbf{Shaded cells are not used by the Parallel Slave Port.}$

Note 1: Bits PSPIE and PSPIF are reserved on the PIC16F73/76; always maintain these bits clear.

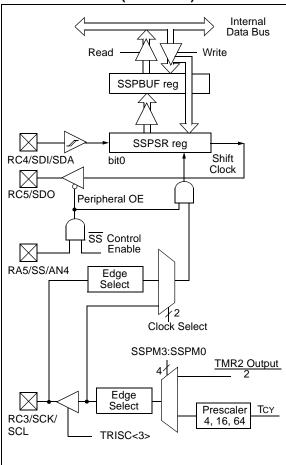

FIGURE 9-1: SSP BLOCK DIAGRAM (SPI MODE)

To enable the serial port, SSP enable bit, SSPEN (SSPCON<5>) must be set. To reset or reconfigure SPI mode, clear bit SSPEN, re-initialize the SSPCON register, and then set bit SSPEN. This configures the SDI, SDO, SCK, and SS pins as serial port pins. For the pins to behave as the serial port function, they must have their data direction bits (in the TRISC register) appropriately programmed. That is:

- SDI must have TRISC<4> set

- SDO must have TRISC<5> cleared

- SCK (Master mode) must have TRISC<3> cleared

- SCK (Slave mode) must have TRISC<3> set

- SS must have TRISA<5> set and ADCON must be configured such that RA5 is a digital I/O

Note 1: When the SPI is in Slave mode with SS pin control enabled (SSPCON<3:0> = 0100), the SPI module will reset if the SS pin is set to VDD.

- 2: If the SPI is used in Slave mode with CKE = '1', then the SS pin control must be enabled.

- 3: When the SPI is in Slave mode with \$\overline{SS}\$ pin control enabled (\$\subsetext{SSPCON} < 3:0 > = '0100'\$), the state of the \$\overline{SS}\$ pin can affect the state read back from the TRISC < 5 > bit. The Peripheral OE signal from the SSP module into PORTC controls the state that is read back from the TRISC < 5 > bit (see Section 4.3 for information on PORTC). If Read-Modify-Write instructions, such as \$\overline{SSF}\$ are performed on the TRISC register while the \$\overline{SS}\$ pin is high, this will cause the TRISC < 5 > bit to be set, thus disabling the SDO output.

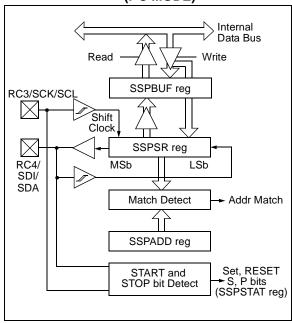

### 9.3 SSP I<sup>2</sup>C Operation

The SSP module in I<sup>2</sup>C mode, fully implements all slave functions, except general call support, and provides interrupts on START and STOP bits in hardware to facilitate firmware implementations of the master functions. The SSP module implements the standard mode specifications as well as 7-bit and 10-bit addressing.

Two pins are used for data transfer. These are the RC3/SCK/SCL pin, which is the clock (SCL), and the RC4/SDI/SDA pin, which is the data (SDA). The user must configure these pins as inputs or outputs through the TRISC<4:3> bits.

The SSP module functions are enabled by setting SSP enable bit SSPEN (SSPCON<5>).

FIGURE 9-5: SSP BLOCK DIAGRAM (1<sup>2</sup>C MODE)

The SSP module has five registers for I<sup>2</sup>C operation. These are the:

- SSP Control Register (SSPCON)

- SSP Status Register (SSPSTAT)

- Serial Receive/Transmit Buffer (SSPBUF)

- · SSP Shift Register (SSPSR) Not directly accessible

- SSP Address Register (SSPADD)

The SSPCON register allows control of the I<sup>2</sup>C operation. Four mode selection bits (SSPCON<3:0>) allow one of the following I<sup>2</sup>C modes to be selected:

- I<sup>2</sup>C Slave mode (7-bit address)

- I<sup>2</sup>C Slave mode (10-bit address)

- I<sup>2</sup>C Slave mode (7-bit address), with START and STOP bit interrupts enabled to support Firmware Master mode

- I<sup>2</sup>C Slave mode (10-bit address), with START and STOP bit interrupts enabled to support Firmware Master mode

- I<sup>2</sup>C START and STOP bit interrupts enabled to support Firmware Master mode, Slave is IDLE

Selection of any I<sup>2</sup>C mode with the SSPEN bit set, forces the SCL and SDA pins to be open drain, provided these pins are programmed to inputs by setting the appropriate TRISC bits. Pull-up resistors must be provided externally to the SCL and SDA pins for proper operation of the I<sup>2</sup>C module.

Additional information on SSP I<sup>2</sup>C operation can be found in the PICmicro™ Mid-Range MCU Family Reference Manual (DS33023A).

#### 9.3.1 SLAVE MODE

In Slave mode, the SCL and SDA pins must be configured as inputs (TRISC<4:3> set). The SSP module will override the input state with the output data when required (slave-transmitter).

When an address is matched, or the data transfer after an address match is received, the hardware automatically will generate the Acknowledge (ACK) pulse, and then load the SSPBUF register with the received value currently in the SSPSR register.

There are certain conditions that will cause the SSP module not to give this  $\overline{ACK}$  pulse. They include (either or both):

- The buffer full bit BF (SSPSTAT<0>) was set before the transfer was received.

- b) The overflow bit SSPOV (SSPCON<6>) was set before the transfer was received.

In this case, the SSPSR register value is not loaded into the SSPBUF, but bit SSPIF (PIR1<3>) is set. Table 9-2 shows what happens when a data transfer byte is received, given the status of bits BF and SSPOV. The shaded cells show the condition where user software did not properly clear the overflow condition. Flag bit BF is cleared by reading the SSPBUF register, while bit SSPOV is cleared through software.

The SCL clock input must have a minimum high and low for proper operation. The high and low times of the  $I^2C$  specification, as well as the requirements of the SSP module, are shown in timing parameter #100 and parameter #101.

#### REGISTER 11-2: ADCON1 REGISTER (ADDRESS 9Fh)

| U-0   | U-0 | U-0 | U-0 | U-0 | R/W-0 | R/W-0 | R/W-0 |

|-------|-----|-----|-----|-----|-------|-------|-------|

| _     | _   | _   | _   | _   | PCFG2 | PCFG1 | PCFG0 |

| bit 7 |     |     |     |     |       |       | bit 0 |

bit 7-3 Unimplemented: Read as '0'

bit 2-0 PCFG2:PCFG0: A/D Port Configuration Control bits

| PCFG2:PCFG0 | RA0 | RA1 | RA2 | RA5 | RA3  | RE0 <sup>(1)</sup> | RE1 <sup>(1)</sup> | RE2 <sup>(1)</sup> | VREF |

|-------------|-----|-----|-----|-----|------|--------------------|--------------------|--------------------|------|

| 000         | Α   | Α   | Α   | Α   | Α    | Α                  | Α                  | Α                  | VDD  |

| 001         | Α   | Α   | Α   | Α   | VREF | Α                  | Α                  | Α                  | RA3  |

| 010         | Α   | Α   | Α   | Α   | Α    | D                  | D                  | D                  | Vdd  |

| 011         | Α   | Α   | Α   | Α   | VREF | D                  | D                  | D                  | RA3  |

| 100         | Α   | Α   | D   | D   | Α    | D                  | D                  | D                  | Vdd  |

| 101         | Α   | Α   | D   | D   | VREF | D                  | D                  | D                  | RA3  |

| 11x         | D   | D   | D   | D   | D    | D                  | D                  | D                  | Vdd  |

A = Analog input D = Digital I/O

Note 1: RE0, RE1 and RE2 are implemented on the PIC16F74/77 only.

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

- n = Value at POR reset '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

### 12.10 Power Control/Status Register (PCON)

The Power Control/Status Register, PCON, has two bits to indicate the type of RESET that last occurred.

Bit0 is Brown-out Reset Status bit,  $\overline{\text{BOR}}$ . Bit  $\overline{\text{BOR}}$  is unknown on a Power-on Reset. It must then be set by the user and checked on subsequent RESETS to see

if bit  $\overline{\mathsf{BOR}}$  cleared, indicating a Brown-out Reset occurred. When the Brown-out Reset is disabled, the state of the  $\overline{\mathsf{BOR}}$  bit is unpredictable.

Bit1 is  $\overline{POR}$  (Power-on Reset Status bit). It is cleared on a Power-on Reset and unaffected otherwise. The user must set this bit following a Power-on Reset.

TABLE 12-3: TIME-OUT IN VARIOUS SITUATIONS

| Occillator Configuration | Power-            | -up       | Drawn aut         | Wake-up from |

|--------------------------|-------------------|-----------|-------------------|--------------|

| Oscillator Configuration | PWRTE = 0         | PWRTE = 1 | Brown-out         | SLEEP        |

| XT, HS, LP               | 72 ms + 1024 Tosc | 1024 Tosc | 72 ms + 1024 Tosc | 1024 Tosc    |

| RC                       | 72 ms             | _         | 72 ms             | _            |

TABLE 12-4: STATUS BITS AND THEIR SIGNIFICANCE

| POR<br>(PCON<1>) | BOR<br>(PCON<0>) | TO<br>(STATUS<4>) | PD<br>(STATUS<3>) | Significance                                            |  |  |

|------------------|------------------|-------------------|-------------------|---------------------------------------------------------|--|--|

| 0                | х                | 1                 | 1                 | Power-on Reset                                          |  |  |

| 0                | х                | 0                 | х                 | Illegal, TO is set on POR                               |  |  |

| 0                | х                | х                 | 0                 | Illegal, PD is set on POR                               |  |  |

| 1                | 0                | 1                 | 1                 | Brown-out Reset                                         |  |  |

| 1                | 1                | 0                 | 1                 | WDT Reset                                               |  |  |

| 1                | 1                | 0                 | 0                 | WDT Wake-up                                             |  |  |

| 1                | 1                | u                 | u                 | MCLR Reset during normal operation                      |  |  |

| 1                | 1                | 1                 | 0                 | MCLR Reset during SLEEP or interrupt wake-up from SLEEP |  |  |

TABLE 12-5: RESET CONDITION FOR SPECIAL REGISTERS

| Condition                          | Program<br>Counter    | STATUS<br>Register | PCON<br>Register |

|------------------------------------|-----------------------|--------------------|------------------|

| Power-on Reset                     | 000h                  | 0001 1xxx          | 0x               |

| MCLR Reset during normal operation | 000h                  | 000u uuuu          | uu               |

| MCLR Reset during SLEEP            | 000h                  | 0001 0uuu          | uu               |

| WDT Reset                          | 000h                  | 0000 1uuu          | uu               |

| WDT Wake-up                        | PC + 1                | uuu0 0uuu          | uu               |

| Brown-out Reset                    | 000h                  | 0001 1uuu          | u0               |

| Interrupt wake-up from SLEEP       | PC + 1 <sup>(1)</sup> | uuu1 0uuu          | uu               |

Legend: u = unchanged, x = unknown, - = unimplemented bit, read as '0'

**Note 1:** When the wake-up is due to an interrupt and the GIE bit is set, the PC is loaded with the interrupt vector (0004h).

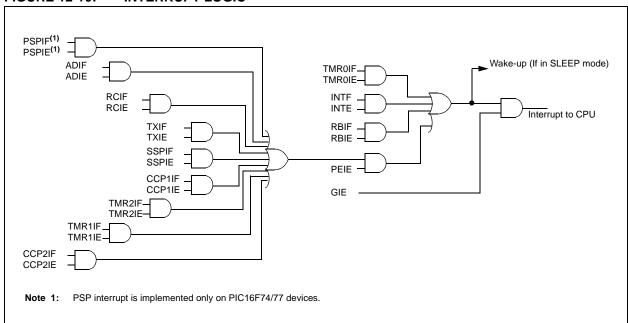

#### 12.11 Interrupts

The PIC16F7X family has up to 12 sources of interrupt. The interrupt control register (INTCON) records individual interrupt requests in flag bits. It also has individual and global interrupt enable bits.

Note: Individual interrupt flag bits are set, regardless of the status of their corresponding mask bit or the GIE bit.

A global interrupt enable bit, GIE (INTCON<7>) enables (if set) all unmasked interrupts, or disables (if cleared) all interrupts. When bit GIE is enabled and an interrupt's flag bit and mask bit are set, the interrupt will vector immediately. Individual interrupts can be disabled through their corresponding enable bits in various registers. Individual interrupt bits are set, regardless of the status of the GIE bit. The GIE bit is cleared on RESET.

The "return from interrupt" instruction, RETFIE, exits the interrupt routine, as well as sets the GIE bit, which re-enables interrupts.

The RB0/INT pin interrupt, the RB port change interrupt and the TMR0 overflow interrupt flags are contained in the INTCON register.

The peripheral interrupt flags are contained in the Special Function Registers, PIR1 and PIR2. The corresponding interrupt enable bits are contained in Special Function Registers, PIE1 and PIE2, and the peripheral interrupt enable bit is contained in Special Function Register, INTCON.

When an interrupt is responded to, the GIE bit is cleared to disable any further interrupt, the return address is pushed onto the stack and the PC is loaded with 0004h. Once in the Interrupt Service Routine, the source(s) of the interrupt can be determined by polling the interrupt flag bits. The interrupt flag bit(s) must be cleared in software before re-enabling interrupts to avoid recursive interrupts.

For external interrupt events, such as the INT pin or PORTB change interrupt, the interrupt latency will be three or four instruction cycles. The exact latency depends when the interrupt event occurs, relative to the current Q cycle. The latency is the same for one or two-cycle instructions. Individual interrupt flag bits are set, regardless of the status of their corresponding mask bit, PEIE bit, or the GIE bit.

FIGURE 12-10: INTERRUPT LOGIC

| SWAPF            | Swap Nibbles in f                                                                                                                                                  |

|------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [ label ] SWAPF f,d                                                                                                                                                |

| Operands:        | $0 \le f \le 127$<br>$d \in [0,1]$                                                                                                                                 |

| Operation:       | $(f<3:0>) \rightarrow (destination<7:4>),$<br>$(f<7:4>) \rightarrow (destination<3:0>)$                                                                            |

| Status Affected: | None                                                                                                                                                               |

| Description:     | The upper and lower nibbles of register 'f' are exchanged. If 'd' is 0, the result is placed in the W register. If 'd' is 1, the result is placed in register 'f'. |

| XORWF            | Exclusive OR W with f                                                                                                                                                       |

|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [ label ] XORWF f,d                                                                                                                                                         |

| Operands:        | $0 \le f \le 127$<br>$d \in [0,1]$                                                                                                                                          |

| Operation:       | (W) .XOR. (f) $\rightarrow$ (destination)                                                                                                                                   |

| Status Affected: | Z                                                                                                                                                                           |

| Description:     | Exclusive OR the contents of the W register with register 'f'. If 'd' is 0, the result is stored in the W register. If 'd' is 1, the result is stored back in register 'f'. |

| XORLW            | Exclusive OR Literal with W                                                                                       |

|------------------|-------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [ label ] XORLW k                                                                                                 |

| Operands:        | $0 \le k \le 255$                                                                                                 |

| Operation:       | (W) .XOR. $k \rightarrow (W)$                                                                                     |

| Status Affected: | Z                                                                                                                 |

| Description:     | The contents of the W register are XOR'ed with the eight-bit literal 'k'. The result is placed in the W register. |

#### 14.13 PICDEM 3 Low Cost PIC16CXXX Demonstration Board

The PICDEM 3 demonstration board is a simple demonstration board that supports the PIC16C923 and PIC16C924 in the PLCC package. It will also support future 44-pin PLCC microcontrollers with an LCD Module. All the necessary hardware and software is included to run the basic demonstration programs. The user can program the sample microcontrollers provided with the PICDEM 3 demonstration board on a PRO MATE II device programmer, or a PICSTART Plus development programmer with an adapter socket, and easily test firmware. The MPLAB ICE in-circuit emulator may also be used with the PICDEM 3 demonstration board to test firmware. A prototype area has been provided to the user for adding hardware and connecting it to the microcontroller socket(s). Some of the features include a RS-232 interface, push button switches, a potentiometer for simulated analog input, a thermistor and separate headers for connection to an external LCD module and a keypad. Also provided on the PICDEM 3 demonstration board is a LCD panel, with 4 commons and 12 segments, that is capable of displaying time, temperature and day of the week. The PICDEM 3 demonstration board provides an additional RS-232 interface and Windows software for showing the demultiplexed LCD signals on a PC. A simple serial interface allows the user to construct a hardware demultiplexer for the LCD signals.

#### 14.14 PICDEM 17 Demonstration Board

The PICDEM 17 demonstration board is an evaluation board that demonstrates the capabilities of several Microchip microcontrollers, including PIC17C752, PIC17C756A, PIC17C762 and PIC17C766. All necessary hardware is included to run basic demo programs, which are supplied on a 3.5-inch disk. A programmed sample is included and the user may erase it and program it with the other sample programs using the PRO MATE II device programmer, or the PICSTART Plus development programmer, and easily debug and test the sample code. In addition, the PICDEM 17 demonstration board supports downloading of programs to and executing out of external FLASH memory on board. The PICDEM 17 demonstration board is also usable with the MPLAB ICE in-circuit emulator, or the PICMASTER emulator and all of the sample programs can be run and modified using either emulator. Additionally, a generous prototype area is available for user hardware.

# 14.15 KEELOQ Evaluation and Programming Tools

KEELOQ evaluation and programming tools support Microchip's HCS Secure Data Products. The HCS evaluation kit includes a LCD display to show changing codes, a decoder to decode transmissions and a programming interface to program test transmitters.

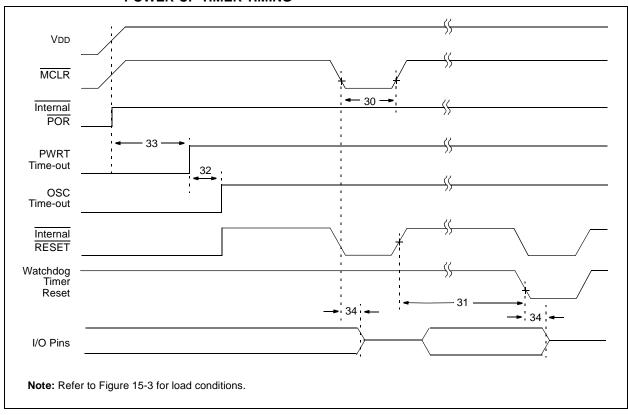

FIGURE 15-6: RESET, WATCHDOG TIMER, OSCILLATOR START-UP TIMER AND POWER-UP TIMER TIMING

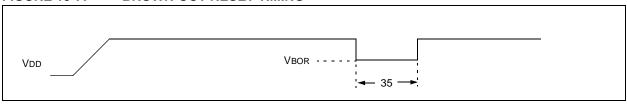

FIGURE 15-7: BROWN-OUT RESET TIMING

TABLE 15-3: RESET, WATCHDOG TIMER, OSCILLATOR START-UP TIMER, POWER-UP TIMER, AND BROWN-OUT RESET REQUIREMENTS

| Parameter<br>No. | Sym   | Characteristic                                         | Min | Typ†      | Max | Units | Conditions                                        |

|------------------|-------|--------------------------------------------------------|-----|-----------|-----|-------|---------------------------------------------------|

| 30               | TmcL  | MCLR Pulse Width (low)                                 | 2   | _         | _   | μs    | VDD = 5V, -40°C to +85°C                          |

| 31*              | TWDT  | Watchdog Timer Time-out Period (No Prescaler)          | 7   | 18        | 33  | ms    | VDD = 5V, -40°C to +85°C                          |

| 32               | Tost  | Oscillation Start-up Timer Period                      | _   | 1024 Tosc | _   | _     | Tosc = OSC1 period                                |

| 33*              | TPWRT | Power-up Timer Period                                  | 28  | 72        | 132 | ms    | $VDD = 5V, -40^{\circ}C \text{ to } +85^{\circ}C$ |

| 34               | Tıoz  | I/O Hi-Impedance from MCLR Low or Watchdog Timer Reset | _   | _         | 2.1 | μs    |                                                   |

| 35               | TBOR  | Brown-out Reset Pulse Width                            | 100 | _         | _   | μs    | VDD ≤ VBOR (D005)                                 |

<sup>\*</sup> These parameters are characterized but not tested.

<sup>†</sup> Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

TABLE 15-12: A/D CONVERTER CHARACTERISTICS: PIC16F7X (INDUSTRIAL, EXTENDED)

PIC16LF7X (INDUSTRIAL)

| Param<br>No. | Sym  | Characteristic                                 |           | Min        | Тур†       | Max        | Units | Conditions                                     |

|--------------|------|------------------------------------------------|-----------|------------|------------|------------|-------|------------------------------------------------|

| A01          | NR   | Resolution                                     | PIC16F7X  | _          | _          | 8 bits     | bit   | VREF = VDD = 5.12V,<br>VSS ≤ VAIN ≤ VREF       |

|              |      |                                                | PIC16LF7X | _          | _          | 8 bits     | bit   | VREF = VDD = 2.2V                              |

| A02          | EABS | Total absolute er                              | ror       | _          | _          | < ±1       | LSb   | $VREF = VDD = 5.12V$ , $VSS \le VAIN \le VREF$ |

| A03          | EIL  | Integral linearity                             | error     | _          | _          | < ±1       | LSb   | $VREF = VDD = 5.12V$ , $VSS \le VAIN \le VREF$ |

| A04          | EDL  | Differential linearity error                   |           | _          | _          | < ±1       | LSb   | $VREF = VDD = 5.12V$ , $VSS \le VAIN \le VREF$ |

| A05          | EFS  | Full scale error                               |           | _          | _          | < ±1       | LSb   | VREF = VDD = 5.12V,<br>VSS ≤ VAIN ≤ VREF       |

| A06          | EOFF | Offset error                                   |           | _          | _          | < ±1       | LSb   | VREF = VDD = 5.12V,<br>VSS ≤ VAIN ≤ VREF       |

| A10          | _    | Monotonicity (Note 3)                          |           | _          | guaranteed | _          | _     | VSS ≤ VAIN ≤ VREF                              |

| A20          | VREF | Reference voltage                              |           | 2.5<br>2.2 | _          | 5.5<br>5.5 | V     | -40°C to +125°C<br>0°C to +125°C               |

| A25          | Vain | Analog input vol                               | tage      | Vss - 0.3  | _          | VREF + 0.3 | V     |                                                |

| A30          | ZAIN | Recommended impedance of analog voltage source |           | _          | _          | 10.0       | kΩ    |                                                |

| A40          | IAD  | A/D conversion                                 | PIC16F7X  | _          | 180        | _          | μΑ    | Average current                                |

|              |      | current (VDD)                                  | PIC16LF7X | _          | 90         | _          | μА    | consumption when A/D is on <b>(Note 1)</b> .   |

| A50          | IREF | VREF input current (Note 2)                    |           | N/A        | _          | ±5         | μΑ    | During VAIN acquisition.                       |

|              |      |                                                |           | _          |            | 500        | μΑ    | During A/D Conversion cycle.                   |

<sup>\*</sup> These parameters are characterized but not tested.

**Note 1:** When A/D is off, it will not consume any current other than minor leakage current. The power-down current spec includes any such leakage from the A/D module.

- 2: VREF current is from the RA3 pin or the VDD pin, whichever is selected as a reference input.

- 3: The A/D conversion result never decreases with an increase in the input voltage and has no missing codes.

<sup>†</sup> Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

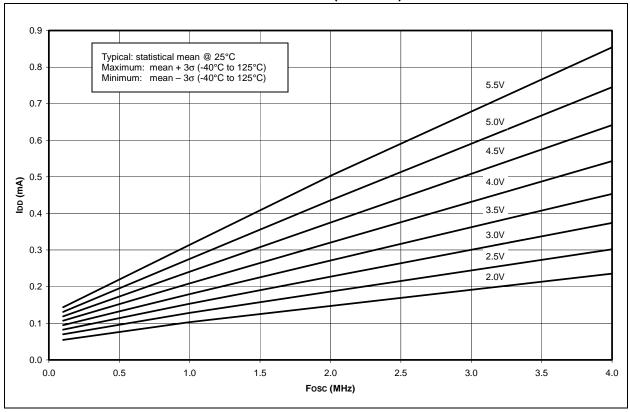

FIGURE 16-3: TYPICAL IDD vs. FOSC OVER VDD (XT MODE)

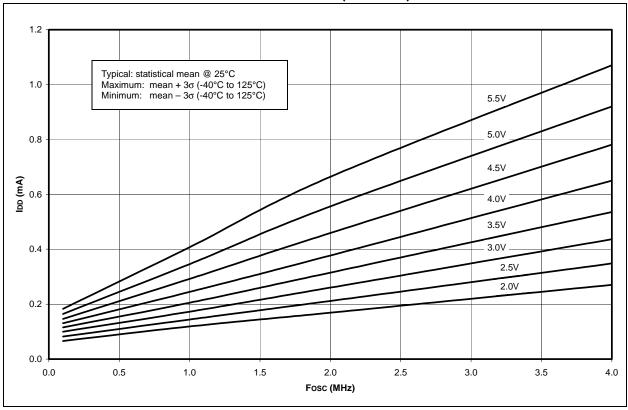

FIGURE 16-4: MAXIMUM IDD vs. Fosc OVER VDD (XT MODE)

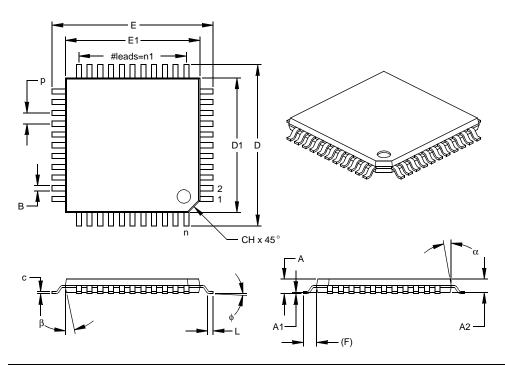

### 44-Lead Plastic Thin Quad Flatpack (PT) 10x10x1 mm Body, 1.0/0.10 mm Lead Form (TQFP)

|                          | Units  | INCHES |      | MILLIMETERS* |       | *     |       |

|--------------------------|--------|--------|------|--------------|-------|-------|-------|

| Dimension                | Limits | MIN    | MOM  | MAX          | MIN   | NOM   | MAX   |

| Number of Pins           | n      |        | 44   |              |       | 44    |       |

| Pitch                    | р      |        | .031 |              |       | 0.80  |       |

| Pins per Side            | n1     |        | 11   |              |       | 11    |       |

| Overall Height           | Α      | .039   | .043 | .047         | 1.00  | 1.10  | 1.20  |

| Molded Package Thickness | A2     | .037   | .039 | .041         | 0.95  | 1.00  | 1.05  |

| Standoff §               | A1     | .002   | .004 | .006         | 0.05  | 0.10  | 0.15  |

| Foot Length              | Г      | .018   | .024 | .030         | 0.45  | 0.60  | 0.75  |

| Footprint (Reference)    | (F)    |        | .039 |              | 1.00  |       |       |

| Foot Angle               | ф      | 0      | 3.5  | 7            | 0     | 3.5   | 7     |

| Overall Width            | Е      | .463   | .472 | .482         | 11.75 | 12.00 | 12.25 |

| Overall Length           | D      | .463   | .472 | .482         | 11.75 | 12.00 | 12.25 |

| Molded Package Width     | E1     | .390   | .394 | .398         | 9.90  | 10.00 | 10.10 |

| Molded Package Length    | D1     | .390   | .394 | .398         | 9.90  | 10.00 | 10.10 |

| Lead Thickness           | С      | .004   | .006 | .008         | 0.09  | 0.15  | 0.20  |

| Lead Width               | В      | .012   | .015 | .017         | 0.30  | 0.38  | 0.44  |

| Pin 1 Corner Chamfer     | CH     | .025   | .035 | .045         | 0.64  | 0.89  | 1.14  |

| Mold Draft Angle Top     | α      | 5      | 10   | 15           | 5     | 10    | 15    |

| Mold Draft Angle Bottom  | β      | 5      | 10   | 15           | 5     | 10    | 15    |

<sup>\*</sup> Controlling Parameter § Significant Characteristic

Dimensions D1 and E1 do not include mold flash or protrusions. Mold flash or protrusions shall not exceed

.010" (0.254mm) per side.

JEDEC Equivalent: MS-026

Drawing No. C04-076

| PORTE Register                          | 37            | RCSTA Register                                 |       |

|-----------------------------------------|---------------|------------------------------------------------|-------|

| Postscaler, WDT                         |               | CREN bit                                       | 70    |

| Assignment (PSA bit)                    | 20            | OERR bit                                       | 70    |

| Rate Select (PS2:PS0 bits)              | 20            | SPEN bit                                       | 69    |

| Power-down Mode. See SLEEP              |               | SREN bit                                       | 70    |

| Power-on Reset (POR)89                  | , 93, 95, 96  | RD0/PSP0 Pin                                   | 12    |

| Oscillator Start-up Timer (OST)         | 89, 94        | RD1/PSP1 Pin                                   | 12    |

| POR Status (POR bit)                    | 25            | RD2/PSP2 Pin                                   | 12    |

| Power Control (PCON) Register           |               | RD3/PSP3 Pin                                   | 12    |

| Power-down (PD bit)                     |               | RD4/PSP4 Pin                                   | 12    |

| Power-up Timer (PWRT)                   |               | RD5/PSP5 Pin                                   | 12    |

| Time-out (TO bit)                       |               | RD6/PSP6 Pin                                   | 12    |

| PR2 Register                            |               | RD7/PSP7 Pin                                   | 12    |

| Prescaler, Timer0                       |               | RE0/RD/AN5 Pin                                 | 12    |

| Assignment (PSA bit)                    | 20            | RE1/WR/AN6 Pin                                 |       |

| Rate Select (PS2:PS0 bits)              |               | RE2/CS/AN7 Pin                                 |       |

| PRO MATE II Universal Device Programmer |               | Read-Modify-Write Operations                   |       |

| Program Counter                         |               | Receive Overflow Indicator bit (SSPOV)         |       |

| RESET Conditions                        | 95            | Register File                                  |       |

| Program Memory                          |               | Registers                                      |       |

| Associated Registers                    |               | ADCON0 (A/D Control 0)                         | 83    |

| Interrupt Vector                        |               | ADCON0 (A/D Control 0) Register                |       |

| Memory and Stack Maps                   |               | ADCON1 (A/D Control 1)                         |       |

| Operation During Code Protect           |               | ADCON1 (A/D Control 1) Register                |       |

| Organization                            |               | ADRES (A/D Result)                             |       |

| Paging                                  |               | CCP1CON/CCP2CON (CCP Control) Registers        |       |

| PMADR Register                          |               | Configuration Word Register                    |       |

| PMADRH Register                         |               | Initialization Conditions (table)9             |       |

| Reading FLASH                           |               | INTCON (Interrupt Control)                     |       |

| Reading, PMADR Register                 |               | INTCON (Interrupt Control) Register            |       |

| Reading, PMADRH Register                |               | OPTION_REG                                     |       |

| Reading, PMCON1 Register                |               | OPTION_REG Register20                          |       |

| •                                       |               | PCON (Power Control)                           |       |

| Reading, PMDATH Register                |               | PCON (Power Control) Register                  |       |

| Reading, PMDATH RegisterRESET Vector    |               | PIE1 (Peripheral Interrupt Enable 1)           |       |

|                                         |               |                                                |       |

| Program Verification                    |               | PIE1 (Peripheral Interrupt Enable 1) Register  |       |

| Programming Pin (VPP)                   |               | PIE2 (Peripheral Interrupt Enable 2)           |       |

| Programming, Device Instructions        |               | PIE2 (Peripheral Interrupt Enable 2) Register  |       |

| PUSH                                    | ∠6            | PIR1 (Peripheral Interrupt Request 1)          |       |

| R                                       |               | PIR1 (Peripheral Interrupt Request 1) Register |       |

| R/W bit                                 | 60 66 67      | PIR2 (Peripheral Interrupt Request 2)          |       |

|                                         | , ,           | PIR2 (Peripheral Interrupt Request 2) Register | 24    |

| RA0/AN0 PinRA1/AN1 Pin                  |               | PMCON1 (Program Memory Control 1)              | 0.0   |

|                                         | ,             | Register                                       |       |

| RA2/AN2/APE Dia                         |               | RCSTA (Receive Status and Control) Register    |       |

| RA3/AN3/VREF Pin                        | ,             | Special Function, Summary10                    |       |

| RA4/T0CKI Pin                           | ,             | SSPCON (Sync Serial Port Control) Register     |       |

| RA5/SS/AN4 Pin                          | 8, 10         | SSPSTAT (Sync Serial Port Status) Register     |       |

| RAM. See Data Memory                    | 0.44          | STATUS Register                                |       |

| RB0/INT Pin                             | ,             | T1CON (Timer 1 Control) Register               |       |

| RB1 Pin                                 | ,             | T2CON (Timer2 Control) Register                |       |

| RB2 Pin                                 | ,             | TRISE Register                                 |       |

| RB3/PGM Pin                             | ,             | TXSTA (Transmit Status and Control) Register   |       |

| RB4 Pin                                 | ,             | RESET89                                        | ,     |

| RB5 Pin                                 | ,             | Brown-out Reset (BOR). See Brown-out Reset (BO | PR)   |

| RB6/PGC Pin                             | ,             | MCLR Reset. See MCLR                           |       |

| RB7/PGD Pin                             | ,             | Power-on Reset (POR). See Power-on Reset (POR  | ,     |

| RC0/T10S0/T1CKI Pin                     | ,             | RESET Conditions for All Registers             |       |

| RC1/T1OSI/CCP2 Pin                      | ,             | RESET Conditions for PCON Register             |       |

| RC2/CCP1 Pin                            | ,             | RESET Conditions for Program Counter           | 95    |

| RC3/SCK/SCL Pin                         | ,             | RESET Conditions for STATUS Register           | 95    |

| RC4/SDI/SDA Pin                         | ,             | RESET                                          |       |

| RC5/SDO Pin                             | 9, 11         | WDT Reset. See Watchdog Timer (WDT)            |       |

| RC6/TX/CK Pin                           | ,             | Revision History                               | . 161 |

| RC7/RX/DT Pin                           | 9 <b>,</b> 11 |                                                |       |

| S                                              | Timer14                                          |

|------------------------------------------------|--------------------------------------------------|

| S (START) bit                                  | Associated Registers50                           |

| SCI. See USART                                 | Asynchronous Counter Mode 49                     |

| SCL6                                           | Capacitor Selection 50                           |

| Serial Communication Interface. See USART      | Counter Operation 4                              |

| SLEEP89, 93, 10                                | Operation in Timer Mode 48                       |

| SMP bit                                        | Oscillator 5                                     |

| Software Simulator (MPLAB SIM)                 | Droppler 50                                      |

| Special Features of the CPU8                   |                                                  |

|                                                | D('1/ 1/ S /('1'D') Din                          |

| Special Function Registers16, 16–1             | Decetting of Limora Degictors 51                 |

| Speed, Operating                               | Resetting Timer1 using a CCP Trigger Output 50   |

| SPI Mode5                                      | Synchronized Counter Mode                        |

| Associated Registers                           | TMP1U Pogistor                                   |

| Serial Clock (SCK pin)5                        | TMP1I Pegister                                   |

| Serial Data In (SDI pin)                       | Timor?                                           |

| Serial Data Out (SDO pin)5                     | Accoriated Projectors                            |

| Slave Select5                                  | Output5                                          |

| SSP                                            | Postscaler5                                      |

| Overview                                       | December                                         |

| RA5/SS/AN4 Pin                                 | Proceeder and Postscalor                         |

| RC3/SCK/SCL Pin                                | Timing Diagrams                                  |

| RC4/SDI/SDA Pin                                | A/D Conversion                                   |

| RC5/SDO Pin                                    | Drawn out Doort                                  |

| SSP I <sup>2</sup> C Operation6                | Canture/Compare/DWM (CCD1 and CCD2) 13           |

| Slave Mode6                                    | CLKOUT and I/O                                   |

| SSPEN bit6                                     | Evternal Clock 120                               |

| SSPIF bit2                                     | 3 I <sup>2</sup> C Rus Data 13                   |

| SSPM<3:0> bits6                                | $^{1}$ $^{12}$ C Rue STAPT/STOP bite 13.         |

| SSPOV bit6                                     | 1 I <sup>2</sup> C Reception (7-bit Address)     |

| Stack2                                         | 1 <sup>2</sup> C Transmission (7 bit Address) 6: |

| Overflows2                                     | Parallel Slave Port                              |

| Underflow2                                     | Parallel Slave Port Read Waveforms               |

| STATUS Register                                | Parallal Slava Port Write Wayeforms              |

| DC Bit1                                        | 9                                                |

| <u>IRP</u> Bit1                                | Power-up Timer                                   |

| <u>PD</u> Bit9                                 | PWM Output55 RESET12i                            |

| TO Bit19, 9                                    | <u></u>                                          |

| Z Bit1                                         | DC Maturagle)                                    |

| Synchronous Serial Port Enable bit (SSPEN)6    | RC Network)                                      |

| Synchronous Serial Port Interrupt bit (SSPIF)2 | SPI Master Mode (CKE = 0, SMP = 0)               |

| Synchronous Serial Port Mode Select bits       | CDI Mada (Mastan Mada)                           |

| (SSPM<3:0>)6                                   | SPI Mode (Master Mode)                           |

| Synchronous Serial Port. See SSP               | SPI Mode (Slave Mode with CKE = 0)               |

| т                                              | SPI Mode (Slave Mode with CKE = 1)               |

|                                                | SPI Slave Mode (CKE = 0)                         |

| T1CKPS0 bit4                                   | 7 Start-up Timer                                 |

| T1CKPS1 bit4                                   | Time out Coguence on Dower up (MCLD Not          |

| <u>T10SCE</u> N bit4                           | Tip d to \(\nabla \)                             |

| T1SYNC bit4                                    | 7 Tied to VDD)<br>2 Case 19                      |

| T2CKPS0 bit5                                   |                                                  |

| T2CKPS1 bit5                                   | Case 2                                           |

| TAD8                                           | Through DC Notwork)                              |

| Time-out Sequence9                             | T: 0                                             |

| Timer04                                        | 3 Timer0                                         |

| Associated Registers4                          | 5 Timer1                                         |

| Clock Source Edge Select (T0SE bit)2           |                                                  |

| Clock Source Select (T0CS bit)2                | USART Asynchronous Master Transmission           |