Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                                          |

|----------------------------|--------------------------------------------------------------------------|

| Product Status             | Active                                                                   |

| Core Processor             | PIC                                                                      |

| Core Size                  | 8-Bit                                                                    |

| Speed                      | 20MHz                                                                    |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                                        |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                    |

| Number of I/O              | 22                                                                       |

| Program Memory Size        | 7KB (4K x 14)                                                            |

| Program Memory Type        | FLASH                                                                    |

| EEPROM Size                | -                                                                        |

| RAM Size                   | 192 x 8                                                                  |

| Voltage - Supply (Vcc/Vdd) | 4V ~ 5.5V                                                                |

| Data Converters            | A/D 5x8b                                                                 |

| Oscillator Type            | External                                                                 |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                        |

| Mounting Type              | Surface Mount                                                            |

| Package / Case             | 28-SOIC (0.295", 7.50mm Width)                                           |

| Supplier Device Package    | 28-SOIC                                                                  |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16f73t-i-so |

# Note the following details of the code protection feature on PICmicro® MCUs.

- The PICmicro family meets the specifications contained in the Microchip Data Sheet.

- Microchip believes that its family of PICmicro microcontrollers is one of the most secure products of its kind on the market today, when used in the intended manner and under normal conditions.

- There are dishonest and possibly illegal methods used to breach the code protection feature. All of these methods, to our knowledge, require using the PICmicro microcontroller in a manner outside the operating specifications contained in the data sheet. The person doing so may be engaged in theft of intellectual property.

- Microchip is willing to work with the customer who is concerned about the integrity of their code.

- Neither Microchip nor any other semiconductor manufacturer can guarantee the security of their code. Code protection does not

mean that we are guaranteeing the product as "unbreakable".

- Code protection is constantly evolving. We at Microchip are committed to continuously improving the code protection features of our product.

If you have any further questions about this matter, please contact the local sales office nearest to you.

Information contained in this publication regarding device applications and the like is intended through suggestion only and may be superseded by updates. It is your responsibility to ensure that your application meets with your specifications. No representation or warranty is given and no liability is assumed by Microchip Technology Incorporated with respect to the accuracy or use of such information, or infringement of patents or other intellectual property rights arising from such use or otherwise. Use of Microchip's products as critical components in life support systems is not authorized except with express written approval by Microchip. No licenses are conveyed, implicitly or otherwise, under any intellectual property rights.

#### **Trademarks**

The Microchip name and logo, the Microchip logo, FilterLab, KEELOQ, MPLAB, PIC, PICmicro, PICMASTER, PICSTART, PRO MATE, SEEVAL and The Embedded Control Solutions Company are registered trademarks of Microchip Technology Incorporated in the U.S.A. and other countries.

dsPIC, ECONOMONITOR, FanSense, FlexROM, fuzzyLAB, In-Circuit Serial Programming, ICSP, ICEPIC, microID, microPort, Migratable Memory, MPASM, MPLIB, MPLINK, MPSIM, MXDEV, PICC, PICDEM, PICDEM.net, rfPIC, Select Mode and Total Endurance are trademarks of Microchip Technology Incorporated in the U.S.A.

Serialized Quick Term Programming (SQTP) is a service mark of Microchip Technology Incorporated in the U.S.A.

All other trademarks mentioned herein are property of their respective companies.

© 2002, Microchip Technology Incorporated, Printed in the U.S.A., All Rights Reserved.

Microchip received QS-9000 quality system certification for its worldwide headquarters, design and wafer fabrication facilities in Chandler and Tempe, Arizona in July 1999. The Company's quality system processes and procedures are QS-9000 compliant for its PICmicro® 8-bit MCUs, KEELO® code hopping devices, Serial EEPROMs and microperipheral products. In addition, Microchip's quality system for the design and manufacture of development systems is ISO 9001 certified.

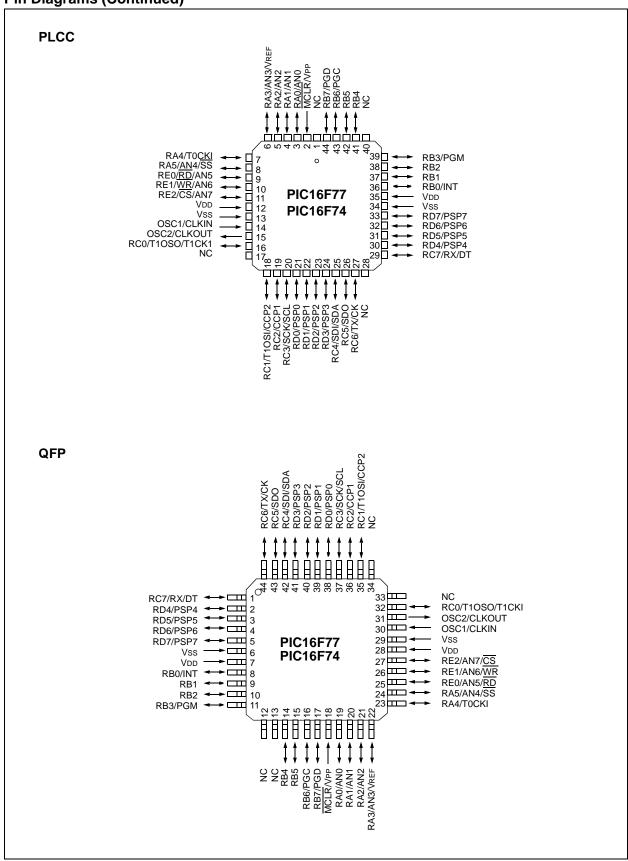

# Pin Diagrams (Continued)

## 2.2.2.2 OPTION\_REG Register

The OPTION\_REG register is a readable and writable register, which contains various control bits to configure the TMR0 prescaler/WDT postscaler (single assignable register known also as the prescaler), the External INT Interrupt, TMR0 and the weak pull-ups on PORTB.

Note: To achieve a 1:1 prescaler assignment for the TMR0 register, assign the prescaler to the Watchdog Timer.

# REGISTER 2-2: OPTION\_REG REGISTER (ADDRESS 81h, 181h)

| R/W-1 | R/W-1  | R/W-1 | R/W-1 | R/W-1 | R/W-1 | R/W-1 | R/W-1 |

|-------|--------|-------|-------|-------|-------|-------|-------|

| RBPU  | INTEDG | T0CS  | T0SE  | PSA   | PS2   | PS1   | PS0   |

| bit 7 |        |       |       |       |       |       | hit 0 |

bit 7 RBPU: PORTB Pull-up Enable bit

1 = PORTB pull-ups are disabled

0 = PORTB pull-ups are enabled by individual port latch values

bit 6 INTEDG: Interrupt Edge Select bit

1 = Interrupt on rising edge of RB0/INT pin0 = Interrupt on falling edge of RB0/INT pin

bit 5 TOCS: TMR0 Clock Source Select bit

1 = Transition on RA4/T0CKI pin

0 = Internal instruction cycle clock (CLKOUT)

bit 4 T0SE: TMR0 Source Edge Select bit

1 = Increment on high-to-low transition on RA4/T0CKI pin

0 = Increment on low-to-high transition on RA4/T0CKI pin

bit 3 **PSA**: Prescaler Assignment bit

1 = Prescaler is assigned to the WDT

0 = Prescaler is assigned to the Timer0 module

bit 2-0 **PS2:PS0**: Prescaler Rate Select bits

| Bit Value | TMR0 Rate | WDT Rate |

|-----------|-----------|----------|

| 000       | 1:2       | 1:1      |

| 001       | 1:4       | 1:2      |

| 010       | 1:8       | 1:4      |

| 011       | 1:16      | 1:8      |

| 100       | 1:32      | 1:16     |

| 101       | 1:64      | 1:32     |

| 110       | 1:128     | 1:64     |

| 111       | 1:256     | 1 : 128  |

| egend: |  |

|--------|--|

|--------|--|

$R = Readable \ bit \qquad \qquad W = Writable \ bit \qquad \qquad U = Unimplemented \ bit, read \ as '0'$

- n = Value at POR reset '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

## 2.2.2.6 PIE2 Register

The PIE2 register contains the individual enable bits for the CCP2 peripheral interrupt.

# REGISTER 2-6: PIE2 REGISTER (ADDRESS 8Dh)

| U-0   | U-0 | U-0 | U-0 | U-0 | U-0 | U-0 | R/W-0  |

|-------|-----|-----|-----|-----|-----|-----|--------|

| _     | -   | _   | _   | _   | _   |     | CCP2IE |

| bit 7 |     |     |     |     |     |     | bit 0  |

bit 7-1 **Unimplemented:** Read as '0' bit 0 **CCP2IE:** CCP2 Interrupt Enable bit

1 = Enables the CCP2 interrupt0 = Disables the CCP2 interrupt

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'- n = Value at POR reset '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

# 2.2.2.7 PIR2 Register

The PIR2 register contains the flag bits for the CCP2 interrupt.

Note: Interrupt flag bits are set when an interrupt condition occurs, regardless of the state of its corresponding enable bit or the global enable bit, GIE (INTCON<7>). User software should ensure the appropriate interrupt flag bits are clear prior to enabling an interrupt.

# REGISTER 2-7: PIR2 REGISTER (ADDRESS 0Dh)

| U-0   | U-0 | U-0 | U-0 | U-0 | U-0 | U-0 | R/W-0  |

|-------|-----|-----|-----|-----|-----|-----|--------|

| _     | _   | _   | _   | _   | _   | _   | CCP2IF |

| bit 7 |     |     |     |     |     |     | bit 0  |

bit 7-1 **Unimplemented:** Read as '0' bit 0 **CCP2IF:** CCP2 Interrupt Flag bit

Capture mode:

- 1 = A TMR1 register capture occurred (must be cleared in software)

- 0 = No TMR1 register capture occurred

Compare mode:

- 1 = A TMR1 register compare match occurred (must be cleared in software)

- 0 = No TMR1 register compare match occurred

PWM mode: Unused

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0' - n = Value at POR reset '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

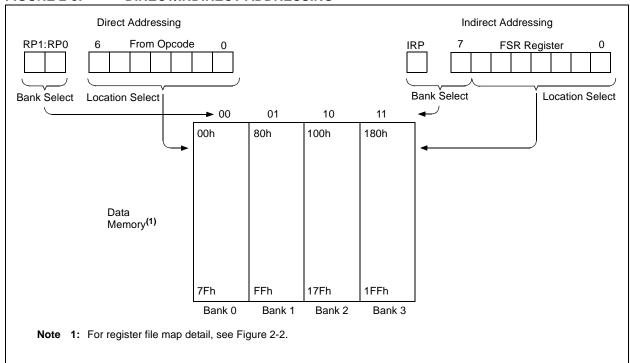

# 2.5 Indirect Addressing, INDF and FSR Registers

The INDF register is not a physical register. Addressing the INDF register will cause indirect addressing.

Indirect addressing is possible by using the INDF register. Any instruction using the INDF register actually accesses the register pointed to by the File Select Register, FSR. Reading the INDF register itself indirectly (FSR = '0') will read 00h. Writing to the INDF register indirectly results in a no operation (although status bits may be affected). An effective 9-bit address is obtained by concatenating the 8-bit FSR register and the IRP bit (STATUS<7>), as shown in Figure 2-5.

A simple program to clear RAM locations 20h-2Fh using indirect addressing is shown in Example 2-2.

### **EXAMPLE 2-2: INDIRECT ADDRESSING**

|        | MOVLW | 0x20   | ;initialize pointer  |

|--------|-------|--------|----------------------|

|        | MOVWF | FSR    | ;to RAM              |

| NEXT   | CLRF  | INDF   | clear INDF register; |

|        | INCF  | FSR, F | ;inc pointer         |

|        | BTFSS | FSR,4  | ;all done?           |

|        | GOTO  | NEXT   | ;no clear next       |

| CONTIN | UE    |        |                      |

| :      |       |        | ;yes continue        |

|        |       |        |                      |

# FIGURE 2-5: DIRECT/INDIRECT ADDRESSING

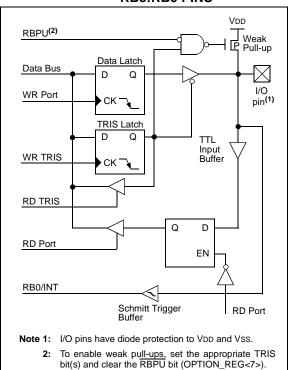

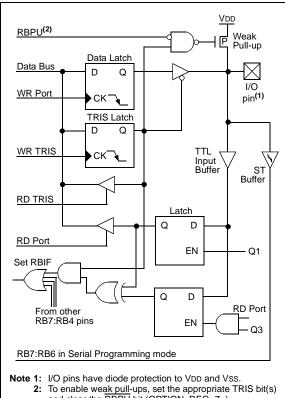

#### 4.2 **PORTB** and the TRISB Register

PORTB is an 8-bit wide, bi-directional port. The corresponding data direction register is TRISB. Setting a TRISB bit (= '1') will make the corresponding PORTB pin an input (i.e., put the corresponding output driver in a Hi-Impedance mode). Clearing a TRISB bit (= '0') will make the corresponding PORTB pin an output (i.e., put the contents of the output latch on the selected pin).

Each of the PORTB pins has a weak internal pull-up. A single control bit can turn on all the pull-ups. This is performed by clearing bit RBPU (OPTION\_REG<7>). The weak pull-up is automatically turned off when the port pin is configured as an output. The pull-ups are disabled on a Power-on Reset.

**BLOCK DIAGRAM OF** FIGURE 4-3: RB3:RB0 PINS

Four of the PORTB pins (RB7:RB4) have an interrupt-on-change feature. Only pins configured as inputs can cause this interrupt to occur (i.e., any RB7:RB4 pin configured as an output is excluded from the interrupt-on-change comparison). The input pins (of RB7:RB4) are compared with the old value latched on the last read of PORTB. The "mismatch" outputs of RB7:RB4 are ORed together to generate the RB Port Change Interrupt with flag bit RBIF (INTCON<0>).

This interrupt can wake the device from SLEEP. The user, in the Interrupt Service Routine, can clear the interrupt in the following manner:

- Any read or write of PORTB. This will end the mismatch condition.

- Clear flag bit RBIF.

A mismatch condition will continue to set flag bit RBIF. Reading PORTB will end the mismatch condition and allow flag bit RBIF to be cleared.

The interrupt-on-change feature is recommended for wake-up on key depression operation and operations where PORTB is only used for the interrupt-on-change feature. Polling of PORTB is not recommended while using the interrupt-on-change feature.

This interrupt on mismatch feature, together with software configureable pull-ups on these four pins, allow easy interface to a keypad and make it possible for wake-up on key depression. Refer to the Embedded Control Handbook, "Implementing Wake-up on Key Stroke" (AN552).

RB0/INT is an external interrupt input pin and is configured using the INTEDG bit (OPTION\_REG<6>).

RB0/INT is discussed in detail in Section 12.11.1.

FIGURE 4-4: **BLOCK DIAGRAM OF RB7:RB4 PINS**

and clear the RBPU bit (OPTION\_REG<7>).

# REGISTER 4-1: TRISE REGISTER (ADDRESS 89h)

| R-0   | R-0 | R/W-0 | R/W-0   | U-0 | R/W-1 | R/W-1 | R/W-1 |  |

|-------|-----|-------|---------|-----|-------|-------|-------|--|

| IBF   | OBF | IBOV  | PSPMODE | _   | Bit2  | Bit1  | Bit0  |  |

| bit 7 |     |       |         |     |       |       | bit 0 |  |

bit 7 Parallel Slave Port Status/Control bits:

IBF: Input Buffer Full Status bit

1 = A word has been received and is waiting to be read by the CPU

0 = No word has been received

bit 6 OBF: Output Buffer Full Status bit

1 = The output buffer still holds a previously written word

0 = The output buffer has been read

bit 5 IBOV: Input Buffer Overflow Detect bit (in Microprocessor mode)

1 = A write occurred when a previously input word has not been read (must be cleared in software)

0 = No overflow occurred

bit 4 **PSPMODE**: Parallel Slave Port Mode Select bit

1 = Parallel Slave Port mode0 = General Purpose I/O mode

bit 3 Unimplemented: Read as '0'

bit 2 PORTE Data Direction bits:

Bit2: Direction Control bit for pin RE2/CS/AN7

1 = Input

0 = Output

bit 1 Bit1: Direction Control bit for pin RE1/WR/AN6

1 = Input

0 = Output

bit 0 Bit0: Direction Control bit for pin RE0/RD/AN5

1 = Input

0 = Output

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

- n = Value at POR reset '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

# 5.2 Using Timer0 with an External Clock

When no prescaler is used, the external clock input is the same as the prescaler output. The synchronization of TOCKI, with the internal phase clocks, is accomplished by sampling the prescaler output on the Q2 and Q4 cycles of the internal phase clocks. Therefore, it is necessary for T0CKI to be high for at least 2Tosc (and a small RC delay of 20 ns) and low for at least 2Tosc (and a small RC delay of 20 ns). Refer to the electrical specification of the desired device.

# REGISTER 5-1: OPTION\_REG REGISTER

| R/W-1 | R/W-1  | R/W-1 | R/W-1 | R/W-1 | R/W-1 | R/W-1 | R/W-1 |

|-------|--------|-------|-------|-------|-------|-------|-------|

| RBPU  | INTEDG | T0CS  | T0SE  | PSA   | PS2   | PS1   | PS0   |

| bit 7 |        |       |       |       |       |       | bit 0 |

bit 7 RBPU: PORTB Pull-up Enable bit (see Section 2.2.2.2) bit 6 INTEDG: Interrupt Edge Select bit (see Section 2.2.2.2) T0CS: TMR0 Clock Source Select bit bit 5 1 = Transition on T0CKI pin 0 = Internal instruction cycle clock (CLKOUT) bit 4 T0SE: TMR0 Source Edge Select bit 1 = Increment on high-to-low transition on TOCKI pin 0 = Increment on low-to-high transition on T0CKI pin bit 3 PSA: Prescaler Assignment bit 1 = Prescaler is assigned to the WDT 0 = Prescaler is assigned to the Timer0 module bit 2-0 PS2:PS0: Prescaler Rate Select bits

| Bit Value | TMR0 Rate | WDT Rate |

|-----------|-----------|----------|

| 000       | 1:2       | 1:1      |

| 001       | 1:4       | 1:2      |

| 010       | 1:8       | 1:4      |

| 011       | 1:16      | 1:8      |

| 100       | 1:32      | 1:16     |

| 101       | 1:64      | 1:32     |

| 110       | 1:128     | 1:64     |

| 111       | 1:256     | 1:128    |

| Legend:                  |                  |                                    |                    |

|--------------------------|------------------|------------------------------------|--------------------|

| R = Readable bit         | W = Writable bit | U = Unimplemented bit, read as '0' |                    |

| - n = Value at POR reset | '1' = Bit is set | '0' = Bit is cleared               | x = Bit is unknown |

**Note:** To avoid an unintended device RESET, the instruction sequences shown in Example 5-1 and Example 5-2 (page 45) must be executed when changing the prescaler assignment between Timer0 and the WDT. This sequence must be followed even if the WDT is disabled.

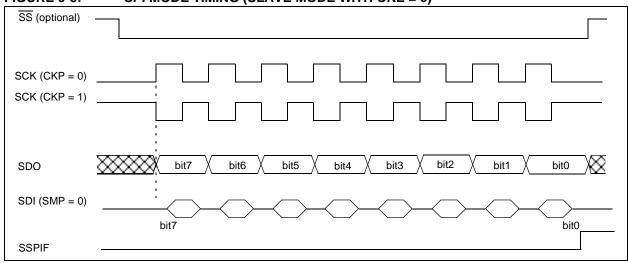

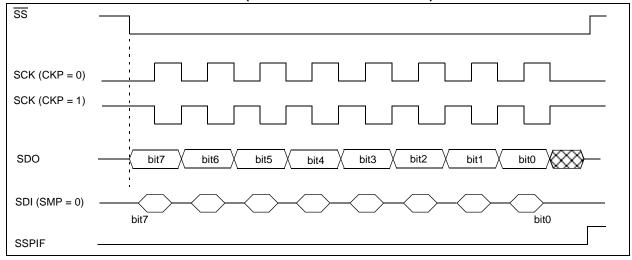

# FIGURE 9-4: SPI MODE TIMING (SLAVE MODE WITH CKE = 1)

# 10.1 USART Baud Rate Generator (BRG)

The BRG supports both the Asynchronous and Synchronous modes of the USART. It is a dedicated 8-bit baud rate generator. The SPBRG register controls the period of a free running 8-bit timer. In Asynchronous mode, bit BRGH (TXSTA<2>) also controls the baud rate. In Synchronous mode, bit BRGH is ignored. Table 10-1 shows the formula for computation of the baud rate for different USART modes which only apply in Master mode (internal clock).

Given the desired baud rate and Fosc, the nearest integer value for the SPBRG register can be calculated using the formula in Table 10-1. From this, the error in baud rate can be determined.

It may be advantageous to use the high baud rate (BRGH = 1), even for slower baud clocks. This is because the Fosc/(16(X + 1)) equation can reduce the baud rate error in some cases.

Writing a new value to the SPBRG register causes the BRG timer to be reset (or cleared). This ensures the BRG does not wait for a timer overflow before outputting the new baud rate.

### 10.1.1 SAMPLING

The data on the RC7/RX/DT pin is sampled three times by a majority detect circuit to determine if a high or a low level is present at the RX pin.

TABLE 10-1: BAUD RATE FORMULA

| SYNC | BRGH = 0 (Low Speed)                      | BRGH = 1 (High Speed)      |

|------|-------------------------------------------|----------------------------|

| 0    | (Asynchronous) Baud Rate = Fosc/(64(X+1)) | Baud Rate = Fosc/(16(X+1)) |

| 1    | (Synchronous) Baud Rate = Fosc/(4(X+1))   | N/A                        |

X = value in SPBRG (0 to 255)

TABLE 10-2: REGISTERS ASSOCIATED WITH BAUD RATE GENERATOR

| Address | Name                                  | Bit 7 | Bit 6                               | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 | Value on:<br>POR,<br>BOR | Value on<br>all other<br>RESETS |

|---------|---------------------------------------|-------|-------------------------------------|-------|-------|-------|-------|-------|-------|--------------------------|---------------------------------|

| 98h     | TXSTA                                 | CSRC  | TX9                                 | TXEN  | SYNC  | _     | BRGH  | TRMT  | TX9D  | 0000 -010                | 0000 -010                       |

| 18h     | RCSTA                                 | SPEN  | SPEN RX9 SREN CREN — FERR OERR RX9D |       |       |       |       |       | RX9D  | 0000 -00x                | 0000 -00x                       |

| 99h     | 9h SPBRG Baud Rate Generator Register |       |                                     |       |       |       |       |       |       | 0000 0000                | 0000 0000                       |

Legend: x = unknown, - = unimplemented, read as '0'. Shaded cells are not used by the BRG.

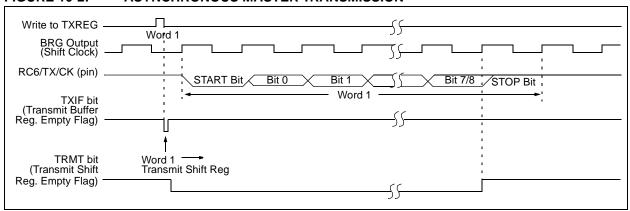

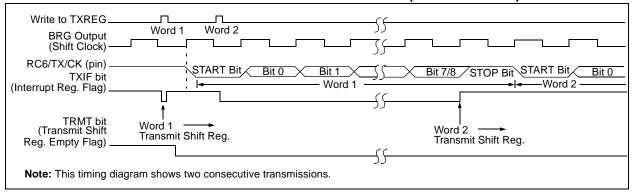

Steps to follow when setting up an Asynchronous Transmission:

- 1. Initialize the SPBRG register for the appropriate baud rate. If a high speed baud rate is desired, set bit BRGH (Section 10.1).

- Enable the asynchronous serial port by clearing bit SYNC and setting bit SPEN.

- 3. If interrupts are desired, then set enable bit TXIE.

- If 9-bit transmission is desired, then set transmit bit TX9.

- Enable the transmission by setting bit TXEN, which will also set bit TXIF.

- If 9-bit transmission is selected, the ninth bit should be loaded in bit TX9D.

- 7. Load data to the TXREG register (starts transmission).

- If using interrupts, ensure that GIE and PEIE in the INTCON register are set.

# FIGURE 10-2: ASYNCHRONOUS MASTER TRANSMISSION

# FIGURE 10-3: ASYNCHRONOUS MASTER TRANSMISSION (BACK TO BACK)

### TABLE 10-5: REGISTERS ASSOCIATED WITH ASYNCHRONOUS TRANSMISSION

| Address                | Name                                   | Bit 7                | Bit 6     | Bit 5   | Bit 4 | Bit 3 | Bit 2  | Bit 1  | Bit 0  | Value or<br>POR,<br>BOR | 1:  | Value of<br>all othe<br>RESET | er  |

|------------------------|----------------------------------------|----------------------|-----------|---------|-------|-------|--------|--------|--------|-------------------------|-----|-------------------------------|-----|

| 0Bh, 8Bh,<br>10Bh,18Bh | INTCON                                 | GIE                  | PEIE      | TMR0IE  | INTE  | RBIE  | TMR0IF | INTF   | RBIF   | 0000 00                 | Эx  | 0000 00                       | 00u |

| 0Ch                    | PIR1                                   | PSPIF <sup>(1)</sup> | ADIF      | RCIF    | TXIF  | SSPIF | CCP1IF | TMR2IF | TMR1IF | 0000 00                 | 00  | 0000 00                       | 000 |

| 18h                    | RCSTA                                  | SPEN                 | RX9       | SREN    | CREN  | _     | FERR   | OERR   | RX9D   | 0000 -0                 | Οx  | 0000 -0                       | 00x |

| 19h                    | TXREG                                  | USART Tra            | ansmit Re | egister |       |       |        |        |        | 0000 00                 | 0.0 | 0000 00                       | 000 |

| 8Ch                    | PIE1                                   | PSPIE <sup>(1)</sup> | ADIE      | RCIE    | TXIE  | SSPIE | CCP1IE | TMR2IE | TMR1IE | 0000 00                 | 0.0 | 0000 00                       | 000 |

| 98h                    | TXSTA                                  | CSRC                 | TX9       | TXEN    | SYNC  | _     | BRGH   | TRMT   | TX9D   | 0000 -0                 | 10  | 0000 -0                       | 010 |

| 99h                    | 99h SPBRG Baud Rate Generator Register |                      |           |         |       |       |        |        |        | 0000 00                 | 00  | 0000 00                       | 000 |

Legend: x = unknown, - = unimplemented locations read as '0'. Shaded cells are not used for asynchronous transmission.

Note 1: Bits PSPIE and PSPIF are reserved on the PIC16F73/76; always maintain these bits clear.

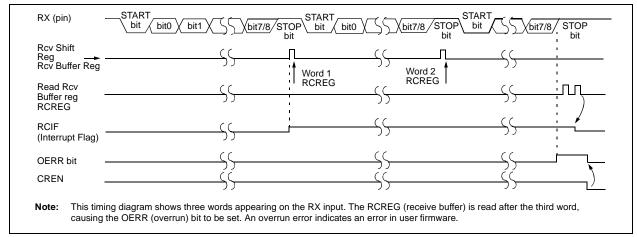

Steps to follow when setting up an Asynchronous Reception:

- Initialize the SPBRG register for the appropriate baud rate. If a high speed baud rate is desired, set bit BRGH (Section 10.1).

- Enable the asynchronous serial port by clearing bit SYNC and setting bit SPEN.

- If interrupts are desired, then set enable bit RCIE.

- 4. If 9-bit reception is desired, then set bit RX9.

- 5. Enable the reception by setting bit CREN.

- Flag bit RCIF will be set when reception is complete and an interrupt will be generated if enable bit RCIE is set.

- Read the RCSTA register to get the ninth bit (if enabled) and determine if any error occurred during reception.

- Read the 8-bit received data by reading the RCREG register.

- If any error occurred, clear the error by clearing enable bit CREN.

- 10. If using interrupts, ensure that GIE and PEIE in the INTCON register are set.

# TABLE 10-6: REGISTERS ASSOCIATED WITH ASYNCHRONOUS RECEPTION

| Address                | Name                               | Bit 7                | Bit 6     | Bit 5  | Bit 4 | Bit 3 | Bit 2  | Bit 1  | Bit 0  | Value on:<br>POR,<br>BOR | Value on<br>all other<br>RESETS |

|------------------------|------------------------------------|----------------------|-----------|--------|-------|-------|--------|--------|--------|--------------------------|---------------------------------|

| 0Bh, 8Bh,<br>10Bh,18Bh | INTCON                             | GIE                  | PEIE      | TMR0IE | INTE  | RBIE  | TMR0IF | INTF   | RBIF   | 0000 000x                | 0000 000u                       |

| 0Ch                    | PIR1                               | PSPIF <sup>(1)</sup> | ADIF      | RCIF   | TXIF  | SSPIF | CCP1IF | TMR2IF | TMR1IF | 0000 0000                | 0000 0000                       |

| 18h                    | RCSTA                              | SPEN                 | RX9       | SREN   | CREN  | _     | FERR   | OERR   | RX9D   | 0000 -00x                | 0000 -00x                       |

| 1Ah                    | RCREG                              | USART R              | eceive Re | gister |       |       |        |        |        | 0000 0000                | 0000 0000                       |

| 8Ch                    | PIE1                               | PSPIE <sup>(1)</sup> | ADIE      | RCIE   | TXIE  | SSPIE | CCP1IE | TMR2IE | TMR1IE | 0000 0000                | 0000 0000                       |

| 98h                    | TXSTA                              | CSRC                 | TX9       | TXEN   | SYNC  | _     | BRGH   | TRMT   | TX9D   | 0000 -010                | 0000 -010                       |

| 99h                    | SPBRG Baud Rate Generator Register |                      |           |        |       |       |        |        |        | 0000 0000                | 0000 0000                       |

Legend: x = unknown, - = unimplemented locations read as '0'. Shaded cells are not used for asynchronous reception.

Note 1: Bits PSPIE and PSPIF are reserved on the PIC16F73/76 devices; always maintain these bits clear.

# 11.0 ANALOG-TO-DIGITAL CONVERTER (A/D) MODULE

The 8-bit analog-to-digital (A/D) converter module has five inputs for the PIC16F73/76 and eight for the PIC16F74/77.

The A/D allows conversion of an analog input signal to a corresponding 8-bit digital number. The output of the sample and hold is the input into the converter, which generates the result via successive approximation. The analog reference voltage is software selectable to either the device's positive supply voltage (VDD), or the voltage level on the RA3/AN3/VREF pin.

The A/D converter has a unique feature of being able to operate while the device is in SLEEP mode. To operate in SLEEP, the A/D conversion clock must be derived from the A/D's internal RC oscillator.

The A/D module has three registers. These registers are:

- A/D Result Register ((ADRES)

- A/D Control Register 0 (ADCON0)

- A/D Control Register 1 ((ADCON1)

The ADCON0 register, shown in Register 11-1, controls the operation of the A/D module. The ADCON1 register, shown in Register 11-2, configures the functions of the port pins. The port pins can be configured as analog inputs (RA3 can also be a voltage reference), or as digital I/O.

Additional information on using the A/D module can be found in the PICmicro™ Mid-Range MCU Family Reference Manual (DS33023) and in Application Note, AN546 (DS00546).

# REGISTER 11-1: ADCON0 REGISTER (ADDRESS 1Fh)

| R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0   | U-0 | R/W-0 |

|-------|-------|-------|-------|-------|---------|-----|-------|

| ADCS1 | ADCS0 | CHS2  | CHS1  | CHS0  | GO/DONE | _   | ADON  |

| bit 7 |       |       |       |       |         |     | bit 0 |

bit 7-6 ADCS1:ADCS0: A/D Conversion Clock Select bits

00 = Fosc/2

01 = Fosc/8

10 = Fosc/32

11 = FRC (clock derived from the internal A/D module RC oscillator)

bit 5-3 CHS2:CHS0: Analog Channel Select bits

000 = Channel 0 (RA0/AN0)

001 = Channel 1 (RA1/AN1)

010 = Channel 2 (RA2/AN2)

011 = Channel 3 (RA3/AN3)

100 = Channel 4 (RA5/AN4)

101 = Channel 5 (RE0/AN5)(1)

110 = Channel 6 (RE1/AN6)(1)

111 = Channel 7 (RE2/AN7)(1)

bit 2 GO/DONE: A/D Conversion Status bit

If ADON = 1:

- 1 = A/D conversion in progress (setting this bit starts the A/D conversion)

- 0 = A/D conversion not in progress (this bit is automatically cleared by hardware when the A/D conversion is complete)

bit 1 **Unimplemented**: Read as '0'

bit 0 **ADON**: A/D On bit

1 = A/D converter module is operating

0 = A/D converter module is shut-off and consumes no operating current

Note 1: A/D channels 5, 6 and 7 are implemented on the PIC16F74/77 only.

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

- n = Value at POR reset '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

TABLE 12-6: INITIALIZATION CONDITIONS FOR ALL REGISTERS (CONTINUED)

| Register |    | Devices |    |    | Power-on Reset,<br>Brown-out Reset | MCLR Reset,<br>WDT Reset | Wake-up via WDT or<br>Interrupt |  |

|----------|----|---------|----|----|------------------------------------|--------------------------|---------------------------------|--|

| PIE2     | 73 | 74      | 76 | 77 | 0                                  | 0                        | u                               |  |

| PCON     | 73 | 74      | 76 | 77 | qq                                 | uu                       | uu                              |  |

| PR2      | 73 | 74      | 76 | 77 | 1111 1111                          | 1111 1111                | 1111 1111                       |  |

| SSPSTAT  | 73 | 74      | 76 | 77 | 00 0000                            | 00 0000                  | uu uuuu                         |  |

| SSPADD   | 73 | 74      | 76 | 77 | 0000 0000                          | 0000 0000                | uuuu uuuu                       |  |

| TXSTA    | 73 | 74      | 76 | 77 | 0000 -010                          | 0000 -010                | uuuu -uuu                       |  |

| SPBRG    | 73 | 74      | 76 | 77 | 0000 0000                          | 0000 0000                | uuuu uuuu                       |  |

| ADCON1   | 73 | 74      | 76 | 77 | 000                                | 000                      | uuu                             |  |

| PMDATA   | 73 | 74      | 76 | 77 | 0 0000                             | 0 0000                   | u uuuu                          |  |

| PMADR    | 73 | 74      | 76 | 77 | xxxx xxxx                          | uuuu uuuu                | uuuu uuuu                       |  |

| PMDATH   | 73 | 74      | 76 | 77 | xxxx xxxx                          | uuuu uuuu                | uuuu uuuu                       |  |

| PMADRH   | 73 | 74      | 76 | 77 | xxxx xxxx                          | uuuu uuuu                | uuuu uuuu                       |  |

| PMCON1   | 73 | 74      | 76 | 77 | 10                                 | 10                       | 1u                              |  |

Legend: u = unchanged, x = unknown, - = unimplemented bit, read as '0', q = value depends on condition, r = reserved, maintain clear

- Note 1: One or more bits in INTCON, PIR1 and/or PIR2 will be affected (to cause wake-up).

- 2: When the wake-up is due to an interrupt and the GIE bit is set, the PC is loaded with the interrupt vector (0004h).

- 3: See Table 12-5 for RESET value for specific condition.

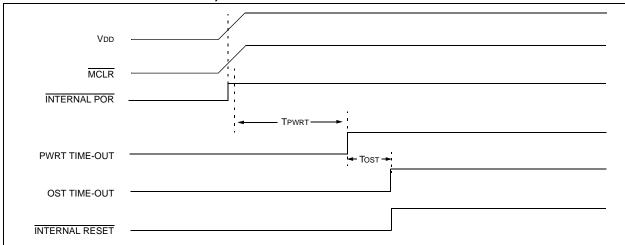

FIGURE 12-6: TIME-OUT SEQUENCE ON POWER-UP (MCLR TIED TO VDD THROUGH RC NETWORK)

# 15.3 Timing Parameter Symbology

The timing parameter symbols have been created using one of the following formats:

1. TppS2ppS 3. Tcc:st (l<sup>2</sup>C specifications only)

2. TppS 4. Ts (l<sup>2</sup>C specifications only)

T

F Frequency T Time

Lowercase letters (pp) and their meanings:

| рр |          |     |          |

|----|----------|-----|----------|

| СС | CCP1     | osc | OSC1     |

| ck | CLKOUT   | rd  | RD       |

| cs | CS       | rw  | RD or WR |

| di | SDI      | SC  | SCK      |

| do | SDO      | SS  | SS       |

| dt | Data in  | t0  | T0CKI    |

| io | I/O port | t1  | T1CKI    |

| mc | MCLR     | wr  | WR       |

Uppercase letters and their meanings:

| S                     |                        |      |              |

|-----------------------|------------------------|------|--------------|

| F                     | Fall                   | Р    | Period       |

| Н                     | High                   | R    | Rise         |

| -1                    | Invalid (Hi-impedance) | V    | Valid        |

| L                     | Low                    | Z    | Hi-impedance |

| I <sup>2</sup> C only |                        |      |              |

| AA                    | output access          | High | High         |

| BUF                   | Bus free               | Low  | Low          |

Tcc:st (I<sup>2</sup>C specifications only)

| CC  |                 |     |                |

|-----|-----------------|-----|----------------|

| HD  | Hold            | SU  | Setup          |

| ST  |                 |     |                |

| DAT | DATA input hold | STO | STOP condition |

| STA | START condition |     |                |

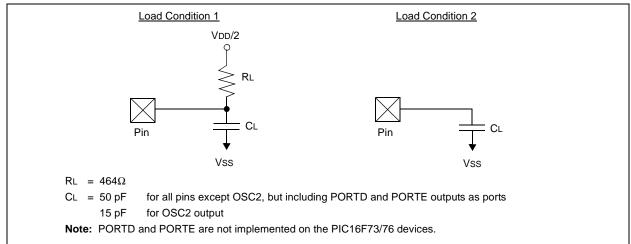

# FIGURE 15-3: LOAD CONDITIONS

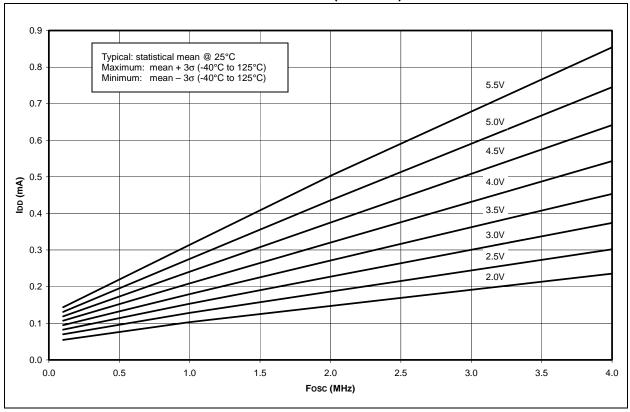

FIGURE 16-3: TYPICAL IDD vs. FOSC OVER VDD (XT MODE)

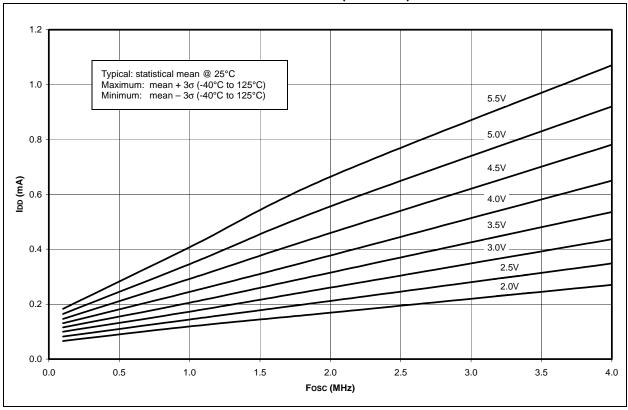

FIGURE 16-4: MAXIMUM IDD vs. Fosc OVER VDD (XT MODE)

#### 17.2 **Package Details**

The following sections give the technical details of the packages.

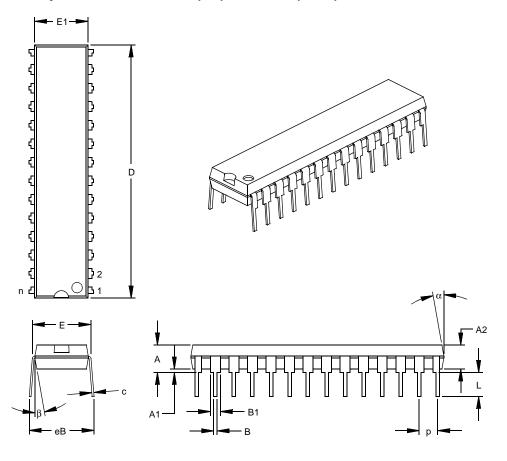

# 28-Lead Skinny Plastic Dual In-line (SP) – 300 mil (PDIP)

|                            | Units  |       | INCHES* |       | N     | IILLIMETERS |       |

|----------------------------|--------|-------|---------|-------|-------|-------------|-------|

| Dimension                  | Limits | MIN   | NOM     | MAX   | MIN   | NOM         | MAX   |

| Number of Pins             | n      |       | 28      |       |       | 28          |       |

| Pitch                      | р      |       | .100    |       |       | 2.54        |       |

| Top to Seating Plane       | Α      | .140  | .150    | .160  | 3.56  | 3.81        | 4.06  |

| Molded Package Thickness   | A2     | .125  | .130    | .135  | 3.18  | 3.30        | 3.43  |

| Base to Seating Plane      | A1     | .015  |         |       | 0.38  |             |       |

| Shoulder to Shoulder Width | Е      | .300  | .310    | .325  | 7.62  | 7.87        | 8.26  |

| Molded Package Width       | E1     | .275  | .285    | .295  | 6.99  | 7.24        | 7.49  |

| Overall Length             | D      | 1.345 | 1.365   | 1.385 | 34.16 | 34.67       | 35.18 |

| Tip to Seating Plane       | L      | .125  | .130    | .135  | 3.18  | 3.30        | 3.43  |

| Lead Thickness             | С      | .008  | .012    | .015  | 0.20  | 0.29        | 0.38  |

| Upper Lead Width           | B1     | .040  | .053    | .065  | 1.02  | 1.33        | 1.65  |

| Lower Lead Width           | В      | .016  | .019    | .022  | 0.41  | 0.48        | 0.56  |

| Overall Row Spacing §      | eВ     | .320  | .350    | .430  | 8.13  | 8.89        | 10.92 |

| Mold Draft Angle Top       | α      | 5     | 10      | 15    | 5     | 10          | 15    |

| Mold Draft Angle Bottom    | β      | 5     | 10      | 15    | 5     | 10          | 15    |

<sup>\*</sup> Controlling Parameter

Dimension D and E1 do not include mold flash or protrusions. Mold flash or protrusions shall not exceed

.010" (0.254mm) per side. JEDEC Equivalent: MO-095

Drawing No. C04-070

<sup>§</sup> Significant Characteristic

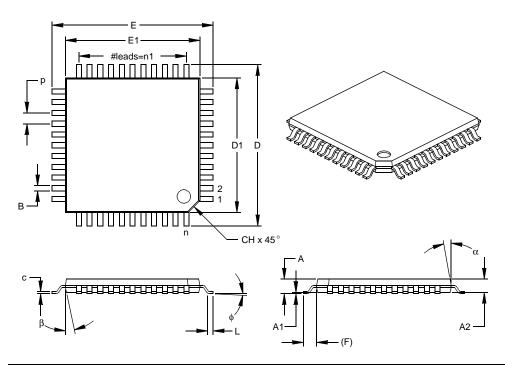

# 44-Lead Plastic Thin Quad Flatpack (PT) 10x10x1 mm Body, 1.0/0.10 mm Lead Form (TQFP)

|                          | Units  |      | INCHES |      | М     | ILLIMETERS | *     |

|--------------------------|--------|------|--------|------|-------|------------|-------|

| Dimension                | Limits | MIN  | MOM    | MAX  | MIN   | NOM        | MAX   |

| Number of Pins           | n      |      | 44     |      |       | 44         |       |

| Pitch                    | р      |      | .031   |      |       | 0.80       |       |

| Pins per Side            | n1     |      | 11     |      |       | 11         |       |

| Overall Height           | Α      | .039 | .043   | .047 | 1.00  | 1.10       | 1.20  |

| Molded Package Thickness | A2     | .037 | .039   | .041 | 0.95  | 1.00       | 1.05  |

| Standoff §               | A1     | .002 | .004   | .006 | 0.05  | 0.10       | 0.15  |

| Foot Length              | L      | .018 | .024   | .030 | 0.45  | 0.60       | 0.75  |

| Footprint (Reference)    | (F)    |      | .039   |      | 1.00  |            |       |

| Foot Angle               | ф      | 0    | 3.5    | 7    | 0     | 3.5        | 7     |

| Overall Width            | Е      | .463 | .472   | .482 | 11.75 | 12.00      | 12.25 |

| Overall Length           | D      | .463 | .472   | .482 | 11.75 | 12.00      | 12.25 |

| Molded Package Width     | E1     | .390 | .394   | .398 | 9.90  | 10.00      | 10.10 |

| Molded Package Length    | D1     | .390 | .394   | .398 | 9.90  | 10.00      | 10.10 |

| Lead Thickness           | С      | .004 | .006   | .008 | 0.09  | 0.15       | 0.20  |

| Lead Width               | В      | .012 | .015   | .017 | 0.30  | 0.38       | 0.44  |

| Pin 1 Corner Chamfer     | CH     | .025 | .035   | .045 | 0.64  | 0.89       | 1.14  |

| Mold Draft Angle Top     | α      | 5    | 10     | 15   | 5     | 10         | 15    |

| Mold Draft Angle Bottom  | β      | 5    | 10     | 15   | 5     | 10         | 15    |

<sup>\*</sup> Controlling Parameter § Significant Characteristic

Dimensions D1 and E1 do not include mold flash or protrusions. Mold flash or protrusions shall not exceed

.010" (0.254mm) per side.

JEDEC Equivalent: MS-026

Drawing No. C04-076

# PIC16F7X

# APPENDIX C: CONVERSION CONSIDERATIONS

Considerations for converting from previous versions of devices to the ones listed in this data sheet are listed in Table C-1.

TABLE C-1: CONVERSION CONSIDERATIONS

| Characteristic | PIC16C7X                                         | PIC16F87X                                               | PIC16F7X                                         |  |

|----------------|--------------------------------------------------|---------------------------------------------------------|--------------------------------------------------|--|

| Pins           | 28/40                                            | 28/40                                                   | 28/40                                            |  |

| Timers         | 3                                                | 3                                                       | 3                                                |  |

| Interrupts     | 11 or 12                                         | 13 or 14                                                | 11 or 12                                         |  |

| Communication  | PSP, USART, SSP<br>(SPI, I <sup>2</sup> C Slave) | PSP, USART, SSP<br>(SPI, I <sup>2</sup> C Master/Slave) | PSP, USART, SSP<br>(SPI, I <sup>2</sup> C Slave) |  |

| Frequency      | 20 MHz                                           | 20 MHz                                                  | 20 MHz                                           |  |

| A/D            | 8-bit                                            | 10-bit                                                  | 8-bit                                            |  |

| ССР            | 2                                                | 2                                                       | 2                                                |  |

| Program Memory | 4K, 8K EPROM                                     | 4K, 8K FLASH<br>(1,000 E/W cycles)                      | 4K, 8K FLASH<br>(100 E/W cycles typical)         |  |

| RAM            | 192, 368 bytes                                   | 192, 368 bytes                                          | 192, 368 bytes                                   |  |

| EEPROM Data    | None                                             | 128, 256 bytes                                          | None                                             |  |

| Other          | _                                                | In-Circuit Debugger,<br>Low Voltage Programming         | _                                                |  |

# PIC16F7X PRODUCT IDENTIFICATION SYSTEM

To order or obtain information, e.g., on pricing or delivery, refer to the factory or the listed sales office.

| PART NO.             | <u>x</u>                                                                                                                                                                                                                                                                            | XXX                             | Examples:                                                                                                                                                                                                                                                                    |

|----------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| <b>Device</b> Device | Temperature Package Range  PIC16F7X <sup>(1)</sup> , PIC16F7XT <sup>(1)</sup> ; PIC16LF7X <sup>(1)</sup> , PIC16LF7XT <sup>(1)</sup>                                                                                                                                                | Pattern  VDD range 4.0V to 5.5V | <ul> <li>a) PIC16F77-I/P 301 = Industrial temp., PDIP package, normal VDD limits, QTP pattern #301.</li> <li>b) PIC16LF76-I/SO = Industrial temp., SOIC package, Extended VDD limits.</li> <li>c) PIC16F74-E/P = Extended temp., PDIP package, normal VDD limits.</li> </ul> |

| Temperature Range    | PIC16LF7X <sup>(1)</sup> , PIC16LF7XT <sup>(1)</sup> $I = -40^{\circ}C \text{ to } +85^{\circ}C$ $E = -40^{\circ}C \text{ to } +125^{\circ}C$                                                                                                                                       | (Industrial)                    | Note 1: F = CMOS FLASH LF = Low Power CMOS FLASH                                                                                                                                                                                                                             |

| Package              | ML         =         MLF (Micro Lea           PT         =         TQFP (Thin Quantum           SO         =         SOIC           SP         =         Skinny Plastic E           P         =         PDIP           L         =         PLCC           SS         =         SSOP | ad Flatpack)                    | 2: T = in tape and reel - SOIC, PLCC, SSOP, TQFP packages only.                                                                                                                                                                                                              |

| Pattern              | QTP, SQTP, Code or Specia<br>(blank otherwise)                                                                                                                                                                                                                                      | I Requirements                  |                                                                                                                                                                                                                                                                              |

# **Sales and Support**

#### Data Sheets

Products supported by a preliminary Data Sheet may have an errata sheet describing minor operational differences and recommended workarounds. To determine if an errata sheet exists for a particular device, please contact one of the following:

- 1. Your local Microchip sales office

- 2. The Microchip Corporate Literature Center U.S. FAX: (480) 792-7277

- 3. The Microchip Worldwide Site (www.microchip.com)

Please specify which device, revision of silicon and Data Sheet (include Literature #) you are using.

### **New Customer Notification System**

Register on our web site (www.microchip.com/cn) to receive the most current information on our products.