Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                  |

|----------------------------|-------------------------------------------------------------------------|

| Core Processor             | PIC                                                                     |

| Core Size                  | 8-Bit                                                                   |

| Speed                      | 20MHz                                                                   |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                                       |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                   |

| Number of I/O              | 33                                                                      |

| Program Memory Size        | 7KB (4K x 14)                                                           |

| Program Memory Type        | FLASH                                                                   |

| EEPROM Size                | -                                                                       |

| RAM Size                   | 192 x 8                                                                 |

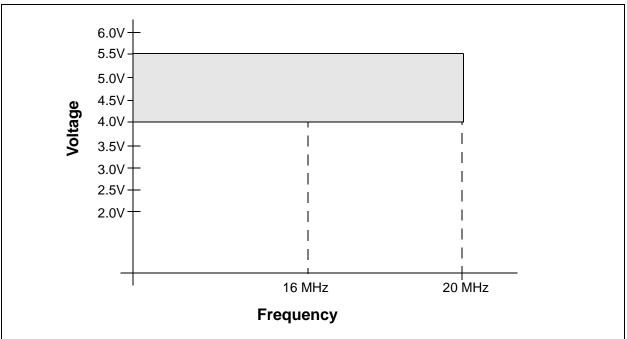

| Voltage - Supply (Vcc/Vdd) | 4V ~ 5.5V                                                               |

| Data Converters            | A/D 8x8b                                                                |

| Oscillator Type            | External                                                                |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                       |

| Mounting Type              | Surface Mount                                                           |

| Package / Case             | 44-TQFP                                                                 |

| Supplier Device Package    | 44-TQFP (10x10)                                                         |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16f74-i-pt |

|                            |                                                                         |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## 3.3 Reading the FLASH Program Memory

A program memory location may be read by writing two bytes of the address to the PMADR and PMADRH registers and then setting control bit RD (PMCON1<0>). Once the read control bit is set, the microcontroller will use the next two instruction cycles to read the data. The data is available in the PMDATA and PMDATH registers after the second NOP instruction. Therefore, it can be read as two bytes in the following instructions. The PMDATA and PMDATH registers will hold this value until the next read operation.

# 3.4 Operation During Code Protect

FLASH program memory has its own code protect mechanism. External Read and Write operations by programmers are disabled if this mechanism is enabled.

The microcontroller can read and execute instructions out of the internal FLASH program memory, regardless of the state of the code protect configuration bits.

|                      | BSF               | STATUS, RP1 | ;                                                                                          |

|----------------------|-------------------|-------------|--------------------------------------------------------------------------------------------|

|                      | BCF               | STATUS, RP0 | ; Bank 2                                                                                   |

|                      | MOVF              | ADDRH, W    | ;                                                                                          |

|                      | MOVWF             | PMADRH      | ; MSByte of Program Address to read                                                        |

|                      | MOVF              | ADDRL, W    | ;                                                                                          |

|                      | MOVWF             | PMADR       | ; LSByte of Program Address to read                                                        |

|                      | BSF               | STATUS, RP0 | ; Bank 3 Required                                                                          |

| Required<br>Sequence | BSF<br>NOP<br>NOP | PMCON1, RD  | ; EEPROM Read Sequence<br>; memory is read in the next two cycles after BSF PMCON1,RD<br>; |

|                      | BCF               | STATUS, RPO | ; Bank 2                                                                                   |

|                      | MOVF              | PMDATA, W   | ; W = LSByte of Program PMDATA                                                             |

|                      | MOVF              | PMDATH, W   | ; W = MSByte of Program PMDATA                                                             |

#### EXAMPLE 3-1: FLASH PROGRAM READ

#### TABLE 3-1: REGISTERS ASSOCIATED WITH PROGRAM FLASH

| Address | Name   | Bit 7     | Bit 6                  | Bit 5    | Bit 4                   | Bit 3     | Bit 2     | Bit 1 | Bit 0 | Value on:<br>POR,<br>BOR | Value on<br>all other<br>RESETS |

|---------|--------|-----------|------------------------|----------|-------------------------|-----------|-----------|-------|-------|--------------------------|---------------------------------|

| 10Dh    | PMADR  | Address F | Register Lo            | ow Byte  |                         |           |           |       |       | xxxx xxxx                | uuuu uuuu                       |

| 10Fh    | PMADRH | _         | —                      | _        | Address I               | xxxx xxxx | uuuu uuuu |       |       |                          |                                 |

| 10Ch    | PMDATA | Data Reg  | Data Register Low Byte |          |                         |           |           |       |       |                          | uuuu uuuu                       |

| 10Eh    | PMDATH | _         | _                      | Data Reg | Data Register High Byte |           |           |       |       |                          | uuuu uuuu                       |

| 18Ch    | PMCON1 | _(1)      | —                      | _        | _                       | —         | _         | —     | RD    | 10                       | 10                              |

Legend: x = unknown, u = unchanged, r = reserved, - = unimplemented read as '0'. Shaded cells are not used during FLASH access. **Note 1:** This bit always reads as a '1'.

# 4.0 I/O PORTS

Some pins for these I/O ports are multiplexed with an alternate function for the peripheral features on the device. In general, when a peripheral is enabled, that pin may not be used as a general purpose I/O pin.

Additional information on I/O ports may be found in the PICmicro<sup>™</sup> Mid-Range Reference Manual, (DS33023).

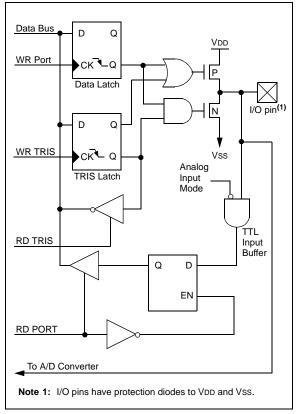

# 4.1 PORTA and the TRISA Register

PORTA is a 6-bit wide, bi-directional port. The corresponding data direction register is TRISA. Setting a TRISA bit (= '1') will make the corresponding PORTA pin an input (i.e., put the corresponding output driver in a Hi-Impedance mode). Clearing a TRISA bit (= '0') will make the corresponding PORTA pin an output (i.e., put the contents of the output latch on the selected pin).

Reading the PORTA register reads the status of the pins, whereas writing to it will write to the port latch. All write operations are read-modify-write operations. Therefore, a write to a port implies that the port pins are read, the value is modified and then written to the port data latch.

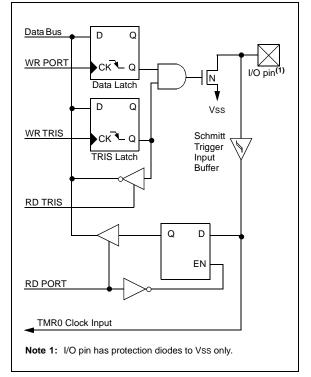

Pin RA4 is multiplexed with the Timer0 module clock input to become the RA4/T0CKI pin. The RA4/T0CKI pin is a Schmitt Trigger input and an open drain output. All other PORTA pins have TTL input levels and full CMOS output drivers.

Other PORTA pins are multiplexed with analog inputs and analog VREF input. The operation of each pin is selected by clearing/setting the control bits in the ADCON1 register (A/D Control Register1).

**Note:** On a Power-on Reset, these pins are configured as analog inputs and read as '0'.

The TRISA register controls the direction of the RA pins, even when they are being used as analog inputs. The user must ensure the bits in the TRISA register are maintained set, when using them as analog inputs.

| BCF<br>BCF<br>CLRF                      | STATUS,<br>STATUS,<br>PORTA                |     | ;<br>; Bank0<br>; Initialize PORTA by<br>; clearing output<br>: data latches | Y |

|-----------------------------------------|--------------------------------------------|-----|------------------------------------------------------------------------------|---|

| BSF<br>MOVLW<br>MOVWF<br>MOVLW<br>MOVWF | STATUS,<br>0x06<br>ADCON1<br>0xCF<br>TRISA | RPO | ,                                                                            |   |

# FIGURE 4-1:

#### BLOCK DIAGRAM OF RA3:RA0 AND RA5 PINS

FIGURE 4-2:

#### BLOCK DIAGRAM OF RA4/T0CKI PIN

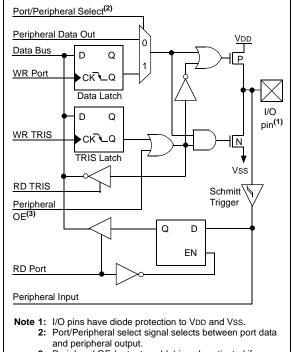

## 4.3 PORTC and the TRISC Register

PORTC is an 8-bit wide, bi-directional port. The corresponding data direction register is TRISC. Setting a TRISC bit (= '1') will make the corresponding PORTC pin an input (i.e., put the corresponding output driver in a Hi-Impedance mode). Clearing a TRISC bit (= '0') will make the corresponding PORTC pin an output (i.e., put the contents of the output latch on the selected pin).

PORTC is multiplexed with several peripheral functions (Table 4-5). PORTC pins have Schmitt Trigger input buffers.

When enabling peripheral functions, care should be taken in defining TRIS bits for each PORTC pin. Some peripherals override the TRIS bit to make a pin an output, while other peripherals override the TRIS bit to make a pin an input. Since the TRIS bit override is in effect while the peripheral is enabled, read-modify-write instructions (BSF, BCF, XORWF) with TRISC as destination should be avoided. The user should refer to the corresponding peripheral section for the correct TRIS bit settings, and to Section 13.1 for additional information on read-modify-write operations.

#### FIGURE 4-5:

#### PORTC BLOCK DIAGRAM (PERIPHERAL OUTPUT OVERRIDE)

**3:** Peripheral OE (output enable) is only activated if peripheral select is active.

| Name            | Bit# | Buffer Type | Function                                                                                        |

|-----------------|------|-------------|-------------------------------------------------------------------------------------------------|

| RC0/T1OSO/T1CKI | bit0 | ST          | Input/output port pin or Timer1 oscillator output/Timer1 clock input.                           |

| RC1/T1OSI/CCP2  | bit1 | ST          | Input/output port pin or Timer1 oscillator input or Capture2 input/Compare2 output/PWM2 output. |

| RC2/CCP1        | bit2 | ST          | Input/output port pin or Capture1 input/Compare1 output/PWM1 output.                            |

| RC3/SCK/SCL     | bit3 | ST          | RC3 can also be the synchronous serial clock for both SPI and $I^2C$ modes.                     |

| RC4/SDI/SDA     | bit4 | ST          | RC4 can also be the SPI Data In (SPI mode) or Data I/O (I <sup>2</sup> C mode).                 |

| RC5/SDO         | bit5 | ST          | Input/output port pin or Synchronous Serial Port data output.                                   |

| RC6/TX/CK       | bit6 | ST          | Input/output port pin or USART Asynchronous Transmit or<br>Synchronous Clock.                   |

| RC7/RX/DT       | bit7 | ST          | Input/output port pin or USART Asynchronous Receive or Synchronous Data.                        |

#### TABLE 4-5: PORTC FUNCTIONS

Legend: ST = Schmitt Trigger input

#### TABLE 4-6: SUMMARY OF REGISTERS ASSOCIATED WITH PORTC

| Address | Name  | Bit 7 | Bit 6                         | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 | Value on:<br>POR,<br>BOR | Value on<br>all other<br>RESETS |

|---------|-------|-------|-------------------------------|-------|-------|-------|-------|-------|-------|--------------------------|---------------------------------|

| 07h     | PORTC | RC7   | RC6                           | RC5   | RC4   | RC3   | RC2   | RC1   | RC0   | xxxx xxxx                | uuuu uuuu                       |

| 87h     | TRISC | PORTC | PORTC Data Direction Register |       |       |       |       |       |       |                          | 1111 1111                       |

Legend: x = unknown, u = unchanged

#### 8.4.1 CCP PIN CONFIGURATION

The user must configure the RC2/CCP1 pin as an output by clearing the TRISC<2> bit.

| Note: | Clearing the CCP1CON register will force |

|-------|------------------------------------------|

|       | the RC2/CCP1 compare output latch to the |

|       | default low level. This is not the PORTC |

|       | I/O data latch.                          |

#### 8.4.2 TIMER1 MODE SELECTION

Timer1 must be running in Timer mode or Synchronized Counter mode if the CCP module is using the compare feature. In Asynchronous Counter mode, the compare operation may not work.

#### 8.4.3 SOFTWARE INTERRUPT MODE

When Generate Software Interrupt mode is chosen, the CCP1 pin is not affected. The CCP1IF or CCP2IF bit is set, causing a CCP interrupt (if enabled).

#### 8.4.4 SPECIAL EVENT TRIGGER

In this mode, an internal hardware trigger is generated, which may be used to initiate an action.

The special event trigger output of CCP1 resets the TMR1 register pair. This allows the CCPR1 register to effectively be a 16-bit programmable period register for Timer1.

The special event trigger output of CCP2 resets the TMR1 register pair and starts an A/D conversion (if the A/D module is enabled).

**Note:** The special event trigger from the CCP1 and CCP2 modules will not set interrupt flag bit TMR1IF (PIR1<0>).

| Address               | Name    | Bit 7                | Bit 6      | Bit 5        | Bit 4         | Bit 3          | Bit 2      | Bit 1      | Bit 0  | Value on:<br>POR,<br>BOR | Value on<br>all other<br>RESETS |

|-----------------------|---------|----------------------|------------|--------------|---------------|----------------|------------|------------|--------|--------------------------|---------------------------------|

| 0Bh,8Bh,<br>10Bh,18Bh | INTCON  | GIE                  | PEIE       | TMR0IE       | INTE          | RBIE           | TMR0IF     | INTF       | RBIF   | 0000 000x                | 0000 000u                       |

| 0Ch                   | PIR1    | PSPIF <sup>(1)</sup> | ADIF       | RCIF         | TXIF          | SSPIF          | CCP1IF     | TMR2IF     | TMR1IF | 0000 0000                | 0000 0000                       |

| 0Dh                   | PIR2    | —                    | —          | —            | —             | _              | _          | _          | CCP2IF | 0                        | 0                               |

| 8Ch                   | PIE1    | PSPIE <sup>(1)</sup> | ADIE       | RCIE         | TXIE          | SSPIE          | CCP1IE     | TMR2IE     | TMR1IE | 0000 0000                | 0000 0000                       |

| 8Dh                   | PIE2    | —                    | _          | —            | _             | _              | —          | _          | CCP2IE | 0                        | 0                               |

| 87h                   | TRISC   | PORTC D              | ata Direc  | tion Registe | er            |                |            |            |        | 1111 1111                | 1111 1111                       |

| 0Eh                   | TMR1L   | Holding R            | egister fo | r the Least  | Significant   | Byte of the 1  | 6-bit TMR  | 1 Register |        | xxxx xxxx                | uuuu uuuu                       |

| 0Fh                   | TMR1H   | Holding R            | egister fo | r the Most S | Significant E | Byte of the 16 | 6-bit TMR1 | Register   |        | xxxx xxxx                | uuuu uuuu                       |

| 10h                   | T1CON   | —                    |            | T1CKPS1      | T1CKPS0       | T1OSCEN        | T1SYNC     | TMR1CS     | TMR10N | 00 0000                  | uu uuuu                         |

| 15h                   | CCPR1L  | Capture/C            | ompare/l   | PWM Regis    | ster1 (LSB)   |                |            |            |        | xxxx xxxx                | uuuu uuuu                       |

| 16h                   | CCPR1H  | Capture/C            | ompare/l   | PWM Regis    | ster1 (MSB)   |                |            |            |        | xxxx xxxx                | uuuu uuuu                       |

| 17h                   | CCP1CON | —                    |            | CCP1X        | CCP1Y         | CCP1M3         | CCP1M2     | CCP1M1     | CCP1M0 | 00 0000                  | 00 0000                         |

| 1Bh                   | CCPR2L  | Capture/C            | ompare/l   | PWM Regis    | ster2 (LSB)   |                |            |            |        | xxxx xxxx                | uuuu uuuu                       |

| 1Ch                   | CCPR2H  | Capture/C            | ompare/l   | PWM Regis    | ster2 (MSB)   |                |            |            |        | xxxx xxxx                | uuuu uuuu                       |

| 1Dh                   | CCP2CON | —                    | _          | CCP2X        | CCP2Y         | CCP2M3         | CCP2M2     | CCP2M1     | CCP2M0 | 00 0000                  | 00 0000                         |

#### TABLE 8-3: REGISTERS ASSOCIATED WITH CAPTURE, COMPARE, AND TIMER1

Legend: x = unknown, u = unchanged, - = unimplemented, read as '0'. Shaded cells are not used by Capture and Timer1.

**Note 1:** The PSP is not implemented on the PIC16F73/76; always maintain these bits clear.

#### 9.3.1.1 Addressing

Once the SSP module has been enabled, it waits for a START condition to occur. Following the START condition, the 8-bits are shifted into the SSPSR register. All incoming bits are sampled with the rising edge of the clock (SCL) line. The value of register SSPSR<7:1> is compared to the value of the SSPADD register. The address is compared on the falling edge of the eighth clock (SCL) pulse. If the addresses match, and the BF and SSPOV bits are clear, the following events occur:

- a) The SSPSR register value is loaded into the SSPBUF register.

- b) The buffer full bit, BF is set.

- c) An ACK pulse is generated.

- d) SSP interrupt flag bit, SSPIF (PIR1<3>) is set (interrupt is generated if enabled) - on the falling edge of the ninth SCL pulse.

In 10-bit Address mode, two address bytes need to be received by the slave (Figure 9-7). The five Most Significant bits (MSbs) of the first address byte specify if this is a 10-bit address. Bit R/W (SSPSTAT<2>) must specify a write so the slave device will receive the second address byte. For a 10-bit address, the first byte would equal '1111 0 A9 A8 0', where A9 and A8 are the two MSbs of the address. The sequence of events for 10-bit address is as follows, with steps 7 - 9 for slave-transmitter:

- 1. Receive first (high) byte of address (bits SSPIF, BF, and bit UA (SSPSTAT<1>) are set).

- Update the SSPADD register with second (low) byte of address (clears bit UA and releases the SCL line).

- 3. Read the SSPBUF register (clears bit BF) and clear flag bit SSPIF.

- 4. Receive second (low) byte of address (bits SSPIF, BF, and UA are set).

- 5. Update the SSPADD register with the first (high) byte of address, if match releases SCL line, this will clear bit UA.

- 6. Read the SSPBUF register (clears bit BF) and clear flag bit SSPIF.

- 7. Receive Repeated START condition.

- 8. Receive first (high) byte of address (bits SSPIF and BF are set).

- 9. Read the SSPBUF register (clears bit BF) and clear flag bit SSPIF.

| Status Bits as Data<br>Transfer is Received |       | $SSPSR \to SSPBUF$ | Generate ACK<br>Pulse | Set bit SSPIF<br>(SSP Interrupt occurs |  |  |

|---------------------------------------------|-------|--------------------|-----------------------|----------------------------------------|--|--|

| BF                                          | SSPOV |                    | Fuise                 | if enabled)                            |  |  |

| 0                                           | 0     | Yes                | Yes                   | Yes                                    |  |  |

| 1                                           | 0     | No                 | No                    | Yes                                    |  |  |

| 1                                           | 1     | No                 | No                    | Yes                                    |  |  |

| 0                                           | 1     | No                 | No                    | Yes                                    |  |  |

# TABLE 9-2: DATA TRANSFER RECEIVED BYTE ACTIONS

**Note:** Shaded cells show the conditions where the user software did not properly clear the overflow condition.

#### 9.3.1.2 Reception

When the R/W bit of the address byte is clear and an address match occurs, the R/W bit of the SSPSTAT register is cleared. The received address is loaded into the SSPBUF register.

When the address byte overflow condition exists, then no Acknowledge (ACK) pulse is given. An overflow condition is defined as either bit BF (SSPSTAT<0>) is set, or bit SSPOV (SSPCON<6>) is set. This is an error condition due to the user's firmware. An SSP interrupt is generated for each data transfer byte. Flag bit SSPIF (PIR1<3>) must be cleared in software. The SSPSTAT register is used to determine the status of the byte.

#### 9.3.2 MASTER MODE

Master mode of operation is supported in firmware using interrupt generation on the detection of the START and STOP conditions. The STOP (P) and START (S) bits are cleared from a RESET or when the SSP module is disabled. The STOP (P) and START (S) bits will toggle based on the START and STOP conditions. Control of the I<sup>2</sup>C bus may be taken when the P bit is set, or the bus is IDLE and both the S and P bits are clear.

In Master mode, the SCL and SDA lines are manipulated by clearing the corresponding TRISC<4:3> bit(s). The output level is always low, irrespective of the value(s) in PORTC<4:3>. So when transmitting data, a '1' data bit must have the TRISC<4> bit set (input) and a '0' data bit must have the TRISC<4> bit cleared (output). The same scenario is true for the SCL line with the TRISC<3> bit. Pull-up resistors must be provided externally to the SCL and SDA pins for proper operation of the I<sup>2</sup>C module.

The following events will cause SSP Interrupt Flag bit, SSPIF, to be set (SSP Interrupt will occur if enabled):

- START condition

- STOP condition

- Data transfer byte transmitted/received

Master mode of operation can be done with either the Slave mode IDLE (SSPM3:SSPM0 = 1011), or with the Slave active. When both Master and Slave modes are enabled, the software needs to differentiate the source(s) of the interrupt.

#### 9.3.3 MULTI-MASTER MODE

In Multi-Master mode, the interrupt generation on the detection of the START and STOP conditions, allows the determination of when the bus is free. The STOP (P) and START (S) bits are cleared from a RESET or when the SSP module is disabled. The STOP (P) and START (S) bits will toggle based on the START and STOP conditions. Control of the  $I^2C$  bus may be taken when bit P (SSPSTAT<4>) is set, or the bus is IDLE and both the S and P bits clear. When the bus is busy, enabling the SSP Interrupt will generate the interrupt when the STOP condition occurs.

In Multi-Master operation, the SDA line must be monitored to see if the signal level is the expected output level. This check only needs to be done when a high level is output. If a high level is expected and a low level is present, the device needs to release the SDA and SCL lines (set TRISC<4:3>). There are two stages where this arbitration can be lost, these are:

- Address Transfer

- Data Transfer

When the slave logic is enabled, the slave continues to receive. If arbitration was lost during the address transfer stage, communication to the device may be in progress. If addressed, an ACK pulse will be generated. If arbitration was lost during the data transfer stage, the device will need to retransfer the data at a later time.

| Address                | Name    | Bit 7                | Bit 6              | Bit 5                  | Bit 4     | Bit 3     | Bit 2       | Bit 1  | Bit 0  | Value on:<br>POR,<br>BOR | Value on<br>all other<br>RESETS |

|------------------------|---------|----------------------|--------------------|------------------------|-----------|-----------|-------------|--------|--------|--------------------------|---------------------------------|

| 0Bh, 8Bh,<br>10Bh,18Bh | INTCON  | GIE                  | PEIE               | TMR0IE                 | INTE      | RBIE      | TMR0IF      | INTF   | RBIF   | 0000 000x                | 0000 000u                       |

| 0Ch                    | PIR1    | PSPIF <sup>(1)</sup> | ADIF               | RCIF                   | TXIF      | SSPIF     | CCP1IF      | TMR2IF | TMR1IF | 0000 0000                | 0000 0000                       |

| 8Ch                    | PIE1    | PSPIE <sup>(1)</sup> | ADIE               | RCIE                   | TXIE      | SSPIE     | CCP1IE      | TMR2IE | TMR1IE | 0000 0000                | 0000 0000                       |

| 13h                    | SSPBUF  | Synchrono            | us Serial          | Port Rece              | eive Buff | er/Transn | nit Registe | ər     |        | xxxx xxxx                | uuuu uuuu                       |

| 93h                    | SSPADD  | Synchrono            | us Serial          | Port (I <sup>2</sup> C | mode) A   | ddress R  | egister     |        |        | 0000 0000                | 0000 0000                       |

| 14h                    | SSPCON  | WCOL                 | SSPOV              | SSPEN                  | CKP       | SSPM3     | SSPM2       | SSPM1  | SSPM0  | 0000 0000                | 0000 0000                       |

| 94h                    | SSPSTAT | SMP <sup>(2)</sup>   | CKE <sup>(2)</sup> | D/A                    | Р         | S         | R/W         | UA     | BF     | 0000 0000                | 0000 0000                       |

| 87h                    | TRISC   | PORTC Da             | ata Direct         | •                      | 1111 1111 | 1111 1111 |             |        |        |                          |                                 |

TABLE 9-3:

REGISTERS ASSOCIATED WITH I<sup>2</sup>C OPERATION

Legend: x = unknown, u = unchanged, - = unimplemented locations read as '0'. Shaded cells are not used by SSP module in I<sup>2</sup>C mode. **Note 1:** PSPIF and PSPIE are reserved on the PIC16F73/76; always maintain these bits clear.

2: Maintain these bits clear in I<sup>2</sup>C mode.

| Address                | Name   | Bit 7                | Bit 6                        | Bit 5   | Bit 4 | Bit 3 | Bit 2  | Bit 1  | Bit 0  | Value on:<br>POR,<br>BOR | Value on<br>all other<br>RESETS |

|------------------------|--------|----------------------|------------------------------|---------|-------|-------|--------|--------|--------|--------------------------|---------------------------------|

| 0Bh, 8Bh,<br>10Bh,18Bh | INTCON | GIE                  | PEIE                         | TMR0IE  | INTE  | RBIE  | TMR0IF | INTF   | RBIF   | 0000 000x                | 0000 000u                       |

| 0Ch                    | PIR1   | PSPIF <sup>(1)</sup> | ADIF                         | RCIF    | TXIF  | SSPIF | CCP1IF | TMR2IF | TMR1IF | 0000 0000                | 0000 0000                       |

| 18h                    | RCSTA  | SPEN                 | RX9                          | SREN    | CREN  | ADDEN | FERR   | OERR   | RX9D   | 0000 000x                | 0000 000x                       |

| 19h                    | TXREG  | USART Tr             | ansmit R                     | egister |       |       |        |        |        | 0000 0000                | 0000 0000                       |

| 8Ch                    | PIE1   | PSPIE <sup>(1)</sup> | ADIE                         | RCIE    | TXIE  | SSPIE | CCP1IE | TMR2IE | TMR1IE | 0000 0000                | 0000 0000                       |

| 98h                    | TXSTA  | CSRC                 | TX9                          | TXEN    | SYNC  | —     | BRGH   | TRMT   | TX9D   | 0000 -010                | 0000 -010                       |

| 99h                    | SPBRG  | Baud Rate            | Baud Rate Generator Register |         |       |       |        |        |        |                          | 0000 0000                       |

Legend: x = unknown, - = unimplemented, read as '0'. Shaded cells are not used for synchronous slave transmission.

Note 1: Bits PSPIE and PSPIF are reserved on the PIC16F73/76 devices; always maintain these bits clear.

#### 10.4.2 USART SYNCHRONOUS SLAVE RECEPTION

The operation of the Synchronous Master and Slave modes is identical, except in the case of the SLEEP mode. Bit SREN is a "don't care" in Slave mode.

If receive is enabled by setting bit CREN prior to the SLEEP instruction, then a word may be received during SLEEP. On completely receiving the word, the RSR register will transfer the data to the RCREG register and if enable bit RCIE bit is set, the interrupt generated will wake the chip from SLEEP. If the global interrupt is enabled, the program will branch to the interrupt vector (0004h).

Follow these steps when setting up a Synchronous Slave Reception:

- Enable the synchronous master serial port by setting bits SYNC and SPEN and clearing bit CSRC.

- 2. If interrupts are desired, set enable bit RCIE.

- 3. If 9-bit reception is desired, set bit RX9.

- 4. To enable reception, set enable bit CREN.

- 5. Flag bit RCIF will be set when reception is complete and an interrupt will be generated, if enable bit RCIE was set.

- Read the RCSTA register to get the ninth bit (if enabled) and determine if any error occurred during reception.

- 7. Read the 8-bit received data by reading the RCREG register.

- 8. If any error occurred, clear the error by clearing bit CREN.

- 9. If using interrupts, ensure that GIE and PEIE in the INTCON register are set.

| Address                | Name   | Bit 7                | Bit 6    | Bit 5        | Bit 4 | Bit 3 | Bit 2  | Bit 1  | Bit 0  | Value on:<br>POR,<br>BOR | Value on<br>all other<br>RESETS |

|------------------------|--------|----------------------|----------|--------------|-------|-------|--------|--------|--------|--------------------------|---------------------------------|

| 0Bh, 8Bh,<br>10Bh,18Bh | INTCON | GIE                  | PEIE     | TMR0IE       | INTE  | RBIE  | TMR0IF | INTF   | RBIF   | 0000 000x                | 0000 000u                       |

| 0Ch                    | PIR1   | PSPIF <sup>(1)</sup> | ADIF     | RCIF         | TXIF  | SSPIF | CCP1IF | TMR2IF | TMR1IF | 0000 0000                | 0000 0000                       |

| 18h                    | RCSTA  | SPEN                 | RX9      | SREN         | CREN  | ADDEN | FERR   | OERR   | RX9D   | 0000 000x                | 0000 000x                       |

| 1Ah                    | RCREG  | USART R              | eceive R | egister      |       |       |        |        |        | 0000 0000                | 0000 0000                       |

| 8Ch                    | PIE1   | PSPIE <sup>(1)</sup> | ADIE     | RCIE         | TXIE  | SSPIE | CCP1IE | TMR2IE | TMR1IE | 0000 0000                | 0000 0000                       |

| 98h                    | TXSTA  | CSRC                 | TX9      | TXEN         | SYNC  | _     | BRGH   | TRMT   | TX9D   | 0000 -010                | 0000 -010                       |

| 99h                    | SPBRG  | Baud Rate            | e Genera | ator Registe | er    |       |        |        |        | 0000 0000                | 0000 0000                       |

#### TABLE 10-10: REGISTERS ASSOCIATED WITH SYNCHRONOUS SLAVE RECEPTION

Legend: x = unknown, - = unimplemented, read as '0'. Shaded cells are not used for synchronous slave reception. Note 1: Bits PSPIE and PSPIF are reserved on the PIC16F73/76 devices, always maintain these bits clear.

| U-0      | U-0 | U-0           | U-0                        | U-0       | U-0      | U-0       | R/P-1        | U-0    | R/P-1    | R/P-1        | R/P-1 | R/P-1 | R/P-1 |

|----------|-----|---------------|----------------------------|-----------|----------|-----------|--------------|--------|----------|--------------|-------|-------|-------|

| _        |     |               |                            | _         |          |           | BOREN        | _      | CP0      | PWRTEN       | WDTEN | FOSC1 | FOSC0 |

| bit13    |     |               |                            |           |          |           |              |        |          |              |       |       | bit0  |

|          |     |               |                            |           |          |           |              |        |          |              |       |       |       |

| bit 13-7 |     | Unimp         | lemente                    | d: Read   | as '1'   |           |              |        |          |              |       |       |       |

| bit 6    |     | BORE          | : Browr                    | out Re    | set Ena  | ble bit   |              |        |          |              |       |       |       |

|          |     | 1 = BO        | R enable                   | ed        |          |           |              |        |          |              |       |       |       |

|          |     | 0 <b>= BO</b> | R disabl                   | ed        |          |           |              |        |          |              |       |       |       |

| bit 5    |     | Unimp         | Unimplemented: Read as '1' |           |          |           |              |        |          |              |       |       |       |

| bit 4    |     | <b>CP0:</b> F | LASH P                     | rogram I  | Memory   | Code F    | Protection b | oit    |          |              |       |       |       |

|          |     | 1 = Coo       | de prote                   | ction off |          |           |              |        |          |              |       |       |       |

|          |     | 0 = All I     | memory                     | location  | s code   | protecte  | d            |        |          |              |       |       |       |

| bit 3    |     | PWRTE         | EN: Pow                    | er-up Ti  | mer Ena  | able bit  |              |        |          |              |       |       |       |

|          |     | 1 = PW        | /RT disa                   | bled      |          |           |              |        |          |              |       |       |       |

|          |     | 0 = PW        | RT enab                    | oled      |          |           |              |        |          |              |       |       |       |

| bit 2    |     | WDTE          | N: Watch                   | ndog Tim  | er Enal  | ole bit   |              |        |          |              |       |       |       |

|          |     | 1 = WD        | T enabl                    | ed        |          |           |              |        |          |              |       |       |       |

|          |     | 0 = WD        | )T disabl                  | ed        |          |           |              |        |          |              |       |       |       |

| bit 1-0  |     | FOSC1         | :FOSCO                     | : Oscilla | tor Sele | ection bi | ts           |        |          |              |       |       |       |

|          |     | 11 = R0       | C oscilla                  | tor       |          |           |              |        |          |              |       |       |       |

|          |     |               | S oscilla                  |           |          |           |              |        |          |              |       |       |       |

|          |     |               | T oscillat                 |           |          |           |              |        |          |              |       |       |       |

|          |     | 00 = LF       | oscillat                   | or        |          |           |              |        |          |              |       |       |       |

|          |     |               |                            |           |          |           |              |        |          |              |       |       |       |

|          |     | Note          | 1. The                     | erased    | lunnroc  | iramme    | d) value of  | the co | onfigura | tion word is | 3FFFh |       |       |

# REGISTER 12-1: CONFIGURATION WORD (ADDRESS 2007h)<sup>(1)</sup>

Note 1: The erased (unprogrammed) value of the configuration word is 3FFFh.

| Legend:                       |                      |                                     |

|-------------------------------|----------------------|-------------------------------------|

| R = Readable bit              | P = Programmable bit | U = Unimplemented bit, read as '0'  |

| - n = Value when device is ur | nprogrammed          | u = Unchanged from programmed state |

| Register   |    | Dev | ices |    | Power-on Reset,<br>Brown-out Reset | MCLR Reset,<br>WDT Reset | Wake-up via WDT or<br>Interrupt |  |

|------------|----|-----|------|----|------------------------------------|--------------------------|---------------------------------|--|

| W          | 73 | 74  | 76   | 77 | xxxx xxxx                          | uuuu uuuu                | uuuu uuuu                       |  |

| INDF       | 73 | 74  | 76   | 77 | N/A                                | N/A                      | N/A                             |  |

| TMR0       | 73 | 74  | 76   | 77 | XXXX XXXX                          | uuuu uuuu                | uuuu uuuu                       |  |

| PCL        | 73 | 74  | 76   | 77 | 0000h                              | 0000h                    | PC + 1 <sup>(2)</sup>           |  |

| STATUS     | 73 | 74  | 76   | 77 | 0001 1xxx                          | 000q quuu <b>(3)</b>     | uuuq quuu <b>(3)</b>            |  |

| FSR        | 73 | 74  | 76   | 77 | xxxx xxxx                          | uuuu uuuu                | uuuu uuuu                       |  |

| PORTA      | 73 | 74  | 76   | 77 | 0x 0000                            | 0u 0000                  | uu uuuu                         |  |

| PORTB      | 73 | 74  | 76   | 77 | XXXX XXXX                          | uuuu uuuu                | uuuu uuuu                       |  |

| PORTC      | 73 | 74  | 76   | 77 | XXXX XXXX                          | uuuu uuuu                | uuuu uuuu                       |  |

| PORTD      | 73 | 74  | 76   | 77 | XXXX XXXX                          | uuuu uuuu                | uuuu uuuu                       |  |

| PORTE      | 73 | 74  | 76   | 77 | xxx                                | uuu                      | uuu                             |  |

| PCLATH     | 73 | 74  | 76   | 77 | 0 0000                             | 0 0000                   | u uuuu                          |  |

| INTCON     | 73 | 74  | 76   | 77 | 0000 000x                          | 0000 000u                | uuuu uuuu <b>(1)</b>            |  |

| PIR1       | 73 | 74  | 76   | 77 | r000 0000                          | r000 0000                | ruuu uuuu <b>(1)</b>            |  |

|            | 73 | 74  | 76   | 77 | 0000 0000                          | 0000 0000                | uuuu uuuu <b>(1)</b>            |  |

| PIR2       | 73 | 74  | 76   | 77 | 0                                  | 0                        | u(1)                            |  |

| TMR1L      | 73 | 74  | 76   | 77 | XXXX XXXX                          | uuuu uuuu                | uuuu uuuu                       |  |

| TMR1H      | 73 | 74  | 76   | 77 | XXXX XXXX                          | uuuu uuuu                | uuuu uuuu                       |  |

| T1CON      | 73 | 74  | 76   | 77 | 00 0000                            | uu uuuu                  | uu uuuu                         |  |

| TMR2       | 73 | 74  | 76   | 77 | 0000 0000                          | 0000 0000                | uuuu uuuu                       |  |

| T2CON      | 73 | 74  | 76   | 77 | -000 0000                          | -000 0000                | -uuu uuuu                       |  |

| SSPBUF     | 73 | 74  | 76   | 77 | XXXX XXXX                          | uuuu uuuu                | uuuu uuuu                       |  |

| SSPCON     | 73 | 74  | 76   | 77 | 0000 0000                          | 0000 0000                | uuuu uuuu                       |  |

| CCPR1L     | 73 | 74  | 76   | 77 | XXXX XXXX                          | uuuu uuuu                | uuuu uuuu                       |  |

| CCPR1H     | 73 | 74  | 76   | 77 | XXXX XXXX                          | uuuu uuuu                | uuuu uuuu                       |  |

| CCP1CON    | 73 | 74  | 76   | 77 | 00 0000                            | 00 0000                  | uu uuuu                         |  |

| RCSTA      | 73 | 74  | 76   | 77 | 0000 -00x                          | 0000 -00x                | uuuu -uuu                       |  |

| TXREG      | 73 | 74  | 76   | 77 | 0000 0000                          | 0000 0000                | uuuu uuuu                       |  |

| RCREG      | 73 | 74  | 76   | 77 | 0000 0000                          | 0000 0000                | uuuu uuuu                       |  |

| CCPR2L     | 73 | 74  | 76   | 77 | XXXX XXXX                          | uuuu uuuu                | uuuu uuuu                       |  |

| CCPR2H     | 73 | 74  | 76   | 77 | XXXX XXXX                          | uuuu uuuu                | uuuu uuuu                       |  |

| CCP2CON    | 73 | 74  | 76   | 77 | 0000 0000                          | 0000 0000                | uuuu uuuu                       |  |

| ADRES      | 73 | 74  | 76   | 77 | XXXX XXXX                          | uuuu uuuu                | uuuu uuuu                       |  |

| ADCON0     | 73 | 74  | 76   | 77 | 0000 00-0                          | 0000 00-0                | uuuu uu-u                       |  |

| OPTION_REG | 73 | 74  | 76   | 77 | 1111 1111                          | 1111 1111                | uuuu uuuu                       |  |

| TRISA      | 73 | 74  | 76   | 77 | 11 1111                            | 11 1111                  | uu uuuu                         |  |

| TRISB      | 73 | 74  | 76   | 77 | 1111 1111                          | 1111 1111                | uuuu uuuu                       |  |

| TRISC      | 73 | 74  | 76   | 77 | 1111 1111                          | 1111 1111                | uuuu uuuu                       |  |

| TRISD      | 73 | 74  | 76   | 77 | 1111 1111                          | 1111 1111                | uuuu uuuu                       |  |

| TRISE      | 73 | 74  | 76   | 77 | 0000 -111                          | 0000 -111                | uuuu -uuu                       |  |

| PIE1       | 73 | 74  | 76   | 77 | r000 0000                          | r000 0000                | ruuu uuuu                       |  |

|            | 73 | 74  | 76   | 77 | 0000 0000                          | 0000 0000                | uuuu uuuu                       |  |

#### TABLE 12-6: INITIALIZATION CONDITIONS FOR ALL REGISTERS

Legend: u = unchanged, x = unknown, - = unimplemented bit, read as '0', q = value depends on condition, r = reserved, maintain clear

Note 1: One or more bits in INTCON, PIR1 and/or PIR2 will be affected (to cause wake-up).

2: When the wake-up is due to an interrupt and the GIE bit is set, the PC is loaded with the interrupt vector (0004h).

**3:** See Table 12-5 for RESET value for specific condition.

#### 12.11.1 INT INTERRUPT

External interrupt on the RB0/INT pin is edge triggered, either rising, if bit INTEDG (OPTION\_REG<6>) is set, or falling, if the INTEDG bit is clear. When a valid edge appears on the RB0/INT pin, flag bit INTF (INTCON<1>) is set. This interrupt can be disabled by clearing enable bit INTE (INTCON<4>). Flag bit INTF must be cleared in software in the Interrupt Service Routine before re-enabling this interrupt. The INT interrupt can wake-up the processor from SLEEP, if bit INTE was set prior to going into SLEEP. The status of global interrupt enable bit GIE decides whether or not the processor branches to the interrupt vector following wakeup. See Section 12.14 for details on SLEEP mode.

#### 12.11.2 TMR0 INTERRUPT

An overflow (FFh  $\rightarrow$  00h) in the TMR0 register will set flag bit TMR0IF (INTCON<2>). The interrupt can be enabled/disabled by setting/clearing enable bit TMR0IE (INTCON<5>). (Section 5.0)

#### 12.11.3 PORTB INTCON CHANGE

An input change on PORTB<7:4> sets flag bit RBIF (INTCON<0>). The interrupt can be enabled/disabled by setting/clearing enable bit RBIE (INTCON<4>), see Section 4.2.

# 12.12 Context Saving During Interrupts

During an interrupt, only the return PC value is saved on the stack. Typically, users may wish to save key registers during an interrupt (i.e., W, PCLATH and STA-TUS registers). This will have to be implemented in software, as shown in Example 12-1.

For the PIC16F73/74 devices, the register W\_TEMP must be defined in both banks 0 and 1 and must be defined at the same offset from the bank base address (i.e., If W\_TEMP is defined at 20h in bank 0, it must also be defined at A0h in bank 1.). The registers, PCLATH\_TEMP and STATUS\_TEMP, are only defined in bank 0.

Since the upper 16 bytes of each bank are common in the PIC16F76/77 devices, temporary holding registers W\_TEMP, STATUS\_TEMP and PCLATH\_TEMP should be placed in here. These 16 locations don't require banking and, therefore, make it easier for context save and restore. The same code shown in Example 12-1 can be used.

|       | LIZ-I. SAVING S          | TATUS, W, AND FCEATH REGISTERS IN RAM                   |

|-------|--------------------------|---------------------------------------------------------|

| MOVWF | W_TEMP                   | ;Copy W to TEMP register                                |

| SWAPF | STATUS,W                 | ;Swap status to be saved into W                         |

| CLRF  | STATUS                   | ;bank 0, regardless of current bank, Clears IRP,RP1,RP0 |

| MOVWF | STATUS_TEMP              | ;Save status to bank zero STATUS_TEMP register          |

| MOVF  | PCLATH, W                | ;Only required if using pages 1, 2 and/or 3             |

| MOVWF | F PCLATH_TEMP            | ;Save PCLATH into W                                     |

| CLRF  | PCLATH                   | ;Page zero, regardless of current page                  |

| :     |                          |                                                         |

| :(ISR | 2)                       | ;Insert user code here                                  |

| :     |                          |                                                         |

| MOVF  | PCLATH_TEMP, W           | ;Restore PCLATH                                         |

| MOVWF | 7 PCLATH                 | ;Move W into PCLATH                                     |

| SWAPF | <pre>STATUS_TEMP,W</pre> | ;Swap STATUS_TEMP register into W                       |

|       |                          | ;(sets bank to original state)                          |

| MOVWF | r status                 | ;Move W into STATUS register                            |

| SWAPF | F W_TEMP,F               | ;Swap W_TEMP                                            |

| SWAPF | F W_TEMP,W               | ;Swap W_TEMP into W                                     |

|       |                          |                                                         |

#### EXAMPLE 12-1: SAVING STATUS, W, AND PCLATH REGISTERS IN RAM

NOTES:

# PIC16F7X

| SWAPF            | Swap Nibbles in f                                                                                                                                                  |

|------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [label] SWAPF f,d                                                                                                                                                  |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ d \in \ [0,1] \end{array}$                                                                                                  |

| Operation:       | $(f<3:0>) \rightarrow (destination<7:4>), (f<7:4>) \rightarrow (destination<3:0>)$                                                                                 |

| Status Affected: | None                                                                                                                                                               |

| Description:     | The upper and lower nibbles of register 'f' are exchanged. If 'd' is 0, the result is placed in the W register. If 'd' is 1, the result is placed in register 'f'. |

| XORWF            | Exclusive OR W with f                                                                                                                                                       |

|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [label] XORWF f,d                                                                                                                                                           |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ d \in \left[0,1\right] \end{array}$                                                                                                  |

| Operation:       | (W) .XOR. (f) $\rightarrow$ (destination)                                                                                                                                   |

| Status Affected: | Z                                                                                                                                                                           |

| Description:     | Exclusive OR the contents of the W register with register 'f'. If 'd' is 0, the result is stored in the W register. If 'd' is 1, the result is stored back in register 'f'. |

| XORLW            | Exclusive OR Literal with W                                                                                                |

|------------------|----------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [ <i>label</i> ] XORLW k                                                                                                   |

| Operands:        | $0 \le k \le 255$                                                                                                          |

| Operation:       | (W) .XOR. $k \rightarrow (W)$                                                                                              |

| Status Affected: | Z                                                                                                                          |

| Description:     | The contents of the W register<br>are XOR'ed with the eight-bit<br>literal 'k'. The result is placed in<br>the W register. |

# 14.13 PICDEM 3 Low Cost PIC16CXXX Demonstration Board

The PICDEM 3 demonstration board is a simple demonstration board that supports the PIC16C923 and PIC16C924 in the PLCC package. It will also support future 44-pin PLCC microcontrollers with an LCD Module. All the necessary hardware and software is included to run the basic demonstration programs. The user can program the sample microcontrollers provided with the PICDEM 3 demonstration board on a PRO MATE II device programmer, or a PICSTART Plus development programmer with an adapter socket, and easily test firmware. The MPLAB ICE in-circuit emulator may also be used with the PICDEM 3 demonstration board to test firmware. A prototype area has been provided to the user for adding hardware and connecting it to the microcontroller socket(s). Some of the features include a RS-232 interface, push button switches, a potentiometer for simulated analog input, a thermistor and separate headers for connection to an external LCD module and a keypad. Also provided on the PICDEM 3 demonstration board is a LCD panel, with 4 commons and 12 segments, that is capable of displaying time, temperature and day of the week. The PICDEM 3 demonstration board provides an additional RS-232 interface and Windows software for showing the demultiplexed LCD signals on a PC. A simple serial interface allows the user to construct a hardware demultiplexer for the LCD signals.

# 14.14 PICDEM 17 Demonstration Board

The PICDEM 17 demonstration board is an evaluation board that demonstrates the capabilities of several Microchip microcontrollers, including PIC17C752, PIC17C756A, PIC17C762 and PIC17C766. All necessary hardware is included to run basic demo programs, which are supplied on a 3.5-inch disk. A programmed sample is included and the user may erase it and program it with the other sample programs using the PRO MATE II device programmer, or the PICSTART Plus development programmer, and easily debug and test the sample code. In addition, the PICDEM 17 demonstration board supports downloading of programs to and executing out of external FLASH memory on board. The PICDEM 17 demonstration board is also usable with the MPLAB ICE in-circuit emulator, or the PICMASTER emulator and all of the sample programs can be run and modified using either emulator. Additionally, a generous prototype area is available for user hardware.

# 14.15 KEELOQ Evaluation and Programming Tools

KEELOQ evaluation and programming tools support Microchip's HCS Secure Data Products. The HCS evaluation kit includes a LCD display to show changing codes, a decoder to decode transmissions and a programming interface to program test transmitters.

# **15.0 ELECTRICAL CHARACTERISTICS**

#### Absolute Maximum Ratings †

| Ambient temperature under bias                                                                                                                                         | 55 to +125°C                          |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------|

| Storage temperature                                                                                                                                                    |                                       |

| Voltage on any pin with respect to Vss (except VDD, MCLR. and RA4)                                                                                                     |                                       |

| Voltage on VDD with respect to Vss                                                                                                                                     |                                       |

| Voltage on MCLR with respect to Vss (Note 2)                                                                                                                           |                                       |

| Voltage on RA4 with respect to Vss                                                                                                                                     |                                       |

| Total power dissipation (Note 1)                                                                                                                                       |                                       |

| Maximum current out of Vss pin                                                                                                                                         |                                       |

| Maximum current into VDD pin                                                                                                                                           |                                       |

| Input clamp current, Iк (Vi < 0 or Vi > VDD)                                                                                                                           |                                       |

| Output clamp current, loк (Vo < 0 or Vo > Voo)                                                                                                                         |                                       |

| Maximum output current sunk by any I/O pin                                                                                                                             |                                       |

| Maximum output current sourced by any I/O pin                                                                                                                          |                                       |

| Maximum current sunk by PORTA, PORTB, and PORTE (combined) (Note 3)                                                                                                    | 200 mA                                |

| Maximum current sourced by PORTA, PORTB, and PORTE (combined) (Note 3)                                                                                                 |                                       |

| Maximum current sunk by PORTC and PORTD (combined) (Note 3)                                                                                                            | 200 mA                                |

| Maximum current sourced by PORTC and PORTD (combined) (Note 3)                                                                                                         |                                       |

| <b>Note 1:</b> Power dissipation is calculated as follows: Pdis = VDD x {IDD - $\sum$ IOH} + $\sum$ {(VDD - V                                                          | $√$ ОН) x IOH} + $\Sigma$ (VOI x IOL) |

| <ol> <li>Voltage spikes at the MCLR pin may cause latchup. A series resistor of greater the to pull MCLR to VDD, rather than tying the pin directly to VDD.</li> </ol> | nan 1 k $\Omega$ should be used       |

3: PORTD and PORTE are not implemented on the PIC16F73/76 devices.

† NOTICE: Stresses above those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress rating only and functional operation of the device at those or any other conditions above those indicated in the operation listings of this specification is not implied. Exposure to maximum rating conditions for extended periods may affect device reliability.

# PIC16F7X

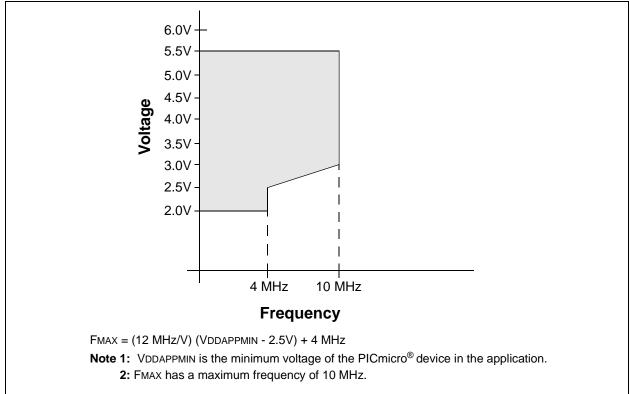

## FIGURE 15-2: PIC16LF7X VOLTAGE-FREQUENCY GRAPH

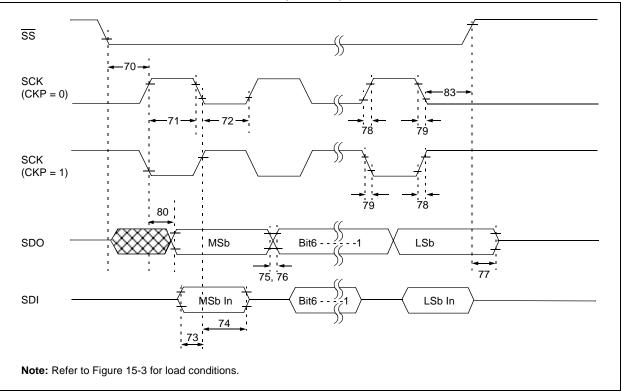

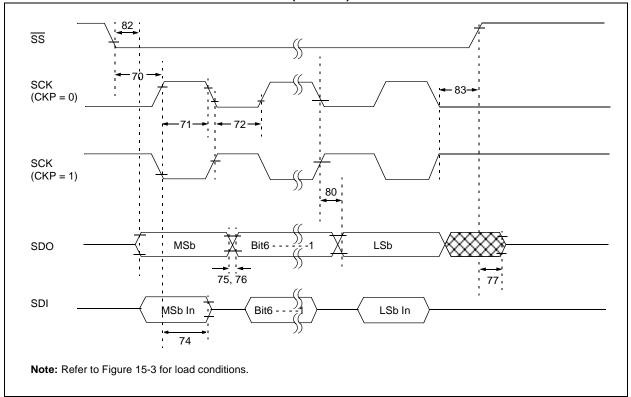

# FIGURE 15-14: SPI SLAVE MODE TIMING (CKE = 1)

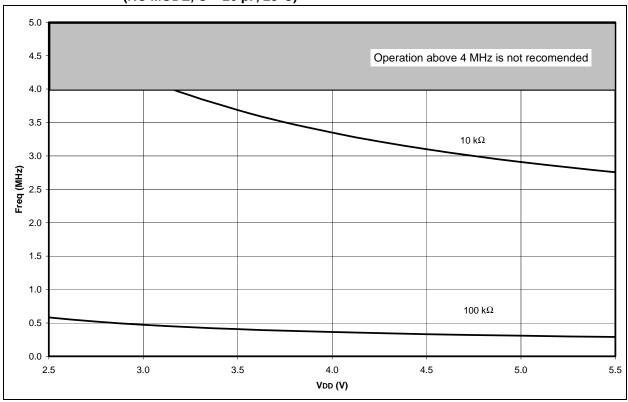

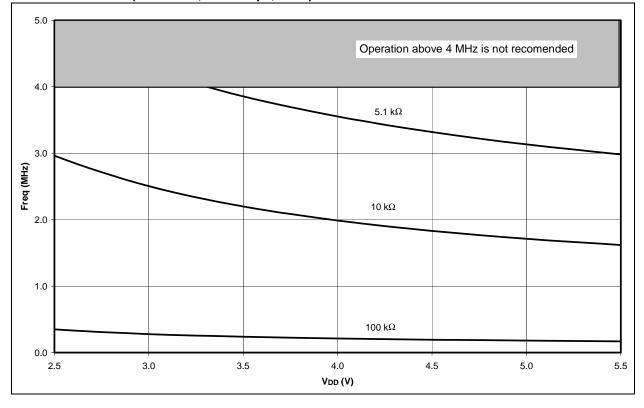

## FIGURE 16-7: AVERAGE FOSC vs. VDD FOR VARIOUS VALUES OF R (RC MODE, C = 20 pF, 25°C)

FIGURE 16-8: AVERAGE Fosc vs. VDD FOR VARIOUS VALUES OF R (RC MODE, C = 100 pF, 25°C)

# Package Marking Information (Cont'd)

#### 44-Lead TQFP

Example

Ο

PIC16F77-I/P

0210017

## 44-Lead PLCC

Example

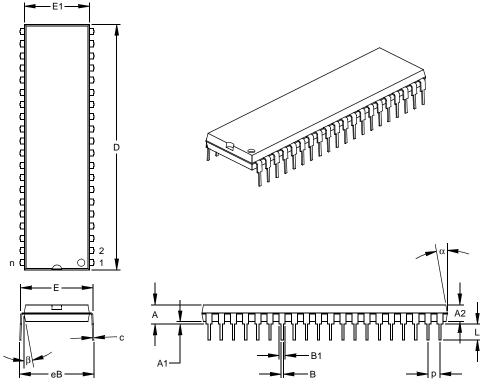

# 40-Lead Plastic Dual In-line (P) - 600 mil (PDIP)

| Units    |                                                                                     | INCHES*                                                                                                                                                                                                                                                                                                                                                       |                                                        | MILLIMETERS                                            |                                                        |                                                        |  |

|----------|-------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------|--------------------------------------------------------|--------------------------------------------------------|--------------------------------------------------------|--|

| n Limits | MIN                                                                                 | NOM                                                                                                                                                                                                                                                                                                                                                           | MAX                                                    | MIN                                                    | NOM                                                    | MAX                                                    |  |

| n        |                                                                                     | 40                                                                                                                                                                                                                                                                                                                                                            |                                                        |                                                        | 40                                                     |                                                        |  |

| р        |                                                                                     | .100                                                                                                                                                                                                                                                                                                                                                          |                                                        |                                                        | 2.54                                                   |                                                        |  |

| Α        | .160                                                                                | .175                                                                                                                                                                                                                                                                                                                                                          | .190                                                   | 4.06                                                   | 4.45                                                   | 4.83                                                   |  |

| A2       | .140                                                                                | .150                                                                                                                                                                                                                                                                                                                                                          | .160                                                   | 3.56                                                   | 3.81                                                   | 4.06                                                   |  |

| A1       | .015                                                                                |                                                                                                                                                                                                                                                                                                                                                               |                                                        | 0.38                                                   |                                                        |                                                        |  |

| Е        | .595                                                                                | .600                                                                                                                                                                                                                                                                                                                                                          | .625                                                   | 15.11                                                  | 15.24                                                  | 15.88                                                  |  |

| E1       | .530                                                                                | .545                                                                                                                                                                                                                                                                                                                                                          | .560                                                   | 13.46                                                  | 13.84                                                  | 14.22                                                  |  |

| D        | 2.045                                                                               | 2.058                                                                                                                                                                                                                                                                                                                                                         | 2.065                                                  | 51.94                                                  | 52.26                                                  | 52.45                                                  |  |

| L        | .120                                                                                | .130                                                                                                                                                                                                                                                                                                                                                          | .135                                                   | 3.05                                                   | 3.30                                                   | 3.43                                                   |  |

| С        | .008                                                                                | .012                                                                                                                                                                                                                                                                                                                                                          | .015                                                   | 0.20                                                   | 0.29                                                   | 0.38                                                   |  |

| B1       | .030                                                                                | .050                                                                                                                                                                                                                                                                                                                                                          | .070                                                   | 0.76                                                   | 1.27                                                   | 1.78                                                   |  |

| В        | .014                                                                                | .018                                                                                                                                                                                                                                                                                                                                                          | .022                                                   | 0.36                                                   | 0.46                                                   | 0.56                                                   |  |

| eB       | .620                                                                                | .650                                                                                                                                                                                                                                                                                                                                                          | .680                                                   | 15.75                                                  | 16.51                                                  | 17.27                                                  |  |

| α        | 5                                                                                   | 10                                                                                                                                                                                                                                                                                                                                                            | 15                                                     | 5                                                      | 10                                                     | 15                                                     |  |

| β        | 5                                                                                   | 10                                                                                                                                                                                                                                                                                                                                                            | 15                                                     | 5                                                      | 10                                                     | 15                                                     |  |

|          | n Limits<br>n<br>P<br>A<br>A2<br>A1<br>E<br>E1<br>D<br>L<br>c<br>B1<br>B<br>eB<br>α | n Limits         MIN           n            p            A         .160           A2         .140           A1         .015           E         .595           E1         .530           D         2.045           L         .120           c         .008           B1         .030           B         .014           eB         .620           α         5 | $\begin{array}{c c c c c c c c c c c c c c c c c c c $ | $\begin{array}{c c c c c c c c c c c c c c c c c c c $ | $\begin{array}{c c c c c c c c c c c c c c c c c c c $ | $\begin{array}{c c c c c c c c c c c c c c c c c c c $ |  |

\* Controlling Parameter § Significant Characteristic

Notes:

Dimensions D and E1 do not include mold flash or protrusions. Mold flash or protrusions shall not exceed .010" (0.254mm) per side. JEDEC Equivalent: MO-011

Drawing No. C04-016

| PORTE Register                          |      |        | . 37 |

|-----------------------------------------|------|--------|------|

| Postscaler, WDT                         |      |        |      |

| Assignment (PSA bit)                    |      |        |      |

| Rate Select (PS2:PS0 bits)              |      |        | . 20 |

| Power-down Mode. See SLEEP              |      |        |      |

| Power-on Reset (POR)89,                 |      |        |      |

| Oscillator Start-up Timer (OST)         |      | 89,    | 94   |

| POR Status (POR bit)                    |      |        | .25  |

| Power Control (PCON) Register           |      |        | . 95 |

| Power-down (PD bit)                     |      |        | .93  |

| Power-up Timer (PWRT)                   |      | 89,    | 94   |

| Time-out (TO bit)                       |      |        |      |

| PR2 Register                            |      |        | .51  |

| Prescaler, Timer0                       |      |        |      |

| Assignment (PSA bit)                    |      |        | .20  |

| Rate Select (PS2:PS0 bits)              |      |        |      |

| PRO MATE II Universal Device Programmer |      |        |      |

| Program Counter                         |      |        |      |

| RESET Conditions                        |      |        | . 95 |

| Program Memory                          |      |        |      |

| Associated Registers                    |      |        |      |

| Interrupt Vector                        |      |        | .13  |

| Memory and Stack Maps                   |      |        |      |

| Operation During Code Protect           |      |        |      |

| Organization                            |      |        |      |

| Paging                                  |      |        |      |

| PMADR Register                          |      |        |      |

| PMADRH Register                         |      |        |      |

| Reading FLASH                           |      |        |      |

| Reading, PMADR Register                 |      |        |      |

| Reading, PMADRH Register                |      |        |      |

| Reading, PMCON1 Register                |      |        |      |

| Reading, PMDATA Register                |      |        |      |

| Reading, PMDATH Register                |      |        |      |

| RESET Vector                            |      |        |      |

| Program Verification                    |      |        |      |

| Programming Pin (VPP)                   |      |        |      |

| Programming, Device Instructions        |      |        |      |

| PUSH                                    |      |        |      |

|                                         |      |        |      |

| R                                       |      |        |      |

| R/W bit                                 | .60. | 66.    | 67   |

|                                         |      | ο<br>Ω |      |

| RA0/AN0 Pin          | 8, | 10 |

|----------------------|----|----|

| RA1/AN1 Pin          | 8, | 10 |

| RA2/AN2 Pin          | 8, | 10 |

| RA3/AN3/VREF Pin     | 8, | 10 |

| RA4/T0CKI Pin        |    |    |

| RA5/SS/AN4 Pin       |    |    |

| RAM. See Data Memory | í  |    |

| RB0/INT Pin          | 9, | 11 |

| RB1 Pin              | 9, | 11 |

| RB2 Pin              |    |    |

| RB3/PGM Pin          | 9, | 11 |

| RB4 Pin              | 9, | 11 |

| RB5 Pin              | 9, | 11 |

| RB6/PGC Pin          | 9, | 11 |

| RB7/PGD Pin          | 9, | 11 |

| RC0/T1OSO/T1CKI Pin  | 9, | 11 |

| RC1/T1OSI/CCP2 Pin   |    |    |

| RC2/CCP1 Pin         |    |    |