Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                                         |

|----------------------------|-------------------------------------------------------------------------|

| Product Status             | Active                                                                  |

| Core Processor             | PIC                                                                     |

| Core Size                  | 8-Bit                                                                   |

| Speed                      | 20MHz                                                                   |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                                       |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                   |

| Number of I/O              | 33                                                                      |

| Program Memory Size        | 7KB (4K x 14)                                                           |

| Program Memory Type        | FLASH                                                                   |

| EEPROM Size                | -                                                                       |

| RAM Size                   | 192 x 8                                                                 |

| Voltage - Supply (Vcc/Vdd) | 4V ~ 5.5V                                                               |

| Data Converters            | A/D 8x8b                                                                |

| Oscillator Type            | External                                                                |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                       |

| Mounting Type              | Surface Mount                                                           |

| Package / Case             | 44-LCC (J-Lead)                                                         |

| Supplier Device Package    | 44-PLCC (16.59x16.59)                                                   |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16f74t-i-l |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### Note the following details of the code protection feature on PICmicro® MCUs.

- The PICmicro family meets the specifications contained in the Microchip Data Sheet.

- Microchip believes that its family of PICmicro microcontrollers is one of the most secure products of its kind on the market today, when used in the intended manner and under normal conditions.

- There are dishonest and possibly illegal methods used to breach the code protection feature. All of these methods, to our knowledge, require using the PICmicro microcontroller in a manner outside the operating specifications contained in the data sheet. The person doing so may be engaged in theft of intellectual property.

- Microchip is willing to work with the customer who is concerned about the integrity of their code.

- Neither Microchip nor any other semiconductor manufacturer can guarantee the security of their code. Code protection does not

mean that we are guaranteeing the product as "unbreakable".

- Code protection is constantly evolving. We at Microchip are committed to continuously improving the code protection features of our product.

If you have any further questions about this matter, please contact the local sales office nearest to you.

Information contained in this publication regarding device applications and the like is intended through suggestion only and may be superseded by updates. It is your responsibility to ensure that your application meets with your specifications. No representation or warranty is given and no liability is assumed by Microchip Technology Incorporated with respect to the accuracy or use of such information, or infringement of patents or other intellectual property rights arising from such use or otherwise. Use of Microchip's products as critical components in life support systems is not authorized except with express written approval by Microchip. No licenses are conveyed, implicitly or otherwise, under any intellectual property rights.

#### **Trademarks**

The Microchip name and logo, the Microchip logo, FilterLab, KEELOQ, MPLAB, PIC, PICmicro, PICMASTER, PICSTART, PRO MATE, SEEVAL and The Embedded Control Solutions Company are registered trademarks of Microchip Technology Incorporated in the U.S.A. and other countries.

dsPIC, ECONOMONITOR, FanSense, FlexROM, fuzzyLAB, In-Circuit Serial Programming, ICSP, ICEPIC, microID, microPort, Migratable Memory, MPASM, MPLIB, MPLINK, MPSIM, MXDEV, PICC, PICDEM, PICDEM.net, rfPIC, Select Mode and Total Endurance are trademarks of Microchip Technology Incorporated in the U.S.A.

Serialized Quick Term Programming (SQTP) is a service mark of Microchip Technology Incorporated in the U.S.A.

All other trademarks mentioned herein are property of their respective companies.

© 2002, Microchip Technology Incorporated, Printed in the U.S.A., All Rights Reserved.

Microchip received QS-9000 quality system certification for its worldwide headquarters, design and wafer fabrication facilities in Chandler and Tempe, Arizona in July 1999. The Company's quality system processes and procedures are QS-9000 compliant for its PICmicro® 8-bit MCUs, KEELO® code hopping devices, Serial EEPROMs and microperipheral products. In addition, Microchip's quality system for the design and manufacture of development systems is ISO 9001 certified.

### PIC16F7X

#### Table of Contents

| 1.0   | Device Overview                                                 | 5   |

|-------|-----------------------------------------------------------------|-----|

| 2.0   | Memory Organization                                             | 13  |

| 3.0   | Reading Program Memory                                          |     |

| 4.0   | I/O Ports                                                       | 31  |

| 5.0   | Timer0 Module                                                   | 43  |

| 6.0   | Timer1 Module                                                   | 47  |

| 7.0   | Timer2 Module                                                   | 51  |

| 8.0   | Capture/Compare/PWM Modules                                     | 53  |

| 9.0   | Synchronous Serial Port (SSP) Module                            | 59  |

| 10.0  | Universal Synchronous Asynchronous Receiver Transmitter (USART) | 69  |

| 11.0  | Analog-to-Digital Converter (A/D) Module                        | 83  |

| 12.0  | Special Features of the CPU                                     | 89  |

| 13.0  | Instruction Set Summary                                         | 105 |

| 14.0  | Development Support                                             | 113 |

| 15.0  | Electrical Characteristics                                      | 119 |

| 16.0  | DC and AC Characteristics Graphs and Tables                     | 141 |

| 17.0  | Packaging Information                                           | 151 |

| Appe  | ndix A: Revision History                                        |     |

| Appe  | ndix B: Device Differences                                      | 161 |

| Appe  | ndix C: Conversion Considerations                               | 162 |

| Index |                                                                 | 163 |

| On-Li | ne Support                                                      | 169 |

|       | er Response                                                     |     |

| PIC16 | SF7X Product Identification System                              | 171 |

#### TO OUR VALUED CUSTOMERS

It is our intention to provide our valued customers with the best documentation possible to ensure successful use of your Microchip products. To this end, we will continue to improve our publications to better suit your needs. Our publications will be refined and enhanced as new volumes and updates are introduced.

If you have any questions or comments regarding this publication, please contact the Marketing Communications Department via E-mail at **docerrors@mail.microchip.com** or fax the **Reader Response Form** in the back of this data sheet to (480) 792-4150. We welcome your feedback.

#### **Most Current Data Sheet**

To obtain the most up-to-date version of this data sheet, please register at our Worldwide Web site at:

http://www.microchip.com

You can determine the version of a data sheet by examining its literature number found on the bottom outside corner of any page. The last character of the literature number is the version number, (e.g., DS30000A is version A of document DS30000).

#### **Errata**

An errata sheet, describing minor operational differences from the data sheet and recommended workarounds, may exist for current devices. As device/documentation issues become known to us, we will publish an errata sheet. The errata will specify the revision of silicon and revision of document to which it applies.

To determine if an errata sheet exists for a particular device, please check with one of the following:

- Microchip's Worldwide Web site; http://www.microchip.com

- Your local Microchip sales office (see last page)

- The Microchip Corporate Literature Center; U.S. FAX: (480) 792-7277

When contacting a sales office or the literature center, please specify which device, revision of silicon and data sheet (include literature number) you are using.

#### **Customer Notification System**

Register on our web site at www.microchip.com/cn to receive the most current information on all of our products.

#### 2.2.2.1 STATUS Register

The STATUS register contains the arithmetic status of the ALU, the RESET status and the bank select bits for data memory.

The STATUS register can be the destination for any instruction, as with any other register. If the STATUS register is the destination for an instruction that affects the Z, DC, or C bits, then the write to these three bits is disabled. These bits are set or cleared according to the device logic. Furthermore, the  $\overline{\text{TO}}$  and  $\overline{\text{PD}}$  bits are not writable, therefore, the result of an instruction with the STATUS register as destination may be different than intended.

For example, CLRF STATUS will clear the upper three bits and set the Z bit. This leaves the STATUS register as 000u uluu (where u = unchanged).

It is recommended, therefore, that only BCF, BSF, SWAPF and MOVWF instructions are used to alter the STATUS register, because these instructions do not affect the Z, C, or DC bits from the STATUS register. For other instructions not affecting any status bits, see the "Instruction Set Summary."

Note 1: The C and DC bits operate as a borrow and digit borrow bit, respectively, in subtraction. See the SUBLW and SUBWF instructions for examples.

### REGISTER 2-1: STATUS REGISTER (ADDRESS 03h, 83h, 103h, 183h)

| R/W-0 | R/W-0 | R/W-0 | R-1 | R-1 | R/W-x | R/W-x | R/W-x |

|-------|-------|-------|-----|-----|-------|-------|-------|

| IRP   | RP1   | RP0   | TO  | PD  | Z     | DC    | С     |

| bit 7 |       |       |     |     |       |       | bit 0 |

bit 7 IRP: Register Bank Select bit (used for indirect addressing)

1 = Bank 2, 3 (100h - 1FFh)

0 = Bank 0, 1 (00h - FFh)

bit 6-5 RP1:RP0: Register Bank Select bits (used for direct addressing)

11 = Bank 3 (180h - 1FFh)

10 = Bank 2 (100h - 17Fh)

01 = Bank 1 (80h - FFh)

00 = Bank 0 (00h - 7Fh)

Each bank is 128 bytes

bit 4 **TO**: Time-out bit

1 = After power-up, CLRWDT instruction, or SLEEP instruction

0 = A WDT time-out occurred

bit 3 **PD**: Power-down bit

1 = After power-up or by the CLRWDT instruction

${\tt 0}$  = By execution of the  ${\tt SLEEP}$  instruction

bit 2 z: Zero bit

1 = The result of an arithmetic or logic operation is zero

0 = The result of an arithmetic or logic operation is not zero

bit 1 DC: Digit carry/borrow bit (ADDWF, ADDLW, SUBLW, SUBWF instructions)

1 = A carry-out from the 4th low order bit of the result occurred

0 = No carry-out from the 4th low order bit of the result

bit 0 C: Carry/borrow bit (ADDWF, ADDLW, SUBLW, SUBWF instructions)

1 = A carry-out from the Most Significant bit of the result occurred

0 = No carry-out from the Most Significant bit of the result occurred

**Note:** For borrow, the polarity is reversed. A subtraction is executed by adding the two's complement of the second operand. For rotate (RRF, RLF) instructions, this bit is loaded with either the high or low order bit of the source register.

Legend:

R = Readable bit

W = Writable bit

U = Unimplemented bit, read as '0'

n = Value at POR reset

'1' = Bit is set

'0' = Bit is cleared

x = Bit is unknown

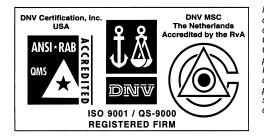

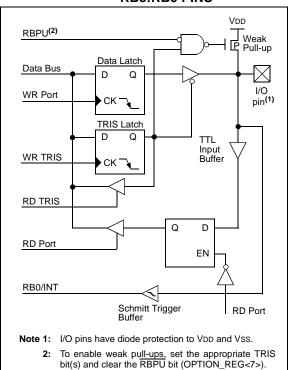

#### 4.2 **PORTB** and the TRISB Register

PORTB is an 8-bit wide, bi-directional port. The corresponding data direction register is TRISB. Setting a TRISB bit (= '1') will make the corresponding PORTB pin an input (i.e., put the corresponding output driver in a Hi-Impedance mode). Clearing a TRISB bit (= '0') will make the corresponding PORTB pin an output (i.e., put the contents of the output latch on the selected pin).

Each of the PORTB pins has a weak internal pull-up. A single control bit can turn on all the pull-ups. This is performed by clearing bit RBPU (OPTION\_REG<7>). The weak pull-up is automatically turned off when the port pin is configured as an output. The pull-ups are disabled on a Power-on Reset.

**BLOCK DIAGRAM OF** FIGURE 4-3: RB3:RB0 PINS

Four of the PORTB pins (RB7:RB4) have an interrupt-on-change feature. Only pins configured as inputs can cause this interrupt to occur (i.e., any RB7:RB4 pin configured as an output is excluded from the interrupt-on-change comparison). The input pins (of RB7:RB4) are compared with the old value latched on the last read of PORTB. The "mismatch" outputs of RB7:RB4 are ORed together to generate the RB Port Change Interrupt with flag bit RBIF (INTCON<0>).

This interrupt can wake the device from SLEEP. The user, in the Interrupt Service Routine, can clear the interrupt in the following manner:

- Any read or write of PORTB. This will end the mismatch condition.

- Clear flag bit RBIF.

A mismatch condition will continue to set flag bit RBIF. Reading PORTB will end the mismatch condition and allow flag bit RBIF to be cleared.

The interrupt-on-change feature is recommended for wake-up on key depression operation and operations where PORTB is only used for the interrupt-on-change feature. Polling of PORTB is not recommended while using the interrupt-on-change feature.

This interrupt on mismatch feature, together with software configureable pull-ups on these four pins, allow easy interface to a keypad and make it possible for wake-up on key depression. Refer to the Embedded Control Handbook, "Implementing Wake-up on Key Stroke" (AN552).

RB0/INT is an external interrupt input pin and is configured using the INTEDG bit (OPTION\_REG<6>).

RB0/INT is discussed in detail in Section 12.11.1.

FIGURE 4-4: **BLOCK DIAGRAM OF RB7:RB4 PINS**

and clear the RBPU bit (OPTION\_REG<7>).

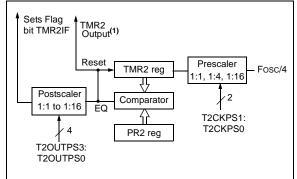

#### 7.0 TIMER2 MODULE

Timer2 is an 8-bit timer with a prescaler and a postscaler. It can be used as the PWM time-base for the PWM mode of the CCP module(s). The TMR2 register is readable and writable, and is cleared on any device RESET.

The input clock (Fosc/4) has a prescale option of 1:1, 1:4 or 1:16, selected by control bits T2CKPS1:T2CKPS0 (T2CON<1:0>).

The Timer2 module has an 8-bit period register, PR2. Timer2 increments from 00h until it matches PR2 and then resets to 00h on the next increment cycle. PR2 is a readable and writable register. The PR2 register is initialized to FFh upon RESET.

The match output of TMR2 goes through a 4-bit postscaler (which gives a 1:1 to 1:16 scaling inclusive) to generate a TMR2 interrupt (latched in flag bit TMR2IF, (PIR1<1>)).

Timer2 can be shut-off by clearing control bit TMR2ON (T2CON<2>) to minimize power consumption.

Register 7-1 shows the Timer2 control register.

Additional information on timer modules is available in the PICmicro™ Mid-Range MCU Family Reference Manual (DS33023).

#### 7.1 Timer2 Prescaler and Postscaler

The prescaler and postscaler counters are cleared when any of the following occurs:

- · a write to the TMR2 register

- · a write to the T2CON register

- any device RESET (POR, MCLR Reset, WDT Reset or BOR)

TMR2 is not cleared when T2CON is written.

#### 7.2 Output of TMR2

The output of TMR2 (before the postscaler) is fed to the SSP module, which optionally uses it to generate shift clock.

#### FIGURE 7-1: TIMER2 BLOCK DIAGRAM

**Note 1:** TMR2 register output can be software selected by the SSP module as a baud clock.

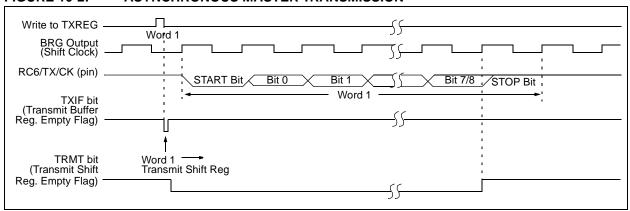

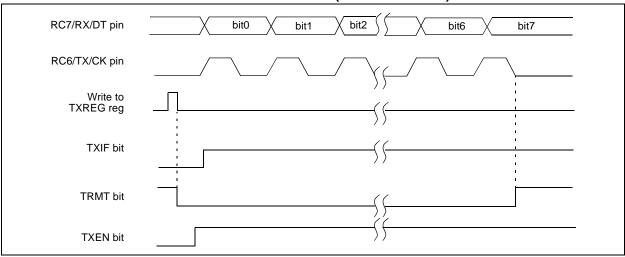

Steps to follow when setting up an Asynchronous Transmission:

- 1. Initialize the SPBRG register for the appropriate baud rate. If a high speed baud rate is desired, set bit BRGH (Section 10.1).

- Enable the asynchronous serial port by clearing bit SYNC and setting bit SPEN.

- 3. If interrupts are desired, then set enable bit TXIE.

- If 9-bit transmission is desired, then set transmit bit TX9.

- Enable the transmission by setting bit TXEN, which will also set bit TXIF.

- If 9-bit transmission is selected, the ninth bit should be loaded in bit TX9D.

- 7. Load data to the TXREG register (starts transmission).

- If using interrupts, ensure that GIE and PEIE in the INTCON register are set.

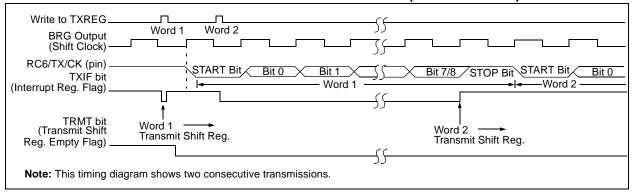

#### FIGURE 10-2: ASYNCHRONOUS MASTER TRANSMISSION

### FIGURE 10-3: ASYNCHRONOUS MASTER TRANSMISSION (BACK TO BACK)

#### TABLE 10-5: REGISTERS ASSOCIATED WITH ASYNCHRONOUS TRANSMISSION

| Address                | Name   | Bit 7                | Bit 6     | Bit 5      | Bit 4 | Bit 3 | Bit 2  | Bit 1  | Bit 0  | Value or<br>POR,<br>BOR | 1:  | Value of<br>all othe<br>RESET | er  |

|------------------------|--------|----------------------|-----------|------------|-------|-------|--------|--------|--------|-------------------------|-----|-------------------------------|-----|

| 0Bh, 8Bh,<br>10Bh,18Bh | INTCON | GIE                  | PEIE      | TMR0IE     | INTE  | RBIE  | TMR0IF | INTF   | RBIF   | 0000 00                 | Эx  | 0000 00                       | 00u |

| 0Ch                    | PIR1   | PSPIF <sup>(1)</sup> | ADIF      | RCIF       | TXIF  | SSPIF | CCP1IF | TMR2IF | TMR1IF | 0000 00                 | 00  | 0000 00                       | 000 |

| 18h                    | RCSTA  | SPEN                 | RX9       | SREN       | CREN  | _     | FERR   | OERR   | RX9D   | 0000 -0                 | Οx  | 0000 -0                       | 00x |

| 19h                    | TXREG  | USART Tra            | ansmit Re | egister    |       |       |        |        |        | 0000 00                 | 0.0 | 0000 00                       | 000 |

| 8Ch                    | PIE1   | PSPIE <sup>(1)</sup> | ADIE      | RCIE       | TXIE  | SSPIE | CCP1IE | TMR2IE | TMR1IE | 0000 00                 | 0.0 | 0000 00                       | 000 |

| 98h                    | TXSTA  | CSRC                 | TX9       | TXEN       | SYNC  | _     | BRGH   | TRMT   | TX9D   | 0000 -0                 | 10  | 0000 -0                       | 010 |

| 99h                    | SPBRG  | Baud Rate            | Generate  | or Registe | r     |       |        |        |        | 0000 00                 | 00  | 0000 00                       | 000 |

Legend: x = unknown, - = unimplemented locations read as '0'. Shaded cells are not used for asynchronous transmission.

Note 1: Bits PSPIE and PSPIF are reserved on the PIC16F73/76; always maintain these bits clear.

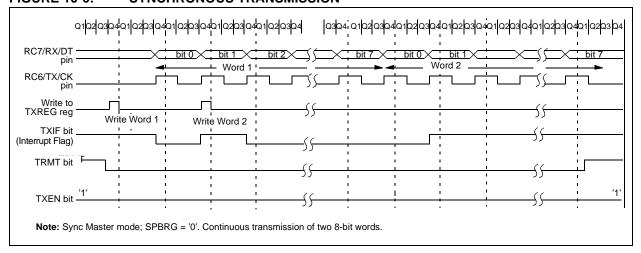

FIGURE 10-6: SYNCHRONOUS TRANSMISSION

FIGURE 10-7: SYNCHRONOUS TRANSMISSION (THROUGH TXEN)

TABLE 10-7: REGISTERS ASSOCIATED WITH SYNCHRONOUS MASTER TRANSMISSION

| Address                | Name   | Bit 7                | Bit 6    | Bit 5      | Bit 4 | Bit 3     | Bit 2     | Bit 1  | Bit 0  | Value on:<br>POR,<br>BOR | Value on<br>all other<br>RESETS |

|------------------------|--------|----------------------|----------|------------|-------|-----------|-----------|--------|--------|--------------------------|---------------------------------|

| 0Bh, 8Bh,<br>10Bh,18Bh | INTCON | GIE                  | PEIE     | TMR0IE     | INTE  | RBIE      | TMR0IF    | INTF   | RBIF   | 0000 000x                | 0000 000u                       |

| 0Ch                    | PIR1   | PSPIF <sup>(1)</sup> | ADIF     | RCIF       | TXIF  | SSPIF     | CCP1IF    | TMR2IF | TMR1IF | 0000 0000                | 0000 0000                       |

| 18h                    | RCSTA  | SPEN                 | RX9      | SREN       | CREN  | _         | FERR      | OERR   | RX9D   | 0000 -00x                | 0000 -00x                       |

| 19h                    | TXREG  | USART Tr             | ansmit R | egister    |       |           |           |        |        | 0000 0000                | 0000 0000                       |

| 8Ch                    | PIE1   | PSPIE <sup>(1)</sup> | ADIE     | RCIE       | TXIE  | SSPIE     | CCP1IE    | TMR2IE | TMR1IE | 0000 0000                | 0000 0000                       |

| 98h                    | TXSTA  | CSRC                 | TX9      | TXEN       | SYNC  | _         | BRGH      | TRMT   | TX9D   | 0000 -010                | 0000 -010                       |

| 99h                    | SPBRG  | Baud Rate            | Generat  | or Registe |       | 0000 0000 | 0000 0000 |        |        |                          |                                 |

Legend: x = unknown, - = unimplemented, read as '0'. Shaded cells are not used for synchronous master transmission.

Note 1: Bits PSPIE and PSPIF are reserved on the PIC16F73/76 devices; always maintain these bits clear.

#### TABLE 10-8: REGISTERS ASSOCIATED WITH SYNCHRONOUS MASTER RECEPTION

| Address                | Name   | Bit 7                | Bit 6     | Bit 5      | Bit 4 | Bit 3     | Bit 2     | Bit 1  | Bit 0  | Value on:<br>POR, BOR | Value on<br>all other<br>RESETS |

|------------------------|--------|----------------------|-----------|------------|-------|-----------|-----------|--------|--------|-----------------------|---------------------------------|

| 0Bh, 8Bh,<br>10Bh,18Bh | INTCON | GIE                  | PEIE      | TMR0IE     | INTE  | RBIE      | TMR0IF    | INTF   | RBIF   | 0000 000x             | 0000 000u                       |

| 0Ch                    | PIR1   | PSPIF <sup>(1)</sup> | ADIF      | RCIF       | TXIF  | SSPIF     | CCP1IF    | TMR2IF | TMR1IF | 0000 0000             | 0000 0000                       |

| 18h                    | RCSTA  | SPEN                 | RX9       | SREN       | CREN  | _         | FERR      | OERR   | RX9D   | 0000 -00x             | 0000 -00x                       |

| 1Ah                    | RCREG  | USART R              | eceive Re | gister     |       |           |           |        |        | 0000 0000             | 0000 0000                       |

| 8Ch                    | PIE1   | PSPIE <sup>(1)</sup> | ADIE      | RCIE       | TXIE  | SSPIE     | CCP1IE    | TMR2IE | TMR1IE | 0000 0000             | 0000 0000                       |

| 98h                    | TXSTA  | CSRC                 | TX9       | TXEN       | SYNC  | _         | BRGH      | TRMT   | TX9D   | 0000 -010             | 0000 -010                       |

| 99h                    | SPBRG  | Baud Rate            | Generate  | or Registe |       | 0000 0000 | 0000 0000 |        |        |                       |                                 |

Legend: x = unknown, - = unimplemented, read as '0'. Shaded cells are not used for synchronous master reception.

Note 1: Bits PSPIE and PSPIF are reserved on the PIC16F73/76 devices; always maintain these bits clear.

#### 10.4 USART Synchronous Slave Mode

Synchronous Slave mode differs from the Master mode, in that the shift clock is supplied externally at the RC6/TX/CK pin (instead of being supplied internally in Master mode). This allows the device to transfer or receive data while in SLEEP mode. Slave mode is entered by clearing bit CSRC (TXSTA<7>).

## 10.4.1 USART SYNCHRONOUS SLAVE TRANSMIT

The operation of the Synchronous Master and Slave modes are identical except in the case of the SLEEP mode.

If two words are written to the TXREG and then the SLEEP instruction is executed, the following will occur:

- a) The first word will immediately transfer to the TSR register and transmit when the master device drives the CK line.

- b) The second word will remain in TXREG register.

- c) Flag bit TXIF will not be set.

- d) When the first word has been shifted out of TSR, the TXREG register will transfer the second word to the TSR and flag bit TXIF will now be set.

- e) If enable bit TXIE is set, the interrupt will wake the chip from SLEEP and if the global interrupt is enabled, the program will branch to the interrupt vector (0004h).

Follow these steps when setting up a Synchronous Slave Transmission:

- Enable the synchronous slave serial port by setting bits SYNC and SPEN and clearing bit CSRC.

- 2. Clear bits CREN and SREN.

- If interrupts are desired, then set enable bit TXIE.

- 4. If 9-bit transmission is desired, then set bit TX9.

- Enable the transmission by setting enable bit TXFN

- If 9-bit transmission is selected, the ninth bit should be loaded in bit TX9D.

- Start transmission by loading data to the TXREG register.

- If using interrupts, ensure that GIE and PEIE in the INTCON register are set.

# 11.0 ANALOG-TO-DIGITAL CONVERTER (A/D) MODULE

The 8-bit analog-to-digital (A/D) converter module has five inputs for the PIC16F73/76 and eight for the PIC16F74/77.

The A/D allows conversion of an analog input signal to a corresponding 8-bit digital number. The output of the sample and hold is the input into the converter, which generates the result via successive approximation. The analog reference voltage is software selectable to either the device's positive supply voltage (VDD), or the voltage level on the RA3/AN3/VREF pin.

The A/D converter has a unique feature of being able to operate while the device is in SLEEP mode. To operate in SLEEP, the A/D conversion clock must be derived from the A/D's internal RC oscillator.

The A/D module has three registers. These registers are:

- A/D Result Register ((ADRES)

- A/D Control Register 0 (ADCON0)

- A/D Control Register 1 ((ADCON1)

The ADCON0 register, shown in Register 11-1, controls the operation of the A/D module. The ADCON1 register, shown in Register 11-2, configures the functions of the port pins. The port pins can be configured as analog inputs (RA3 can also be a voltage reference), or as digital I/O.

Additional information on using the A/D module can be found in the PICmicro™ Mid-Range MCU Family Reference Manual (DS33023) and in Application Note, AN546 (DS00546).

#### REGISTER 11-1: ADCON0 REGISTER (ADDRESS 1Fh)

| R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0   | U-0 | R/W-0 |

|-------|-------|-------|-------|-------|---------|-----|-------|

| ADCS1 | ADCS0 | CHS2  | CHS1  | CHS0  | GO/DONE | _   | ADON  |

| bit 7 |       |       |       |       |         |     | bit 0 |

bit 7-6 ADCS1:ADCS0: A/D Conversion Clock Select bits

00 = Fosc/2

01 = Fosc/8

10 = Fosc/32

11 = FRC (clock derived from the internal A/D module RC oscillator)

bit 5-3 CHS2:CHS0: Analog Channel Select bits

000 = Channel 0 (RA0/AN0)

001 = Channel 1 (RA1/AN1)

010 = Channel 2 (RA2/AN2)

011 = Channel 3 (RA3/AN3)

100 = Channel 4 (RA5/AN4)

101 = Channel 5 (RE0/AN5)(1)

110 = Channel 6 (RE1/AN6)(1)

111 = Channel 7 (RE2/AN7)(1)

bit 2 GO/DONE: A/D Conversion Status bit

If ADON = 1:

- 1 = A/D conversion in progress (setting this bit starts the A/D conversion)

- 0 = A/D conversion not in progress (this bit is automatically cleared by hardware when the A/D conversion is complete)

bit 1 **Unimplemented**: Read as '0'

bit 0 **ADON**: A/D On bit

1 = A/D converter module is operating

0 = A/D converter module is shut-off and consumes no operating current

Note 1: A/D channels 5, 6 and 7 are implemented on the PIC16F74/77 only.

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

- n = Value at POR reset '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

### REGISTER 11-2: ADCON1 REGISTER (ADDRESS 9Fh)

| U-0   | U-0 | U-0 | U-0 | U-0 | R/W-0 | R/W-0 | R/W-0 |

|-------|-----|-----|-----|-----|-------|-------|-------|

| _     | _   | _   | _   | _   | PCFG2 | PCFG1 | PCFG0 |

| bit 7 |     |     |     |     |       |       | bit 0 |

bit 7-3 Unimplemented: Read as '0'

bit 2-0 PCFG2:PCFG0: A/D Port Configuration Control bits

| PCFG2:PCFG0 | RA0 | RA1 | RA2 | RA5 | RA3  | RE0 <sup>(1)</sup> | RE1 <sup>(1)</sup> | RE2 <sup>(1)</sup> | VREF |

|-------------|-----|-----|-----|-----|------|--------------------|--------------------|--------------------|------|

| 000         | Α   | Α   | Α   | Α   | Α    | Α                  | Α                  | Α                  | VDD  |

| 001         | Α   | Α   | Α   | Α   | VREF | Α                  | Α                  | Α                  | RA3  |

| 010         | Α   | Α   | Α   | Α   | Α    | D                  | D                  | D                  | Vdd  |

| 011         | Α   | Α   | Α   | Α   | VREF | D                  | D                  | D                  | RA3  |

| 100         | Α   | Α   | D   | D   | Α    | D                  | D                  | D                  | Vdd  |

| 101         | Α   | Α   | D   | D   | VREF | D                  | D                  | D                  | RA3  |

| 11x         | D   | D   | D   | D   | D    | D                  | D                  | D                  | Vdd  |

A = Analog input D = Digital I/O

Note 1: RE0, RE1 and RE2 are implemented on the PIC16F74/77 only.

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

- n = Value at POR reset '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

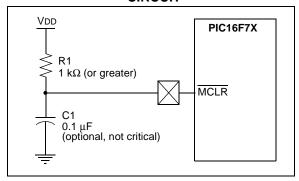

### 12.4 MCLR

PIC16F7X devices have a noise filter in the MCLR Reset path. The filter will detect and ignore small pulses.

It should be noted that a WDT Reset does not drive  $\overline{\text{MCLR}}$  pin low.

The behavior of the ESD protection on the MCLR pin has been altered from previous devices of this family. Voltages applied to the pin that exceed its specification can result in both MCLR Resets and excessive current beyond the device specification during the ESD event. For this reason, Microchip recommends that the MCLR pin no longer be tied directly to VDD. The use of an RC network, as shown in Figure 12-5, is suggested.

FIGURE 12-5: RECOMMENDED MCLR

CIRCUIT

#### 12.5 Power-on Reset (POR)

A Power-on Reset pulse is generated on-chip when VDD rise is detected (in the range of 1.2V - 1.7V). To take advantage of the POR, tie the MCLR pin to VDD as described in Section 12.4. A maximum rise time for VDD is specified. See the Electrical Specifications for details.

When the device starts normal operation (exits the RESET condition), device operating parameters (voltage, frequency, temperature,...) must be met to ensure operation. If these conditions are not met, the device must be held in RESET until the operating conditions are met. For additional information, refer to Application Note, AN607, "Power-up Trouble Shooting" (DS00607).

#### 12.6 Power-up Timer (PWRT)

The Power-up Timer provides a fixed 72 ms nominal time-out on power-up only from the POR. The Power-up Timer operates on an internal RC oscillator. The chip is kept in RESET as long as the PWRT is active. The PWRT's time delay allows VDD to rise to an acceptable level. A configuration bit is provided to enable/ disable the PWRT.

The power-up time delay will vary from chip to chip, due to VDD, temperature and process variation. See DC parameters for details (TPWRT, parameter #33).

### 12.7 Oscillator Start-up Timer (OST)

The Oscillator Start-up Timer (OST) provides 1024 oscillator cycles (from OSC1 input) delay after the PWRT delay is over (if enabled). This helps to ensure that the crystal oscillator or resonator has started and stabilized.

The OST time-out is invoked only for XT, LP and HS modes and only on Power-on Reset, or wake-up from SLEEP.

#### 12.8 Brown-out Reset (BOR)

The configuration bit, BODEN, can enable or disable the Brown-out Reset circuit. If VDD falls below VBOR (parameter D005, about 4V) for longer than TBOR (parameter #35, about 100  $\mu\text{S}$ ), the brown-out situation will reset the device. If VDD falls below VBOR for less than TBOR, a RESET may not occur.

Once the brown-out occurs, the device will remain in Brown-out Reset until VDD rises above VBOR. The Power-up Timer then keeps the device in RESET for TPWRT (parameter #33, about 72 mS). If VDD should fall below VBOR during TPWRT, the Brown-out Reset process will restart when VDD rises above VBOR, with the Power-up Timer Reset. The Power-up Timer is always enabled when the Brown-out Reset circuit is enabled, regardless of the state of the PWRT configuration bit.

#### 12.9 Time-out Sequence

On power-up, the time-out sequence is as follows: the PWRT delay starts (if enabled) when a POR Reset occurs. Then, OST starts counting 1024 oscillator cycles when PWRT ends (LP, XT, HS). When the OST ends, the device comes out of RESET.

If MCLR is kept low long enough, all delays will expire. Bringing MCLR high will begin execution immediately. This is useful for testing purposes or to synchronize more than one PIC16F7X device operating in parallel.

Table 12-5 shows the RESET conditions for the STATUS, PCON and PC registers, while Table 12-6 shows the RESET conditions for all the registers.

## PIC16F7X

TABLE 13-2: PIC16F7X INSTRUCTION SET

| Mnemo  | onic, | Description                  | Cycles  |       | 14-Bit | Opcode | •    | Status   | Notes |  |

|--------|-------|------------------------------|---------|-------|--------|--------|------|----------|-------|--|

| Opera  | ınds  | Description                  | Cycles  | MSb   |        |        | LSb  | Affected | Notes |  |

|        |       | BYTE-ORIENTED FILE REGIS     | TER OPE | RATIO | NS     |        |      |          |       |  |

| ADDWF  | f, d  | Add W and f                  | 1       | 0.0   | 0111   | dfff   | ffff | C,DC,Z   | 1,2   |  |

| ANDWF  | f, d  | AND W with f                 | 1       | 0.0   | 0101   | dfff   | ffff | Z        | 1,2   |  |

| CLRF   | f     | Clear f                      | 1       | 0.0   | 0001   | lfff   | ffff | Z        | 2     |  |

| CLRW   | -     | Clear W                      | 1       | 0.0   | 0001   | 0xxx   | xxxx | Z        |       |  |

| COMF   | f, d  | Complement f                 | 1       | 0.0   | 1001   | dfff   | ffff | Z        | 1,2   |  |

| DECF   | f, d  | Decrement f                  | 1       | 0.0   | 0011   | dfff   | ffff | Z        | 1,2   |  |

| DECFSZ | f, d  | Decrement f, Skip if 0       | 1(2)    | 0.0   | 1011   | dfff   | ffff |          | 1,2,3 |  |

| INCF   | f, d  | Increment f                  | 1       | 0.0   | 1010   | dfff   | ffff | Z        | 1,2   |  |

| INCFSZ | f, d  | Increment f, Skip if 0       | 1(2)    | 0.0   | 1111   | dfff   | ffff |          | 1,2,3 |  |

| IORWF  | f, d  | Inclusive OR W with f        | 1       | 0.0   | 0100   | dfff   | ffff | Z        | 1,2   |  |

| MOVF   | f, d  | Move f                       | 1       | 0.0   | 1000   | dfff   | ffff | Z        | 1,2   |  |

| MOVWF  | f     | Move W to f                  | 1       | 0.0   | 0000   | lfff   | ffff |          |       |  |

| NOP    | -     | No Operation                 | 1       | 0.0   | 0000   | 0xx0   | 0000 |          |       |  |

| RLF    | f, d  | Rotate Left f through Carry  | 1       | 0.0   | 1101   | dfff   | ffff | С        | 1,2   |  |

| RRF    | f, d  | Rotate Right f through Carry | 1       | 0.0   | 1100   | dfff   | ffff | С        | 1,2   |  |

| SUBWF  | f, d  | Subtract W from f            | 1       | 0.0   | 0010   | dfff   | ffff | C,DC,Z   | 1,2   |  |

| SWAPF  | f, d  | Swap nibbles in f            | 1       | 0.0   | 1110   | dfff   | ffff |          | 1,2   |  |

| XORWF  | f, d  | Exclusive OR W with f        | 1       | 00    | 0110   | dfff   | ffff | Z        | 1,2   |  |

|        |       | BIT-ORIENTED FILE REGIST     | ER OPER | ATION | NS .   |        |      |          |       |  |

| BCF    | f, b  | Bit Clear f                  | 1       | 01    | 00bb   | bfff   | ffff |          | 1,2   |  |

| BSF    | f, b  | Bit Set f                    | 1       | 01    | 01bb   | bfff   | ffff |          | 1,2   |  |

| BTFSC  | f, b  | Bit Test f, Skip if Clear    | 1 (2)   | 01    | 10bb   | bfff   | ffff |          | 3     |  |

| BTFSS  | f, b  | Bit Test f, Skip if Set      | 1 (2)   | 01    | 11bb   | bfff   | ffff |          | 3     |  |

|        |       | LITERAL AND CONTROL          | OPERAT  | IONS  |        |        |      |          |       |  |

| ADDLW  | k     | Add literal and W            | 1       | 11    | 111x   | kkkk   | kkkk | C,DC,Z   |       |  |

| ANDLW  | k     | AND literal with W           | 1       | 11    | 1001   | kkkk   | kkkk | Z        |       |  |

| CALL   | k     | Call subroutine              | 2       | 10    | 0kkk   | kkkk   | kkkk |          |       |  |

| CLRWDT | -     | Clear Watchdog Timer         | 1       | 0.0   | 0000   | 0110   | 0100 | TO,PD    |       |  |

| GOTO   | k     | Go to address                | 2       | 10    | 1kkk   | kkkk   | kkkk |          |       |  |

| IORLW  | k     | Inclusive OR literal with W  | 1       | 11    | 1000   | kkkk   | kkkk | Z        |       |  |

| MOVLW  | k     | Move literal to W            | 1       | 11    | 00xx   | kkkk   | kkkk |          |       |  |

| RETFIE | -     | Return from interrupt        | 2       | 0.0   | 0000   | 0000   | 1001 |          |       |  |

| RETLW  | k     | Return with literal in W     | 2       | 11    | 01xx   | kkkk   | kkkk |          |       |  |

| RETURN | -     | Return from Subroutine       | 2       | 0.0   | 0000   | 0000   | 1000 |          |       |  |

| SLEEP  | -     | Go into Standby mode         | 1       | 0.0   | 0000   | 0110   | 0011 | TO,PD    |       |  |

| SUBLW  | k     | Subtract W from literal      | 1       | 11    | 110x   | kkkk   | kkkk | C,DC,Z   |       |  |

| XORLW  | k     | Exclusive OR literal with W  | 1       | 11    | 1010   | kkkk   | kkkk | Z        |       |  |

Note 1: When an I/O register is modified as a function of itself (e.g., MOVF PORTB, 1), the value used will be that value present on the pins themselves. For example, if the data latch is '1' for a pin configured as input and is driven low by an external device, the data will be written back with a '0'.

**Note:** Additional information on the mid-range instruction set is available in the PICmicro™ Mid-Range MCU Family Reference Manual (DS33023).

<sup>2:</sup> If this instruction is executed on the TMR0 register (and, where applicable, d = 1), the prescaler will be cleared if assigned to the Timer0 module.

<sup>3:</sup> If Program Counter (PC) is modified, or a conditional test is true, the instruction requires two cycles. The second cycle is executed as a NOP.

| CALL             | Call Subroutine                                                                                                                                                                                             | CLRWDT           | Clear Watchdog Timer                                                                                                                           |

|------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [label] CALL k                                                                                                                                                                                              | Syntax:          | [label] CLRWDT                                                                                                                                 |

| Operands:        | $0 \leq k \leq 2047$                                                                                                                                                                                        | Operands:        | None                                                                                                                                           |

| Operation:       | (PC)+ 1 $\rightarrow$ TOS,<br>k $\rightarrow$ PC<10:0>,<br>(PCLATH<4:3>) $\rightarrow$ PC<12:11>                                                                                                            | Operation:       | 00h → WDT<br>0 → WDT prescaler,<br>1 → $\overline{TO}$                                                                                         |

| Status Affected: | None                                                                                                                                                                                                        |                  | 1 → PD<br>————————————————————————————————————                                                                                                 |

| Description:     | Call Subroutine. First, return                                                                                                                                                                              | Status Affected: | TO, PD                                                                                                                                         |

|                  | address (PC+1) is pushed onto<br>the stack. The eleven-bit immedi-<br>ate address is loaded into PC bits<br><10:0>. The upper bits of the PC<br>are loaded from PCLATH. CALL is<br>a two-cycle instruction. | Description:     | CLRWDT instruction resets the Watchdog Timer. It also resets the prescaler of the WDT. Status bits TO and PD are set.                          |

| CLRF             | Clear f                                                                                                                                                                                                     | COMF             | Complement f                                                                                                                                   |

| Syntax:          | [label] CLRF f                                                                                                                                                                                              | Syntax:          | [ label ] COMF f,d                                                                                                                             |

| Operands:        | $0 \le f \le 127$                                                                                                                                                                                           | Operands:        | 0 ≤ f ≤ 127                                                                                                                                    |

| Operation:       | $00h \rightarrow (f)$                                                                                                                                                                                       |                  | $d \in [0,1]$                                                                                                                                  |

|                  | $1 \rightarrow Z$                                                                                                                                                                                           | Operation:       | $(\bar{f}) \rightarrow (destination)$                                                                                                          |

| Status Affected: | Z                                                                                                                                                                                                           | Status Affected: | Z                                                                                                                                              |

| Description:     | The contents of register 'f' are cleared and the Z bit is set.                                                                                                                                              | Description:     | The contents of register 'f' are complemented. If 'd' is 0, the result is stored in W. If 'd' is 1, the result is stored back in register 'f'. |

| CLRW             | Clear W                                                                                                                                                                                                     | DECF             | Decrement f                                                                                                                                    |

| Syntax:          | [ label ] CLRW                                                                                                                                                                                              | Syntax:          | [ label ] DECF f,d                                                                                                                             |

| Operands:        | None                                                                                                                                                                                                        | Operands:        | $0 \le f \le 127$                                                                                                                              |

| Operation:       | $00h \rightarrow (W)$                                                                                                                                                                                       |                  | d ∈ [0,1]                                                                                                                                      |

|                  | $1 \rightarrow Z$                                                                                                                                                                                           | Operation:       | (f) - 1 $\rightarrow$ (destination)                                                                                                            |

| Status Affected: | Z                                                                                                                                                                                                           | Status Affected: | Z                                                                                                                                              |

| Description:     | W register is cleared. Zero bit (Z) is set.                                                                                                                                                                 | Description:     | Decrement register 'f'. If 'd' is 0, the result is stored in the W register. If 'd' is 1, the result is                                        |

stored back in register 'f'.

# PIC16F7X

NOTES:

# 15.1 DC Characteristics: PIC16F73/74/76/77 (Industrial, Extended) PIC16LF73/74/76/77 (Industrial) (Continued)

| PIC16L<br>(Indus |                                | 76/77                               | Standard Operating Conditions (unless otherwise stated)<br>Operating temperature $-40^{\circ}\text{C} \le \text{TA} \le +85^{\circ}\text{C}$ for industrial                                                                            |             |          |          |                                                                                       |  |  |  |  |

|------------------|--------------------------------|-------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|----------|----------|---------------------------------------------------------------------------------------|--|--|--|--|

| PIC16F           | <b>73/74/7</b> 0<br>strial, Ex |                                     | Standard Operating Conditions (unless otherwise stated) Operating temperature $-40^{\circ}\text{C} \leq \text{TA} \leq +85^{\circ}\text{C}$ for industrial $-40^{\circ}\text{C} \leq \text{TA} \leq +125^{\circ}\text{C}$ for extended |             |          |          |                                                                                       |  |  |  |  |

| Param<br>No.     | Sym                            | Characteristic                      | Min                                                                                                                                                                                                                                    | Тур†        | Max      | Units    | Conditions                                                                            |  |  |  |  |

|                  | IDD                            | Supply Current (Notes 2, 5          | j)                                                                                                                                                                                                                                     |             |          |          |                                                                                       |  |  |  |  |

| D010             |                                | PIC16LF7X                           | _                                                                                                                                                                                                                                      | 0.4         | 2.0      | mA       | XT, RC osc configuration<br>FOSC = 4 MHz, VDD = 3.0V (Note 4)                         |  |  |  |  |

| D010A            |                                |                                     | _                                                                                                                                                                                                                                      | 20          | 48       | μΑ       | LP osc configuration<br>Fosc = 32 kHz, VDD = 3.0V, WDT disabled                       |  |  |  |  |

| D010             |                                | PIC16F7X                            | -                                                                                                                                                                                                                                      | 0.9         | 4        | mA       | XT, RC osc configuration<br>FOSC = 4 MHz, VDD = 5.5V (Note 4)                         |  |  |  |  |

| D013             |                                |                                     | _                                                                                                                                                                                                                                      | 5.2         | 15       | mA       | HS osc configuration<br>Fosc = 20 MHz, VDD = 5.5V                                     |  |  |  |  |

| D015*            | $\Delta IBOR$                  | Brown-out<br>Reset Current (Note 6) | _                                                                                                                                                                                                                                      | 25          | 200      | μΑ       | BOR enabled, VDD = 5.0V                                                               |  |  |  |  |

| D020             | IPD                            | Power-down Current (Note            | es 3, 5)                                                                                                                                                                                                                               |             | •        |          |                                                                                       |  |  |  |  |

| D021             |                                | PIC16LF7X                           | _<br>_                                                                                                                                                                                                                                 | 2.0<br>0.1  | 30<br>5  | μA<br>μA | VDD = 3.0V, WDT enabled, -40°C to +85°C VDD = 3.0V, WDT disabled, -40°C to +85°C      |  |  |  |  |

| D020<br>D021     |                                | PIC16F7X                            | _<br>_                                                                                                                                                                                                                                 | 5.0<br>0.1  | 42<br>19 | μA<br>μA | VDD = 4.0V, WDT enabled, -40°C to +85°C<br>VDD = 4.0V, WDT disabled, -40°C to +85°C   |  |  |  |  |

| D021A            |                                |                                     | _                                                                                                                                                                                                                                      | 10.5<br>1.5 | 57<br>42 | μΑ<br>μΑ | VDD = 4.0V, WDT enabled, -40°C to +125°C $VDD = 4.0V$ , WDT disabled, -40°C to +125°C |  |  |  |  |

| D023*            | Δlbor                          | Brown-out<br>Reset Current (Note 6) | _                                                                                                                                                                                                                                      | 25          | 200      | μA       | BOR enabled, VDD = 5.0V                                                               |  |  |  |  |

Legend: Shading of rows is to assist in readability of of the table.

- \* These parameters are characterized but not tested.

- † Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

- Note 1: This is the limit to which VDD can be lowered without losing RAM data.

- 2: The supply current is mainly a function of the operating voltage and frequency. Other factors, such as I/O pin loading and switching rate, oscillator type, internal code execution pattern and temperature also have an impact on the current consumption.

The test conditions for all IDD measurements in active operation mode are:

OSC1 = external square wave, from-rail to-rail; all I/O pins tri-stated, pulled to VDD

MCLR = VDD; WDT enabled/disabled as specified.

- 3: The power-down current in SLEEP mode does not depend on the oscillator type. Power-down current is measured with the part in SLEEP mode, with all I/O pins in hi-impedance state and tied to VDD and Vss.

- **4:** For RC osc configuration, current through REXT is not included. The current through the resistor can be estimated by the formula Ir = VDD/2REXT (mA) with REXT in kOhm.

- 5: Timer1 oscillator (when enabled) adds approximately 20 μA to the specification. This value is from characterization and is for design guidance only. This is not tested.

- **6:** The  $\Delta$  current is the additional current consumed when this peripheral is enabled. This current should be added to the base IDD or IPD measurement.

- 7: When BOR is enabled, the device will operate correctly until the VBOR voltage trip point is reached.

# 15.2 DC Characteristics: PIC16F73/74/76/77 (Industrial, Extended) PIC16LF73/74/76/77 (Industrial)

| DC CHARACTERISTICS |                                        |                             | Standard Operating Conditions (unless otherwise stated)  Operating temperature $-40^{\circ}\text{C} \le \text{Ta} \le +85^{\circ}\text{C}$ for industrial $-40^{\circ}\text{C} \le \text{Ta} \le +125^{\circ}\text{C}$ for extended Operating voltage VDD range as described in DC Specification, Section 15.1. |                         |         |    |                                                                        |  |  |  |

|--------------------|----------------------------------------|-----------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------|---------|----|------------------------------------------------------------------------|--|--|--|

| Param<br>No.       | Sym                                    | Characteristic              | Min                                                                                                                                                                                                                                                                                                             | Min Typ† Max Units Cond |         |    | Conditions                                                             |  |  |  |

|                    | VIL                                    | Input Low Voltage           |                                                                                                                                                                                                                                                                                                                 |                         |         |    |                                                                        |  |  |  |

|                    |                                        | I/O ports:                  |                                                                                                                                                                                                                                                                                                                 |                         |         |    |                                                                        |  |  |  |

| D030               |                                        | with TTL buffer             | Vss                                                                                                                                                                                                                                                                                                             | _                       | 0.15VDD | V  | For entire VDD range                                                   |  |  |  |

| D030A              |                                        |                             | Vss                                                                                                                                                                                                                                                                                                             | _                       | 0.8V    | V  | $4.5V \le VDD \le 5.5V$                                                |  |  |  |

| D031               |                                        | with Schmitt Trigger buffer | Vss                                                                                                                                                                                                                                                                                                             | _                       | 0.2Vdd  | V  |                                                                        |  |  |  |

| D032               |                                        | MCLR, OSC1 (in RC mode)     | Vss                                                                                                                                                                                                                                                                                                             | _                       | 0.2Vdd  | V  | (Note 1)                                                               |  |  |  |

| D033               |                                        | OSC1 (in XT and LP mode)    | Vss                                                                                                                                                                                                                                                                                                             | _                       | 0.3V    | V  |                                                                        |  |  |  |

|                    |                                        | OSC1 (in HS mode)           | Vss                                                                                                                                                                                                                                                                                                             |                         | 0.3Vdd  | V  |                                                                        |  |  |  |

|                    | VIH                                    | Input High Voltage          |                                                                                                                                                                                                                                                                                                                 |                         |         |    |                                                                        |  |  |  |

|                    |                                        | I/O ports:                  |                                                                                                                                                                                                                                                                                                                 |                         |         |    |                                                                        |  |  |  |

| D040               |                                        | with TTL buffer             | 2.0                                                                                                                                                                                                                                                                                                             | _                       | VDD     | V  | $4.5V \le VDD \le 5.5V$                                                |  |  |  |

| D040A              |                                        |                             | 0.25VDD<br>+ 0.8V                                                                                                                                                                                                                                                                                               |                         | VDD     | V  | For entire VDD range                                                   |  |  |  |

| D041               |                                        | with Schmitt Trigger buffer | 0.8VDD                                                                                                                                                                                                                                                                                                          | _                       | VDD     | V  | For entire VDD range                                                   |  |  |  |

| D042               |                                        | MCLR                        | 0.8VDD                                                                                                                                                                                                                                                                                                          | _                       | VDD     | V  |                                                                        |  |  |  |

| D042A              |                                        | OSC1 (in XT and LP mode)    | 1.6V                                                                                                                                                                                                                                                                                                            | _                       | VDD     | V  |                                                                        |  |  |  |

|                    |                                        | OSC1 (in HS mode)           | 0.7Vdd                                                                                                                                                                                                                                                                                                          | _                       | VDD     | V  |                                                                        |  |  |  |

| D043               |                                        | OSC1 (in RC mode)           | 0.9Vdd                                                                                                                                                                                                                                                                                                          | _                       | VDD     | V  | (Note 1)                                                               |  |  |  |

| D070               | IPURB                                  | PORTB Weak Pull-up Current  | 50                                                                                                                                                                                                                                                                                                              | 250                     | 400     | μΑ | VDD = 5V, VPIN = VSS                                                   |  |  |  |

|                    | II∟ Input Leakage Current (Notes 2, 3) |                             |                                                                                                                                                                                                                                                                                                                 |                         |         |    |                                                                        |  |  |  |

| D060               |                                        | I/O ports                   | _                                                                                                                                                                                                                                                                                                               | _                       | ±1      | μΑ | Vss ≤ VPIN ≤ VDD, pin at<br>hi-impedance                               |  |  |  |

| D061               |                                        | MCLR, RA4/T0CKI             | _                                                                                                                                                                                                                                                                                                               | _                       | ±5      | μΑ | Vss ≤ Vpin ≤ Vdd                                                       |  |  |  |

| D063               |                                        | OSC1                        | _                                                                                                                                                                                                                                                                                                               |                         | ±5      | μΑ | $Vss \leq VPIN \leq VDD, \ XT, \ HS \ and \ LP \\ osc \ configuration$ |  |  |  |

- \* These parameters are characterized but not tested.

- † Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

- **Note 1:** In RC oscillator configuration, the OSC1/CLKIN pin is a Schmitt Trigger input. It is not recommended that the PIC16F7X be driven with external clock in RC mode.

- 2: The leakage current on the MCLR pin is strongly dependent on the applied voltage level. The specified levels represent normal operating conditions. Higher leakage current may be measured at different input voltages.

- 3: Negative current is defined as current sourced by the pin.

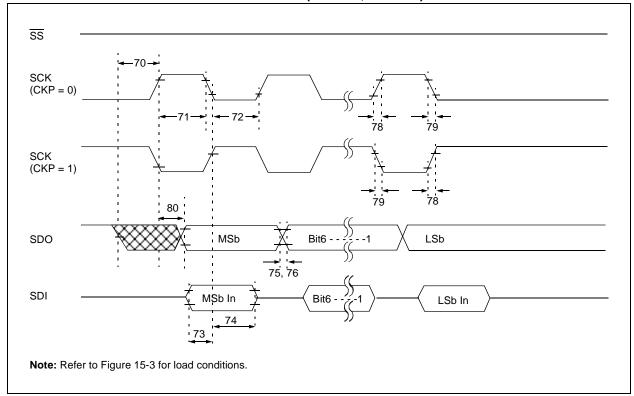

FIGURE 15-11: SPI MASTER MODE TIMING (CKE = 0, SMP = 0)

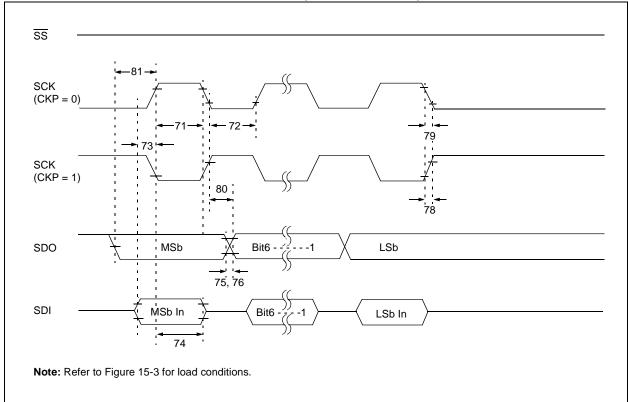

FIGURE 15-12: SPI MASTER MODE TIMING (CKE = 1, SMP = 1)

### Package Marking Information (Cont'd)

#### 40-Lead PDIP

#### Example

44-Lead TQFP

### Example

#### 44-Lead PLCC

#### Example

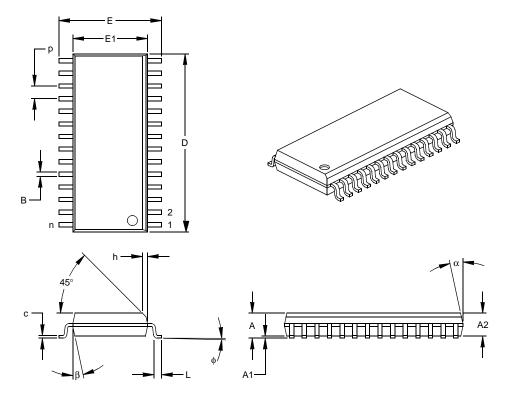

### 28-Lead Plastic Small Outline (SO) - Wide, 300 mil (SOIC)

|                          | Units |      | INCHES* |      | MILLIMETERS |       |       |

|--------------------------|-------|------|---------|------|-------------|-------|-------|

| Dimensio                 | MIN   | NOM  | MAX     | MIN  | NOM         | MAX   |       |

| Number of Pins           | n     |      | 28      |      |             | 28    |       |

| Pitch                    | р     |      | .050    |      |             | 1.27  |       |

| Overall Height           | Α     | .093 | .099    | .104 | 2.36        | 2.50  | 2.64  |

| Molded Package Thickness | A2    | .088 | .091    | .094 | 2.24        | 2.31  | 2.39  |

| Standoff §               | A1    | .004 | .008    | .012 | 0.10        | 0.20  | 0.30  |

| Overall Width            | Е     | .394 | .407    | .420 | 10.01       | 10.34 | 10.67 |

| Molded Package Width     | E1    | .288 | .295    | .299 | 7.32        | 7.49  | 7.59  |

| Overall Length           | D     | .695 | .704    | .712 | 17.65       | 17.87 | 18.08 |

| Chamfer Distance         | h     | .010 | .020    | .029 | 0.25        | 0.50  | 0.74  |

| Foot Length              | L     | .016 | .033    | .050 | 0.41        | 0.84  | 1.27  |

| Foot Angle Top           | ф     | 0    | 4       | 8    | 0           | 4     | 8     |

| Lead Thickness           | С     | .009 | .011    | .013 | 0.23        | 0.28  | 0.33  |

| Lead Width               | В     | .014 | .017    | .020 | 0.36        | 0.42  | 0.51  |

| Mold Draft Angle Top     | α     | 0    | 12      | 15   | 0           | 12    | 15    |

| Mold Draft Angle Bottom  | β     | 0    | 12      | 15   | 0           | 12    | 15    |

Dimensions D and E1 do not include mold flash or protrusions. Mold flash or protrusions shall not exceed

.010" (0.254mm) per side. JEDEC Equivalent: MS-013 Drawing No. C04-052

<sup>\*</sup> Controlling Parameter § Significant Characteristic

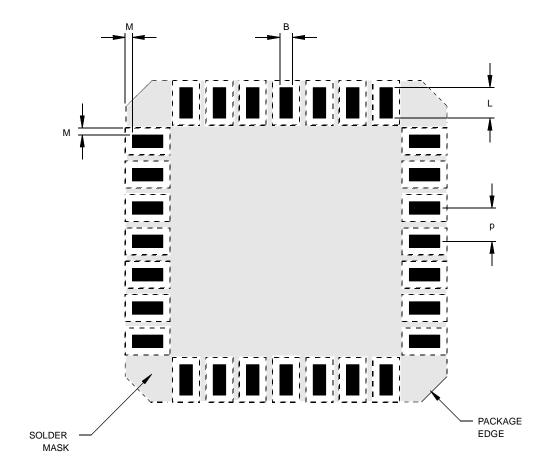

### 28-Lead Plastic Micro Leadframe Package (MF) 6x6 mm Body (MLF) (Continued)

|                    | Unit             | 3 | INCHES   |      |      |      | MILLIMETERS* |      |  |  |

|--------------------|------------------|---|----------|------|------|------|--------------|------|--|--|

|                    | Dimension Limits | М | IIN      | NOM  | MAX  | MIN  | NOM          | MAX  |  |  |

| Pitch              | р                |   | .026 BSC |      |      |      | 0.65 BSC     |      |  |  |

| Pad Width          | В                |   | .009     | .011 | .014 | 0.23 | 0.28         | 0.35 |  |  |

| Pad Length         | L                |   | .020     | .024 | .030 | 0.50 | 0.60         | 0.75 |  |  |

| Pad to Solder Mask |                  |   | .005     |      | .006 | 0.13 |              | 0.15 |  |  |

<sup>\*</sup>Controlling Parameter

Drawing No. C04-2114