Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                   |

|----------------------------|--------------------------------------------------------------------------|

| Core Processor             | PIC                                                                      |

| Core Size                  | 8-Bit                                                                    |

| Speed                      | 20MHz                                                                    |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                                        |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                    |

| Number of I/O              | 33                                                                       |

| Program Memory Size        | 7KB (4K x 14)                                                            |

| Program Memory Type        | FLASH                                                                    |

| EEPROM Size                | -                                                                        |

| RAM Size                   | 192 x 8                                                                  |

| Voltage - Supply (Vcc/Vdd) | 4V ~ 5.5V                                                                |

| Data Converters            | A/D 8x8b                                                                 |

| Oscillator Type            | External                                                                 |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                        |

| Mounting Type              | Surface Mount                                                            |

| Package / Case             | 44-TQFP                                                                  |

| Supplier Device Package    | 44-TQFP (10x10)                                                          |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16f74t-i-pt |

|                            |                                                                          |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

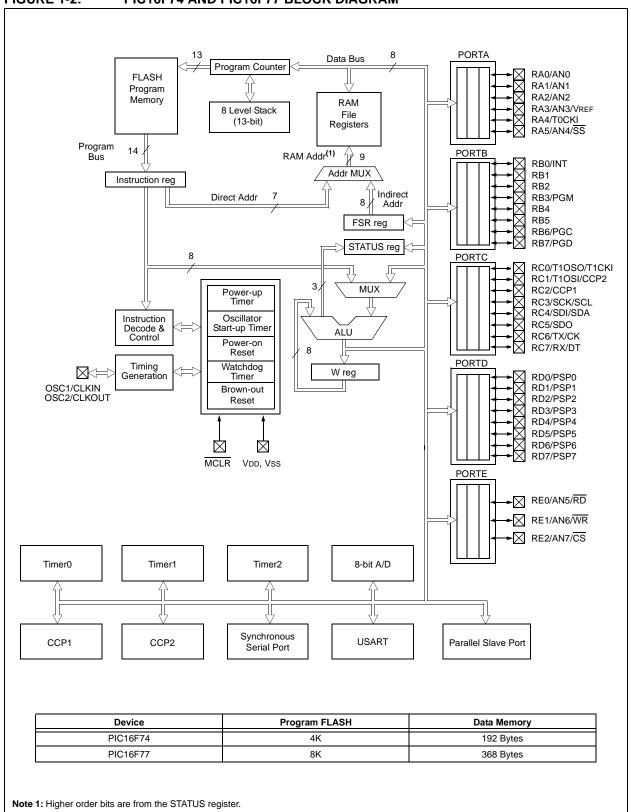

FIGURE 1-2: PIC16F74 AND PIC16F77 BLOCK DIAGRAM

#### PIC16F77/76 REGISTER FILE MAP FIGURE 2-2:

| A                              | File<br>ddress | A                                          | File<br>ddress |                                            | File<br>Address |                                            | File<br>Addres |

|--------------------------------|----------------|--------------------------------------------|----------------|--------------------------------------------|-----------------|--------------------------------------------|----------------|

| Indirect addr.(*)              | 00h            | Indirect addr.(*)                          | 80h            | Indirect addr.(*)                          | 100h            | Indirect addr.(*)                          | 180h           |

| TMR0                           | 01h            | OPTION_REG                                 | 81h            | TMR0                                       | 101h            | OPTION_REG                                 | 181h           |

| PCL                            | 02h            | PCL                                        | 82h            | PCL                                        | 102h            | PCL                                        | 182h           |

| STATUS                         | 03h            | STATUS                                     | 83h            | STATUS                                     | 103h            | STATUS                                     | 183h           |

| FSR                            | 04h            | FSR                                        | 84h            | FSR                                        | 104h            | FSR                                        | 184h           |

| PORTA                          | 05h            | TRISA                                      | 85h            |                                            | 105h            |                                            | 185h           |

| PORTB                          | 06h            | TRISB                                      | 86h            | PORTB                                      | 106h            | TRISB                                      | 186h           |

| PORTC                          | 07h            | TRISC                                      | 87h            |                                            | 107h            |                                            | 187h           |

| PORTD <sup>(1)</sup>           | 08h            | TRISD <sup>(1)</sup>                       | 88h            |                                            | 108h            |                                            | 188h           |

| PORTE <sup>(1)</sup>           | 09h            | TRISE <sup>(1)</sup>                       | 89h            |                                            | 109h            |                                            | 189h           |

| PCLATH                         | 0Ah            | PCLATH                                     | 8Ah            | PCLATH                                     | 10Ah            | PCLATH                                     | 18Ah           |

| INTCON                         | 0Bh            | INTCON                                     | 8Bh            | INTCON                                     | 10Bh            | INTCON                                     | 18Bh           |

| PIR1                           | 0Ch            | PIE1                                       | 8Ch            | PMDATA                                     | 10Ch            | PMCON1                                     | 18Ch           |

| PIR2                           | 0Dh            | PIE2                                       | 8Dh            | PMADR                                      | 10Dh            |                                            | 18Dh           |

| TMR1L                          | 0Eh            | PCON                                       | 8Eh            | PMDATH                                     | 10Eh            |                                            | 18Eh           |

| TMR1H                          | 0Fh            |                                            | 8Fh            | PMADRH                                     | 10Fh            |                                            | 18Fh           |

| T1CON                          | 10h            |                                            | 90h            |                                            | 110h            |                                            | 190h           |

| TMR2                           | 11h            |                                            | 91h            |                                            | 111h            |                                            | 191h           |

| T2CON                          | 12h            | PR2                                        | 92h            |                                            | 112h            |                                            | 192h           |

| SSPBUF                         | 13h            | SSPADD                                     | 93h            |                                            | 113h            |                                            | 193h           |

| SSPCON                         | 14h            | SSPSTAT                                    | 94h            |                                            | 114h            |                                            | 194h           |

| CCPR1L                         | 15h            |                                            | 95h            |                                            | 115h            |                                            | 195h           |

| CCPR1H                         | 16h            |                                            | 96h            |                                            | 116h            |                                            | 196h           |

| CCP1CON                        | 17h            |                                            | 97h            | General                                    | 117h            | General                                    | 197h           |

| RCSTA                          | 18h            | TXSTA                                      | 98h            | Purpose<br>Register                        | 118h            | Purpose<br>Register                        | 198h           |

| TXREG                          | 19h            | SPBRG                                      | 99h            | 16 Bytes                                   | 119h            | 16 Bytes                                   | 199h           |

| RCREG                          | 1Ah            | OF BITO                                    | 9Ah            |                                            | 11Ah            | ,                                          | 19Ah           |

| CCPR2L                         | 1Bh            |                                            | 9Bh            |                                            | 11Bh            |                                            | 19Bh           |

| CCPR2H                         | 1Ch            |                                            | 9Ch            |                                            | 11Ch            |                                            | 19Ch           |

| CCP2CON                        | 1Dh            |                                            | 9Dh            |                                            | 11Dh            |                                            | 19Dh           |

| ADRES                          | 1Eh            |                                            | 9Eh            |                                            | 11Eh            |                                            | 19Eh           |

| ADCON0                         | 1Fh            | ADCON1                                     | 9Fh            |                                            | 11Fh            |                                            | 19Fh           |

| 71200110                       | 20h            | 7.000111                                   |                |                                            | 120h            |                                            |                |

|                                | 2011           |                                            | A0h            |                                            | 12011           |                                            | 1A0h           |

| General<br>Purpose<br>Register |                | General<br>Purpose<br>Register<br>80 Bytes |                | General<br>Purpose<br>Register<br>80 Bytes |                 | General<br>Purpose<br>Register<br>80 Bytes |                |

| 96 Bytes                       |                | accesses                                   | EFh<br>F0h     | accesses                                   | 16Fh<br>170h    | accesses                                   | 1EFh<br>1F0h   |

|                                | 7Fh            | 70h-7Fh                                    | FFh            | 70h-7Fh                                    | 17Fh            | 70h - 7Fh                                  | 1FFh           |

| Bank 0                         |                | Bank 1                                     |                | Bank 2                                     |                 | Bank 3                                     |                |

Unimplemented data memory locations, read as '0'. \* Not a physical register.

Note 1: These registers are not implemented on 28-pin devices.

#### 2.2.2.4 PIE1 Register

The PIE1 register contains the individual enable bits for the peripheral interrupts.

Note: Bit PEIE (INTCON<6>) must be set to enable any peripheral interrupt.

# REGISTER 2-4: PIE1 REGISTER (ADDRESS 8Ch)

|              |                        | •                             |               | •             |             |        |        |        |

|--------------|------------------------|-------------------------------|---------------|---------------|-------------|--------|--------|--------|

|              | R/W-0                  | R/W-0                         | R/W-0         | R/W-0         | R/W-0       | R/W-0  | R/W-0  | R/W-0  |

|              | PSPIE <sup>(1)</sup>   | ADIE                          | RCIE          | TXIE          | SSPIE       | CCP1IE | TMR2IE | TMR1IE |

|              | bit 7                  |                               |               |               |             |        |        | bit 0  |

|              |                        |                               |               |               |             |        |        |        |

| bit 7        | PSPIE <sup>(1)</sup> : | Parallel Slav                 | e Port Read   | d/Write Inter | rupt Enable | bit    |        |        |

|              | 1 = Enable             | es the PSP r                  | ead/write int | terrupt       |             |        |        |        |

|              | 0 = Disabl             | es the PSP                    | read/write in | terrupt       |             |        |        |        |

| bit 6        | ADIE: A/D              | Converter I                   | nterrupt Ena  | able bit      |             |        |        |        |

|              |                        | es the A/D co                 |               |               |             |        |        |        |

|              | 0 = Disabl             | es the A/D c                  | onverter inte | errupt        |             |        |        |        |

| bit 5        |                        | ART Receive                   | •             |               |             |        |        |        |

|              |                        | es the USAR                   |               | •             |             |        |        |        |

|              |                        | es the USAF                   |               |               |             |        |        |        |

| bit 4        |                        | RT Transmi                    | -             |               |             |        |        |        |

|              |                        | es the USAR                   |               |               |             |        |        |        |

| <b>h</b> # 0 |                        | es the USAF                   |               |               | hla h:+     |        |        |        |

| bit 3        | •                      | nchronous S                   |               | iterrupt Ena  | DIE DIT     |        |        |        |

|              |                        | es the SSP in<br>es the SSP i |               |               |             |        |        |        |

| bit 2        |                        | CP1 Interru                   |               | i+            |             |        |        |        |

|              |                        | es the CCP1                   | •             | it i          |             |        |        |        |

|              |                        | es the CCP                    | •             |               |             |        |        |        |

| bit 1        |                        | MR2 to PR                     |               | rrupt Enable  | e bit       |        |        |        |

|              |                        | es the TMR2                   |               | •             |             |        |        |        |

|              |                        | es the TMR2                   |               |               |             |        |        |        |

| bit 0        | TMR1IE: T              | MR1 Overfl                    | ow Interrupt  | Enable bit    |             |        |        |        |

|              |                        | es the TMR1                   |               |               |             |        |        |        |

|              |                        | es the TMR                    |               | •             |             |        |        |        |

|              |                        |                               |               |               |             |        |        |        |

Note 1: PSPIE is reserved on 28-pin devices; always maintain this bit clear.

| Legend:                  |                  |                      |                    |

|--------------------------|------------------|----------------------|--------------------|

| R = Readable bit         | W = Writable bit | U = Unimplemented    | bit, read as '0'   |

| - n = Value at POR reset | '1' = Bit is set | '0' = Bit is cleared | x = Bit is unknown |

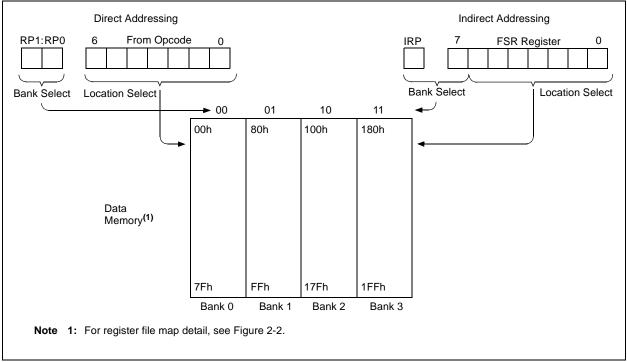

INDIDECT ADDESSING

# 2.5 Indirect Addressing, INDF and FSR Registers

The INDF register is not a physical register. Addressing the INDF register will cause indirect addressing.

Indirect addressing is possible by using the INDF register. Any instruction using the INDF register actually accesses the register pointed to by the File Select Register, FSR. Reading the INDF register itself indirectly (FSR = '0') will read 00h. Writing to the INDF register indirectly results in a no operation (although status bits may be affected). An effective 9-bit address is obtained by concatenating the 8-bit FSR register and the IRP bit (STATUS<7>), as shown in Figure 2-5.

A simple program to clear RAM locations 20h-2Fh using indirect addressing is shown in Example 2-2.

|        | PLE 2-2: | INL   | JIRECT ADDRESSING    |

|--------|----------|-------|----------------------|

|        | MOVLW    | 0x20  | ;initialize pointer  |

|        | MOVWF    | FSR   | ;to RAM              |

| NEXT   | CLRF     | INDF  | clear INDF register; |

|        | INCF     | FSR,F | ;inc pointer         |

|        | BTFSS    | FSR,4 | ;all done?           |

|        | GOTO     | NEXT  | ;no clear next       |

| CONTIN | IUE      |       |                      |

| :      |          |       | ;yes continue        |

|        |          |       |                      |

EVAMPLE 2.2.

## FIGURE 2-5: DIRECT/INDIRECT ADDRESSING

| Name    | Bit# | Buffer                | Function                                                                                                               |

|---------|------|-----------------------|------------------------------------------------------------------------------------------------------------------------|

| RB0/INT | bit0 | TTL/ST <sup>(1)</sup> | Input/output pin or external interrupt input. Internal software programmable weak pull-up.                             |

| RB1     | bit1 | TTL                   | Input/output pin. Internal software programmable weak pull-up.                                                         |

| RB2     | bit2 | TTL                   | Input/output pin. Internal software programmable weak pull-up.                                                         |

| RB3     | bit3 | TTL                   | Input/output pin. Internal software programmable weak pull-up.                                                         |

| RB4     | bit4 | TTL                   | Input/output pin (with interrupt-on-change). Internal software programmable weak pull-up.                              |

| RB5     | bit5 | TTL                   | Input/output pin (with interrupt-on-change). Internal software programmable weak pull-up.                              |

| RB6     | bit6 | TTL/ST <sup>(2)</sup> | Input/output pin (with interrupt-on-change).<br>Internal software programmable weak pull-up. Serial programming clock. |

| RB7     | bit7 | TTL/ST <sup>(2)</sup> | Input/output pin (with interrupt-on-change).<br>Internal software programmable weak pull-up. Serial programming data.  |

#### TABLE 4-3: PORTB FUNCTIONS

Legend: TTL = TTL input, ST = Schmitt Trigger input

Note 1: This buffer is a Schmitt Trigger input when configured as the external interrupt.

2: This buffer is a Schmitt Trigger input when used in Serial Programming mode.

#### TABLE 4-4: SUMMARY OF REGISTERS ASSOCIATED WITH PORTB

| Address   | Name       | Bit 7   | Bit 6                        | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 | Value on:<br>POR,<br>BOR | Value on<br>all other<br>RESETS |

|-----------|------------|---------|------------------------------|-------|-------|-------|-------|-------|-------|--------------------------|---------------------------------|

| 06h, 106h | PORTB      | RB7     | RB6                          | RB5   | RB4   | RB3   | RB2   | RB1   | RB0   | xxxx xxxx                | uuuu uuuu                       |

| 86h, 186h | TRISB      | PORTB I | ORTB Data Direction Register |       |       |       |       |       |       | 1111 1111                | 1111 1111                       |

| 81h, 181h | OPTION_REG | RBPU    | INTEDG                       | TOCS  | TOSE  | PSA   | PS2   | PS1   | PS0   | 1111 1111                | 1111 1111                       |

Legend: x = unknown, u = unchanged. Shaded cells are not used by PORTB.

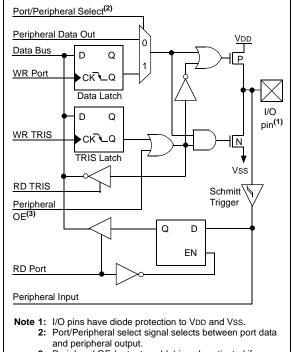

### 4.3 PORTC and the TRISC Register

PORTC is an 8-bit wide, bi-directional port. The corresponding data direction register is TRISC. Setting a TRISC bit (= '1') will make the corresponding PORTC pin an input (i.e., put the corresponding output driver in a Hi-Impedance mode). Clearing a TRISC bit (= '0') will make the corresponding PORTC pin an output (i.e., put the contents of the output latch on the selected pin).

PORTC is multiplexed with several peripheral functions (Table 4-5). PORTC pins have Schmitt Trigger input buffers.

When enabling peripheral functions, care should be taken in defining TRIS bits for each PORTC pin. Some peripherals override the TRIS bit to make a pin an output, while other peripherals override the TRIS bit to make a pin an input. Since the TRIS bit override is in effect while the peripheral is enabled, read-modify-write instructions (BSF, BCF, XORWF) with TRISC as destination should be avoided. The user should refer to the corresponding peripheral section for the correct TRIS bit settings, and to Section 13.1 for additional information on read-modify-write operations.

#### FIGURE 4-5:

#### PORTC BLOCK DIAGRAM (PERIPHERAL OUTPUT OVERRIDE)

**3:** Peripheral OE (output enable) is only activated if peripheral select is active.

| Name            | Bit# | Buffer Type | Function                                                                                        |

|-----------------|------|-------------|-------------------------------------------------------------------------------------------------|

| RC0/T1OSO/T1CKI | bit0 | ST          | Input/output port pin or Timer1 oscillator output/Timer1 clock input.                           |

| RC1/T1OSI/CCP2  | bit1 | ST          | Input/output port pin or Timer1 oscillator input or Capture2 input/Compare2 output/PWM2 output. |

| RC2/CCP1        | bit2 | ST          | Input/output port pin or Capture1 input/Compare1 output/PWM1 output.                            |

| RC3/SCK/SCL     | bit3 | ST          | RC3 can also be the synchronous serial clock for both SPI and $I^2C$ modes.                     |

| RC4/SDI/SDA     | bit4 | ST          | RC4 can also be the SPI Data In (SPI mode) or Data I/O (I <sup>2</sup> C mode).                 |

| RC5/SDO         | bit5 | ST          | Input/output port pin or Synchronous Serial Port data output.                                   |

| RC6/TX/CK       | bit6 | ST          | Input/output port pin or USART Asynchronous Transmit or<br>Synchronous Clock.                   |

| RC7/RX/DT       | bit7 | ST          | Input/output port pin or USART Asynchronous Receive or Synchronous Data.                        |

#### TABLE 4-5: PORTC FUNCTIONS

Legend: ST = Schmitt Trigger input

#### TABLE 4-6: SUMMARY OF REGISTERS ASSOCIATED WITH PORTC

| Address | Name  | Bit 7 | Bit 6                        | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 | Value on:<br>POR,<br>BOR | Value on<br>all other<br>RESETS |

|---------|-------|-------|------------------------------|-------|-------|-------|-------|-------|-------|--------------------------|---------------------------------|

| 07h     | PORTC | RC7   | RC6                          | RC5   | RC4   | RC3   | RC2   | RC1   | RC0   | xxxx xxxx                | uuuu uuuu                       |

| 87h     | TRISC | PORTC | ORTC Data Direction Register |       |       |       |       |       |       |                          | 1111 1111                       |

Legend: x = unknown, u = unchanged

# 8.0 CAPTURE/COMPARE/PWM MODULES

Each Capture/Compare/PWM (CCP) module contains a 16-bit register which can operate as a:

- 16-bit Capture register

- 16-bit Compare register

- PWM Master/Slave Duty Cycle register

Both the CCP1 and CCP2 modules are identical in operation, with the exception being the operation of the special event trigger. Table 8-1 and Table 8-2 show the resources and interactions of the CCP module(s). In the following sections, the operation of a CCP module is described with respect to CCP1. CCP2 operates the same as CCP1, except where noted.

#### 8.1 CCP1 Module

Capture/Compare/PWM Register1 (CCPR1) is comprised of two 8-bit registers: CCPR1L (low byte) and CCPR1H (high byte). The CCP1CON register controls the operation of CCP1. The special event trigger is generated by a compare match and will clear both TMR1H and TMR1L registers.

## 8.2 CCP2 Module

Capture/Compare/PWM Register1 (CCPR1) is comprised of two 8-bit registers: CCPR1L (low byte) and CCPR1H (high byte). The CCP2CON register controls the operation of CCP2. The special event trigger is generated by a compare match; it will clear both TMR1H and TMR1L registers, and start an A/D conversion (if the A/D module is enabled).

Additional information on CCP modules is available in the PICmicro<sup>™</sup> Mid-Range MCU Family Reference Manual (DS33023) and in Application Note AN594, "Using the CCP Modules" (DS00594).

#### TABLE 8-1: CCP MODE - TIMER RESOURCES REQUIRED

| CCP Mode | Timer Resource |

|----------|----------------|

| Capture  | Timer1         |

| Compare  | Timer1         |

| PWM      | Timer2         |

#### TABLE 8-2:INTERACTION OF TWO CCP MODULES

| CCPx Mode | CCPy Mode | Interaction                                                                                           |

|-----------|-----------|-------------------------------------------------------------------------------------------------------|

| Capture   | Capture   | Same TMR1 time-base.                                                                                  |

| Capture   | Compare   | Same TMR1 time-base.                                                                                  |

| Compare   | Compare   | Same TMR1 time-base.                                                                                  |

| PWM       | PWM       | The PWMs will have the same frequency and update rate (TMR2 interrupt). The rising edges are aligned. |

| PWM       | Capture   | None.                                                                                                 |

| PWM       | Compare   | None.                                                                                                 |

# PIC16F7X

# REGISTER 8-1: CCP1CON REGISTER/CCP2CON REGISTER (ADDRESS: 17h/1Dh)

| bit 7-6                                                                                          | U-0<br>—                                                                                                                                                                                     | U-0            | R/W-0<br>CCPxX | R/W-0       | R/W-0  | R/W-0  | R/W-0  | R/W-0  |  |  |  |  |  |  |

|--------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------|----------------|-------------|--------|--------|--------|--------|--|--|--|--|--|--|

| bit 7-6                                                                                          | —<br>bit 7                                                                                                                                                                                   | _              | CCDvV          |             |        |        |        |        |  |  |  |  |  |  |

| Dit 7-6                                                                                          | bit 7                                                                                                                                                                                        |                | COFXA          | CCPxY       | CCPxM3 | CCPxM2 | CCPxM1 | CCPxM0 |  |  |  |  |  |  |

| bit 5-4 ()<br>()<br>()<br>()<br>()<br>()<br>()<br>()<br>()<br>()<br>()<br>()<br>()<br>(          |                                                                                                                                                                                              |                |                |             |        |        |        | bit 0  |  |  |  |  |  |  |

| ()<br>()<br>()<br>()<br>()<br>()<br>()<br>()<br>()<br>()<br>()<br>()<br>()<br>(                  | Unimplemented: Read as '0'<br>CCPxX:CCPxY: PWM Least Significant bits                                                                                                                        |                |                |             |        |        |        |        |  |  |  |  |  |  |

| 1<br>1<br>1<br>2<br>2<br>2<br>2<br>2<br>1<br>2<br>2<br>2<br>1<br>1<br>1<br>1<br>1<br>1<br>1<br>1 | CCPxX:CC                                                                                                                                                                                     | PxY: PWN       | l Least Signi  | ficant bits |        |        |        |        |  |  |  |  |  |  |

| bit 3-0                                                                                          | Capture mode:<br>Unused                                                                                                                                                                      |                |                |             |        |        |        |        |  |  |  |  |  |  |

| -<br>bit 3-0                                                                                     | <u>Compare mode:</u><br>Unused                                                                                                                                                               |                |                |             |        |        |        |        |  |  |  |  |  |  |

| bit 3-0                                                                                          | PWM mode                                                                                                                                                                                     | <del>)</del> : |                |             |        |        |        |        |  |  |  |  |  |  |

|                                                                                                  | These bits are the two LSbs of the PWM duty cycle. The eight MSbs are found in CCPRxL.                                                                                                       |                |                |             |        |        |        |        |  |  |  |  |  |  |

| ,                                                                                                | CCPxM3:CCPxM0: CCPx Mode Select bits                                                                                                                                                         |                |                |             |        |        |        |        |  |  |  |  |  |  |

|                                                                                                  | 0000 = Capture/Compare/PWM disabled (resets CCPx module)                                                                                                                                     |                |                |             |        |        |        |        |  |  |  |  |  |  |

|                                                                                                  | 0100 = Capture mode, every falling edge                                                                                                                                                      |                |                |             |        |        |        |        |  |  |  |  |  |  |

| (                                                                                                | 0101 = Capture mode, every rising edge                                                                                                                                                       |                |                |             |        |        |        |        |  |  |  |  |  |  |

| (                                                                                                | 0110 = Capture mode, every 4th rising edge                                                                                                                                                   |                |                |             |        |        |        |        |  |  |  |  |  |  |

|                                                                                                  | 0111 = Capture mode, every 16th rising edge                                                                                                                                                  |                |                |             |        |        |        |        |  |  |  |  |  |  |

|                                                                                                  | 1000 = Compare mode, set output on match (CCPxIF bit is set)                                                                                                                                 |                |                |             |        |        |        |        |  |  |  |  |  |  |

|                                                                                                  |                                                                                                                                                                                              |                | e, clear outp  |             |        |        |        |        |  |  |  |  |  |  |

| -                                                                                                | 1010 = Compare mode, generate software interrupt on match (CCPxIF bit is set, CCPx pin is unaffected)                                                                                        |                |                |             |        |        |        |        |  |  |  |  |  |  |

| :                                                                                                | 1011 = Compare mode, trigger special event (CCPxIF bit is set, CCPx pin is unaffected);<br>CCP1 clears Timer1; CCP2 clears Timer1 and starts an A/D conversion (if A/D module<br>is enabled) |                |                |             |        |        |        |        |  |  |  |  |  |  |

| :                                                                                                | 11xx = PW                                                                                                                                                                                    | /M mode        |                |             |        |        |        |        |  |  |  |  |  |  |

|                                                                                                  |                                                                                                                                                                                              |                |                |             |        |        |        |        |  |  |  |  |  |  |

|                                                                                                  | Legend:                                                                                                                                                                                      |                |                |             |        |        |        |        |  |  |  |  |  |  |

| Legend:                  |                  |                      |                    |

|--------------------------|------------------|----------------------|--------------------|

| R = Readable bit         | W = Writable bit | U = Unimplemented    | l bit, read as '0' |

| - n = Value at POR reset | '1' = Bit is set | '0' = Bit is cleared | x = Bit is unknown |

#### 8.4.1 CCP PIN CONFIGURATION

The user must configure the RC2/CCP1 pin as an output by clearing the TRISC<2> bit.

| Note: | Clearing the CCP1CON register will force |  |  |  |

|-------|------------------------------------------|--|--|--|

|       | the RC2/CCP1 compare output latch to the |  |  |  |

|       | default low level. This is not the PORTC |  |  |  |

|       | I/O data latch.                          |  |  |  |

#### 8.4.2 TIMER1 MODE SELECTION

Timer1 must be running in Timer mode or Synchronized Counter mode if the CCP module is using the compare feature. In Asynchronous Counter mode, the compare operation may not work.

#### 8.4.3 SOFTWARE INTERRUPT MODE

When Generate Software Interrupt mode is chosen, the CCP1 pin is not affected. The CCP1IF or CCP2IF bit is set, causing a CCP interrupt (if enabled).

#### 8.4.4 SPECIAL EVENT TRIGGER

In this mode, an internal hardware trigger is generated, which may be used to initiate an action.

The special event trigger output of CCP1 resets the TMR1 register pair. This allows the CCPR1 register to effectively be a 16-bit programmable period register for Timer1.

The special event trigger output of CCP2 resets the TMR1 register pair and starts an A/D conversion (if the A/D module is enabled).

**Note:** The special event trigger from the CCP1 and CCP2 modules will not set interrupt flag bit TMR1IF (PIR1<0>).

| Address               | Name    | Bit 7                | Bit 6                               | Bit 5        | Bit 4         | Bit 3          | Bit 2      | Bit 1      | Bit 0     | Value on:<br>POR,<br>BOR | Value on<br>all other<br>RESETS |

|-----------------------|---------|----------------------|-------------------------------------|--------------|---------------|----------------|------------|------------|-----------|--------------------------|---------------------------------|

| 0Bh,8Bh,<br>10Bh,18Bh | INTCON  | GIE                  | PEIE                                | TMR0IE       | INTE          | RBIE           | TMR0IF     | INTF       | RBIF      | 0000 000x                | 0000 000u                       |

| 0Ch                   | PIR1    | PSPIF <sup>(1)</sup> | ADIF                                | RCIF         | TXIF          | SSPIF          | CCP1IF     | TMR2IF     | TMR1IF    | 0000 0000                | 0000 0000                       |

| 0Dh                   | PIR2    | —                    | —                                   | —            | —             | _              | _          | _          | CCP2IF    | 0                        | 0                               |

| 8Ch                   | PIE1    | PSPIE <sup>(1)</sup> | ADIE                                | RCIE         | TXIE          | SSPIE          | CCP1IE     | TMR2IE     | TMR1IE    | 0000 0000                | 0000 0000                       |

| 8Dh                   | PIE2    | —                    | _                                   | —            | _             | _              | —          | _          | CCP2IE    | 0                        | 0                               |

| 87h                   | TRISC   | PORTC D              | ata Direc                           | tion Registe | er            |                |            |            |           | 1111 1111                | 1111 1111                       |

| 0Eh                   | TMR1L   | Holding R            | egister fo                          | r the Least  | Significant   | Byte of the 1  | 6-bit TMR  | 1 Register |           | xxxx xxxx                | uuuu uuuu                       |

| 0Fh                   | TMR1H   | Holding R            | egister fo                          | r the Most S | Significant E | Byte of the 16 | 6-bit TMR1 | Register   |           | xxxx xxxx                | uuuu uuuu                       |

| 10h                   | T1CON   | —                    |                                     | T1CKPS1      | T1CKPS0       | T1OSCEN        | T1SYNC     | TMR1CS     | TMR10N    | 00 0000                  | uu uuuu                         |

| 15h                   | CCPR1L  | Capture/C            | ompare/l                            | PWM Regis    | ster1 (LSB)   |                |            |            |           | xxxx xxxx                | uuuu uuuu                       |

| 16h                   | CCPR1H  | Capture/C            | ompare/l                            | PWM Regis    | ster1 (MSB)   |                |            |            |           | xxxx xxxx                | uuuu uuuu                       |

| 17h                   | CCP1CON | —                    |                                     | CCP1X        | CCP1Y         | CCP1M3         | CCP1M2     | CCP1M1     | CCP1M0    | 00 0000                  | 00 0000                         |

| 1Bh                   | CCPR2L  | Capture/C            | Capture/Compare/PWM Register2 (LSB) |              |               |                |            |            |           | xxxx xxxx                | uuuu uuuu                       |

| 1Ch                   | CCPR2H  | Capture/C            | Capture/Compare/PWM Register2 (MSB) |              |               |                |            |            | xxxx xxxx | uuuu uuuu                |                                 |

| 1Dh                   | CCP2CON | —                    | _                                   | CCP2X        | CCP2Y         | CCP2M3         | CCP2M2     | CCP2M1     | CCP2M0    | 00 0000                  | 00 0000                         |

#### TABLE 8-3: REGISTERS ASSOCIATED WITH CAPTURE, COMPARE, AND TIMER1

Legend: x = unknown, u = unchanged, - = unimplemented, read as '0'. Shaded cells are not used by Capture and Timer1.

**Note 1:** The PSP is not implemented on the PIC16F73/76; always maintain these bits clear.

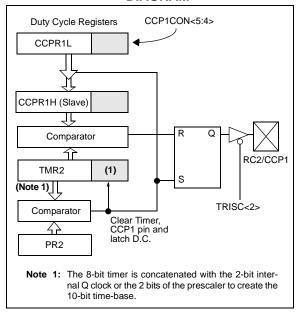

### 8.5 PWM Mode (PWM)

In Pulse Width Modulation mode, the CCPx pin produces up to a 10-bit resolution PWM output. Since the CCP1 pin is multiplexed with the PORTC data latch, the TRISC<2> bit must be cleared to make the CCP1 pin an output.

| Note: | Clearing the CCP1CON register will force  |

|-------|-------------------------------------------|

|       | the CCP1 PWM output latch to the default  |

|       | low level. This is not the PORTC I/O data |

|       | latch.                                    |

Figure 8-3 shows a simplified block diagram of the CCP module in PWM mode.

For a step-by-step procedure on how to set up the CCP module for PWM operation, see Section 8.5.3.

#### FIGURE 8-3: SIMPLIFIED PWM BLOCK DIAGRAM

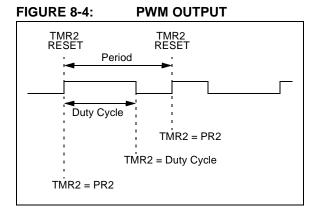

A PWM output (Figure 8-4) has a time-base (period) and a time that the output stays high (duty cycle). The frequency of the PWM is the inverse of the period (1/period).

#### 8.5.1 PWM PERIOD

The PWM period is specified by writing to the PR2 register. The PWM period can be calculated using the following formula:

$PWM period = [(PR2) + 1] \cdot 4 \cdot Tosc \cdot (TMR2 prescale value)$

PWM frequency is defined as 1 / [PWM period].

When TMR2 is equal to PR2, the following three events occur on the next increment cycle:

- TMR2 is cleared

- The CCP1 pin is set (exception: if PWM duty cycle = 0%, the CCP1 pin will not be set)

- The PWM duty cycle is latched from CCPR1L into CCPR1H

Note: The Timer2 postscaler (see Section 8.3) is not used in the determination of the PWM frequency. The postscaler could be used to have a servo update rate at a different frequency than the PWM output.

#### 8.5.2 PWM DUTY CYCLE

The PWM duty cycle is specified by writing to the CCPR1L register and to the CCP1CON<5:4> bits. Up to 10-bit resolution is available. The CCPR1L contains the eight MSbs and the CCP1CON<5:4> contains the two LSbs. This 10-bit value is represented by CCPR1L:CCP1CON<5:4>. The following equation is used to calculate the PWM duty cycle in time:

```

PWM duty cycle = (CCPR1L:CCP1CON<5:4>)•

TOSC • (TMR2 prescale value)

```

CCPR1L and CCP1CON<5:4> can be written to at any time, but the duty cycle value is not latched into CCPR1H until after a match between PR2 and TMR2 occurs (i.e., the period is complete). In PWM mode, CCPR1H is a read only register.

The CCPR1H register and a 2-bit internal latch are used to double buffer the PWM duty cycle. This double buffering is essential for glitchless PWM operation.

When the CCPR1H and 2-bit latch match TMR2, concatenated with an internal 2-bit Q clock or 2 bits of the TMR2 prescaler, the CCP1 pin is cleared.

The maximum PWM resolution (bits) for a given PWM frequency is given by the formula:

Resolution =

$$\frac{\log(\frac{FOSC}{FPWM})}{\log(2)}$$

bits

Note: If the PWM duty cycle value is longer than the PWM period, the CCP1 pin will not be cleared.

# 10.0 UNIVERSAL SYNCHRONOUS ASYNCHRONOUS RECEIVER TRANSMITTER (USART)

The Universal Synchronous Asynchronous Receiver Transmitter (USART) module is one of the two serial I/O modules. (USART is also known as a Serial Communications Interface or SCI.) The USART can be configured as a full duplex asynchronous system that can communicate with peripheral devices, such as CRT terminals and personal computers, or it can be configured as a half duplex synchronous system that can communicate with peripheral devices, such as A/D or D/A integrated circuits, serial EEPROMs, etc. The USART can be configured in the following modes:

- Asynchronous (full duplex)

- Synchronous Master (half duplex)

- Synchronous Slave (half duplex)

Bit SPEN (RCSTA<7>) and bits TRISC<7:6> have to be set in order to configure pins RC6/TX/CK and RC7/RX/DT as the Universal Synchronous Asynchronous Receiver Transmitter.

#### REGISTER 10-1: TXSTA: TRANSMIT STATUS AND CONTROL REGISTER (ADDRESS 98h)

|        | R/W-0                     | R/W-0                        | R/W-0         | R/W-0        | U-0      | R/W-0      | R-1          | R/W-0 |

|--------|---------------------------|------------------------------|---------------|--------------|----------|------------|--------------|-------|

|        | CSRC                      | TX9                          | TXEN          | SYNC         |          | BRGH       | TRMT         | TX9D  |

|        | bit 7                     |                              |               |              |          |            |              | bit 0 |

| bit 7  | CSRC: Clo                 | ock Source S                 | Select bit    |              |          |            |              |       |

|        | Asynchron                 | ous mode:                    |               |              |          |            |              |       |

|        | Don't care                |                              |               |              |          |            |              |       |

|        | Synchrono                 |                              |               |              |          |            |              |       |

|        |                           | · mode (clock<br>mode (clock |               |              | om BRG)  |            |              |       |

| bit 6  | <b>TX9</b> : 9-bit        | Transmit Ena                 | able bit      |              |          |            |              |       |

|        |                           | s 9-bit transn               |               |              |          |            |              |       |

| 1.11.5 |                           | s 8-bit transn               |               |              |          |            |              |       |

| bit 5  |                           | nsmit Enable<br>nit enabled  | e dit         |              |          |            |              |       |

|        |                           | nit disabled                 |               |              |          |            |              |       |

|        | Note:                     | SREN/CRE                     | N overrides   | TXEN in Sy   | nc mode. |            |              |       |

| bit 4  | SYNC: US                  | ART Mode S                   | Select bit    |              |          |            |              |       |

|        |                           | ronous mode                  |               |              |          |            |              |       |

|        | -                         | nronous mod                  |               |              |          |            |              |       |

| bit 3  | -                         | ented: Read                  |               |              |          |            |              |       |

| bit 2  | -                         | gh Baud Rate                 | e Select bit  |              |          |            |              |       |

|        | Asynchron                 |                              |               |              |          |            |              |       |

|        | 1 = High sp<br>0 = Low sp |                              |               |              |          |            |              |       |

|        | Synchrono                 |                              |               |              |          |            |              |       |

|        | Unused in                 |                              |               |              |          |            |              |       |

| bit 1  | TRMT: Tra                 | nsmit Shift R                | Register Stat | us bit       |          |            |              |       |

|        | 1 = TSR ei                |                              |               |              |          |            |              |       |

| 1 1 0  | 0 = TSR fu                |                              |               |              |          |            |              |       |

| bit 0  | Can be par                | bit of Transr                | nit Data      |              |          |            |              |       |

|        | oun be pu                 |                              |               |              |          |            |              |       |

|        | Legend:                   |                              |               |              |          |            |              |       |

|        | R = Reada                 | ble bit                      | W = W         | /ritable bit | U = Unir | nplemented | bit, read as | ʻ0'   |

| R = Readable bit         | W = Writable bit | U = Unimplemented bit, read as '0' |                    |  |  |  |

|--------------------------|------------------|------------------------------------|--------------------|--|--|--|

| - n = Value at POR reset | '1' = Bit is set | '0' = Bit is cleared               | x = Bit is unknown |  |  |  |

# 11.0 ANALOG-TO-DIGITAL CONVERTER (A/D) MODULE

The 8-bit analog-to-digital (A/D) converter module has five inputs for the PIC16F73/76 and eight for the PIC16F74/77.

The A/D allows conversion of an analog input signal to a corresponding 8-bit digital number. The output of the sample and hold is the input into the converter, which generates the result via successive approximation. The analog reference voltage is software selectable to either the device's positive supply voltage (VDD), or the voltage level on the RA3/AN3/VREF pin.

The A/D converter has a unique feature of being able to operate while the device is in SLEEP mode. To operate in SLEEP, the A/D conversion clock must be derived from the A/D's internal RC oscillator. The A/D module has three registers. These registers are:

- A/D Result Register ((ADRES)

- A/D Control Register 0 (ADCON0)

- A/D Control Register 1 ((ADCON1)

The ADCON0 register, shown in Register 11-1, controls the operation of the A/D module. The ADCON1 register, shown in Register 11-2, configures the functions of the port pins. The port pins can be configured as analog inputs (RA3 can also be a voltage reference), or as digital I/O.

Additional information on using the A/D module can be found in the PICmicro<sup>™</sup> Mid-Range MCU Family Reference Manual (DS33023) and in Application Note, AN546 (DS00546).

|         | Aboono                 |                              |                      | 50 mm,         |              |                 |             |        |

|---------|------------------------|------------------------------|----------------------|----------------|--------------|-----------------|-------------|--------|

|         | R/W-0                  | R/W-0                        | R/W-0                | R/W-0          | R/W-0        | R/W-0           | U-0         | R/W-0  |

|         | ADCS1                  | ADCS0                        | CHS2                 | CHS1           | CHS0         | GO/DONE         |             | ADON   |

|         | bit 7                  |                              |                      |                |              |                 |             | bit 0  |

|         |                        |                              |                      |                |              |                 |             |        |

| bit 7-6 | ADCS1:AI               | DCS0: A/D (                  | Conversion (         | Clock Select   | bits         |                 |             |        |

|         | 00 = Fosc              | · —                          |                      |                |              |                 |             |        |

|         | 01 = Fosc<br>10 = Fosc |                              |                      |                |              |                 |             |        |

|         |                        |                              | d from the ir        | nternal A/D m  | nodule RC c  | scillator)      |             |        |

| bit 5-3 | · ·                    | <b>SO</b> : Analog C         |                      |                |              | oomator)        |             |        |

|         |                        | nnel 0 (RA0                  |                      |                |              |                 |             |        |

|         |                        | nnel 1 (RA1                  | ,                    |                |              |                 |             |        |

|         | 010 <b>= Ch</b> a      | nnel 2 (RA2                  | /AN2)                |                |              |                 |             |        |

|         |                        | Innel 3 (RA3                 | ,                    |                |              |                 |             |        |

|         |                        | innel 4 (RA5<br>innel 5 (RE0 |                      |                |              |                 |             |        |

|         | 101 = Cha<br>110 = Cha | innel 6 (RE1                 | /ANS)(1)             |                |              |                 |             |        |

|         | 111 = Cha              | nnel 7 (RE2                  | /AN7) <sup>(1)</sup> |                |              |                 |             |        |

| bit 2   | GO/DONE                | : A/D Conve                  | rsion Status         | bit            |              |                 |             |        |

|         | If ADON =              | <u>1:</u>                    |                      |                |              |                 |             |        |

|         |                        |                              |                      |                |              | D conversion)   |             |        |

|         |                        |                              |                      | (this bit is a | utomatically | cleared by ha   | rdware wh   | en the |

|         |                        | nversion is c                | • •                  |                |              |                 |             |        |

| bit 1   | -                      | ented: Read                  | d as '0'             |                |              |                 |             |        |

| bit 0   | ADON: A/I              |                              |                      |                |              |                 |             |        |

|         |                        | nverter mod                  |                      |                | mos no onc   | erating current |             |        |

|         |                        |                              |                      |                | •            | •               | 7           |        |

|         | Note 1:                | A/D channe                   | els 5, 6 and         | 7 are implem   | iented on tr | e PIC16F74/7    | 7 only.     |        |

|         | Legend:                |                              |                      |                |              |                 |             |        |

|         | R = Reada              | able bit                     | W = V                | Vritable bit   | U = Unir     | nplemented bit  | , read as ' | 0'     |

|         |                        |                              |                      |                |              |                 |             |        |

'1' = Bit is set

'0' = Bit is cleared

### REGISTER 11-1: ADCON0 REGISTER (ADDRESS 1Fh)

- n = Value at POR reset

x = Bit is unknown

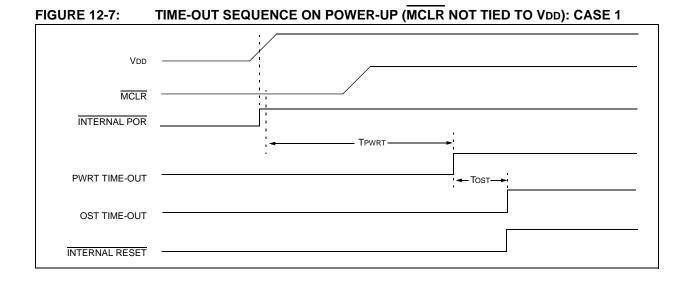

#### 12.10 Power Control/Status Register (PCON)

The Power Control/Status Register, PCON, has two bits to indicate the type of RESET that last occurred.

Bit0 is Brown-out Reset Status bit,  $\overline{\text{BOR}}$ . Bit  $\overline{\text{BOR}}$  is unknown on a Power-on Reset. It must then be set by the user and checked on subsequent RESETS to see

### TABLE 12-3: TIME-OUT IN VARIOUS SITUATIONS

if bit  $\overline{\text{BOR}}$  cleared, indicating a Brown-out Reset occurred. When the Brown-out Reset is disabled, the state of the  $\overline{\text{BOR}}$  bit is unpredictable.

Bit1 is POR (Power-on Reset Status bit). It is cleared on a Power-on Reset and unaffected otherwise. The user must set this bit following a Power-on Reset.

| Oppillator Configuration | Power             | -up       | Drown out         | Wake-up from |  |

|--------------------------|-------------------|-----------|-------------------|--------------|--|

| Oscillator Configuration | PWRTE = 0         | PWRTE = 1 | Brown-out         | SLEEP        |  |

| XT, HS, LP               | 72 ms + 1024 Tosc | 1024 Tosc | 72 ms + 1024 Tosc | 1024 Tosc    |  |

| RC                       | 72 ms             |           | 72 ms             | —            |  |

#### TABLE 12-4: STATUS BITS AND THEIR SIGNIFICANCE

| POR<br>(PCON<1>) | BOR<br>(PCON<0>) | TO<br>(STATUS<4>) | PD<br>(STATUS<3>)                    | Significance                                            |  |  |  |

|------------------|------------------|-------------------|--------------------------------------|---------------------------------------------------------|--|--|--|

| 0                | х                | 1                 | 1                                    | Power-on Reset                                          |  |  |  |

| 0                | x                | 0                 | x                                    | Illegal, TO is set on POR                               |  |  |  |

| 0                | x                | x                 | 0                                    | Illegal, PD is set on POR                               |  |  |  |

| 1                | 0                | 1                 | 1                                    | Brown-out Reset                                         |  |  |  |

| 1                | 1                | 0                 | 1                                    | WDT Reset                                               |  |  |  |

| 1                | 1                | 0                 | 0 WDT Wake-up                        |                                                         |  |  |  |

| 1                | 1                | u                 | u MCLR Reset during normal operation |                                                         |  |  |  |

| 1                | 1                | 1                 | 0                                    | MCLR Reset during SLEEP or interrupt wake-up from SLEEP |  |  |  |

#### TABLE 12-5: RESET CONDITION FOR SPECIAL REGISTERS

| Condition                          | Program<br>Counter    | STATUS<br>Register | PCON<br>Register |

|------------------------------------|-----------------------|--------------------|------------------|

| Power-on Reset                     | 000h                  | 0001 1xxx          | 0x               |

| MCLR Reset during normal operation | 000h                  | 000u uuuu          | uu               |

| MCLR Reset during SLEEP            | 000h                  | 0001 0uuu          | uu               |

| WDT Reset                          | 000h                  | 0000 luuu          | uu               |

| WDT Wake-up                        | PC + 1                | uuu0 0uuu          | uu               |

| Brown-out Reset                    | 000h                  | 0001 luuu          | u0               |

| Interrupt wake-up from SLEEP       | PC + 1 <sup>(1)</sup> | uuul Ouuu          | uu               |

Legend: u = unchanged, x = unknown, - = unimplemented bit, read as '0'

**Note 1:** When the wake-up is due to an interrupt and the GIE bit is set, the PC is loaded with the interrupt vector (0004h).

# PIC16F7X

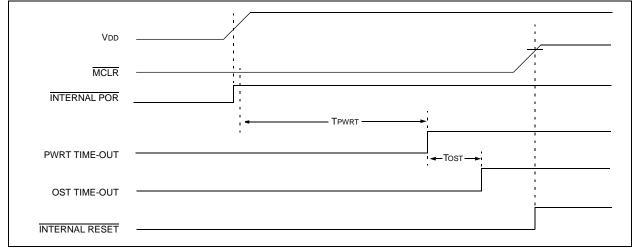

# FIGURE 12-8: TIME-OUT SEQUENCE ON POWER-UP (MCLR NOT TIED TO VDD): CASE 2

# FIGURE 12-9: SLOW RISE TIME (MCLR TIED TO VDD THROUGH RC NETWORK)

#### TABLE 13-2: PIC16F7X INSTRUCTION SET

| Mnemonic,                              |         | Description                                        | Cycles         |        | 14-Bit    | Opcode   | •         | Status       | Notes   |

|----------------------------------------|---------|----------------------------------------------------|----------------|--------|-----------|----------|-----------|--------------|---------|

| Opera                                  | nds     | Description                                        | Cycles         | MSb    |           |          | LSb       | Affected     | Notes   |

| BYTE-ORIENTED FILE REGISTER OPERATIONS |         |                                                    |                |        |           |          |           |              |         |

| ADDWF                                  | f, d    | Add W and f                                        | 1              | 00     | 0111      | dfff     | ffff      | C,DC,Z       | 1,2     |

| ANDWF                                  | f, d    | AND W with f                                       | 1              | 00     | 0101      | dfff     | ffff      | Z            | 1,2     |

| CLRF                                   | f       | Clear f                                            | 1              | 00     | 0001      | lfff     | ffff      | Z            | 2       |

| CLRW                                   | -       | Clear W                                            | 1              | 00     | 0001      | 0xxx     | xxxx      | Z            |         |

| COMF                                   | f, d    | Complement f                                       | 1              | 00     | 1001      | dfff     | ffff      | Z            | 1,2     |

| DECF                                   | f, d    | Decrement f                                        | 1              | 00     | 0011      | dfff     | ffff      | Z            | 1,2     |

| DECFSZ                                 | f, d    | Decrement f, Skip if 0                             | 1(2)           | 00     | 1011      | dfff     | ffff      |              | 1,2,3   |

| INCF                                   | f, d    | Increment f                                        | 1              | 00     | 1010      | dfff     | ffff      | Z            | 1,2     |

| INCFSZ                                 | f, d    | Increment f, Skip if 0                             | 1(2)           | 00     | 1111      | dfff     | ffff      |              | 1,2,3   |

| IORWF                                  | f, d    | Inclusive OR W with f                              | 1              | 00     | 0100      | dfff     | ffff      | Z            | 1,2     |

| MOVF                                   | f, d    | Move f                                             | 1              | 00     | 1000      | dfff     | ffff      | Z            | 1,2     |

| MOVWF                                  | f       | Move W to f                                        | 1              | 00     | 0000      | lfff     | ffff      |              |         |

| NOP                                    | -       | No Operation                                       | 1              | 00     | 0000      | 0xx0     | 0000      |              |         |

| RLF                                    | f, d    | Rotate Left f through Carry                        | 1              | 00     | 1101      | dfff     | ffff      | С            | 1,2     |

| RRF                                    | f, d    | Rotate Right f through Carry                       | 1              | 00     | 1100      | dfff     | ffff      | С            | 1,2     |

| SUBWF                                  | f, d    | Subtract W from f                                  | 1              | 00     | 0010      | dfff     | ffff      | C,DC,Z       | 1,2     |

| SWAPF                                  | f, d    | Swap nibbles in f                                  | 1              | 00     | 1110      | dfff     | ffff      |              | 1,2     |

| XORWF                                  | f, d    | Exclusive OR W with f                              | 1              | 00     | 0110      | dfff     | ffff      | Z            | 1,2     |

|                                        |         | BIT-ORIENTED FILE REG                              |                | RATION | IS        |          |           |              |         |

| BCF                                    | f, b    | Bit Clear f                                        | 1              | 01     | 00bb      | bfff     | ffff      |              | 1,2     |

| BSF                                    | f, b    | Bit Set f                                          | 1              | 01     | 01bb      | bfff     | ffff      |              | 1,2     |

| BTFSC                                  | f, b    | Bit Test f, Skip if Clear                          | 1 (2)          | 01     | 10bb      | bfff     | ffff      |              | 3       |

| BTFSS                                  | f, b    | Bit Test f, Skip if Set                            | 1 (2)          | 01     | 11bb      | bfff     | ffff      |              | 3       |

|                                        |         | LITERAL AND CONT                                   | ROL OPERAT     | IONS   |           |          |           |              |         |

| ADDLW                                  | k       | Add literal and W                                  | 1              | 11     | 111x      | kkkk     | kkkk      | C,DC,Z       |         |

| ANDLW                                  | k       | AND literal with W                                 | 1              | 11     | 1001      | kkkk     | kkkk      | Z            |         |

| CALL                                   | k       | Call subroutine                                    | 2              | 10     | 0kkk      | kkkk     | kkkk      |              |         |

| CLRWDT                                 | -       | Clear Watchdog Timer                               | 1              | 00     | 0000      | 0110     | 0100      | TO,PD        |         |

| GOTO                                   | k       | Go to address                                      | 2              | 10     | 1kkk      | kkkk     | kkkk      |              |         |

| IORLW                                  | k       | Inclusive OR literal with W                        | 1              | 11     | 1000      | kkkk     | kkkk      | Z            |         |

| MOVLW                                  | k       | Move literal to W                                  | 1              | 11     | 00xx      | kkkk     | kkkk      |              |         |

| RETFIE                                 | -       | Return from interrupt                              | 2              | 00     | 0000      | 0000     | 1001      |              |         |

| RETLW                                  | k       | Return with literal in W                           | 2              | 11     | 01xx      | kkkk     | kkkk      |              |         |

| RETURN                                 | -       | Return from Subroutine                             | 2              | 00     | 0000      | 0000     | 1000      |              |         |

| SLEEP                                  | -       | Go into Standby mode                               | 1              | 00     | 0000      | 0110     | 0011      | TO,PD        |         |

| SUBLW                                  | k       | Subtract W from literal                            | 1              | 11     | 110x      | kkkk     | kkkk      | C,DC,Z       |         |

| XORLW                                  | k       | Exclusive OR literal with W                        | 1              | 11     | 1010      | kkkk     | kkkk      | Z            |         |

| Note 1: V                              | Vhen an | I/O register is modified as a function of itself ( | e.g., MOVF POI | RTB, : | 1), the v | alue use | ed will b | e that value | present |

Note 1: When an I/O register is modified as a function of itself (e.g., MOVF PORTB, 1), the value used will be that value present on the pins themselves. For example, if the data latch is '1' for a pin configured as input and is driven low by an external device, the data will be written back with a '0'.

2: If this instruction is executed on the TMR0 register (and, where applicable, d = 1), the prescaler will be cleared if assigned to the Timer0 module.

3: If Program Counter (PC) is modified, or a conditional test is true, the instruction requires two cycles. The second cycle is executed as a NOP.

Note: Additional information on the mid-range instruction set is available in the PICmicro<sup>™</sup> Mid-Range MCU Family Reference Manual (DS33023).

| RLF              | Rotate Left f through Carry                                                                                                                                                                                   |

|------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [ <i>label</i> ] RLF f,d                                                                                                                                                                                      |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ d \in \left[0,1\right] \end{array}$                                                                                                                                    |

| Operation:       | See description below                                                                                                                                                                                         |

| Status Affected: | С                                                                                                                                                                                                             |

| Description:     | The contents of register 'f' are rotated<br>one bit to the left through the Carry<br>Flag. If 'd' is 0, the result is placed in<br>the W register. If 'd' is 1, the result is<br>stored back in register 'f'. |

# SLEEP

| Syntax:          | [label] SLEEP                                                                                                                                                                                                                        |

|------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Operands:        | None                                                                                                                                                                                                                                 |

| Operation:       | $\begin{array}{l} 00h \rightarrow WDT, \\ 0 \rightarrow WDT \text{ prescaler,} \\ 1 \rightarrow \overline{TO}, \\ 0 \rightarrow \overline{PD} \end{array}$                                                                           |

| Status Affected: | TO, PD                                                                                                                                                                                                                               |

| Description:     | The power-down status bit, $\overline{\text{PD}}$ is cleared. Time-out status bit, $\overline{\text{TO}}$ is set. Watchdog Timer and its prescaler are cleared.<br>The processor is put into SLEEP mode with the oscillator stopped. |

| RETURN           | Return from Subroutine                                                                                                                                     |  |  |  |  |  |

|------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| Syntax:          | [label] RETURN                                                                                                                                             |  |  |  |  |  |

| Operands:        | None                                                                                                                                                       |  |  |  |  |  |

| Operation:       | $TOS\toPC$                                                                                                                                                 |  |  |  |  |  |

| Status Affected: | None                                                                                                                                                       |  |  |  |  |  |

| Description:     | Return from subroutine. The stack<br>is POPed and the top of the stack<br>(TOS) is loaded into the program<br>counter. This is a two-cycle<br>instruction. |  |  |  |  |  |