Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                                         |

|----------------------------|-------------------------------------------------------------------------|

| Product Status             | Active                                                                  |

| Core Processor             | PIC                                                                     |

| Core Size                  | 8-Bit                                                                   |

| Speed                      | 20MHz                                                                   |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                                       |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                   |

| Number of I/O              | 22                                                                      |

| Program Memory Size        | 14KB (8K x 14)                                                          |

| Program Memory Type        | FLASH                                                                   |

| EEPROM Size                | -                                                                       |

| RAM Size                   | 368 x 8                                                                 |

| Voltage - Supply (Vcc/Vdd) | 4V ~ 5.5V                                                               |

| Data Converters            | A/D 5x8b                                                                |

| Oscillator Type            | External                                                                |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                      |

| Mounting Type              | Surface Mount                                                           |

| Package / Case             | 28-SOIC (0.295", 7.50mm Width)                                          |

| Supplier Device Package    | 28-SOIC                                                                 |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16f76-e-so |

TABLE 1-2: PIC16F73 AND PIC16F76 PINOUT DESCRIPTION

| Pin Name                           | DIP<br>SSOP<br>SOIC<br>Pin# | MLF<br>Pin# | I/O/P<br>Type | Buffer<br>Type         | Description                                                                                                                                                 |

|------------------------------------|-----------------------------|-------------|---------------|------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------|

| OSC1/CLKI<br>OSC1                  | 9                           | 6           | I             | ST/CMOS <sup>(3)</sup> | Oscillator crystal or external clock input.  Oscillator crystal input or external clock source input. ST buffer when configured in RC mode. Otherwise CMOS. |

| CLKI                               |                             |             | I             |                        | External clock source input. Always associated with pin function OSC1 (see OSC1/CLKI, OSC2/CLKO pins).                                                      |

| OSC2/CLKO<br>OSC2                  | 10                          | 7           | 0             | _                      | Oscillator crystal or clock output.  Oscillator crystal output.  Connects to crystal or resonator in Crystal Oscillator mode.                               |

| CLKO                               |                             |             | 0             |                        | In RC mode, OSC2 pin outputs CLKO, which has 1/4 the frequency of OSC1 and denotes the instruction cycle rate.                                              |

| MCLR/VPP<br>MCLR                   | 1                           | 26          | I             | ST                     | Master Clear (input) or programming voltage (output).  Master Clear (Reset) input. This pin is an active low RESET to the device.                           |

| VPP                                |                             |             | Р             |                        | Programming voltage input.                                                                                                                                  |

|                                    |                             |             |               |                        | PORTA is a bi-directional I/O port.                                                                                                                         |

| RA0/AN0<br>RA0<br>AN0              | 2                           | 27          | I/O<br>I      | TTL                    | Digital I/O.<br>Analog input 0.                                                                                                                             |

| RA1/AN1<br>RA1<br>AN1              | 3                           | 28          | I/O<br>I      | TTL                    | Digital I/O.<br>Analog input 1.                                                                                                                             |

| RA2/AN2<br>RA2<br>AN2              | 4                           | 1           | I/O<br>I      | TTL                    | Digital I/O. Analog input 2.                                                                                                                                |

| RA3/AN3/VREF<br>RA3<br>AN3<br>VREF | 5                           | 2           | I/O<br>I      | TTL                    | Digital I/O. Analog input 3. A/D reference voltage input.                                                                                                   |

| RA4/T0CKI<br>RA4<br>T0CKI          | 6                           | 4           | I/O<br>I      | ST                     | Digital I/O – Open drain when configured as output. Timer0 external clock input.                                                                            |

| RA5/SS/AN4<br>RA5<br>SS<br>AN4     | 7                           | 5           | I/O<br>I<br>I | TTL                    | Digital I/O. SPI slave select input. Analog input 4.                                                                                                        |

Legend:I = inputO = outputI/O = input/outputP = power— = Not usedTTL = TTL inputST = Schmitt Trigger input

Note 1: This buffer is a Schmitt Trigger input when configured as the external interrupt.

<sup>2:</sup> This buffer is a Schmitt Trigger input when used in Serial Programming mode.3: This buffer is a Schmitt Trigger input when configured in RC Oscillator mode and a CMOS input otherwise.

### 3.3 Reading the FLASH Program Memory

A program memory location may be read by writing two bytes of the address to the PMADR and PMADRH registers and then setting control bit RD (PMCON1<0>). Once the read control bit is set, the microcontroller will use the next two instruction cycles to read the data. The data is available in the PMDATA and PMDATH registers after the second NOP instruction. Therefore, it can be read as two bytes in the following instructions. The PMDATA and PMDATH registers will hold this value until the next read operation.

#### 3.4 Operation During Code Protect

FLASH program memory has its own code protect mechanism. External Read and Write operations by programmers are disabled if this mechanism is enabled.

The microcontroller can read and execute instructions out of the internal FLASH program memory, regardless of the state of the code protect configuration bits.

#### **EXAMPLE 3-1: FLASH PROGRAM READ**

```

STATUS, RP1

; Bank 2

BCF

STATUS, RPO

MOVF

ADDRH, W

MOVWF

PMADRH

; MSByte of Program Address to read

MOVF

ADDRL, W

;

MOVWF

PMADR

; LSByte of Program Address to read

BSF

STATUS, RP0

; Bank 3 Required

Required

BSF

PMCON1, RD

; EEPROM Read Sequence

; memory is read in the next two cycles after BSF PMCON1,RD

Sequence

NOP

NOP

BCF

STATUS, RP0

; Bank 2

; W = LSByte of Program PMDATA

MOVF

PMDATA, W

MOVF

PMDATH, W

; W = MSByte of Program PMDATA

```

#### TABLE 3-1: REGISTERS ASSOCIATED WITH PROGRAM FLASH

| Address | Name   | Bit 7     | Bit 6       | Bit 5    | Bit 4      | Bit 3      | Bit 2    | Bit 1 | Bit 0 | Value on:<br>POR,<br>BOR | Value on<br>all other<br>RESETS |

|---------|--------|-----------|-------------|----------|------------|------------|----------|-------|-------|--------------------------|---------------------------------|

| 10Dh    | PMADR  | Address F | Register Lo | ow Byte  |            |            |          |       |       | xxxx xxxx                | uuuu uuuu                       |

| 10Fh    | PMADRH | _         | _           | _        | Address F  | Register H | igh Byte |       |       | xxxx xxxx                | uuuu uuuu                       |

| 10Ch    | PMDATA | Data Reg  | ister Low I | Byte     |            |            |          |       |       | xxxx xxxx                | uuuu uuuu                       |

| 10Eh    | PMDATH | _         | _           | Data Reg | ister High | Byte       |          |       |       | xxxx xxxx                | uuuu uuuu                       |

| 18Ch    | PMCON1 | (1)       | _           | _        | _          | _          | ı        | _     | RD    | 10                       | 10                              |

Legend: x = unknown, u = unchanged, r = reserved, - = unimplemented read as '0'. Shaded cells are not used during FLASH access. **Note 1:** This bit always reads as a '1'.

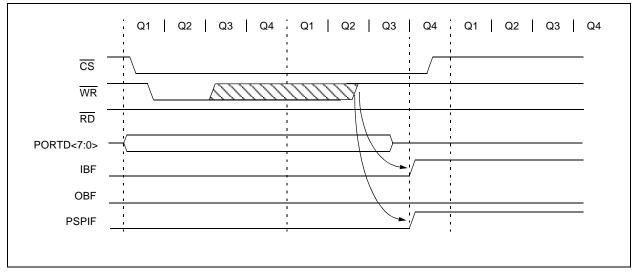

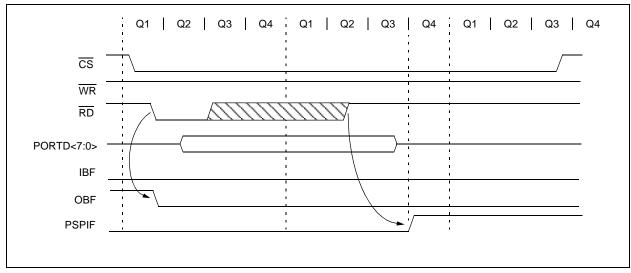

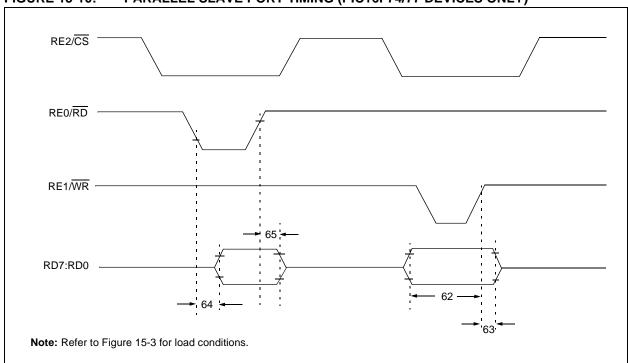

FIGURE 4-10: PARALLEL SLAVE PORT READ WAVEFORMS

TABLE 4-11: REGISTERS ASSOCIATED WITH PARALLEL SLAVE PORT

| Address | Name   | Bit 7                | Bit 6   | Bit 5     | Bit 4         | Bit 3    | Bit 2   | Bit 1       | Bit 0    | Value on:<br>POR,<br>BOR | Value on<br>all other<br>RESETS |

|---------|--------|----------------------|---------|-----------|---------------|----------|---------|-------------|----------|--------------------------|---------------------------------|

| 08h     | PORTD  | Port data I          | atch wh | nen writt | en: Port pins | when rea | d       |             |          | xxxx xxxx                | uuuu uuuu                       |

| 09h     | PORTE  | _                    | _       | _         | _             | _        | RE2     | RE1         | RE0      | xxx                      | uuu                             |

| 89h     | TRISE  | IBF                  | OBF     | IBOV      | PSPMODE       | _        | PORTE D | Data Direct | ion Bits | 0000 -111                | 0000 -111                       |

| 0Ch     | PIR1   | PSPIF <sup>(1)</sup> | ADIF    | RCIF      | TXIF          | SSPIF    | CCP1IF  | TMR2IF      | TMR1IF   | 0000 0000                | 0000 0000                       |

| 8Ch     | PIE1   | PSPIE <sup>(1)</sup> | ADIE    | RCIE      | TXIE          | SSPIE    | CCP1IE  | TMR2IE      | TMR1IE   | 0000 0000                | 0000 0000                       |

| 9Fh     | ADCON1 | _                    | _       | _         | _             | 1        | PCFG2   | PCFG1       | PCFG0    | 000                      | 000                             |

$\label{eq:local_equation} \textbf{Legend:} \quad \textbf{x} = \textbf{unknown}, \ \textbf{u} = \textbf{unchanged}, \ \textbf{-} = \textbf{unimplemented}, \ \textbf{read as '0'}. \ \textbf{Shaded cells are not used by the Parallel Slave Port.}$

Note 1: Bits PSPIE and PSPIF are reserved on the PIC16F73/76; always maintain these bits clear.

#### 6.5 Timer1 Oscillator

A crystal oscillator circuit is built-in between pins T1OSI (input) and T1OSO (amplifier output). It is enabled by setting control bit T1OSCEN (T1CON<3>). The oscillator is a low power oscillator rated up to 200 kHz. It will continue to run during SLEEP. It is primarily intended for use with a 32 kHz crystal. Table 6-1 shows the capacitor selection for the Timer1 oscillator.

The Timer1 oscillator is identical to the LP oscillator. The user must provide a software time delay to ensure proper oscillator start-up.

#### 6.6 Resetting Timer1 using a CCP Trigger Output

If the CCP1 or CCP2 module is configured in Compare mode to generate a "special event trigger" (CCP1M3:CCP1M0 = '1011'), this signal will reset Timer1.

| Note: | The special event triggers from the CCP1 |

|-------|------------------------------------------|

|       | and CCP2 modules will not set interrupt  |

|       | flag bit TMR1IF (PIR1<0>).               |

Timer1 must be configured for either Timer or Synchronized Counter mode, to take advantage of this feature. If Timer1 is running in Asynchronous Counter mode, this RESET operation may not work.

In the event that a write to Timer1 coincides with a special event trigger from CCP1 or CCP2, the write will take precedence.

In this mode of operation, the CCPRxH:CCPRxL register pair effectively becomes the period register for Timer1.

## 6.7 Resetting of Timer1 Register Pair (TMR1H, TMR1L)

TMR1H and TMR1L registers are not reset to 00h on a POR, or any other RESET, except by the CCP1 and CCP2 special event triggers.

TABLE 6-1: CAPACITOR SELECTION FOR THE TIMER1 OSCILLATOR

| Osa Typa | Erogueney | Capacito | ors Used: |

|----------|-----------|----------|-----------|

| Osc Type | Frequency | OSC1     | OSC2      |

| LP       | 32 kHz    | 47 pF    | 47 pF     |

|          | 100 kHz   | 33 pF    | 33 pF     |

|          | 200 kHz   | 15 pF    | 15 pF     |

#### Capacitor values are for design guidance only.

These capacitors were tested with the crystals listed below for basic start-up and operation. These values were not optimized.

Different capacitor values may be required to produce acceptable oscillator operation. The user should test the performance of the oscillator over the expected VDD and temperature range for the application.

See the notes (below) table for additional information.

|            | Commonly Used Crystals: |

|------------|-------------------------|

| 32.768 kHz | Epson C-001R32.768K-A   |

| 100 kHz    | Epson C-2 100.00 KC-P   |

| 200 kHz    | STD XTL 200.000 kHz     |

- Note 1: Higher capacitance increases the stability of the oscillator, but also increases the start-up time.

- 2: Since each resonator/crystal has its own characteristics, the user should consult the resonator/crystal manufacturer for appropriate values of external components.

T1CON register is reset to 00h on a Power-on Reset or a Brown-out Reset, which shuts off the timer and leaves a 1:1 prescale. In all other RESETS, the register is unaffected.

#### 6.8 Timer1 Prescaler

The prescaler counter is cleared on writes to the TMR1H or TMR1L registers.

TABLE 6-2: REGISTERS ASSOCIATED WITH TIMER1 AS A TIMER/COUNTER

| Address               | Name   | Bit 7                | Bit 6      | Bit 5      | Bit 4         | Bit 3       | Bit 2      | Bit 1      | Bit 0  | PC   | e on:<br>DR,<br>DR |      | e on<br>other<br>SETS |

|-----------------------|--------|----------------------|------------|------------|---------------|-------------|------------|------------|--------|------|--------------------|------|-----------------------|

| 0Bh,8Bh,<br>10Bh,18Bh | INTCON | GIE                  | PEIE       | TMR0IE     | INTE          | RBIE        | TMR0IF     | INTF       | RBIF   | 0000 | 000x               | 0000 | 000u                  |

| 0Ch                   | PIR1   | PSPIF <sup>(1)</sup> | ADIF       | RCIF       | TXIF          | SSPIF       | CCP1IF     | TMR2IF     | TMR1IF | 0000 | 0000               | 0000 | 0000                  |

| 8Ch                   | PIE1   | PSPIE <sup>(1)</sup> | ADIE       | RCIE       | TXIE          | SSPIE       | CCP1IE     | TMR2IE     | TMR1IE | 0000 | 0000               | 0000 | 0000                  |

| 0Eh                   | TMR1L  | Holding re           | gister for | the Least  | Significant   | Byte of the | 16-bit TMF | R1 Registe | r      | xxxx | xxxx               | uuuu | uuuu                  |

| 0Fh                   | TMR1H  | Holding re           | gister for | the Most S | Significant I | Byte of the | 16-bit TMR | 1 Register |        | xxxx | xxxx               | uuuu | uuuu                  |

| 10h                   | T1CON  | _                    | _          | T1CKPS1    | T1CKPS0       | T1OSCEN     | T1SYNC     | TMR1CS     | TMR10N | 00   | 0000               | uu   | uuuu                  |

Legend: x = unknown, u = unchanged, - = unimplemented, read as '0'. Shaded cells are not used by the Timer1 module.

Note 1: Bits PSPIE and PSPIF are reserved on the PIC16F73/76; always maintain these bits clear.

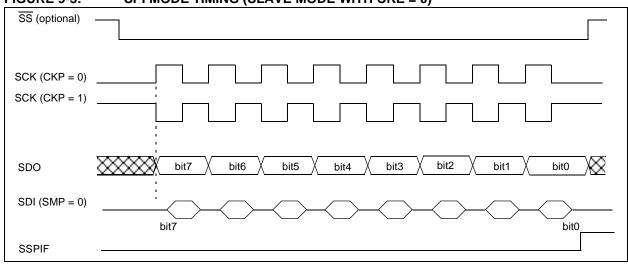

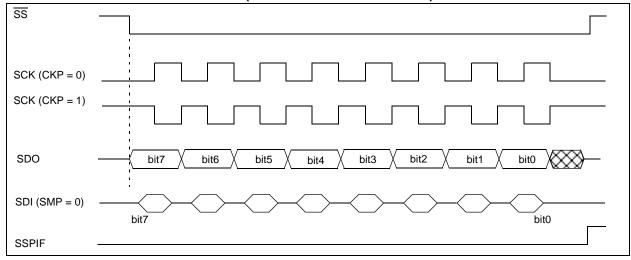

#### FIGURE 9-4: SPI MODE TIMING (SLAVE MODE WITH CKE = 1)

NOTES:

#### 11.7 Use of the CCP Trigger

An A/D conversion can be started by the "special event trigger" of the CCP2 module. This requires that the CCP2M3:CCP2M0 bits (CCP2CON<3:0>) be programmed as 1011 and that the A/D module is enabled (ADON bit is set). When the trigger occurs, the GO/DONE bit will be set, starting the A/D conversion, and the Timer1 counter will be reset to zero. Timer1 is reset to automatically repeat the A/D acquisition period

with minimal software overhead (moving the ADRES to the desired location). The appropriate analog input channel must be selected and an appropriate acquisition time should pass before the "special event trigger" sets the GO/DONE bit (starts a conversion).

If the A/D module is not enabled (ADON is cleared), then the "special event trigger" will be ignored by the A/D module, but will still reset the Timer1 counter.

TABLE 11-2: SUMMARY OF A/D REGISTERS

| Address                | Name                 | Bit 7                | Bit 6       | Bit 5   | Bit 4         | Bit 3    | Bit 2    | Bit 1       | Bit 0  | Value on:<br>POR,<br>BOR | Value on all other RESETS |

|------------------------|----------------------|----------------------|-------------|---------|---------------|----------|----------|-------------|--------|--------------------------|---------------------------|

| 0Bh,8Bh,<br>10Bh, 18Bh | INTCON               | GIE                  | PEIE        | TMR0IE  | INTE          | RBIE     | TMR0IF   | INTF        | RBIF   | 0000 000x                | 0000 000u                 |

| 0Ch                    | PIR1                 | PSPIF <sup>(1)</sup> | ADIF        | RCIF    | TXIF          | SSPIF    | CCP1IF   | TMR2IF      | TMR1IF | 0000 0000                | 0000 0000                 |

| 0Dh                    | PIR2                 | _                    | _           | _       | _             | _        | _        | _           | CCP2IF | 0                        | 0                         |

| 8Ch                    | PIE1                 | PSPIE <sup>(1)</sup> | ADIE        | RCIE    | TXIE          | SSPIE    | CCP1IE   | TMR2IE      | TMR1IE | 0000 0000                | 0000 0000                 |

| 8Dh                    | PIE2                 | _                    | _           | _       | _             | _        | _        | _           | CCP2IE | 0                        | 0                         |

| 1Eh                    | ADRES                | A/D Resu             | ılt Registe | er      |               |          |          |             |        | xxxx xxxx                | uuuu uuuu                 |

| 1Fh                    | ADCON0               | ADCS1                | ADCS0       | CHS2    | CHS1          | CHS0     | GO/DONE  | _           | ADON   | 0000 00-0                | 0000 00-0                 |

| 9Fh                    | ADCON1               | _                    | _           | _       | _             | _        | PCFG2    | PCFG1       | PCFG0  | 000                      | 000                       |

| 05h                    | PORTA                | _                    | _           | RA5     | RA4           | RA3      | RA2      | RA1         | RA0    | 0x 0000                  | 0u 0000                   |

| 85h                    | TRISA                | _                    | 1           | PORTA [ | Data Directio | n Regist | er       |             |        | 11 1111                  | 11 1111                   |

| 09h                    | PORTE <sup>(2)</sup> | _                    | _           | _       | _             |          | RE2      | RE1         | RE0    | xxx                      | uuu                       |

| 89h                    | TRISE <sup>(2)</sup> | IBF                  | OBF         | IBOV    | PSPMODE       | _        | PORTE Da | ta Directio | n Bits | 0000 -111                | 0000 -111                 |

Legend: x = unknown, u = unchanged, - = unimplemented, read as '0'. Shaded cells are not used for A/D conversion.

Note 1: Bits PSPIE and PSPIF are reserved on the PIC16F73/76; always maintain these bits clear.

2: These registers are reserved on the PIC16F73/76.

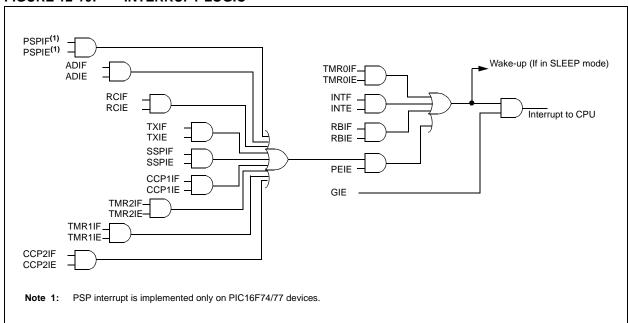

#### 12.11 Interrupts

The PIC16F7X family has up to 12 sources of interrupt. The interrupt control register (INTCON) records individual interrupt requests in flag bits. It also has individual and global interrupt enable bits.

Note: Individual interrupt flag bits are set, regardless of the status of their corresponding mask bit or the GIE bit.

A global interrupt enable bit, GIE (INTCON<7>) enables (if set) all unmasked interrupts, or disables (if cleared) all interrupts. When bit GIE is enabled and an interrupt's flag bit and mask bit are set, the interrupt will vector immediately. Individual interrupts can be disabled through their corresponding enable bits in various registers. Individual interrupt bits are set, regardless of the status of the GIE bit. The GIE bit is cleared on RESET.

The "return from interrupt" instruction, RETFIE, exits the interrupt routine, as well as sets the GIE bit, which re-enables interrupts.

The RB0/INT pin interrupt, the RB port change interrupt and the TMR0 overflow interrupt flags are contained in the INTCON register.

The peripheral interrupt flags are contained in the Special Function Registers, PIR1 and PIR2. The corresponding interrupt enable bits are contained in Special Function Registers, PIE1 and PIE2, and the peripheral interrupt enable bit is contained in Special Function Register, INTCON.

When an interrupt is responded to, the GIE bit is cleared to disable any further interrupt, the return address is pushed onto the stack and the PC is loaded with 0004h. Once in the Interrupt Service Routine, the source(s) of the interrupt can be determined by polling the interrupt flag bits. The interrupt flag bit(s) must be cleared in software before re-enabling interrupts to avoid recursive interrupts.

For external interrupt events, such as the INT pin or PORTB change interrupt, the interrupt latency will be three or four instruction cycles. The exact latency depends when the interrupt event occurs, relative to the current Q cycle. The latency is the same for one or two-cycle instructions. Individual interrupt flag bits are set, regardless of the status of their corresponding mask bit, PEIE bit, or the GIE bit.

FIGURE 12-10: INTERRUPT LOGIC

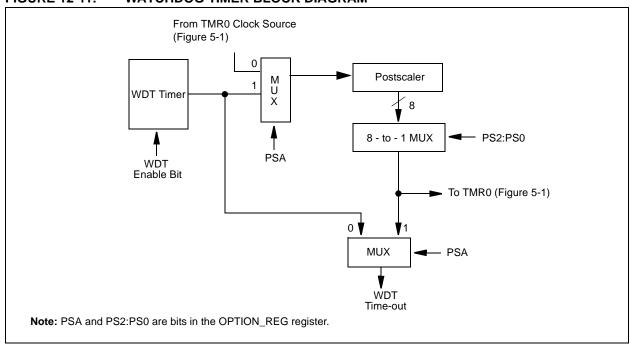

#### 12.13 Watchdog Timer (WDT)

The Watchdog Timer is a free running on-chip RC oscillator, which does not require any external components. This RC oscillator is separate from the RC oscillator of the OSC1/CLKIN pin. That means that the WDT will run, even if the clock on the OSC1/CLKIN and OSC2/CLKOUT pins of the device has been stopped, for example, by execution of a SLEEP instruction.

During normal operation, a WDT time-out generates a device RESET (Watchdog Timer Reset). If the device is in SLEEP mode, a WDT time-out causes the device to wake-up and continue with normal operation (Watchdog Timer Wake-up). The TO bit in the STATUS register will be cleared upon a Watchdog Timer time-out.

The WDT can be permanently disabled by clearing configuration bit, WDTE (Section 12.1).

WDT time-out period values may be found in the Electrical Specifications section under parameter #31. Values for the WDT prescaler (actually a postscaler, but shared with the Timer0 prescaler) may be assigned using the OPTION\_REG register.

- Note 1: The CLRWDT and SLEEP instructions clear the WDT and the postscaler, if assigned to the WDT, and prevent it from timing out and generating a device RESET condition.

- 2: When a CLRWDT instruction is executed and the prescaler is assigned to the WDT, the prescaler count will be cleared, but the prescaler assignment is not changed.

FIGURE 12-11: WATCHDOG TIMER BLOCK DIAGRAM

TABLE 12-7: SUMMARY OF WATCHDOG TIMER REGISTERS

| Address  | Name         | Bit 7 | Bit 6                | Bit 5 | Bit 4 | Bit 3                | Bit 2 | Bit 1 | Bit 0 |

|----------|--------------|-------|----------------------|-------|-------|----------------------|-------|-------|-------|

| 2007h    | Config. bits | (1)   | BODEN <sup>(1)</sup> | _     | CP0   | PWRTE <sup>(1)</sup> | WDTE  | FOSC1 | FOSC0 |

| 81h,181h | OPTION_REG   | RBPU  | INTEDG               | T0CS  | T0SE  | PSA                  | PS2   | PS1   | PS0   |

Legend: Shaded cells are not used by the Watchdog Timer.

Note 1: See Register 12-1 for operation of these bits.

NOTES:

| MOVF             | Move f                                                                                                                                                                                                                                                      |

|------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [ label ] MOVF f,d                                                                                                                                                                                                                                          |

| Operands:        | $0 \le f \le 127$<br>$d \in [0,1]$                                                                                                                                                                                                                          |

| Operation:       | (f) $\rightarrow$ (destination)                                                                                                                                                                                                                             |

| Status Affected: | Z                                                                                                                                                                                                                                                           |

| Description:     | The contents of register f are moved to a destination dependant upon the status of d. If $d=0$ , destination is W register. If $d=1$ , the destination is file register f itself. $d=1$ is useful to test a file register, since status flag Z is affected. |

| NOP              | No Operation  |

|------------------|---------------|

| Syntax:          | [label] NOP   |

| Operands:        | None          |

| Operation:       | No operation  |

| Status Affected: | None          |

| Description:     | No operation. |

|                  |               |

|                  |               |

|                  |               |

|                  |               |

| MOVLW            | Move Literal to W                                                                          |  |  |  |  |  |

|------------------|--------------------------------------------------------------------------------------------|--|--|--|--|--|

| Syntax:          | [ label ] MOVLW k                                                                          |  |  |  |  |  |

| Operands:        | $0 \leq k \leq 255$                                                                        |  |  |  |  |  |

| Operation:       | $k \rightarrow (W)$                                                                        |  |  |  |  |  |

| Status Affected: | None                                                                                       |  |  |  |  |  |

| Description:     | The eight-bit literal 'k' is loaded into W register. The don't cares will assemble as 0's. |  |  |  |  |  |

| RETFIE           | Return from Interrupt                      |  |  |  |  |

|------------------|--------------------------------------------|--|--|--|--|

| Syntax:          | [label] RETFIE                             |  |  |  |  |

| Operands:        | None                                       |  |  |  |  |

| Operation:       | $TOS \rightarrow PC, $ $1 \rightarrow GIE$ |  |  |  |  |

| Status Affected: | None                                       |  |  |  |  |

| MOVWF            | Move W to f                                |  |  |  |  |  |

|------------------|--------------------------------------------|--|--|--|--|--|

| Syntax:          | [ label ] MOVWF f                          |  |  |  |  |  |

| Operands:        | $0 \le f \le 127$                          |  |  |  |  |  |

| Operation:       | $(W) \rightarrow (f)$                      |  |  |  |  |  |

| Status Affected: | None                                       |  |  |  |  |  |

| Description:     | Move data from W register to register 'f'. |  |  |  |  |  |

| RETLW            | Return with Literal in W                                                                                                                                                |

|------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [label] RETLW k                                                                                                                                                         |

| Operands:        | $0 \le k \le 255$                                                                                                                                                       |

| Operation:       | $k \rightarrow (W);$<br>TOS $\rightarrow$ PC                                                                                                                            |

| Status Affected: | None                                                                                                                                                                    |

| Description:     | The W register is loaded with the eight-bit literal 'k'. The program counter is loaded from the top of the stack (the return address). This is a two-cycle instruction. |

Description:

| SWAPF            | Swap Nibbles in f                                                                                                                                                  |

|------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [label] SWAPF f,d                                                                                                                                                  |

| Operands:        | $0 \le f \le 127$<br>$d \in [0,1]$                                                                                                                                 |

| Operation:       | $(f<3:0>) \rightarrow (destination<7:4>),$<br>$(f<7:4>) \rightarrow (destination<3:0>)$                                                                            |

| Status Affected: | None                                                                                                                                                               |

| Description:     | The upper and lower nibbles of register 'f' are exchanged. If 'd' is 0, the result is placed in the W register. If 'd' is 1, the result is placed in register 'f'. |

The contents of the W register are XOR'ed with the eight-bit literal 'k'. The result is placed in

the W register.

| Description: The upper and lower nibbles of register 'f' are exchanged. If 'd' is 0, the result is placed in the W register. If 'd' is 1, the result is placed in register 'f'. |                               | W register with register 'f'. If 'd' is 0, the result is stored in the W register. If 'd' is 1, the result is stored back in register 'f'. |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------|

| XORLW                                                                                                                                                                           | Exclusive OR Literal with W   |                                                                                                                                            |

| Syntax:                                                                                                                                                                         | [label] XORLW k               |                                                                                                                                            |

| Operands:                                                                                                                                                                       | $0 \le k \le 255$             |                                                                                                                                            |

| Operation:                                                                                                                                                                      | (W) .XOR. $k \rightarrow (W)$ |                                                                                                                                            |

| Status Affected:                                                                                                                                                                | Z                             |                                                                                                                                            |

XORWF Syntax:

Operands:

Operation:

Status Affected:

Description:

**Exclusive OR W with f**

[label] XORWF f,d

(W) .XOR. (f)  $\rightarrow$  (destination)

Exclusive OR the contents of the

$\begin{array}{l} 0 \leq f \leq 127 \\ d \in \, \begin{bmatrix} 0,1 \end{bmatrix} \end{array}$

#### 14.13 PICDEM 3 Low Cost PIC16CXXX Demonstration Board

The PICDEM 3 demonstration board is a simple demonstration board that supports the PIC16C923 and PIC16C924 in the PLCC package. It will also support future 44-pin PLCC microcontrollers with an LCD Module. All the necessary hardware and software is included to run the basic demonstration programs. The user can program the sample microcontrollers provided with the PICDEM 3 demonstration board on a PRO MATE II device programmer, or a PICSTART Plus development programmer with an adapter socket, and easily test firmware. The MPLAB ICE in-circuit emulator may also be used with the PICDEM 3 demonstration board to test firmware. A prototype area has been provided to the user for adding hardware and connecting it to the microcontroller socket(s). Some of the features include a RS-232 interface, push button switches, a potentiometer for simulated analog input, a thermistor and separate headers for connection to an external LCD module and a keypad. Also provided on the PICDEM 3 demonstration board is a LCD panel, with 4 commons and 12 segments, that is capable of displaying time, temperature and day of the week. The PICDEM 3 demonstration board provides an additional RS-232 interface and Windows software for showing the demultiplexed LCD signals on a PC. A simple serial interface allows the user to construct a hardware demultiplexer for the LCD signals.

#### 14.14 PICDEM 17 Demonstration Board

The PICDEM 17 demonstration board is an evaluation board that demonstrates the capabilities of several Microchip microcontrollers, including PIC17C752, PIC17C756A, PIC17C762 and PIC17C766. All necessary hardware is included to run basic demo programs, which are supplied on a 3.5-inch disk. A programmed sample is included and the user may erase it and program it with the other sample programs using the PRO MATE II device programmer, or the PICSTART Plus development programmer, and easily debug and test the sample code. In addition, the PICDEM 17 demonstration board supports downloading of programs to and executing out of external FLASH memory on board. The PICDEM 17 demonstration board is also usable with the MPLAB ICE in-circuit emulator, or the PICMASTER emulator and all of the sample programs can be run and modified using either emulator. Additionally, a generous prototype area is available for user hardware.

# 14.15 KEELOQ Evaluation and Programming Tools

KEELOQ evaluation and programming tools support Microchip's HCS Secure Data Products. The HCS evaluation kit includes a LCD display to show changing codes, a decoder to decode transmissions and a programming interface to program test transmitters.

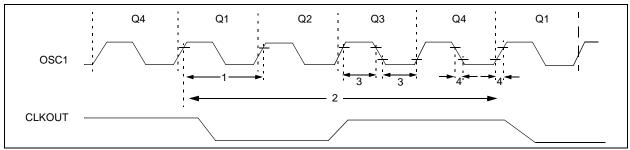

FIGURE 15-4: EXTERNAL CLOCK TIMING

TABLE 15-1: EXTERNAL CLOCK TIMING REQUIREMENTS

| Parameter<br>No. | Symbol | Characteristic                  | Min  | Typ† | Max    | Units | Conditions    |

|------------------|--------|---------------------------------|------|------|--------|-------|---------------|

|                  | Fosc   | External CLKIN Frequency        | DC   |      | 1      | MHz   | XT osc mode   |

|                  |        | (Note 1)                        | DC   | _    | 20     | MHz   | HS osc mode   |

|                  |        |                                 | DC   | _    | 32     | kHz   | LP osc mode   |

|                  |        | Oscillator Frequency            | DC   | _    | 4      | MHz   | RC osc mode   |

|                  |        | (Note 1)                        | 0.1  | _    | 4      | MHz   | XT osc mode   |

|                  |        |                                 | 4    | _    | 20     | MHz   | HS osc mode   |

|                  |        |                                 | 5    | _    | 200    | kHz   | LP osc mode   |

| 1                | Tosc   | External CLKIN Period           | 1000 | _    |        | ns    | XT osc mode   |

|                  |        | (Note 1)                        | 50   | _    | _      | ns    | HS osc mode   |

|                  |        |                                 | 5    | 1    | _      | ms    | LP osc mode   |

|                  |        | Oscillator Period               | 250  | _    | _      | ns    | RC osc mode   |

|                  |        | (Note 1)                        | 250  | _    | 10,000 | ns    | XT osc mode   |

|                  |        |                                 | 50   | _    | 250    | ns    | HS osc mode   |

|                  |        |                                 | 5    | 1    |        | ms    | LP osc mode   |

| 2                | Tcy    | Instruction Cycle Time (Note 1) | 200  | Tcy  | DC     | ns    | Tcy = 4/Fosc  |

| 3                | TosL,  | External Clock in (OSC1)        | 500  |      | _      | ns    | XT oscillator |

|                  | TosH   | High or Low Time                | 2.5  | _    |        | ms    | LP oscillator |

|                  |        |                                 | 15   |      |        | ns    | HS oscillator |

| 4                | TosR,  | External Clock in (OSC1)        | _    | _    | 25     | ns    | XT oscillator |

|                  | TosF   | Rise or Fall Time               | _    | _    | 50     | ns    | LP oscillator |

|                  |        |                                 | _    | _    | 15     | ns    | HS oscillator |

<sup>†</sup> Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

Note 1: Instruction cycle period (TCY) equals four times the input oscillator time-base period. All specified values are based on characterization data for that particular oscillator type under standard operating conditions, with the device executing code. Exceeding these specified limits may result in an unstable oscillator operation and/or higher than expected current consumption. All devices are tested to operate at "min." values with an external clock applied to the OSC1/CLKIN pin. When an external clock input is used, the "max." cycle time limit is "DC" (no clock) for all devices.

FIGURE 15-10: PARALLEL SLAVE PORT TIMING (PIC16F74/77 DEVICES ONLY)

TABLE 15-6: PARALLEL SLAVE PORT REQUIREMENTS (PIC16F74/77 DEVICES ONLY)

| Parameter No. | Symbol   | Characteristic                            |                       |          | Тур† | Max      | Units    | Conditions          |

|---------------|----------|-------------------------------------------|-----------------------|----------|------|----------|----------|---------------------|

| 62            | TdtV2wrH | Data in valid before WR↑ or CS1           | (setup time)          | 20<br>25 | _    | 1 1      | ns<br>ns | Extended range only |

| 63*           | TwrH2dtl | WR↑ or CS↑ to data in invalid (hold time) | Standard(F)           | 20       | _    | _        | ns       |                     |

|               |          |                                           | Extended( <b>LF</b> ) | 35       | _    | _        | ns       |                     |

| 64            | TrdL2dtV | RD↓ and CS↓ to data out valid             |                       | _        | _    | 80<br>90 | ns<br>ns | Extended range only |

| 65            | TrdH2dtl | RD↑ or CS↓ to data out invalid            |                       | 10       | _    | 30       | ns       |                     |

<sup>\*</sup> These parameters are characterized but not tested.

<sup>†</sup> Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

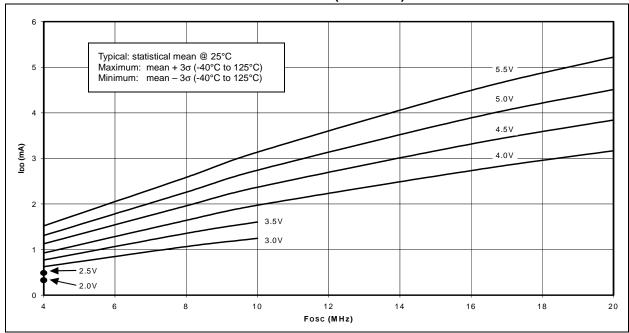

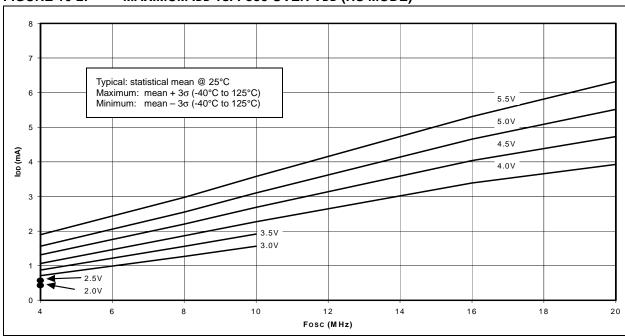

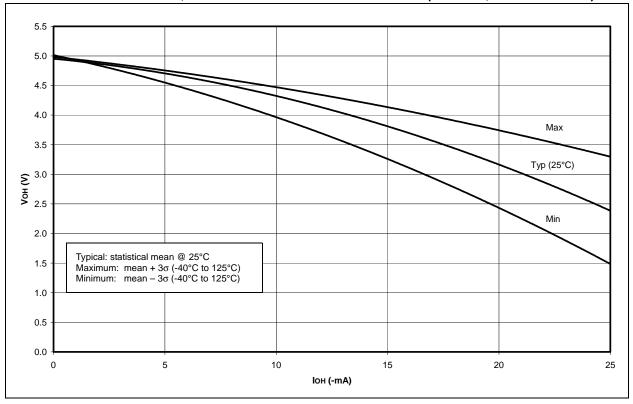

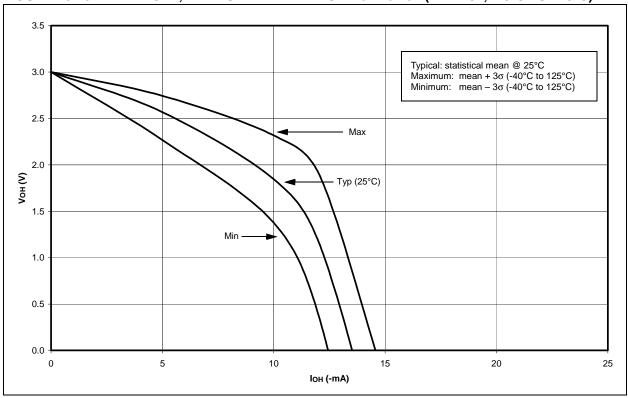

#### 16.0 DC AND AC CHARACTERISTICS GRAPHS AND TABLES

**Note:** The graphs and tables provided following this note are a statistical summary based on a limited number of samples and are provided for informational purposes only. The performance characteristics listed herein are not tested or guaranteed. In some graphs or tables, the data presented may be outside the specified operating range (e.g., outside specified power supply range) and therefore, outside the warranted range.

"Typical" represents the mean of the distribution at 25°C. "Maximum" or "minimum" represents (mean +  $3\sigma$ ) or (mean -  $3\sigma$ ) respectively, where  $\sigma$  is a standard deviation, over the whole temperature range.

FIGURE 16-1: TYPICAL IDD vs. Fosc OVER VDD (HS MODE)

FIGURE 16-2: MAXIMUM IDD vs. Fosc OVER VDD (HS MODE)

FIGURE 16-15: TYPICAL, MINIMUM AND MAXIMUM VOH vs. IOH (VDD = 5V, -40°C TO 125°C)

FIGURE 16-16: TYPICAL, MINIMUM AND MAXIMUM VOH vs. IOH (VDD = 3V, -40°C TO 125°C)

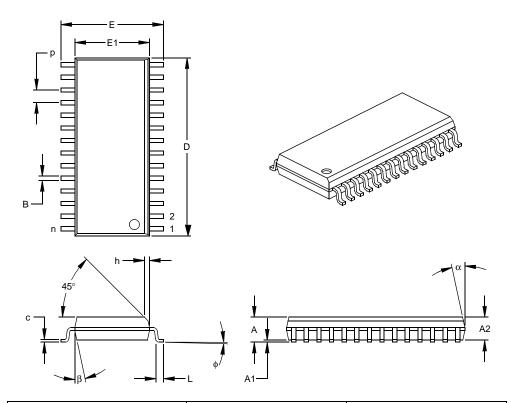

### 28-Lead Plastic Small Outline (SO) - Wide, 300 mil (SOIC)

|                          | Units  | INCHES* |             |      | N     | 3     |       |

|--------------------------|--------|---------|-------------|------|-------|-------|-------|

| Dimension                | Limits | MIN     | MIN NOM MAX |      |       | NOM   | MAX   |

| Number of Pins           | n      |         | 28          |      |       | 28    |       |

| Pitch                    | р      |         | .050        |      |       | 1.27  |       |

| Overall Height           | Α      | .093    | .099        | .104 | 2.36  | 2.50  | 2.64  |

| Molded Package Thickness | A2     | .088    | .091        | .094 | 2.24  | 2.31  | 2.39  |

| Standoff §               | A1     | .004    | .008        | .012 | 0.10  | 0.20  | 0.30  |

| Overall Width            | Е      | .394    | .407        | .420 | 10.01 | 10.34 | 10.67 |

| Molded Package Width     | E1     | .288    | .295        | .299 | 7.32  | 7.49  | 7.59  |

| Overall Length           | D      | .695    | .704        | .712 | 17.65 | 17.87 | 18.08 |

| Chamfer Distance         | h      | .010    | .020        | .029 | 0.25  | 0.50  | 0.74  |

| Foot Length              | L      | .016    | .033        | .050 | 0.41  | 0.84  | 1.27  |

| Foot Angle Top           | ф      | 0       | 4           | 8    | 0     | 4     | 8     |

| Lead Thickness           | С      | .009    | .011        | .013 | 0.23  | 0.28  | 0.33  |

| Lead Width               | В      | .014    | .017        | .020 | 0.36  | 0.42  | 0.51  |

| Mold Draft Angle Top     | α      | 0       | 12          | 15   | 0     | 12    | 15    |

| Mold Draft Angle Bottom  | β      | 0       | 12          | 15   | 0     | 12    | 15    |

Dimensions D and E1 do not include mold flash or protrusions. Mold flash or protrusions shall not exceed .010" (0.254mm) per side.

JEDEC Equivalent: MS-013 Drawing No. C04-052

<sup>\*</sup> Controlling Parameter § Significant Characteristic

#### **APPENDIX A: REVISION HISTORY**

| Version | Date | Revision Description                                                                                                                                                       |

|---------|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| A       | 2000 | This is a new data sheet. However, these devices are similar to the PIC16C7X devices found in the PIC16C7X Data Sheet (DS30390) or the PIC16F87X devices (DS30292).        |

| В       | 2001 | Final data sheet. Includes device characterization data. Addition of extended temperature devices. Addition of 28-pin MLF package. Minor typographic revisions throughout. |

# APPENDIX B: DEVICE DIFFERENCES

The differences between the devices in this data sheet are listed in Table B-1.

TABLE B-1: DEVICE DIFFERENCES

| Difference                             | PIC16F73                                                | PIC16F74                                  | PIC16F76                                                | PIC16F77                                  |

|----------------------------------------|---------------------------------------------------------|-------------------------------------------|---------------------------------------------------------|-------------------------------------------|

| FLASH Program Memory<br>(14-bit words) | 4K                                                      | 4K                                        | 8K                                                      | 8K                                        |

| Data Memory (bytes)                    | 192                                                     | 192                                       | 368                                                     | 368                                       |

| I/O Ports                              | 3                                                       | 5                                         | 3                                                       | 5                                         |

| A/D                                    | 5 channels,<br>8 bits                                   | 8 channels,<br>8 bits                     | 5 channels,<br>8 bits                                   | 8 channels,<br>8 bits                     |

| Parallel Slave Port                    | no                                                      | yes                                       | no                                                      | yes                                       |

| Interrupt Sources                      | 11                                                      | 12                                        | 11                                                      | 12                                        |

| Packages                               | 28-pin PDIP<br>28-pin SOIC<br>28-pin SSOP<br>28-pin MLF | 40-pin PDIP<br>44-pin TQFP<br>44-pin PLCC | 28-pin PDIP<br>28-pin SOIC<br>28-pin SSOP<br>28-pin MLF | 40-pin PDIP<br>44-pin TQFP<br>44-pin PLCC |

| PORTE Register37                                      | RCSTA Register                                   |            |

|-------------------------------------------------------|--------------------------------------------------|------------|

| Postscaler, WDT                                       | CREN bit                                         | 70         |

| Assignment (PSA bit)20                                | OERR bit7                                        | 70         |

| Rate Select (PS2:PS0 bits)20                          | SPEN bit                                         | 39         |

| Power-down Mode. See SLEEP                            | SREN bit7                                        | 70         |

| Power-on Reset (POR)89, 93, 95, 96                    | RD0/PSP0 Pin1                                    | 12         |

| Oscillator Start-up Timer (OST)89, 94                 | RD1/PSP1 Pin1                                    | 12         |

| POR Status (POR bit)25                                | RD2/PSP2 Pin1                                    | 12         |

| Power Control (PCON) Register95                       | RD3/PSP3 Pin1                                    |            |

| Power-down (PD bit)93                                 | RD4/PSP4 Pin1                                    | 12         |

| Power-up <u>Timer (PWRT)</u> 89, 94                   | RD5/PSP5 Pin1                                    | 12         |

| Time-out (TO bit)                                     | RD6/PSP6 Pin1                                    |            |

| PR2 Register51                                        | RD7/ <u>PS</u> P7 Pin1                           | 12         |

| Prescaler, Timer0                                     | RE0/ <u>RD/</u> AN5 Pin 1                        | 12         |

| Assignment (PSA bit)20                                | RE1/ <u>WR</u> /AN6 Pin 1                        |            |

| Rate Select (PS2:PS0 bits)20                          | RE2/ <del>CS</del> /AN7 Pin1                     |            |

| PRO MATE II Universal Device Programmer115            | Read-Modify-Write Operations10                   |            |

| Program Counter                                       | Receive Overflow Indicator bit (SSPOV)6          |            |

| RESET Conditions95                                    | Register File1                                   | 13         |

| Program Memory29                                      | Registers                                        |            |

| Associated Registers30                                | ADCON0 (A/D Control 0)                           |            |

| Interrupt Vector13                                    | ADCON0 (A/D Control 0) Register                  |            |

| Memory and Stack Maps13                               | ADCON1 (A/D Control 1)                           |            |

| Operation During Code Protect30                       | ADCON1 (A/D Control 1) Register                  |            |

| Organization13                                        | ADRES (A/D Result)                               |            |

| Paging                                                | CCP1CON/CCP2CON (CCP Control) Registers 5        |            |

| PMADR Register29                                      | Configuration Word Register                      |            |

| PMADRH Register                                       | Initialization Conditions (table)96—9            |            |

| Reading FLASH                                         | INTCON (Interrupt Control)                       |            |

| Reading, PMADRIL Register                             | INTCON (Interrupt Control) Register              |            |

| Reading, PMADRH Register29                            | OPTION_REG                                       |            |

| Reading, PMDATA Register                              | OPTION_REG Register20, 4                         |            |

| Reading, PMDATA Register29 Reading, PMDATH Register29 | PCON (Power Control)                             |            |

| RESET Vector                                          | PIE1 (Peripheral Interrupt Enable 1)             |            |

| Program Verification                                  | PIE1 (Peripheral Interrupt Enable 1) Register    |            |

| Programming Pin (VPP)                                 | PIE2 (Peripheral Interrupt Enable 1) Register    |            |

| Programming, Device Instructions                      | PIE2 (Peripheral Interrupt Enable 2) Register    |            |

| PUSH                                                  | PIR1 (Peripheral Interrupt Request 1)            |            |

| _                                                     | PIR1 (Peripheral Interrupt Request 1) Register 2 |            |

| R                                                     | PIR2 (Peripheral Interrupt Request 2)            |            |

| R/W bit60, 66, 67                                     | PIR2 (Peripheral Interrupt Request 2) Register 2 |            |

| RA0/AN0 Pin                                           | PMCON1 (Program Memory Control 1)                |            |

| RA1/AN1 Pin                                           | Register2                                        | 29         |

| RA2/AN2 Pin                                           | RCSTA (Receive Status and Control) Register 7    |            |

| RA3/AN3/VREF Pin                                      | Special Function, Summary16-1                    | 18         |

| RA4/ <u>T0</u> CKI Pin                                | SSPCON (Sync Serial Port Control) Register 6     | 31         |

| RA5/SS/AN4 Pin                                        | SSPSTAT (Sync Serial Port Status) Register 6     | 30         |

| RAM. See Data Memory                                  | STATUS Register1                                 | 19         |

| RB0/INT Pin9, 11                                      | T1CON (Timer 1 Control) Register4                | 17         |

| RB1 Pin9, 11                                          | T2CON (Timer2 Control) Register 5                |            |

| RB2 Pin9, 11                                          | TRISE Register3                                  |            |

| RB3/PGM Pin                                           | TXSTA (Transmit Status and Control) Register 6   | 39         |

| RB4 Pin9, 11                                          | RESET89, 9                                       |            |

| RB5 Pin                                               | Brown-out Reset (BOR). See Brown-out Reset (BOR) |            |

| RB6/PGC Pin                                           | MCLR Reset. See MCLR                             |            |

| RB7/PGD Pin                                           | Power-on Reset (POR). See Power-on Reset (POR)   | _          |

| RC0/T1OSO/T1CKI Pin                                   | RESET Conditions for All Registers               |            |

| RC1/T10SI/CCP2 Pin                                    | RESET Conditions for PCON Register               |            |

| RC2/CCP1 Pin                                          | RESET Conditions for Program Counter             |            |

| RC3/SCK/SCL Pin                                       | RESET Conditions for STATUS Register             | <i>1</i> 5 |

| RC4/SDI/SDA Pin                                       | RESET                                            |            |

| RC5/SDO Pin                                           | WDT Reset. See Watchdog Timer (WDT)              | - 4        |

| RC7/RX/DT Pin                                         | Revision History16                               | ונ         |