Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                         |

|----------------------------|-------------------------------------------------------------------------|

| Product Status             | Active                                                                  |

| Core Processor             | PIC                                                                     |

| Core Size                  | 8-Bit                                                                   |

| Speed                      | 20MHz                                                                   |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                                       |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                   |

| Number of I/O              | 22                                                                      |

| Program Memory Size        | 14KB (8K x 14)                                                          |

| Program Memory Type        | FLASH                                                                   |

| EEPROM Size                | -                                                                       |

| RAM Size                   | 368 x 8                                                                 |

| Voltage - Supply (Vcc/Vdd) | 4V ~ 5.5V                                                               |

| Data Converters            | A/D 5x8b                                                                |

| Oscillator Type            | External                                                                |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                       |

| Mounting Type              | Surface Mount                                                           |

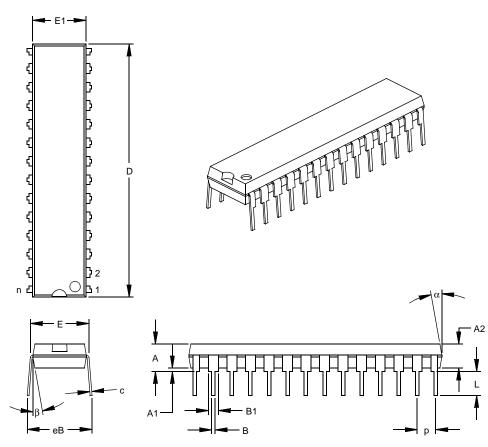

| Package / Case             | 28-SOIC (0.295", 7.50mm Width)                                          |

| Supplier Device Package    | 28-SOIC                                                                 |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16f76-i-so |

|                            |                                                                         |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

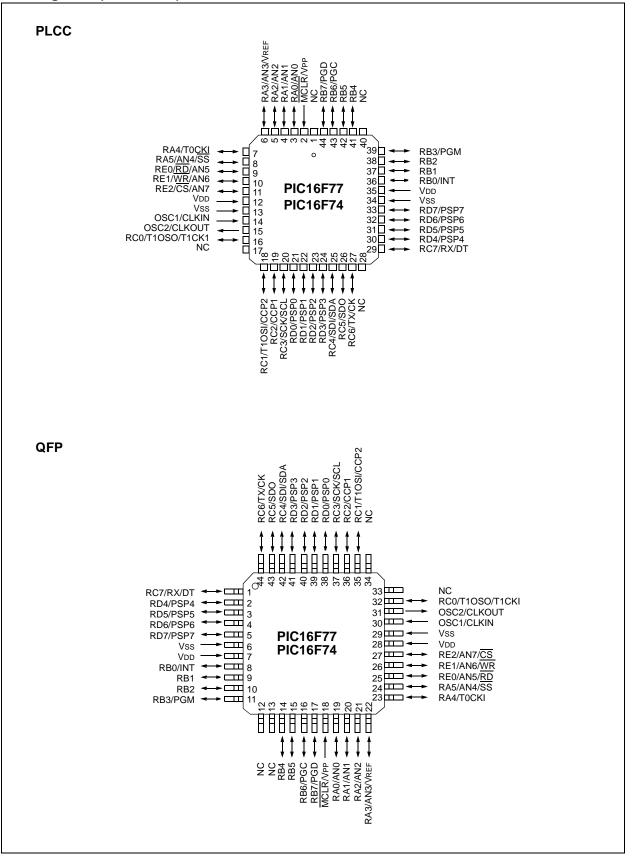

### **Pin Diagrams (Continued)**

#### PIC16F73 AND PIC16F76 PINOUT DESCRIPTION **TABLE 1-2:**

| Pin Name          | DIP<br>SSOP<br>SOIC<br>Pin# | MLF<br>Pin# | I/O/P<br>Type | Buffer<br>Type         | Description                                                                                                                                                      |

|-------------------|-----------------------------|-------------|---------------|------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| OSC1/CLKI<br>OSC1 | 9                           | 6           | Ι             | ST/CMOS <sup>(3)</sup> | Oscillator crystal or external clock input.<br>Oscillator crystal input or external clock source input. ST<br>buffer when configured in RC mode. Otherwise CMOS. |

| CLKI              |                             |             | I             |                        | External clock source input. Always associated with pin<br>function OSC1 (see OSC1/CLKI, OSC2/CLKO pins).                                                        |

| OSC2/CLKO<br>OSC2 | 10                          | 7           | 0             | _                      | Oscillator crystal or clock output.<br>Oscillator crystal output.<br>Connects to crystal or resonator in Crystal Oscillator<br>mode.                             |

| CLKO              |                             |             | 0             |                        | In RC mode, OSC2 pin outputs CLKO, which has 1/4 the frequency of OSC1 and denotes the instruction cycle rate.                                                   |

| MCLR/VPP<br>MCLR  | 1                           | 26          | I             | ST                     | Master Clear (input) or programming voltage (output).<br>Master Clear (Reset) input. This pin is an active low<br>RESET to the device.                           |

| Vpp               |                             |             | Р             |                        | Programming voltage input.                                                                                                                                       |

|                   |                             |             |               |                        | PORTA is a bi-directional I/O port.                                                                                                                              |

| RA0/AN0           | 2                           | 27          |               | TTL                    |                                                                                                                                                                  |

| RA0<br>AN0        |                             |             | I/O           |                        | Digital I/O.<br>Analog input 0.                                                                                                                                  |

| RA1/AN1           | 3                           | 28          | 1             | TTL                    | Analog input 0.                                                                                                                                                  |

| RA1/ANT<br>RA1    | 3                           | 20          | I/O           | 116                    | Digital I/O.                                                                                                                                                     |

| AN1               |                             |             | "c            |                        | Analog input 1.                                                                                                                                                  |

| RA2/AN2           | 4                           | 1           |               | TTL                    |                                                                                                                                                                  |

| RA2               |                             |             | I/O           |                        | Digital I/O.                                                                                                                                                     |

| AN2               |                             |             | I             |                        | Analog input 2.                                                                                                                                                  |

| RA3/AN3/VREF      | 5                           | 2           |               | TTL                    |                                                                                                                                                                  |

| RA3               |                             |             | I/O           |                        | Digital I/O.                                                                                                                                                     |

| AN3               |                             |             | I             |                        | Analog input 3.                                                                                                                                                  |

|                   | 0                           |             | I             | 07                     | A/D reference voltage input.                                                                                                                                     |

| RA4/T0CKI<br>RA4  | 6                           | 4           | I/O           | ST                     | Digital I/O – Open drain when configured as output.                                                                                                              |

| TOCKI             |                             |             | "U            |                        | Timer0 external clock input.                                                                                                                                     |

| RA5/SS/AN4        | 7                           | 5           |               | TTL                    |                                                                                                                                                                  |

| RA5               |                             | -           | I/O           |                        | Digital I/O.                                                                                                                                                     |

| SS                |                             |             | Ι             |                        | SPI slave select input.                                                                                                                                          |

| AN4               |                             |             | Ι             |                        | Analog input 4.                                                                                                                                                  |

| Legend: I = input | tucod                       | O = out     | put           | I/O = inpu             | ut/output P = power                                                                                                                                              |

— = Not used TTL = TTL input ST = Schmitt Trigger input

Note 1: This buffer is a Schmitt Trigger input when configured as the external interrupt.

This buffer is a Schmitt Trigger input when used in Serial Programming mode.

This buffer is a Schmitt Trigger input when configured in RC Oscillator mode and a CMOS input otherwise.

#### TABLE 1-3:PIC16F74 AND PIC16F77 PINOUT DESCRIPTION

| OSC1/CLKI<br>OSC1<br>CLKI<br>OSC2/CLKO<br>OSC2<br>CLKO<br>MCLR/VPP<br>MCLR<br>VPP | 13 | 14<br>15 | 30<br>31 | 1        | ST/CMOS <sup>(4)</sup> | Oscillator crystal or external clock input.<br>Oscillator crystal input or external clock source input.<br>ST buffer when configured in RC mode. Otherwise<br>CMOS.<br>External clock source input. Always associated with pin |

|-----------------------------------------------------------------------------------|----|----------|----------|----------|------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| CLKI<br>OSC2/CLKO<br>OSC2<br>CLKO<br><u>MCLR/VPP</u><br>MCLR                      | 14 | 15       | 31       | I        |                        | Oscillator crystal input or external clock source input.<br>ST buffer when configured in RC mode. Otherwise<br>CMOS.<br>External clock source input. Always associated with pin                                                |

| OSC2/CLKO<br>OSC2<br>CLKO<br>MCLR/VPP<br>MCLR                                     | 14 | 15       | 31       |          |                        | CMOS.<br>External clock source input. Always associated with pin                                                                                                                                                               |

| OSC2/CLKO<br>OSC2<br>CLKO<br>MCLR/VPP<br>MCLR                                     | 14 | 15       | 31       |          |                        | External clock source input. Always associated with pin                                                                                                                                                                        |

| OSC2<br>CLKO<br>MCLR/VPP<br>MCLR                                                  | 14 | 15       | 31       |          |                        |                                                                                                                                                                                                                                |

| OSC2<br>CLKO<br>MCLR/VPP<br>MCLR                                                  | 14 | 15       | 31       | 0        |                        | function OSC1 (see OSC1/CLKI, OSC2/CLKO pins).                                                                                                                                                                                 |

| CLKO<br>MCLR/VPP<br>MCLR                                                          |    |          |          | <u> </u> | I —                    | Oscillator crystal or clock output.                                                                                                                                                                                            |

| MCLR/Vpp<br>MCLR                                                                  |    |          |          | 0        |                        | Oscillator crystal output.                                                                                                                                                                                                     |

| MCLR/Vpp<br>MCLR                                                                  |    |          |          |          |                        | Connects to crystal or resonator in Crystal Oscillator                                                                                                                                                                         |

| MCLR/Vpp<br>MCLR                                                                  |    |          |          |          |                        | mode.                                                                                                                                                                                                                          |

| MCLR                                                                              |    |          |          | 0        |                        | In RC mode, OSC2 pin outputs CLKO, which has 1/4                                                                                                                                                                               |

| MCLR                                                                              |    |          |          |          |                        | the frequency of OSC1 and denotes the instruction                                                                                                                                                                              |

| MCLR                                                                              |    |          |          |          |                        | cycle rate.                                                                                                                                                                                                                    |

|                                                                                   | 1  | 2        | 18       |          | ST                     | Master Clear (input) or programming voltage (output).                                                                                                                                                                          |

| Vpp                                                                               |    |          |          | I        |                        | Master Clear (Reset) input. This pin is an active low                                                                                                                                                                          |

| VPP                                                                               |    |          |          |          |                        | RESET to the device.                                                                                                                                                                                                           |

|                                                                                   |    |          |          | Р        |                        | Programming voltage input.                                                                                                                                                                                                     |

|                                                                                   |    |          |          |          |                        | PORTA is a bi-directional I/O port.                                                                                                                                                                                            |

| RA0/AN0                                                                           | 2  | 3        | 19       |          | TTL                    |                                                                                                                                                                                                                                |

| RA0                                                                               |    |          |          | I/O      |                        | Digital I/O.                                                                                                                                                                                                                   |

| AN0                                                                               |    |          |          | I        |                        | Analog input 0.                                                                                                                                                                                                                |

| RA1/AN1                                                                           | 3  | 4        | 20       |          | TTL                    |                                                                                                                                                                                                                                |

| RA1                                                                               |    |          |          | I/O      |                        | Digital I/O.                                                                                                                                                                                                                   |

| AN1                                                                               |    |          |          | I        |                        | Analog input 1.                                                                                                                                                                                                                |

| RA2/AN2                                                                           | 4  | 5        | 21       |          | TTL                    |                                                                                                                                                                                                                                |

| RA2                                                                               |    |          |          | I/O      |                        | Digital I/O.                                                                                                                                                                                                                   |

| AN2                                                                               |    |          |          | I        |                        | Analog input 2.                                                                                                                                                                                                                |

| RA3/AN3/Vref                                                                      | 5  | 6        | 22       |          | TTL                    |                                                                                                                                                                                                                                |

| RA3                                                                               |    |          |          | I/O      |                        | Digital I/O.                                                                                                                                                                                                                   |

| AN3                                                                               |    |          |          | I        |                        | Analog input 3.                                                                                                                                                                                                                |

| VREF                                                                              |    |          |          | I        |                        | A/D reference voltage input.                                                                                                                                                                                                   |

| RA4/T0CKI                                                                         | 6  | 7        | 23       |          | ST                     |                                                                                                                                                                                                                                |

| RA4                                                                               |    |          |          | I/O      |                        | Digital I/O – Open drain when configured as output.                                                                                                                                                                            |

| TOCKI                                                                             |    |          |          | I        |                        | Timer0 external clock input.                                                                                                                                                                                                   |

| RA5/SS/AN4                                                                        | 7  | 8        | 24       |          | TTL                    |                                                                                                                                                                                                                                |

| RA5                                                                               |    | -        |          | I/O      |                        | Digital I/O.                                                                                                                                                                                                                   |

| SS                                                                                | 1  |          |          | 1        |                        | SPI slave select input.                                                                                                                                                                                                        |

| AN4                                                                               |    |          |          |          | 1                      |                                                                                                                                                                                                                                |

| Legend: I = inpu                                                                  |    | 1        |          |          |                        | Analog input 4.                                                                                                                                                                                                                |

— = Not used TTL = TTL input ST = Schmitt Trigger input

**Note 1:** This buffer is a Schmitt Trigger input when configured as an external interrupt.

2: This buffer is a Schmitt Trigger input when used in Serial Programming mode.

**3:** This buffer is a Schmitt Trigger input when configured as general purpose I/O and a TTL input when used in the Parallel Slave Port mode (for interfacing to a microprocessor bus).

4: This buffer is a Schmitt Trigger input when configured in RC Oscillator mode and a CMOS input otherwise.

| Pin Name        | DIP<br>Pin# | PLCC<br>Pin# | QFP<br>Pin# | I/O/P<br>Type | Buffer<br>Type        | Description                                              |

|-----------------|-------------|--------------|-------------|---------------|-----------------------|----------------------------------------------------------|

|                 |             |              |             |               |                       | PORTB is a bi-directional I/O port. PORTB can be softwar |

|                 |             |              |             |               |                       | programmed for internal weak pull-up on all inputs.      |

| RB0/INT         | 33          | 36           | 8           |               | TTL/ST <sup>(1)</sup> |                                                          |

| RB0             |             |              |             | I/O           |                       | Digital I/O.                                             |

| INT             |             |              |             | I             |                       | External interrupt.                                      |

| RB1             | 34          | 37           | 9           | I/O           | TTL                   | Digital I/O.                                             |

| RB2             | 35          | 38           | 10          | I/O           | TTL                   | Digital I/O.                                             |

| RB3/PGM         | 36          | 39           | 11          |               | TTL                   |                                                          |

| RB3             |             |              |             | I/O           |                       | Digital I/O.                                             |

| PGM             |             |              |             | I/O           |                       | Low voltage ICSP programming enable pin.                 |

| RB4             | 37          | 41           | 14          | I/O           | TTL                   | Digital I/O.                                             |

| RB5             | 38          | 42           | 15          | I/O           | TTL                   | Digital I/O.                                             |

| RB6/PGC         | 39          | 43           | 16          |               | TTL/ST <sup>(2)</sup> |                                                          |

| RB6             |             |              |             | I/O           |                       | Digital I/O.                                             |

| PGC             |             |              |             | I/O           |                       | In-Circuit Debugger and ICSP programming clock.          |

| RB7/PGD         | 40          | 44           | 17          |               | TTL/ST <sup>(2)</sup> |                                                          |

| RB7             |             |              |             | I/O           |                       | Digital I/O.                                             |

| PGD             |             |              |             | I/O           |                       | In-Circuit Debugger and ICSP programming data.           |

|                 |             |              |             |               |                       | PORTC is a bi-directional I/O port.                      |

| RC0/T1OSO/T1CKI | 15          | 16           | 32          |               | ST                    |                                                          |

| RC0             |             |              |             | I/O           |                       | Digital I/O.                                             |

| T1OSO           |             |              |             | 0             |                       | Timer1 oscillator output.                                |

| T1CKI           |             |              |             | I             |                       | Timer1 external clock input.                             |

| RC1/T1OSI/CCP2  | 16          | 18           | 35          |               | ST                    |                                                          |

| RC1             |             |              |             | I/O           |                       | Digital I/O.                                             |

| T1OSI           |             |              |             | 1/0           |                       | Timer1 oscillator input.                                 |

| CCP2            | 47          | 10           | 20          | 1/0           | OT                    | Capture2 input, Compare2 output, PWM2 output.            |

| RC2/CCP1<br>RC2 | 17          | 19           | 36          | I/O           | ST                    | Digital I/O.                                             |

| CCP1            |             |              |             | 1/O<br>1/O    |                       | Capture1 input/Compare1 output/PWM1 output               |

| RC3/SCK/SCL     | 18          | 20           | 37          | 1/0           | ST                    |                                                          |

| RC3             | 10          | 20           | 57          | I/O           | 31                    | Digital I/O                                              |

| SCK             |             |              |             | I/O           |                       | Synchronous serial clock input/output for SPI mode.      |

| SCL             |             |              |             | I/O           |                       | Synchronous serial clock input/output for $I^2C$ mode.   |

| RC4/SDI/SDA     | 23          | 25           | 42          |               | ST                    |                                                          |

| RC4             |             |              |             | I/O           |                       | Digital I/O.                                             |

| SDI             |             |              |             | I             |                       | SPI data in.                                             |

| SDA             |             |              |             | I/O           |                       | I <sup>2</sup> C data I/O.                               |

| RC5/SDO         | 24          | 26           | 43          |               | ST                    |                                                          |

| RC5             |             |              |             | I/O           |                       | Digital I/O.                                             |

| SDO             |             |              |             | 0             |                       | SPI data out.                                            |

| RC6/TX/CK       | 25          | 27           | 44          |               | ST                    |                                                          |

| RC6             |             |              |             | I/O           |                       | Digital I/O.                                             |

| ТХ              |             |              |             | 0             |                       | USART asynchronous transmit.                             |

| СК              |             |              |             | I/O           |                       | USART 1 synchronous clock.                               |

| RC7/RX/DT       | 26          | 29           | 1           |               | ST                    |                                                          |

| RC7             |             |              |             | I/O           |                       | Digital I/O.                                             |

| RX              |             |              |             |               |                       | USART asynchronous receive.                              |

| DT              |             |              |             | I/O           |                       | USART synchronous data.                                  |

| TABLE 1-3: | PIC16F74 AND PIC16F77 | PINOUT DESCRIPTION ( | (CONTINUED) |

|------------|-----------------------|----------------------|-------------|

|            |                       |                      |             |

**Note 1:** This buffer is a Schmitt Trigger input when configured as an external interrupt.

2: This buffer is a Schmitt Trigger input when used in Serial Programming mode.

3: This buffer is a Schmitt Trigger input when configured as general purpose I/O and a TTL input when used in the Parallel Slave Port mode (for interfacing to a microprocessor bus).

4: This buffer is a Schmitt Trigger input when configured in RC Oscillator mode and a CMOS input otherwise.

| Address              | Name       | Bit 7                        | Bit 6                          | Bit 5                      | Bit 4          | Bit 3        | Bit 2           | Bit 1         | Bit 0        | Value on:<br>POR,<br>BOR | Details<br>on page |

|----------------------|------------|------------------------------|--------------------------------|----------------------------|----------------|--------------|-----------------|---------------|--------------|--------------------------|--------------------|

| Bank 1               |            |                              |                                |                            |                |              |                 |               |              |                          |                    |

| 80h <sup>(4)</sup>   | INDF       | Addressin                    | g this locatio                 | n uses conte               | ents of FSR to | address dat  | a memory (r     | not a physica | al register) | 0000 0000                | 27, 96             |

| 81h                  | OPTION_REG | RBPU                         | INTEDG                         | TOCS                       | T0SE           | PSA          | PS2             | PS1           | PS0          | 1111 1111                | 20, 44, 96         |

| 82h <sup>(4)</sup>   | PCL        | Program C                    | Counter's (PC                  | C) Least Sigr              | ificant Byte   |              |                 |               |              | 0000 0000                | 26, 96             |

| 83h <sup>(4)</sup>   | STATUS     | IRP                          | RP1                            | RP0                        | TO             | PD           | Z               | DC            | С            | 0001 1xxx                | 19, 96             |

| 84h <sup>(4)</sup>   | FSR        | Indirect da                  | ata memory a                   | ddress point               | ier            |              |                 |               |              | xxxx xxxx                | 27, 96             |

| 85h                  | TRISA      |                              | _                              | PORTA Dat                  | a Direction Re | egister      |                 |               |              | 11 1111                  | 32, 96             |

| 86h                  | TRISB      | PORTB D                      | ata Direction                  | Register                   |                | •            |                 |               |              | 1111 1111                | 34, 96             |

| 87h                  | TRISC      | PORTC D                      | ata Direction                  | Register                   |                |              |                 |               |              | 1111 1111                | 35, 96             |

| 88h <sup>(5)</sup>   | TRISD      | PORTD D                      | ata Direction                  | Register                   |                |              |                 |               |              | 1111 1111                | 36, 96             |

| 89h <sup>(5)</sup>   | TRISE      | IBF                          | OBF                            | IBOV                       | PSPMODE        |              | PORTE Da        | ata Direction | Bits         | 0000 -111                | 38, 96             |

| 8Ah <sup>(1,4)</sup> | PCLATH     | _                            | _                              | _                          | Write Buffer f | or the upper | r 5 bits of the | Program C     | ounter       | 0 0000                   | 21,96              |

| 8Bh <sup>(4)</sup>   | INTCON     | GIE                          | PEIE                           | TMR0IE                     | INTE           | RBIE         | TMR0IF          | INTF          | RBIF         | 0000 000x                | 23, 96             |

| 8Ch                  | PIE1       | PSPIE <sup>(3)</sup>         | ADIE                           | RCIE                       | TXIE           | SSPIE        | CCP1IE          | TMR2IE        | TMR1IE       | 0000 0000                | 22,96              |

| 8Dh                  | PIE2       | _                            | _                              | _                          | _              | _            |                 | _             | CCP2IE       | 0                        | 24, 97             |

| 8Eh                  | PCON       | _                            | _                              | _                          | _              |              | _               | POR           | BOR          | dd                       | 25, 97             |

| 8Fh                  | —          | Unimplem                     | Unimplemented                  |                            |                |              |                 |               |              | _                        | _                  |

| 90h                  | —          | Unimplem                     | Unimplemented                  |                            |                |              |                 |               |              | _                        | _                  |

| 91h                  | —          | Unimplem                     | Unimplemented —                |                            |                |              |                 |               |              | —                        |                    |

| 92h                  | PR2        | Timer2 Pe                    | Timer2 Period Register 1111 11 |                            |                |              |                 |               |              | 1111 1111                | 52, 97             |

| 93h                  | SSPADD     | Synchrono                    | ous Serial Po                  | ort (I <sup>2</sup> C mode | ) Address Reg  | gister       |                 |               |              | 0000 0000                | 68, 97             |

| 94h                  | SSPSTAT    | SMP                          | CKE                            | D/A                        | Р              | S            | R/W             | UA            | BF           | 0000 0000                | 60, 97             |

| 95h                  | —          | Unimplemented —              |                                |                            |                |              |                 |               | —            | —                        |                    |

| 96h                  | —          | Unimplemented                |                                |                            |                |              |                 |               | —            | —                        |                    |

| 97h                  | —          | Unimplem                     | ented                          |                            |                |              | _               |               |              | —                        | —                  |

| 98h                  | TXSTA      | CSRC                         | TX9                            | TXEN                       | SYNC           |              | BRGH            | TRMT          | TX9D         | 0000 -010                | 69, 97             |

| 99h                  | SPBRG      | Baud Rate Generator Register |                                |                            |                |              |                 |               | 0000 0000    | 71, 97                   |                    |

| 9Ah                  | —          | Unimplem                     | ented                          |                            |                |              |                 |               |              | —                        |                    |

| 9Bh                  | —          | Unimplem                     | ented                          |                            |                |              |                 |               |              | -                        |                    |

| 9Ch                  | —          | Unimplem                     | ented                          |                            |                |              |                 |               |              | _                        |                    |

| 9Dh                  | —          | Unimplem                     | ented                          |                            |                |              |                 |               |              | _                        |                    |

| 9Eh                  | —          | Unimplem                     | ented                          |                            |                |              |                 |               |              | -                        |                    |

| 9Fh                  | ADCON1     | _                            | _                              | _                          | _              | _            | PCFG2           | PCFG1         | PCFG0        | 000                      | 84, 97             |

| TABLE 2-1: SPECIAL FUNCTION REGISTER SUMMARY (CONTINUED) |

|----------------------------------------------------------|

|----------------------------------------------------------|

$\label{eq:legend: Legend: Legend: u = unchanged, q = value depends on condition, - = unimplemented, read as '0', r = reserved.$ Shaded locations are unimplemented, read as '0'.

Note 1: The upper byte of the program counter is not directly accessible. PCLATH is a holding register for the PC<12:8>, whose contents are transferred to the upper byte of the program counter during branches (CALL or GOTO).

2: Other (non power-up) RESETS include external RESET through MCLR and Watchdog Timer Reset. 3: Bits PSPIE and PSPIF are reserved on the 28-pin devices; always maintain these bits clear.

4: These registers can be addressed from any bank.

5: PORTD, PORTE, TRISD, and TRISE are not physically implemented on the 28-pin devices, read as '0'.

6: This bit always reads as a '1'.

x = Bit is unknown

#### **PCON Register** 2.2.2.8

The Power Control (PCON) register contains flag bits to allow differentiation between a Power-on Reset (POR), a Brown-out Reset (BOR), a Watchdog Reset (WDT) and an external MCLR Reset.

BOR is unknown on POR. It must be set by Note: the user and checked on subsequent RESETS to see if BOR is clear, indicating a brown-out has occurred. The BOR status bit is not predictable if the brown-out circuit is disabled (by clearing the BODEN bit in the configuration word).

#### **REGISTER 2-8:** PCON REGISTER (ADDRESS 8Eh)

- n = Value at POR reset

|         | U-0                                                                                     | U-0         | U-0        | U-0         | U-0      | U-0         | R/W-0        | R/W-1  |  |

|---------|-----------------------------------------------------------------------------------------|-------------|------------|-------------|----------|-------------|--------------|--------|--|

|         | _                                                                                       | _           | _          |             | —        |             | POR          | BOR    |  |

|         | bit 7                                                                                   |             |            |             |          |             |              | bit 0  |  |

|         |                                                                                         |             |            |             |          |             |              |        |  |

| bit 7-2 | Unimplemented: Read as '0'                                                              |             |            |             |          |             |              |        |  |

| bit 1   | POR: Pow                                                                                | er-on Reset | Status bit |             |          |             |              |        |  |

|         | 1 = No Power-on Reset occurred                                                          |             |            |             |          |             |              |        |  |

|         | 0 = A Power-on Reset occurred (must be set in software after a Power-on Reset occurs)   |             |            |             |          |             |              | ccurs) |  |

| bit 0   | BOR: Brown-out Reset Status bit                                                         |             |            |             |          |             |              |        |  |

|         | 1 = No Brown-out Reset occurred                                                         |             |            |             |          |             |              |        |  |

|         | 0 = A Brown-out Reset occurred (must be set in software after a Brown-out Reset occurs) |             |            |             |          |             |              |        |  |

|         |                                                                                         |             |            |             |          |             |              |        |  |

|         | Legend:                                                                                 |             |            |             |          |             |              |        |  |

|         | R = Reada                                                                               | ble bit     | W = W      | ritable bit | U = Unim | plemented l | bit, read as | '0'    |  |

'0' = Bit is cleared

'1' = Bit is set

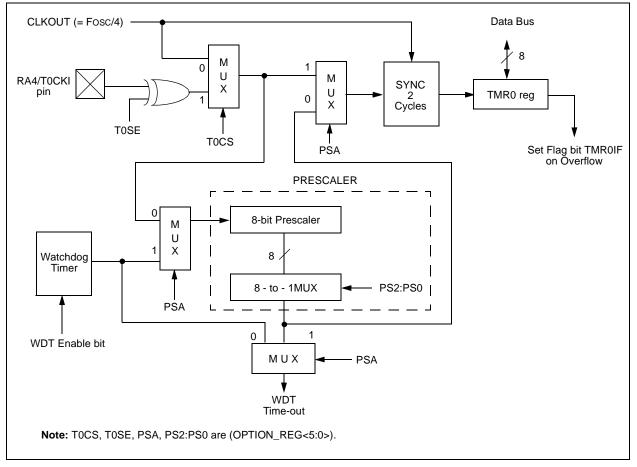

# 5.0 TIMER0 MODULE

The Timer0 module timer/counter has the following features:

- 8-bit timer/counter

- Readable and writable

- 8-bit software programmable prescaler

- · Internal or external clock select

- Interrupt on overflow from FFh to 00h

- Edge select for external clock

Additional information on the Timer0 module is available in the PICmicro<sup>™</sup> Mid-Range MCU Family Reference Manual (DS33023).

Figure 5-1 is a block diagram of the Timer0 module and the prescaler shared with the WDT.

Timer0 operation is controlled through the OPTION\_REG register (Register 5-1 on the following page). Timer mode is selected by clearing bit TOCS (OPTION\_REG<5>). In Timer mode, the Timer0 module will increment every instruction cycle (without prescaler). If the TMR0 register is written, the increment is inhibited for the following two instruction cycles. The user can work around this by writing an adjusted value to the TMR0 register.

Counter mode is selected by setting bit T0CS (OPTION\_REG<5>). In Counter mode, Timer0 will increment, either on every rising or falling edge of pin RA4/T0CKI. The incrementing edge is determined by the Timer0 Source Edge Select bit T0SE (OPTION\_REG<4>). Clearing bit T0SE selects the rising edge. Restrictions on the external clock input are discussed in detail in Section 5.2.

The prescaler is mutually exclusively shared between the Timer0 module and the Watchdog Timer. The prescaler is not readable or writable. Section 5.3 details the operation of the prescaler.

### 5.1 Timer0 Interrupt

The TMR0 interrupt is generated when the TMR0 register overflows from FFh to 00h. This overflow sets bit TMR0IF (INTCON<2>). The interrupt can be masked by clearing bit TMR0IE (INTCON<5>). Bit TMR0IF must be cleared in software by the Timer0 module Interrupt Service Routine, before re-enabling this interrupt. The TMR0 interrupt cannot awaken the processor from SLEEP, since the timer is shut-off during SLEEP.

| EGISTER 9-1: SSPSTAT: SYNC SERIAL PORT STATUS REGISTER (ADDRESS 94h)                                                                                  |                                                                                                                                                                     |  |  |  |  |  |  |  |  |  |  |  |

|-------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|--|--|--|--|--|

| R/W-0 R/W-0 R-0 R-0 R-0 R-0 R-0 R-0 R-0 R-0 R-0 R                                                                                                     | -0 R-0                                                                                                                                                              |  |  |  |  |  |  |  |  |  |  |  |

| SMP CKE D/A P S R/W U                                                                                                                                 | A BF                                                                                                                                                                |  |  |  |  |  |  |  |  |  |  |  |

| bit 7                                                                                                                                                 | bit C                                                                                                                                                               |  |  |  |  |  |  |  |  |  |  |  |

| bit 7 SMP: SPI Data Input Sample Phase bit                                                                                                            |                                                                                                                                                                     |  |  |  |  |  |  |  |  |  |  |  |

| SPI Master mode:                                                                                                                                      |                                                                                                                                                                     |  |  |  |  |  |  |  |  |  |  |  |

| 1 = Input data sampled at end of data output time                                                                                                     |                                                                                                                                                                     |  |  |  |  |  |  |  |  |  |  |  |

|                                                                                                                                                       | 0 = Input data sampled at middle of data output time (Microwire <sup>®</sup> )                                                                                      |  |  |  |  |  |  |  |  |  |  |  |

| <u>SPI Slave mode:</u><br>SMP must be cleared when SPI is used in Slave mode                                                                          |                                                                                                                                                                     |  |  |  |  |  |  |  |  |  |  |  |

| I <sup>2</sup> C mode:                                                                                                                                |                                                                                                                                                                     |  |  |  |  |  |  |  |  |  |  |  |

| This bit must be maintained clear                                                                                                                     |                                                                                                                                                                     |  |  |  |  |  |  |  |  |  |  |  |

| bit 6 <b>CKE</b> : SPI Clock Edge Select bit (Figure 9-2, Figure 9-3, and Figure 9-4)                                                                 |                                                                                                                                                                     |  |  |  |  |  |  |  |  |  |  |  |

| <u>SPI mode, CKP = 0:</u>                                                                                                                             |                                                                                                                                                                     |  |  |  |  |  |  |  |  |  |  |  |

| <ul> <li>1 = Data transmitted on rising edge of SCK (Microwire<sup>®</sup> alternate)</li> <li>0 = Data transmitted on falling edge of SCK</li> </ul> |                                                                                                                                                                     |  |  |  |  |  |  |  |  |  |  |  |

| SPI mode, $CKP = 1$ :                                                                                                                                 |                                                                                                                                                                     |  |  |  |  |  |  |  |  |  |  |  |

| 1 = Data transmitted on falling edge of SCK (Microwire <sup>®</sup> default)                                                                          |                                                                                                                                                                     |  |  |  |  |  |  |  |  |  |  |  |

| 0 = Data transmitted on rising edge of SCK                                                                                                            |                                                                                                                                                                     |  |  |  |  |  |  |  |  |  |  |  |

| I <sup>2</sup> C mode:<br>This bit must be maintained clear                                                                                           |                                                                                                                                                                     |  |  |  |  |  |  |  |  |  |  |  |

| bit 5 <b>D/A</b> : Data/Address bit (I <sup>2</sup> C mode only)                                                                                      |                                                                                                                                                                     |  |  |  |  |  |  |  |  |  |  |  |

| 1 = Indicates that the last byte received or transmitted was data                                                                                     |                                                                                                                                                                     |  |  |  |  |  |  |  |  |  |  |  |

| 0 = Indicates that the last byte received or transmitted was address                                                                                  |                                                                                                                                                                     |  |  |  |  |  |  |  |  |  |  |  |

| bit 4 <b>P</b> : STOP bit (I <sup>2</sup> C mode only)                                                                                                |                                                                                                                                                                     |  |  |  |  |  |  |  |  |  |  |  |

|                                                                                                                                                       | This bit is cleared when the SSP module is disabled, or when the START bit is detected last.<br>SSPEN is cleared.                                                   |  |  |  |  |  |  |  |  |  |  |  |

|                                                                                                                                                       | 1 = Indicates that a STOP bit has been detected last (this bit is '0' on RESET)                                                                                     |  |  |  |  |  |  |  |  |  |  |  |

| 0 = STOP bit was not detected last                                                                                                                    |                                                                                                                                                                     |  |  |  |  |  |  |  |  |  |  |  |

|                                                                                                                                                       | S: START bit (I <sup>2</sup> C mode only)                                                                                                                           |  |  |  |  |  |  |  |  |  |  |  |

| This bit is cleared when the SSP module is disabled, or when the STOP bit is detected I<br>SSPEN is cleared.                                          |                                                                                                                                                                     |  |  |  |  |  |  |  |  |  |  |  |

| 1 = Indicates that a START bit has been detected last (this bit is '0' on RESET                                                                       | )                                                                                                                                                                   |  |  |  |  |  |  |  |  |  |  |  |

| 0 = START bit was not detected last                                                                                                                   |                                                                                                                                                                     |  |  |  |  |  |  |  |  |  |  |  |

| bit 2 <b>R/W</b> : Read/Write bit Information (I <sup>2</sup> C mode only)                                                                            |                                                                                                                                                                     |  |  |  |  |  |  |  |  |  |  |  |

|                                                                                                                                                       | This bit holds the R/W bit information following the last address match. This bit is only valid from the address match to the next START bit, STOP bit, or ACK bit. |  |  |  |  |  |  |  |  |  |  |  |

| 1 = Read                                                                                                                                              |                                                                                                                                                                     |  |  |  |  |  |  |  |  |  |  |  |

| 0 = Write                                                                                                                                             |                                                                                                                                                                     |  |  |  |  |  |  |  |  |  |  |  |

| bit 1 <b>UA</b> : Update Address bit (10-bit I <sup>2</sup> C mode only)                                                                              |                                                                                                                                                                     |  |  |  |  |  |  |  |  |  |  |  |

| 1 = Indicates that the user needs to update the address in the SSPADD regist                                                                          | er                                                                                                                                                                  |  |  |  |  |  |  |  |  |  |  |  |

| <ul> <li>0 = Address does not need to be updated</li> <li>bit 0</li> <li><b>BF</b>: Buffer Full Status bit</li> </ul>                                 |                                                                                                                                                                     |  |  |  |  |  |  |  |  |  |  |  |

| Receive (SPI and I <sup>2</sup> C modes):                                                                                                             |                                                                                                                                                                     |  |  |  |  |  |  |  |  |  |  |  |

|                                                                                                                                                       | 1 = Receive complete, SSPBUF is full                                                                                                                                |  |  |  |  |  |  |  |  |  |  |  |

| 0 = Receive not complete, SSPBUF is empty                                                                                                             |                                                                                                                                                                     |  |  |  |  |  |  |  |  |  |  |  |

| Transmit (I <sup>2</sup> C mode only):                                                                                                                |                                                                                                                                                                     |  |  |  |  |  |  |  |  |  |  |  |

| 1 = Transmit in progress, SSPBUF is full                                                                                                              |                                                                                                                                                                     |  |  |  |  |  |  |  |  |  |  |  |

| 0 = Transmit complete, SSPBUF is empty                                                                                                                |                                                                                                                                                                     |  |  |  |  |  |  |  |  |  |  |  |

| Legend:                                                                                                                                               |                                                                                                                                                                     |  |  |  |  |  |  |  |  |  |  |  |

| R = Readable bit W = Writable bit U = Unimplemented bit, rea                                                                                          | id as '0'                                                                                                                                                           |  |  |  |  |  |  |  |  |  |  |  |

| - n = Value at POR reset $'1'$ = Bit is set $'0'$ = Bit is cleared x = B                                                                              | Bit is unknown                                                                                                                                                      |  |  |  |  |  |  |  |  |  |  |  |

\_

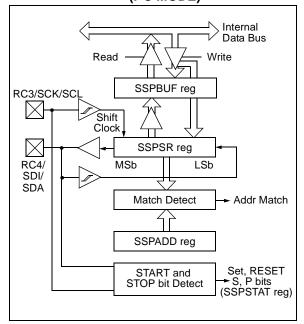

# 9.3 SSP I<sup>2</sup>C Operation

The SSP module in  $l^2C$  mode, fully implements all slave functions, except general call support, and provides interrupts on START and STOP bits in hardware to facilitate firmware implementations of the master functions. The SSP module implements the standard mode specifications as well as 7-bit and 10-bit addressing.

Two pins are used for data transfer. These are the RC3/ SCK/SCL pin, which is the clock (SCL), and the RC4/ SDI/SDA pin, which is the data (SDA). The user must configure these pins as inputs or outputs through the TRISC<4:3> bits.

The SSP module functions are enabled by setting SSP enable bit SSPEN (SSPCON<5>).

FIGURE 9-5: SSP BLOCK DIAGRAM (I<sup>2</sup>C MODE)

The SSP module has five registers for  $\mathsf{I}^2\mathsf{C}$  operation. These are the:

- SSP Control Register (SSPCON)

- SSP Status Register (SSPSTAT)

- Serial Receive/Transmit Buffer (SSPBUF)

- SSP Shift Register (SSPSR) Not directly accessible

- SSP Address Register (SSPADD)

The SSPCON register allows control of the  $I^2C$  operation. Four mode selection bits (SSPCON<3:0>) allow one of the following  $I^2C$  modes to be selected:

- I<sup>2</sup>C Slave mode (7-bit address)

- I<sup>2</sup>C Slave mode (10-bit address)

- I<sup>2</sup>C Slave mode (7-bit address), with START and STOP bit interrupts enabled to support Firmware Master mode

- I<sup>2</sup>C Slave mode (10-bit address), with START and STOP bit interrupts enabled to support Firmware Master mode

- I<sup>2</sup>C START and STOP bit interrupts enabled to support Firmware Master mode, Slave is IDLE

Selection of any  $I^2C$  mode with the SSPEN bit set, forces the SCL and SDA pins to be open drain, provided these pins are programmed to inputs by setting the appropriate TRISC bits. Pull-up resistors must be provided externally to the SCL and SDA pins for proper operation of the  $I^2C$  module.

Additional information on SSP I<sup>2</sup>C operation can be found in the PICmicro<sup>™</sup> Mid-Range MCU Family Reference Manual (DS33023A).

#### 9.3.1 SLAVE MODE

In Slave mode, the SCL and SDA pins must be configured as inputs (TRISC<4:3> set). The SSP module will override the input state with the output data when required (slave-transmitter).

When an address is matched, or the data transfer after an address match is received, the hardware automatically will generate the Acknowledge ( $\overline{ACK}$ ) pulse, and then load the SSPBUF register with the received value currently in the SSPSR register.

There are certain conditions that will cause the SSP module not to give this ACK pulse. They include (either or both):

- a) The buffer full bit BF (SSPSTAT<0>) was set before the transfer was received.

- b) The overflow bit SSPOV (SSPCON<6>) was set before the transfer was received.

In this case, the SSPSR register value is not loaded into the SSPBUF, but bit SSPIF (PIR1<3>) is set. Table 9-2 shows what happens when a data transfer byte is received, given the status of bits BF and SSPOV. The shaded cells show the condition where user software did not properly clear the overflow condition. Flag bit BF is cleared by reading the SSPBUF register, while bit SSPOV is cleared through software.

The SCL clock input must have a minimum high and low for proper operation. The high and low times of the  $I^2C$  specification, as well as the requirements of the SSP module, are shown in timing parameter #100 and parameter #101.

#### 9.3.2 MASTER MODE

Master mode of operation is supported in firmware using interrupt generation on the detection of the START and STOP conditions. The STOP (P) and START (S) bits are cleared from a RESET or when the SSP module is disabled. The STOP (P) and START (S) bits will toggle based on the START and STOP conditions. Control of the I<sup>2</sup>C bus may be taken when the P bit is set, or the bus is IDLE and both the S and P bits are clear.

In Master mode, the SCL and SDA lines are manipulated by clearing the corresponding TRISC<4:3> bit(s). The output level is always low, irrespective of the value(s) in PORTC<4:3>. So when transmitting data, a '1' data bit must have the TRISC<4> bit set (input) and a '0' data bit must have the TRISC<4> bit cleared (output). The same scenario is true for the SCL line with the TRISC<3> bit. Pull-up resistors must be provided externally to the SCL and SDA pins for proper operation of the I<sup>2</sup>C module.

The following events will cause SSP Interrupt Flag bit, SSPIF, to be set (SSP Interrupt will occur if enabled):

- START condition

- STOP condition

- Data transfer byte transmitted/received

Master mode of operation can be done with either the Slave mode IDLE (SSPM3:SSPM0 = 1011), or with the Slave active. When both Master and Slave modes are enabled, the software needs to differentiate the source(s) of the interrupt.

#### 9.3.3 MULTI-MASTER MODE

In Multi-Master mode, the interrupt generation on the detection of the START and STOP conditions, allows the determination of when the bus is free. The STOP (P) and START (S) bits are cleared from a RESET or when the SSP module is disabled. The STOP (P) and START (S) bits will toggle based on the START and STOP conditions. Control of the  $I^2C$  bus may be taken when bit P (SSPSTAT<4>) is set, or the bus is IDLE and both the S and P bits clear. When the bus is busy, enabling the SSP Interrupt will generate the interrupt when the STOP condition occurs.

In Multi-Master operation, the SDA line must be monitored to see if the signal level is the expected output level. This check only needs to be done when a high level is output. If a high level is expected and a low level is present, the device needs to release the SDA and SCL lines (set TRISC<4:3>). There are two stages where this arbitration can be lost, these are:

- Address Transfer

- Data Transfer

When the slave logic is enabled, the slave continues to receive. If arbitration was lost during the address transfer stage, communication to the device may be in progress. If addressed, an ACK pulse will be generated. If arbitration was lost during the data transfer stage, the device will need to retransfer the data at a later time.

| Address                | Name    | Bit 7                | Bit 6                                                            | Bit 5  | Bit 4 | Bit 3 | Bit 2  | Bit 1  | Bit 0  | Value on:<br>POR,<br>BOR | Value on<br>all other<br>RESETS |

|------------------------|---------|----------------------|------------------------------------------------------------------|--------|-------|-------|--------|--------|--------|--------------------------|---------------------------------|

| 0Bh, 8Bh,<br>10Bh,18Bh | INTCON  | GIE                  | PEIE                                                             | TMR0IE | INTE  | RBIE  | TMR0IF | INTF   | RBIF   | 0000 000x                | 0000 000u                       |

| 0Ch                    | PIR1    | PSPIF <sup>(1)</sup> | ADIF                                                             | RCIF   | TXIF  | SSPIF | CCP1IF | TMR2IF | TMR1IF | 0000 0000                | 0000 0000                       |

| 8Ch                    | PIE1    | PSPIE <sup>(1)</sup> | ADIE                                                             | RCIE   | TXIE  | SSPIE | CCP1IE | TMR2IE | TMR1IE | 0000 0000                | 0000 0000                       |

| 13h                    | SSPBUF  | Synchrono            | Synchronous Serial Port Receive Buffer/Transmit Register         |        |       |       |        |        |        | xxxx xxxx                | uuuu uuuu                       |

| 93h                    | SSPADD  | Synchrono            | Synchronous Serial Port (I <sup>2</sup> C mode) Address Register |        |       |       |        |        |        | 0000 0000                | 0000 0000                       |

| 14h                    | SSPCON  | WCOL                 | SSPOV                                                            | SSPEN  | CKP   | SSPM3 | SSPM2  | SSPM1  | SSPM0  | 0000 0000                | 0000 0000                       |

| 94h                    | SSPSTAT | SMP <sup>(2)</sup>   | CKE <sup>(2)</sup>                                               | D/A    | Р     | S     | R/W    | UA     | BF     | 0000 0000                | 0000 0000                       |

| 87h                    | TRISC   | PORTC Da             | PORTC Data Direction Register                                    |        |       |       |        |        |        | 1111 1111                | 1111 1111                       |

TABLE 9-3:

REGISTERS ASSOCIATED WITH I<sup>2</sup>C OPERATION

Legend: x = unknown, u = unchanged, - = unimplemented locations read as '0'. Shaded cells are not used by SSP module in I<sup>2</sup>C mode. **Note 1:** PSPIF and PSPIE are reserved on the PIC16F73/76; always maintain these bits clear.

2: Maintain these bits clear in I<sup>2</sup>C mode.

# 12.0 SPECIAL FEATURES OF THE CPU

These devices have a host of features intended to maximize system reliability, minimize cost through elimination of external components, provide power saving operating modes and offer code protection. These are:

- Oscillator Selection

- RESET

- Power-on Reset (POR)

- Power-up Timer (PWRT)

- Oscillator Start-up Timer (OST)

- Brown-out Reset (BOR)

- Interrupts

- Watchdog Timer (WDT)

- SLEEP

- Code Protection

- ID Locations

- In-Circuit Serial Programming

These devices have a Watchdog Timer, which can be enabled or disabled, using a configuration bit. It runs off its own RC oscillator for added reliability.

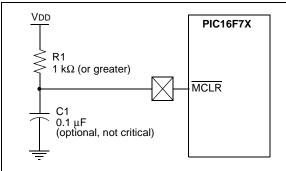

There are two timers that offer necessary delays on power-up. One is the Oscillator Start-up Timer (OST), intended to keep the chip in RESET until the crystal oscillator is stable. The other is the Power-up Timer (PWRT), which provides a fixed delay of 72 ms (nominal) on power-up only. It is designed to keep the part in RESET while the power supply stabilizes, and is enabled or disabled, using a configuration bit. With these two timers on-chip, most applications need no external RESET circuitry. SLEEP mode is designed to offer a very low current power-down mode. The user can wake-up from SLEEP through external RESET, Watchdog Timer Wake-up, or through an interrupt.

Several oscillator options are also made available to allow the part to fit the application. The RC oscillator option saves system cost while the LP crystal option saves power. Configuration bits are used to select the desired oscillator mode.

Additional information on special features is available in the PICmicro<sup>™</sup> Mid-Range Reference Manual (DS33023).

# 12.1 Configuration Bits