Welcome to E-XFL.COM

# What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

## Details

| Product Status             | Active                                                                  |

|----------------------------|-------------------------------------------------------------------------|

| Core Processor             | PIC                                                                     |

| Core Size                  | 8-Bit                                                                   |

| Speed                      | 20MHz                                                                   |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                                       |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                   |

| Number of I/O              | 22                                                                      |

| Program Memory Size        | 14KB (8K x 14)                                                          |

| Program Memory Type        | FLASH                                                                   |

| EEPROM Size                | -                                                                       |

| RAM Size                   | 368 × 8                                                                 |

| Voltage - Supply (Vcc/Vdd) | 4V ~ 5.5V                                                               |

| Data Converters            | A/D 5x8b                                                                |

| Oscillator Type            | External                                                                |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                       |

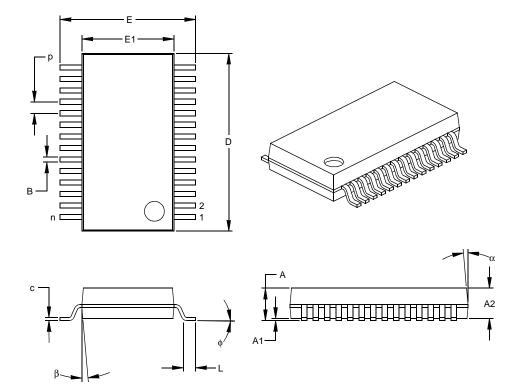

| Mounting Type              | Surface Mount                                                           |

| Package / Case             | 28-SSOP (0.209", 5.30mm Width)                                          |

| Supplier Device Package    | 28-SSOP                                                                 |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16f76-i-ss |

|                            |                                                                         |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

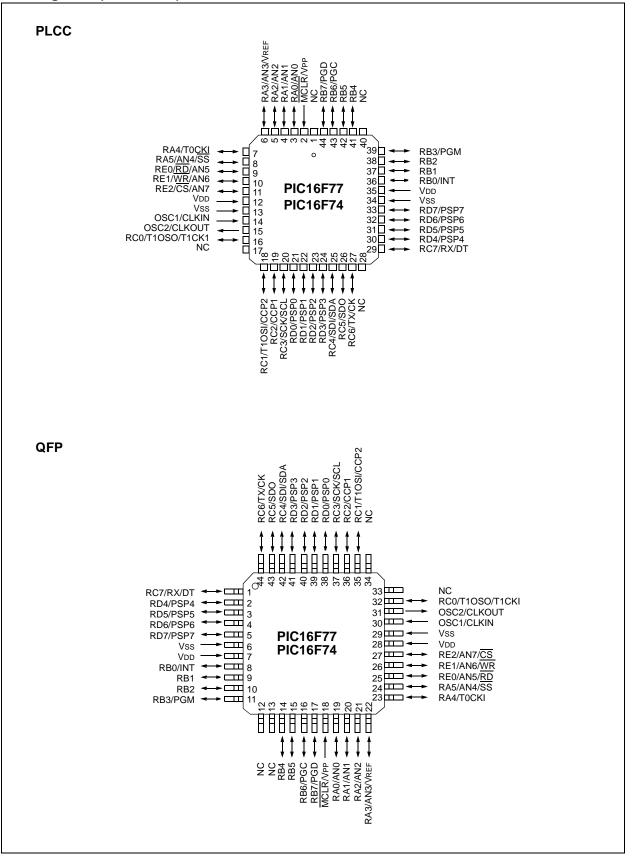

# **Pin Diagrams (Continued)**

# TABLE 1-3:PIC16F74 AND PIC16F77 PINOUT DESCRIPTION

| OSC1/CLKI<br>OSC1<br>CLKI<br>OSC2/CLKO<br>OSC2<br>CLKO<br>MCLR/VPP<br>MCLR<br>VPP | 13 | 14<br>15 | 30<br>31 | 1        | ST/CMOS <sup>(4)</sup> | Oscillator crystal or external clock input.<br>Oscillator crystal input or external clock source input.<br>ST buffer when configured in RC mode. Otherwise<br>CMOS.<br>External clock source input. Always associated with pin |

|-----------------------------------------------------------------------------------|----|----------|----------|----------|------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| CLKI<br>OSC2/CLKO<br>OSC2<br>CLKO<br><u>MCLR/VPP</u><br>MCLR                      | 14 | 15       | 31       | I        |                        | Oscillator crystal input or external clock source input.<br>ST buffer when configured in RC mode. Otherwise<br>CMOS.<br>External clock source input. Always associated with pin                                                |

| OSC2/CLKO<br>OSC2<br>CLKO<br>MCLR/VPP<br>MCLR                                     | 14 | 15       | 31       |          |                        | CMOS.<br>External clock source input. Always associated with pin                                                                                                                                                               |

| OSC2/CLKO<br>OSC2<br>CLKO<br>MCLR/VPP<br>MCLR                                     | 14 | 15       | 31       |          |                        | External clock source input. Always associated with pin                                                                                                                                                                        |

| OSC2<br>CLKO<br>MCLR/VPP<br>MCLR                                                  | 14 | 15       | 31       |          |                        |                                                                                                                                                                                                                                |

| OSC2<br>CLKO<br>MCLR/VPP<br>MCLR                                                  | 14 | 15       | 31       | 0        |                        | function OSC1 (see OSC1/CLKI, OSC2/CLKO pins).                                                                                                                                                                                 |

| CLKO<br>MCLR/VPP<br>MCLR                                                          |    |          |          | <u> </u> | I —                    | Oscillator crystal or clock output.                                                                                                                                                                                            |

| MCLR/Vpp<br>MCLR                                                                  |    |          |          | 0        |                        | Oscillator crystal output.                                                                                                                                                                                                     |

| MCLR/Vpp<br>MCLR                                                                  |    |          |          |          |                        | Connects to crystal or resonator in Crystal Oscillator                                                                                                                                                                         |

| MCLR/Vpp<br>MCLR                                                                  |    |          |          |          |                        | mode.                                                                                                                                                                                                                          |

| MCLR                                                                              |    |          |          | 0        |                        | In RC mode, OSC2 pin outputs CLKO, which has 1/4                                                                                                                                                                               |

| MCLR                                                                              |    |          |          |          |                        | the frequency of OSC1 and denotes the instruction                                                                                                                                                                              |

| MCLR                                                                              |    |          |          |          |                        | cycle rate.                                                                                                                                                                                                                    |

|                                                                                   | 1  | 2        | 18       |          | ST                     | Master Clear (input) or programming voltage (output).                                                                                                                                                                          |

| Vpp                                                                               |    |          |          | I        |                        | Master Clear (Reset) input. This pin is an active low                                                                                                                                                                          |

| VPP                                                                               |    |          |          |          |                        | RESET to the device.                                                                                                                                                                                                           |

|                                                                                   |    |          |          | Р        |                        | Programming voltage input.                                                                                                                                                                                                     |

|                                                                                   |    |          |          |          |                        | PORTA is a bi-directional I/O port.                                                                                                                                                                                            |

| RA0/AN0                                                                           | 2  | 3        | 19       |          | TTL                    |                                                                                                                                                                                                                                |

| RA0                                                                               |    |          |          | I/O      |                        | Digital I/O.                                                                                                                                                                                                                   |

| AN0                                                                               |    |          |          | I        |                        | Analog input 0.                                                                                                                                                                                                                |

| RA1/AN1                                                                           | 3  | 4        | 20       |          | TTL                    |                                                                                                                                                                                                                                |

| RA1                                                                               |    |          |          | I/O      |                        | Digital I/O.                                                                                                                                                                                                                   |

| AN1                                                                               |    |          |          | I        |                        | Analog input 1.                                                                                                                                                                                                                |

| RA2/AN2                                                                           | 4  | 5        | 21       |          | TTL                    |                                                                                                                                                                                                                                |

| RA2                                                                               |    |          |          | I/O      |                        | Digital I/O.                                                                                                                                                                                                                   |

| AN2                                                                               |    |          |          | I        |                        | Analog input 2.                                                                                                                                                                                                                |

| RA3/AN3/Vref                                                                      | 5  | 6        | 22       |          | TTL                    |                                                                                                                                                                                                                                |

| RA3                                                                               |    |          |          | I/O      |                        | Digital I/O.                                                                                                                                                                                                                   |

| AN3                                                                               |    |          |          | I        |                        | Analog input 3.                                                                                                                                                                                                                |

| VREF                                                                              |    |          |          | I        |                        | A/D reference voltage input.                                                                                                                                                                                                   |

| RA4/T0CKI                                                                         | 6  | 7        | 23       |          | ST                     |                                                                                                                                                                                                                                |

| RA4                                                                               |    |          |          | I/O      |                        | Digital I/O – Open drain when configured as output.                                                                                                                                                                            |

| TOCKI                                                                             |    |          |          | I        |                        | Timer0 external clock input.                                                                                                                                                                                                   |

| RA5/SS/AN4                                                                        | 7  | 8        | 24       |          | TTL                    |                                                                                                                                                                                                                                |

| RA5                                                                               |    | -        |          | I/O      |                        | Digital I/O.                                                                                                                                                                                                                   |

| SS                                                                                | 1  |          |          | 1        |                        | SPI slave select input.                                                                                                                                                                                                        |

| AN4                                                                               |    |          |          |          | 1                      |                                                                                                                                                                                                                                |

| Legend: I = inpu                                                                  |    | 1        |          |          |                        | Analog input 4.                                                                                                                                                                                                                |

— = Not used TTL = TTL input ST = Schmitt Trigger input

**Note 1:** This buffer is a Schmitt Trigger input when configured as an external interrupt.

2: This buffer is a Schmitt Trigger input when used in Serial Programming mode.

**3:** This buffer is a Schmitt Trigger input when configured as general purpose I/O and a TTL input when used in the Parallel Slave Port mode (for interfacing to a microprocessor bus).

4: This buffer is a Schmitt Trigger input when configured in RC Oscillator mode and a CMOS input otherwise.

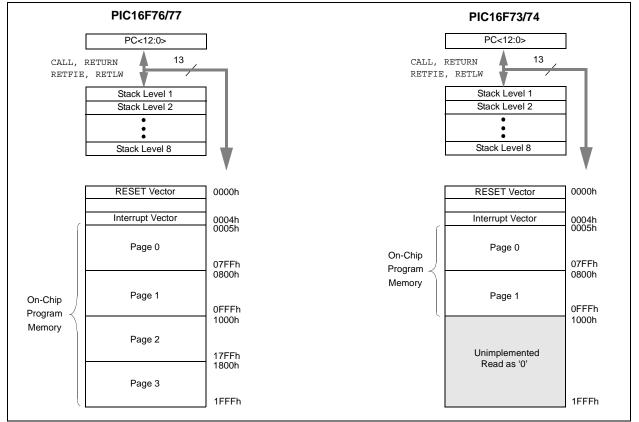

# 2.0 MEMORY ORGANIZATION

There are two memory blocks in each of these PICmicro<sup>®</sup> MCUs. The Program Memory and Data Memory have separate buses so that concurrent access can occur and is detailed in this section. The Program Memory can be read internally by user code (see Section 3.0).

Additional information on device memory may be found in the PICmicro<sup>™</sup> Mid-Range Reference Manual (DS33023).

# 2.1 Program Memory Organization

The PIC16F7X devices have a 13-bit program counter capable of addressing an 8K word x 14-bit program memory space. The PIC16F77/76 devices have 8K words of FLASH program memory and the PIC16F73/74 devices have 4K words. The program memory maps for PIC16F7X devices are shown in Figure 2-1. Accessing a location above the physically implemented address will cause a wraparound.

The RESET Vector is at 0000h and the Interrupt Vector is at 0004h.

# 2.2 Data Memory Organization

The Data Memory is partitioned into multiple banks, which contain the General Purpose Registers and the Special Function Registers. Bits RP1 (STATUS<6>) and RP0 (STATUS<5>) are the bank select bits:

| RP1:RP0 | Bank |

|---------|------|

| 00      | 0    |

| 01      | 1    |

| 10      | 2    |

| 11      | 3    |

Each bank extends up to 7Fh (128 bytes). The lower locations of each bank are reserved for the Special Function Registers. Above the Special Function Registers are General Purpose Registers, implemented as static RAM. All implemented banks contain Special Function Registers. Some frequently used Special Function Registers from one bank may be mirrored in another bank for code reduction and quicker access.

# 2.2.1 GENERAL PURPOSE REGISTER FILE

The register file (shown in Figure 2-2 and Figure 2-3) can be accessed either directly, or indirectly, through the File Select Register FSR.

# FIGURE 2-1: PROGRAM MEMORY MAPS AND STACKS FOR PIC16F7X DEVICES

| Address              | Name       | Bit 7                | Bit 6          | Bit 5                      | Bit 4          | Bit 3        | Bit 2           | Bit 1         | Bit 0        | Value on:<br>POR,<br>BOR | Details<br>on page |

|----------------------|------------|----------------------|----------------|----------------------------|----------------|--------------|-----------------|---------------|--------------|--------------------------|--------------------|

| Bank 1               |            |                      |                |                            |                |              |                 |               |              |                          |                    |

| 80h <sup>(4)</sup>   | INDF       | Addressin            | g this locatio | n uses conte               | ents of FSR to | address dat  | a memory (r     | not a physica | al register) | 0000 0000                | 27, 96             |

| 81h                  | OPTION_REG | RBPU                 | INTEDG         | TOCS                       | T0SE           | PSA          | PS2             | PS1           | PS0          | 1111 1111                | 20, 44, 96         |

| 82h <sup>(4)</sup>   | PCL        | Program C            | Counter's (PC  | C) Least Sigr              | ificant Byte   |              |                 |               |              | 0000 0000                | 26, 96             |

| 83h <sup>(4)</sup>   | STATUS     | IRP                  | RP1            | RP0                        | TO             | PD           | Z               | DC            | С            | 0001 1xxx                | 19, 96             |

| 84h <sup>(4)</sup>   | FSR        | Indirect da          | ata memory a   | ddress point               | ier            |              |                 |               |              | xxxx xxxx                | 27, 96             |

| 85h                  | TRISA      |                      | _              | PORTA Dat                  | a Direction Re | egister      |                 |               |              | 11 1111                  | 32, 96             |

| 86h                  | TRISB      | PORTB D              | ata Direction  | Register                   |                | •            |                 |               |              | 1111 1111                | 34, 96             |

| 87h                  | TRISC      | PORTC D              | ata Direction  | Register                   |                |              |                 |               |              | 1111 1111                | 35, 96             |

| 88h <sup>(5)</sup>   | TRISD      | PORTD D              | ata Direction  | Register                   |                |              |                 |               |              | 1111 1111                | 36, 96             |

| 89h <sup>(5)</sup>   | TRISE      | IBF                  | OBF            | IBOV                       | PSPMODE        |              | PORTE Da        | ata Direction | Bits         | 0000 -111                | 38, 96             |

| 8Ah <sup>(1,4)</sup> | PCLATH     | _                    | _              | _                          | Write Buffer f | or the upper | r 5 bits of the | Program C     | 0 0000       | 21,96                    |                    |

| 8Bh <sup>(4)</sup>   | INTCON     | GIE                  | PEIE           | TMR0IE                     | INTE           | RBIE         | TMR0IF          | INTF          | RBIF         | 0000 000x                | 23, 96             |

| 8Ch                  | PIE1       | PSPIE <sup>(3)</sup> | ADIE           | RCIE                       | TXIE           | SSPIE        | CCP1IE          | TMR2IE        | TMR1IE       | 0000 0000                | 22,96              |

| 8Dh                  | PIE2       | _                    | _              | _                          | _              | _            |                 | _             | CCP2IE       | 0                        | 24, 97             |

| 8Eh                  | PCON       | _                    | _              | _                          | _              |              | _               | POR           | BOR          | dd                       | 25, 97             |

| 8Fh                  | —          | Unimplem             | ented          |                            |                |              |                 |               |              | _                        | _                  |

| 90h                  | —          | Unimplem             | ented          |                            |                |              |                 |               |              | _                        | _                  |

| 91h                  | —          | Unimplem             | ented          |                            |                |              |                 |               |              | —                        | —                  |

| 92h                  | PR2        | Timer2 Pe            | riod Registe   | r                          |                |              |                 |               |              | 1111 1111                | 52, 97             |

| 93h                  | SSPADD     | Synchrono            | ous Serial Po  | ort (I <sup>2</sup> C mode | ) Address Reg  | gister       |                 |               |              | 0000 0000                | 68, 97             |

| 94h                  | SSPSTAT    | SMP                  | CKE            | D/A                        | Р              | S            | R/W             | UA            | BF           | 0000 0000                | 60, 97             |

| 95h                  | —          | Unimplem             | ented          |                            |                |              |                 |               |              | —                        | —                  |

| 96h                  | —          | Unimplem             | ented          |                            |                |              |                 |               |              | —                        | —                  |

| 97h                  | —          | Unimplem             | ented          |                            |                |              | _               |               | -            | —                        | —                  |

| 98h                  | TXSTA      | CSRC                 | TX9            | TXEN                       | SYNC           |              | BRGH            | TRMT          | TX9D         | 0000 -010                | 69, 97             |

| 99h                  | SPBRG      | Baud Rate            | e Generator I  | Register                   |                |              |                 |               |              | 0000 0000                | 71, 97             |

| 9Ah                  | —          | Unimplem             | ented          |                            |                |              |                 |               |              | —                        |                    |

| 9Bh                  | —          | Unimplem             | ented          |                            |                |              |                 |               |              | -                        |                    |

| 9Ch                  | —          | Unimplem             | ented          |                            |                |              |                 |               |              | _                        |                    |

| 9Dh                  | —          | Unimplem             | ented          |                            |                |              |                 |               |              | _                        |                    |

| 9Eh                  | —          | Unimplem             | ented          |                            |                |              |                 |               |              | -                        |                    |

| 9Fh                  | ADCON1     | _                    | _              | _                          | _              | _            | PCFG2           | PCFG1         | PCFG0        | 000                      | 84, 97             |

| TABLE 2-1: SPECIAL FUNCTION REGISTER SUMMARY (CONTINUED) |

|----------------------------------------------------------|

|----------------------------------------------------------|

$\label{eq:legend: Legend: Legend: u = unchanged, q = value depends on condition, - = unimplemented, read as '0', r = reserved.$ Shaded locations are unimplemented, read as '0'.

Note 1: The upper byte of the program counter is not directly accessible. PCLATH is a holding register for the PC<12:8>, whose contents are transferred to the upper byte of the program counter during branches (CALL or GOTO).

2: Other (non power-up) RESETS include external RESET through MCLR and Watchdog Timer Reset. 3: Bits PSPIE and PSPIF are reserved on the 28-pin devices; always maintain these bits clear.

4: These registers can be addressed from any bank.

5: PORTD, PORTE, TRISD, and TRISE are not physically implemented on the 28-pin devices, read as '0'.

6: This bit always reads as a '1'.

| <b>TABLE 2-1:</b> | SPECIAL FUNCTION REGISTER SUMMARY | (CONTINUED) |

|-------------------|-----------------------------------|-------------|

|-------------------|-----------------------------------|-------------|

| Address               | Name       | Bit 7                          | Bit 6          | Bit 5                   | Bit 4          | Bit 3         | Bit 2         | Bit 1         | Bit 0        | Value on:<br>POR,<br>BOR | Details<br>on page |

|-----------------------|------------|--------------------------------|----------------|-------------------------|----------------|---------------|---------------|---------------|--------------|--------------------------|--------------------|

| Bank 2                |            |                                |                |                         |                |               |               |               |              |                          |                    |

| 100h <sup>(4)</sup>   | INDF       | Addressin                      | g this locatio | n uses conte            | ents of FSR to | address data  | a memory (r   | not a physica | al register) | 0000 0000                | 27, 96             |

| 101h                  | TMR0       | Timer0 Mo                      | dule Registe   | er                      |                |               |               |               |              | xxxx xxxx                | 45, 96             |

| 102h <sup>(4)</sup>   | PCL        | Program C                      | Counter (PC)   | Least Signif            | icant Byte     |               |               |               |              | 0000 0000                | 26, 96             |

| 103h <sup>(4)</sup>   | STATUS     | IRP                            | RP1            | RP0                     | ТО             | PD            | Z             | DC            | С            | 0001 1xxx                | 19, 96             |

| 104h <sup>(4)</sup>   | FSR        | Indirect Da                    | ata Memory /   | Address Poir            | nter           |               |               |               |              | xxxx xxxx                | 27, 96             |

| 105h                  | —          | Unimplem                       | ented          |                         |                |               |               |               |              | _                        | —                  |

| 106h                  | PORTB      | PORTB D                        | ata Latch wh   | en written: F           | ORTB pins w    | hen read      |               |               |              | xxxx xxxx                | 34, 96             |

| 107h                  | _          | Unimplem                       | ented          |                         |                |               |               |               |              | —                        | —                  |

| 108h                  | —          | Unimplem                       | ented          |                         |                |               |               |               |              | —                        | —                  |

| 109h                  | —          | Unimplem                       | ented          |                         |                |               |               |               |              | _                        | —                  |

| 10Ah <sup>(1,4)</sup> | PCLATH     | —                              | _              | _                       | Write Buffer   | for the upper | 5 bits of the | Program C     | ounter       | 0 0000                   | 21, 96             |

| 10Bh <sup>(4)</sup>   | INTCON     | GIE                            | PEIE           | TMR0IE                  | INTE           | RBIE          | TMR0IF        | INTF          | RBIF         | 0000 000x                | 23, 96             |

| 10Ch                  | PMDATA     | Data Register Low Byte         |                |                         |                |               |               |               | XXXX XXXX    | 29, 97                   |                    |

| 10Dh                  | PMADR      | Address R                      | egister Low    | Low Byte                |                |               |               |               |              |                          | 29, 97             |

| 10Eh                  | PMDATH     | —                              | _              | Data Register High Byte |                |               |               |               |              |                          | 29, 97             |

| 10Fh                  | PMADRH     | — — Address Register High Byte |                |                         |                |               |               |               | XXXX XXXX    | 29, 97                   |                    |

| Bank 3                |            |                                |                |                         |                |               |               |               |              |                          |                    |

| 180h <sup>(4)</sup>   | INDF       | Addressin                      | g this locatio | n uses conte            | ents of FSR to | address data  | a memory (r   | not a physica | al register) | 0000 0000                | 27, 96             |

| 181h                  | OPTION_REG | RBPU                           | INTEDG         | TOCS                    | TOSE           | PSA           | PS2           | PS1           | PS0          | 1111 1111                | 20, 44, 96         |

| 182h <sup>(4)</sup>   | PCL        | Program C                      | Counter (PC)   | Least Signif            | icant Byte     |               |               |               |              | 0000 0000                | 26, 96             |

| 183h <sup>(4)</sup>   | STATUS     | IRP                            | RP1            | RP0                     | TO             | PD            | Z             | DC            | С            | 0001 1xxx                | 19, 96             |

| 184h <sup>(4)</sup>   | FSR        | Indirect Da                    | ata Memory /   | Address Poir            | nter           |               |               |               |              | xxxx xxxx                | 27, 96             |

| 185h                  | —          | Unimplem                       | ented          |                         |                |               |               |               |              | _                        | _                  |

| 186h                  | TRISB      | PORTB D                        | ata Direction  | Register                |                |               |               |               |              | 1111 1111                | 34, 96             |

| 187h                  | —          | Unimplem                       | ented          |                         |                |               |               |               |              | _                        | _                  |

| 188h                  | —          | Unimplem                       | ented          |                         |                |               |               |               |              | _                        | _                  |

| 189h                  | —          | Unimplem                       | ented          |                         |                |               |               |               |              | _                        | _                  |

| 18Ah <sup>(1,4)</sup> | PCLATH     | _                              |                | _                       | Write Buffer   | for the upper | 5 bits of the | Program C     | ounter       | 0 0000                   | 21, 96             |

| 18Bh <sup>(4)</sup>   | INTCON     | GIE                            | PEIE           | TMR0IE                  | INTE           | RBIE          | TMR0IF        | INTF          | RBIF         | 0000 000x                | 23, 96             |

| 18Ch                  | PMCON1     | (6)                            | _              | —                       | —              | _             | _             | —             | RD           | 10                       | 29, 97             |

| 18Dh                  | —          | Unimplem                       | ented          |                         |                |               |               |               |              | _                        |                    |

| 18Eh                  | _          | Reserved                       | maintain clea  | ar                      |                |               |               |               |              | 0000 0000                |                    |

| 18Fh                  | _          | Reserved                       | maintain clea  | ar                      |                |               |               |               |              | 0000 0000                |                    |

Legend: x = unknown, u = unchanged, q = value depends on condition, - = unimplemented, read as '0', r = reserved. Shaded locations are unimplemented, read as '0'.

**Note** 1: The upper byte of the program counter is not directly accessible. PCLATH is a holding register for the PC<12:8>, whose contents are transferred to the upper byte of the program counter during branches (CALL or GOTO).

2: Other (non power-up) RESETS include external RESET through MCLR and Watchdog Timer Reset.

3: Bits PSPIE and PSPIF are reserved on the 28-pin devices; always maintain these bits clear.

4: These registers can be addressed from any bank.

5: PORTD, PORTE, TRISD, and TRISE are not physically implemented on the 28-pin devices, read as '0'.

6: This bit always reads as a '1'.

# 2.2.2.1 STATUS Register

The STATUS register contains the arithmetic status of the ALU, the RESET status and the bank select bits for data memory.

The STATUS register can be the destination for any instruction, as with any other register. If the STATUS register is the destination for an instruction that affects the Z, DC, or C bits, then the write to these three bits is disabled. These bits are set or cleared according to the device logic. Furthermore, the TO and PD bits are not writable, therefore, the result of an instruction with the STATUS register as destination may be different than intended.

For example, CLRF STATUS will clear the upper three bits and set the Z bit. This leaves the STATUS register as  $000u \ u1uu$  (where u = unchanged).

It is recommended, therefore, that only BCF, BSF, SWAPF and MOVWF instructions are used to alter the STATUS register, because these instructions do not affect the Z, C, or DC bits from the STATUS register. For other instructions not affecting any status bits, see the "Instruction Set Summary."

Note 1: The <u>C</u> and <u>DC</u> bits operate as a borrow and digit borrow bit, respectively, in subtraction. See the <u>SUBLW</u> and <u>SUBWF</u> instructions for examples.

# REGISTER 2-1: STATUS REGISTER (ADDRESS 03h, 83h, 103h, 183h)

|         | R/W-0                               | R/W-0                                                                            | R/W-0           | R-1            | R-1           | R/W-x        | R/W-x       | R/W-x |  |  |  |

|---------|-------------------------------------|----------------------------------------------------------------------------------|-----------------|----------------|---------------|--------------|-------------|-------|--|--|--|

|         | IRP                                 | RP1                                                                              | RP0             | TO             | PD            | Z            | DC          | С     |  |  |  |

|         | bit 7                               |                                                                                  |                 |                |               |              |             | bit 0 |  |  |  |

| bit 7   | 1 = Bank 2                          | ter Bank Sele<br>2, 3 (100h - 1F                                                 | Fh)             | or indirect ac | ldressing)    |              |             |       |  |  |  |

|         |                                     | 0 = Bank 0, 1 (00h - FFh)                                                        |                 |                |               |              |             |       |  |  |  |

| bit 6-5 |                                     | Register Ban                                                                     |                 | (used for dire | ect addressi  | ng)          |             |       |  |  |  |

|         | 10 = Bank<br>01 = Bank<br>00 = Bank | 3 (180h - 1FF<br>2 (100h - 17F<br>1 (80h - FFh)<br>0 (00h - 7Fh)<br>is 128 bytes | <sup>-</sup> h) |                |               |              |             |       |  |  |  |

| bit 4   | TO: Time-c                          | out bit                                                                          |                 |                |               |              |             |       |  |  |  |

|         |                                     | ower-up, CLR<br>time-out occ                                                     |                 | on, or SLEEP   | o instruction |              |             |       |  |  |  |

| bit 3   | PD: Power                           | -down bit                                                                        |                 |                |               |              |             |       |  |  |  |

|         |                                     | ower-up or by<br>cution of the                                                   |                 |                |               |              |             |       |  |  |  |

| bit 2   | z: Zero bit                         |                                                                                  |                 |                |               |              |             |       |  |  |  |

|         |                                     | sult of an arith<br>sult of an arith                                             |                 |                |               |              |             |       |  |  |  |

| bit 1   | DC: Digit c                         | arry/borrow b                                                                    | it (addwf, ae   | DLW, SUBL      | W, SUBWF      | instructions | 5)          |       |  |  |  |

|         | •                                   | r-out from the<br>ry-out from th                                                 |                 |                |               | d            |             |       |  |  |  |

| bit 0   | C: Carry/b                          | orrow bit (ADI                                                                   | WF, ADDLW       | , SUBLW, S     | SUBWF instr   | uctions)     |             |       |  |  |  |

|         |                                     | -out from the<br>ry-out from th                                                  |                 |                |               |              |             |       |  |  |  |

|         | Note:                               | For borrow, t<br>complement<br>loaded with e                                     | of the secon    | d operand. F   | or rotate (R  | RF, RLF)     | instruction |       |  |  |  |

|         | Legend:                             |                                                                                  |                 |                |               |              |             |       |  |  |  |

| Legend:                                    |                  |                      |                    |

|--------------------------------------------|------------------|----------------------|--------------------|

| R = Readable bit                           | W = Writable bit | U = Unimplemented    | bit, read as '0'   |

| <ul> <li>n = Value at POR reset</li> </ul> | '1' = Bit is set | '0' = Bit is cleared | x = Bit is unknown |

# 2.2.2.3 INTCON Register

The INTCON register is a readable and writable register, which contains various enable and flag bits for the TMR0 register overflow, RB Port change and External RB0/INT pin interrupts.

# **Note:** Interrupt flag bits are set when an interrupt condition occurs, regardless of the state of its corresponding enable bit or the global enable bit, GIE (INTCON<7>). User software should ensure the appropriate interrupt flag bits are clear prior to enabling an interrupt.

# REGISTER 2-3: INTCON REGISTER (ADDRESS 0Bh, 8Bh, 10Bh, 18Bh)

|       | R/W-0      | R/W-0                      | R/W-0                                             | R/W-0         | R/W-0         | R/W-0         | R/W-0          | R/W-x      |

|-------|------------|----------------------------|---------------------------------------------------|---------------|---------------|---------------|----------------|------------|

|       | GIE        | PEIE                       | TMR0IE                                            | INTE          | RBIE          | TMR0IF        | INTF           | RBIF       |

|       | bit 7      |                            |                                                   |               |               |               |                | bit 0      |

| bit 7 | GIE: Globa | al Interrupt E             | nable bit                                         |               |               |               |                |            |

|       | 1 = Enable | •                          | ked interrupt                                     | S             |               |               |                |            |

| bit 6 |            |                            | upt Enable b                                      | oit           |               |               |                |            |

|       |            |                            | ked peripher<br>eral interrup                     |               | i             |               |                |            |

| bit 5 | TMR0IE: T  | MR0 Overfl                 | ow Interrupt                                      | Enable bit    |               |               |                |            |

|       |            | es the TMR0<br>es the TMR0 |                                                   |               |               |               |                |            |

| bit 4 | INTE: RB0  | /INT Externa               | al Interrupt E                                    | nable bit     |               |               |                |            |

|       |            |                            | NT external i<br>NT external                      | •             |               |               |                |            |

| bit 3 | RBIE: RB   | Port Change                | e Interrupt Er                                    | nable bit     |               |               |                |            |

|       |            |                            | ort change in<br>ort change in                    |               |               |               |                |            |

| bit 2 | TMR0IF: T  | MR0 Overfle                | ow Interrupt                                      | Flag bit      |               |               |                |            |

|       |            |                            | overflowed<br>not overflow                        | (must be cle  | eared in soft | ware)         |                |            |

| bit 1 | INTF: RB0  | /INT Externa               | al Interrupt F                                    | lag bit       |               |               |                |            |

|       |            |                            | nal interrupt<br>nal interrupt                    |               |               | red in softwa | are)           |            |

| bit 0 | A mismatc  | h condition v              | e Interrupt Fla<br>will continue<br>g bit RBIF to | to set flag b |               | ding PORTE    | 3 will end the | e mismatch |

|       |            |                            | RB7:RB4 pi<br>B4 pins hav                         |               |               | be cleared i  | n software)    |            |

| Legend:                  |                  |                      |                    |

|--------------------------|------------------|----------------------|--------------------|

| R = Readable bit         | W = Writable bit | U = Unimplemented    | bit, read as '0'   |

| - n = Value at POR reset | '1' = Bit is set | '0' = Bit is cleared | x = Bit is unknown |

### 3.0 **READING PROGRAM MEMORY**

The FLASH Program Memory is readable during normal operation over the entire VDD range. It is indirectly addressed through Special Function Registers (SFR). Up to 14-bit numbers can be stored in memory for use as calibration parameters, serial numbers, packed 7-bit ASCII, etc. Executing a program memory location containing data that forms an invalid instruction results in a NOP.

There are five SFRs used to read the program and memory. These registers are:

- PMCON1

- PMDATA

- PMDATH

- PMADR

- PMADRH

The program memory allows word reads. Program memory access allows for checksum calculation and reading calibration tables.

When interfacing to the program memory block, the PMDATH:PMDATA registers form a two-byte word, which holds the 14-bit data for reads. The PMADRH:PMADR registers form a two-byte word, which holds the 13-bit address of the FLASH location being accessed. These devices can have up to 8K words of program FLASH, with an address range from Oh to 3FFFh. The unused upper bits in both the PMDATH and PMADRH registers are not implemented and read as "0's".

### 3.1 **PMADR**

The address registers can address up to a maximum of 8K words of program FLASH.

When selecting a program address value, the MSByte of the address is written to the PMADRH register and the LSByte is written to the PMADR register. The upper MSbits of PMADRH must always be clear.

### 3.2 PMCON1 Register

PMCON1 is the control register for memory accesses.

The control bit RD initiates read operations. This bit cannot be cleared, only set, in software. It is cleared in hardware at the completion of the read operation.

### **REGISTER 3-1:** PMCON1 REGISTER (ADDRESS 18Ch)

|         | R-1                       | U-0         | U-0          | U-0           | U-x        | U-0          | U-0            | R/S-0       |

|---------|---------------------------|-------------|--------------|---------------|------------|--------------|----------------|-------------|

|         | reserved                  | _           | —            | _             | _          | —            | —              | RD          |

|         | bit 7                     |             |              |               |            |              |                | bit 0       |

|         |                           |             |              |               |            |              |                |             |

| bit 7   | Reserved:                 | Read as '1  | ,            |               |            |              |                |             |

| bit 6-1 | Unimplem                  | ented: Rea  | d as '0'     |               |            |              |                |             |

| bit 0   | RD: Read                  | Control bit |              |               |            |              |                |             |

|         | 1 = Initiates<br>in softw |             | ead, RD is c | leared in har | dware. The | RD bit can c | only be set (n | ot cleared) |

|         | 0 = FLASH                 | l read comp | leted        |               |            |              |                |             |

|         | _                         |             |              |               |            |              |                |             |

|         | Legend:                   |             |              |               |            |              |                |             |

| Legend:                  |                  |                      |                    |

|--------------------------|------------------|----------------------|--------------------|

| R = Readable bit         | W = Writable bit | U = Unimplemented    | bit, read as '0'   |

| - n = Value at POR reset | '1' = Bit is set | '0' = Bit is cleared | x = Bit is unknown |

# 4.0 I/O PORTS

Some pins for these I/O ports are multiplexed with an alternate function for the peripheral features on the device. In general, when a peripheral is enabled, that pin may not be used as a general purpose I/O pin.

Additional information on I/O ports may be found in the PICmicro<sup>™</sup> Mid-Range Reference Manual, (DS33023).

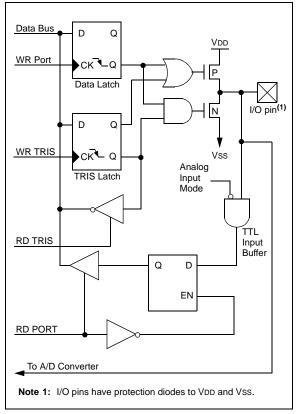

# 4.1 PORTA and the TRISA Register

PORTA is a 6-bit wide, bi-directional port. The corresponding data direction register is TRISA. Setting a TRISA bit (= '1') will make the corresponding PORTA pin an input (i.e., put the corresponding output driver in a Hi-Impedance mode). Clearing a TRISA bit (= '0') will make the corresponding PORTA pin an output (i.e., put the contents of the output latch on the selected pin).

Reading the PORTA register reads the status of the pins, whereas writing to it will write to the port latch. All write operations are read-modify-write operations. Therefore, a write to a port implies that the port pins are read, the value is modified and then written to the port data latch.

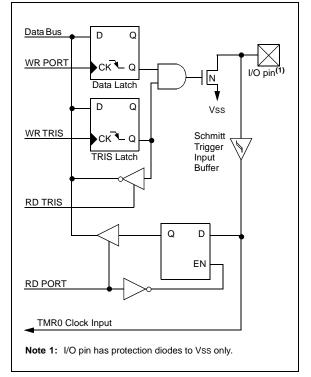

Pin RA4 is multiplexed with the Timer0 module clock input to become the RA4/T0CKI pin. The RA4/T0CKI pin is a Schmitt Trigger input and an open drain output. All other PORTA pins have TTL input levels and full CMOS output drivers.

Other PORTA pins are multiplexed with analog inputs and analog VREF input. The operation of each pin is selected by clearing/setting the control bits in the ADCON1 register (A/D Control Register1).

**Note:** On a Power-on Reset, these pins are configured as analog inputs and read as '0'.

The TRISA register controls the direction of the RA pins, even when they are being used as analog inputs. The user must ensure the bits in the TRISA register are maintained set, when using them as analog inputs.

| BCF<br>BCF<br>CLRF                      | STATUS,<br>STATUS,<br>PORTA                |     | ;<br>; Bank0<br>; Initialize PORTA by<br>; clearing output<br>: data latches | Y |

|-----------------------------------------|--------------------------------------------|-----|------------------------------------------------------------------------------|---|

| BSF<br>MOVLW<br>MOVWF<br>MOVLW<br>MOVWF | STATUS,<br>0x06<br>ADCON1<br>0xCF<br>TRISA | RPO | ,                                                                            |   |

# FIGURE 4-1:

# BLOCK DIAGRAM OF RA3:RA0 AND RA5 PINS

FIGURE 4-2:

# BLOCK DIAGRAM OF RA4/T0CKI PIN

| Name    | Bit# | Buffer                | Function                                                                                                               |

|---------|------|-----------------------|------------------------------------------------------------------------------------------------------------------------|

| RB0/INT | bit0 | TTL/ST <sup>(1)</sup> | Input/output pin or external interrupt input. Internal software programmable weak pull-up.                             |

| RB1     | bit1 | TTL                   | Input/output pin. Internal software programmable weak pull-up.                                                         |

| RB2     | bit2 | TTL                   | Input/output pin. Internal software programmable weak pull-up.                                                         |

| RB3     | bit3 | TTL                   | Input/output pin. Internal software programmable weak pull-up.                                                         |

| RB4     | bit4 | TTL                   | Input/output pin (with interrupt-on-change). Internal software programmable weak pull-up.                              |

| RB5     | bit5 | TTL                   | Input/output pin (with interrupt-on-change). Internal software programmable weak pull-up.                              |

| RB6     | bit6 | TTL/ST <sup>(2)</sup> | Input/output pin (with interrupt-on-change).<br>Internal software programmable weak pull-up. Serial programming clock. |

| RB7     | bit7 | TTL/ST <sup>(2)</sup> | Input/output pin (with interrupt-on-change).<br>Internal software programmable weak pull-up. Serial programming data.  |

# TABLE 4-3: PORTB FUNCTIONS

Legend: TTL = TTL input, ST = Schmitt Trigger input

Note 1: This buffer is a Schmitt Trigger input when configured as the external interrupt.

2: This buffer is a Schmitt Trigger input when used in Serial Programming mode.

# TABLE 4-4: SUMMARY OF REGISTERS ASSOCIATED WITH PORTB

| Address   | Name       | Bit 7   | Bit 6                         | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1     | Bit 0     | Value on:<br>POR,<br>BOR | Value on<br>all other<br>RESETS |

|-----------|------------|---------|-------------------------------|-------|-------|-------|-------|-----------|-----------|--------------------------|---------------------------------|

| 06h, 106h | PORTB      | RB7     | RB6                           | RB5   | RB4   | RB3   | RB2   | RB1       | RB0       | xxxx xxxx                | uuuu uuuu                       |

| 86h, 186h | TRISB      | PORTB I | PORTB Data Direction Register |       |       |       |       | 1111 1111 | 1111 1111 |                          |                                 |

| 81h, 181h | OPTION_REG | RBPU    | INTEDG                        | TOCS  | TOSE  | PSA   | PS2   | PS1       | PS0       | 1111 1111                | 1111 1111                       |

Legend: x = unknown, u = unchanged. Shaded cells are not used by PORTB.

# 5.0 TIMER0 MODULE

The Timer0 module timer/counter has the following features:

- 8-bit timer/counter

- Readable and writable

- 8-bit software programmable prescaler

- · Internal or external clock select

- Interrupt on overflow from FFh to 00h

- Edge select for external clock

Additional information on the Timer0 module is available in the PICmicro<sup>™</sup> Mid-Range MCU Family Reference Manual (DS33023).

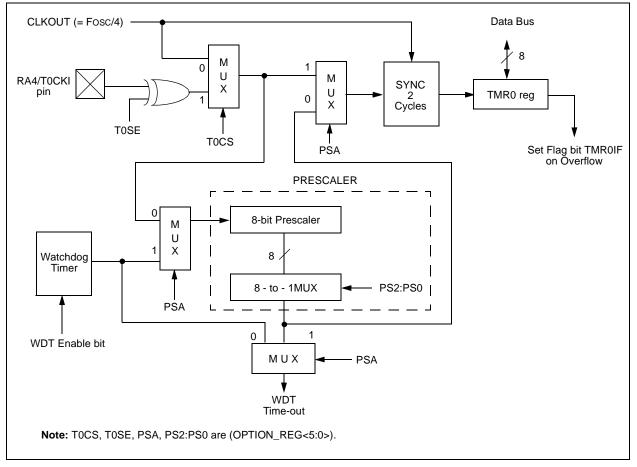

Figure 5-1 is a block diagram of the Timer0 module and the prescaler shared with the WDT.

Timer0 operation is controlled through the OPTION\_REG register (Register 5-1 on the following page). Timer mode is selected by clearing bit TOCS (OPTION\_REG<5>). In Timer mode, the Timer0 module will increment every instruction cycle (without prescaler). If the TMR0 register is written, the increment is inhibited for the following two instruction cycles. The user can work around this by writing an adjusted value to the TMR0 register.

Counter mode is selected by setting bit T0CS (OPTION\_REG<5>). In Counter mode, Timer0 will increment, either on every rising or falling edge of pin RA4/T0CKI. The incrementing edge is determined by the Timer0 Source Edge Select bit T0SE (OPTION\_REG<4>). Clearing bit T0SE selects the rising edge. Restrictions on the external clock input are discussed in detail in Section 5.2.

The prescaler is mutually exclusively shared between the Timer0 module and the Watchdog Timer. The prescaler is not readable or writable. Section 5.3 details the operation of the prescaler.

# 5.1 Timer0 Interrupt

The TMR0 interrupt is generated when the TMR0 register overflows from FFh to 00h. This overflow sets bit TMR0IF (INTCON<2>). The interrupt can be masked by clearing bit TMR0IE (INTCON<5>). Bit TMR0IF must be cleared in software by the Timer0 module Interrupt Service Routine, before re-enabling this interrupt. The TMR0 interrupt cannot awaken the processor from SLEEP, since the timer is shut-off during SLEEP.

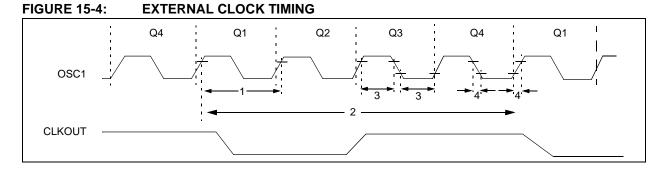

### 5.2 Using Timer0 with an External Clock

When no prescaler is used, the external clock input is the same as the prescaler output. The synchronization of T0CKI, with the internal phase clocks, is accomplished by sampling the prescaler output on the Q2 and Q4 cycles of the internal phase clocks. Therefore, it is necessary for T0CKI to be high for at least 2Tosc (and a small RC delay of 20 ns) and low for at least 2Tosc (and a small RC delay of 20 ns). Refer to the electrical specification of the desired device.

|         | R/W-1                                                                                                    | R/W-1                                                                             | R/W-1             | R/W-1        | R/W-1      | R/W-1 | R/W-1 | R/W-1       |  |

|---------|----------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------|-------------------|--------------|------------|-------|-------|-------------|--|

|         | RBPU                                                                                                     | INTEDG                                                                            | TOCS              | T0SE         | PSA        | PS2   | PS1   | PS0         |  |

|         | bit 7                                                                                                    |                                                                                   |                   |              |            |       |       | bit 0       |  |

|         |                                                                                                          |                                                                                   |                   |              |            |       |       |             |  |

| bit 7   | RBPU: PC                                                                                                 | ORTB Pull-up                                                                      | Enable bit        | (see Sectior | n 2.2.2.2) |       |       |             |  |

| bit 6   | INTEDG:                                                                                                  | <b>INTEDG</b> : Interrupt Edge Select bit (see Section 2.2.2.2)                   |                   |              |            |       |       |             |  |

| bit 5   | TOCS: TM                                                                                                 | IR0 Clock Sc                                                                      | ource Select      | bit          |            |       |       |             |  |

|         |                                                                                                          | tion on TOCk<br>al instruction                                                    |                   | (CLKOUT)     |            |       |       |             |  |

| bit 4   | TOSE: TM                                                                                                 | R0 Source E                                                                       | dge Select        | bit          |            |       |       |             |  |

|         | 1 = Incren                                                                                               | nent on high-                                                                     | to-low trans      | ition on TOC | KI pin     |       |       |             |  |

|         | 0 = Incren                                                                                               | nent on low-t                                                                     | o-high trans      | ition on TOC | KI pin     |       |       |             |  |

| bit 3   | PSA: Pres                                                                                                | scaler Assigr                                                                     | ment bit          |              |            |       |       |             |  |

|         | 1 = Presca                                                                                               | aler is assign                                                                    | ed to the W       | DT           |            |       |       |             |  |

|         | 0 = Presca                                                                                               | aler is assign                                                                    | ed to the Ti      | mer0 modul   | e          |       |       |             |  |

| bit 2-0 | PS2:PS0:                                                                                                 | Prescaler R                                                                       | ate Select b      | its          |            |       |       |             |  |

|         | Bit Value                                                                                                | TMR0 Rate                                                                         | WDT Rate          |              |            |       |       |             |  |

|         | 000 1:2 1:1                                                                                              |                                                                                   |                   |              |            |       |       |             |  |

|         | 001<br>010                                                                                               | 1:4<br>1:8                                                                        | 1:2<br>1:4        |              |            |       |       |             |  |

|         | 010                                                                                                      | 1:16                                                                              | 1:4               |              |            |       |       |             |  |

|         | 100                                                                                                      | 1:32                                                                              | 1:16              |              |            |       |       |             |  |

|         | 101                                                                                                      | 1:64                                                                              | 1:32              |              |            |       |       |             |  |

|         | 110<br>111                                                                                               | 1 : 128<br>1 : 256                                                                | 1 : 64<br>1 : 128 |              |            |       |       |             |  |

|         | 111                                                                                                      | 1.200                                                                             | 1.120             |              |            |       |       |             |  |

|         | Legend:                                                                                                  |                                                                                   |                   |              |            |       |       |             |  |

|         | R = Readable bit $W = Writable bit$ $U = Unimplemented bit, read as '0'$                                 |                                                                                   |                   |              |            |       |       | '0'         |  |

|         | - n = Value                                                                                              | n = Value at POR reset '1' = Bit is set '0' = Bit is cleared $x = Bit$ is unknown |                   |              |            |       |       |             |  |

|         |                                                                                                          |                                                                                   |                   |              |            |       |       | -           |  |

|         |                                                                                                          | To avoid ar                                                                       |                   |              |            |       |       |             |  |

|         |                                                                                                          | Example 5-1                                                                       |                   |              |            |       |       |             |  |

|         | caler assignment between Timer0 and the WDT. This sequence must be followed even if the WDT is disabled. |                                                                                   |                   |              |            |       |       | be followed |  |

|         | even i the wort is disabled.                                                                             |                                                                                   |                   |              |            |       |       |             |  |

NOTES:

NOTES:

| DECFSZ           | Decrement f, Skip if 0                                                                                                                                                                                                                                                                                                       |

|------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [label] DECFSZ f,d                                                                                                                                                                                                                                                                                                           |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ d \in \ [0,1] \end{array}$                                                                                                                                                                                                                                                            |

| Operation:       | (f) - 1 $\rightarrow$ (destination);<br>skip if result = 0                                                                                                                                                                                                                                                                   |

| Status Affected: | None                                                                                                                                                                                                                                                                                                                         |

| Description:     | The contents of register 'f' are<br>decremented. If 'd' is 0, the result<br>is placed in the W register. If 'd' is<br>1, the result is placed back in<br>register 'f'.<br>If the result is 1, the next instruc-<br>tion is executed. If the result is 0,<br>then a NOP is executed instead,<br>making it a 2TCY instruction. |

| INCFSZ           | Increment f, Skip if 0                                                                                                                                                                                                                                                                                                  |

|------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [label] INCFSZ f,d                                                                                                                                                                                                                                                                                                      |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ d \in \ [0,1] \end{array}$                                                                                                                                                                                                                                                       |

| Operation:       | (f) + 1 $\rightarrow$ (destination),<br>skip if result = 0                                                                                                                                                                                                                                                              |

| Status Affected: | None                                                                                                                                                                                                                                                                                                                    |

| Description:     | The contents of register 'f' are<br>incremented. If 'd' is 0, the result is<br>placed in the W register. If 'd' is 1,<br>the result is placed back in<br>register 'f'.<br>If the result is 1, the next instruc-<br>tion is executed. If the result is 0,<br>a NOP is executed instead, making<br>it a 2TCY instruction. |

| GOTO             | Unconditional Branch                                                                                                                                                                              |  |  |  |  |  |

|------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| Syntax:          | [ <i>label</i> ] GOTO k                                                                                                                                                                           |  |  |  |  |  |

| Operands:        | $0 \le k \le 2047$                                                                                                                                                                                |  |  |  |  |  |

| Operation:       | $k \rightarrow PC < 10:0>$<br>PCLATH<4:3> $\rightarrow$ PC<12:11>                                                                                                                                 |  |  |  |  |  |

| Status Affected: | None                                                                                                                                                                                              |  |  |  |  |  |

| Description:     | GOTO is an unconditional branch.<br>The eleven-bit immediate value is<br>loaded into PC bits <10:0>. The<br>upper bits of PC are loaded from<br>PCLATH<4:3>. GOTO is a two-<br>cycle instruction. |  |  |  |  |  |

| IORLW            | Inclusive OR Literal with W                                                                                               |  |  |  |  |  |

|------------------|---------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|