Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                                          |

|----------------------------|--------------------------------------------------------------------------|

| Product Status             | Active                                                                   |

| Core Processor             | PIC                                                                      |

| Core Size                  | 8-Bit                                                                    |

| Speed                      | 20MHz                                                                    |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                                        |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                    |

| Number of I/O              | 22                                                                       |

| Program Memory Size        | 14KB (8K x 14)                                                           |

| Program Memory Type        | FLASH                                                                    |

| EEPROM Size                | -                                                                        |

| RAM Size                   | 368 x 8                                                                  |

| Voltage - Supply (Vcc/Vdd) | 4V ~ 5.5V                                                                |

| Data Converters            | A/D 5x8b                                                                 |

| Oscillator Type            | External                                                                 |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                       |

| Mounting Type              | Surface Mount                                                            |

| Package / Case             | 28-SSOP (0.209", 5.30mm Width)                                           |

| Supplier Device Package    | 28-SSOP                                                                  |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16f76t-e-ss |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

### Note the following details of the code protection feature on PICmicro® MCUs.

- The PICmicro family meets the specifications contained in the Microchip Data Sheet.

- Microchip believes that its family of PICmicro microcontrollers is one of the most secure products of its kind on the market today, when used in the intended manner and under normal conditions.

- There are dishonest and possibly illegal methods used to breach the code protection feature. All of these methods, to our knowledge, require using the PICmicro microcontroller in a manner outside the operating specifications contained in the data sheet. The person doing so may be engaged in theft of intellectual property.

- Microchip is willing to work with the customer who is concerned about the integrity of their code.

- Neither Microchip nor any other semiconductor manufacturer can guarantee the security of their code. Code protection does not

mean that we are guaranteeing the product as "unbreakable".

- Code protection is constantly evolving. We at Microchip are committed to continuously improving the code protection features of our product.

If you have any further questions about this matter, please contact the local sales office nearest to you.

Information contained in this publication regarding device applications and the like is intended through suggestion only and may be superseded by updates. It is your responsibility to ensure that your application meets with your specifications. No representation or warranty is given and no liability is assumed by Microchip Technology Incorporated with respect to the accuracy or use of such information, or infringement of patents or other intellectual property rights arising from such use or otherwise. Use of Microchip's products as critical components in life support systems is not authorized except with express written approval by Microchip. No licenses are conveyed, implicitly or otherwise, under any intellectual property rights.

### **Trademarks**

The Microchip name and logo, the Microchip logo, FilterLab, KEELOQ, MPLAB, PIC, PICmicro, PICMASTER, PICSTART, PRO MATE, SEEVAL and The Embedded Control Solutions Company are registered trademarks of Microchip Technology Incorporated in the U.S.A. and other countries.

dsPIC, ECONOMONITOR, FanSense, FlexROM, fuzzyLAB, In-Circuit Serial Programming, ICSP, ICEPIC, microID, microPort, Migratable Memory, MPASM, MPLIB, MPLINK, MPSIM, MXDEV, PICC, PICDEM, PICDEM.net, rfPIC, Select Mode and Total Endurance are trademarks of Microchip Technology Incorporated in the U.S.A.

Serialized Quick Term Programming (SQTP) is a service mark of Microchip Technology Incorporated in the U.S.A.

All other trademarks mentioned herein are property of their respective companies.

© 2002, Microchip Technology Incorporated, Printed in the U.S.A., All Rights Reserved.

Microchip received QS-9000 quality system certification for its worldwide headquarters, design and wafer fabrication facilities in Chandler and Tempe, Arizona in July 1999. The Company's quality system processes and procedures are QS-9000 compliant for its PICmicro® 8-bit MCUs, KEELO® code hopping devices, Serial EEPROMs and microperipheral products. In addition, Microchip's quality system for the design and manufacture of development systems is ISO 9001 certified.

PIC16F73 AND PIC16F76 BLOCK DIAGRAM FIGURE 1-1: 13 8 **PORTA** Data Bus Program Counter RA0/AN0 FLASH RA1/AN1 Program Memory RA2/AN2/ RAM 8 Level Stack RA3/AN3/VREF File (13-bit) RA4/T0CKI Registers RA5/AN4/SS Program RAM Addr<sup>(1)</sup> 9 Bus **PORTB** RB0/INT Addr MUX Instruction reg RB1 Indirect Addr RB2 Direct Addr 8 RB3/PGM RB4 FSR reg RB5 RB6/PGC RB7/PGD STATUS reg 8 PORTC RC0/T1OSO/T1CKI RC1/T1OSI/CCP2 3 MUX Power-up Timer RC2/CCP1 RC3/SCK/SCL Instruction Decode & Oscillator RC4/SDI/SDA Start-up Timer ALU RC5/SDO Control Power-on Reset RC6/TX/CK RC7/RX/DT Timing Generation Watchdog W reg OSC1/CLKIN Brown-out OSC2/CLKOUT Reset  $\boxtimes$  $\boxtimes$ MCLR VDD, VSS Timer0 Timer1 Timer2 8-bit A/D Synchronous **USART** CCP1 CCP2 Serial Port Device Program FLASH **Data Memory** PIC16F73 192 Bytes 4K PIC16F76 8K 368 Bytes

Note 1: Higher order bits are from the STATUS register.

TABLE 1-2: PIC16F73 AND PIC16F76 PINOUT DESCRIPTION (CONTINUED)

| Pin Name              | DIP<br>SSOP<br>SOIC<br>Pin# | MLF<br>Pin# | I/O/P<br>Type | Buffer<br>Type        | Description                                                                                                           |

|-----------------------|-----------------------------|-------------|---------------|-----------------------|-----------------------------------------------------------------------------------------------------------------------|

|                       |                             |             |               |                       | PORTB is a bi-directional I/O port. PORTB can be software                                                             |

|                       |                             |             |               | (0-(1)                | programmed for internal weak pull-up on all inputs.                                                                   |

| RB0/INT               | 21                          | 18          | I/O           | TTL/ST <sup>(1)</sup> | Digital I/O                                                                                                           |

| RB0<br>INT            |                             |             | I/O           |                       | Digital I/O. External interrupt.                                                                                      |

| RB1                   | 22                          | 19          | I/O           | TTL                   | Digital I/O.                                                                                                          |

| RB2                   | 23                          | 20          | I/O           | TTL                   | Digital I/O.                                                                                                          |

| RB3/PGM               | 24                          | 21          | 1/0           | TTL                   | Digital 1/O.                                                                                                          |

| RB3                   | 24                          | 21          | I/O           | '''                   | Digital I/O.                                                                                                          |

| PGM                   |                             |             | I/O           |                       | Low voltage ICSP programming enable pin.                                                                              |

| RB4                   | 25                          | 22          | I/O           | TTL                   | Digital I/O.                                                                                                          |

| RB5                   | 26                          | 23          | I/O           | TTL                   | Digital I/O.                                                                                                          |

| RB6/PGC               | 27                          | 24          |               | TTL/ST <sup>(2)</sup> | - 19 5.                                                                                                               |

| RB6                   |                             |             | I/O           | ,                     | Digital I/O.                                                                                                          |

| PGC                   |                             |             | I/O           |                       | In-Circuit Debugger and ICSP programming clock.                                                                       |

| RB7/PGD               | 28                          | 25          |               | TTL/ST <sup>(2)</sup> |                                                                                                                       |

| RB7                   |                             |             | I/O           |                       | Digital I/O.                                                                                                          |

| PGD                   |                             |             | I/O           |                       | In-Circuit Debugger and ICSP programming data.                                                                        |

|                       |                             |             |               |                       | PORTC is a bi-directional I/O port.                                                                                   |

| RC0/T1OSO/T1CKI       | 11                          | 8           |               | ST                    |                                                                                                                       |

| RC0                   |                             |             | I/O           |                       | Digital I/O.                                                                                                          |

| T1OSO<br>T1CKI        |                             |             | 0             |                       | Timer1 oscillator output.                                                                                             |

|                       | 40                          | 0           | '             | СТ                    | Timer1 external clock input.                                                                                          |

| RC1/T1OSI/CCP2<br>RC1 | 12                          | 9           | I/O           | ST                    | Digital I/O.                                                                                                          |

| T1OSI                 |                             |             | ı,O           |                       | Timer1 oscillator input.                                                                                              |

| CCP2                  |                             |             | I/O           |                       | Capture2 input, Compare2 output, PWM2 output.                                                                         |

| RC2/CCP1              | 13                          | 10          |               | ST                    |                                                                                                                       |

| RC2                   |                             |             | I/O           |                       | Digital I/O.                                                                                                          |

| CCP1                  |                             |             | I/O           |                       | Capture1 input/Compare1 output/PWM1 output.                                                                           |

| RC3/SCK/SCL           | 14                          | 11          |               | ST                    |                                                                                                                       |

| RC3                   |                             |             | I/O           |                       | Digital I/O.                                                                                                          |

| SCK<br>SCL            |                             |             | I/O<br>I/O    |                       | Synchronous serial clock input/output for SPI mode.  Synchronous serial clock input/output for I <sup>2</sup> C mode. |

| RC4/SDI/SDA           | 15                          | 12          | 1/0           | ST                    | Synchronous serial clock inpulvoutput for 1 C mode.                                                                   |

| RC4/3DI/3DA<br>RC4    | 15                          | 12          | I/O           | 31                    | Digital I/O.                                                                                                          |

| SDI                   |                             |             | ı, C          |                       | SPI data in.                                                                                                          |

| SDA                   |                             |             | I/O           |                       | I <sup>2</sup> C data I/O.                                                                                            |

| RC5/SDO               | 16                          | 13          |               | ST                    |                                                                                                                       |

| RC5                   |                             |             | I/O           |                       | Digital I/O.                                                                                                          |

| SDO                   |                             |             | 0             |                       | SPI data out.                                                                                                         |

| RC6/TX/CK             | 17                          | 14          |               | ST                    |                                                                                                                       |

| RC6                   |                             |             | 1/0           |                       | Digital I/O.                                                                                                          |

| TX<br>CK              |                             |             | 0<br>I/O      |                       | USART asynchronous transmit. USART 1 synchronous clock.                                                               |

| RC7/RX/DT             | 18                          | 15          | 1,0           | ST                    | CONTRI I Synonionous clock.                                                                                           |

| RC7/RX/DT<br>RC7      | 10                          | 10          | I/O           | 31                    | Digital I/O.                                                                                                          |

| RX                    |                             |             | ı, O          |                       | USART asynchronous receive.                                                                                           |

| DT                    |                             |             | I/O           |                       | USART synchronous data.                                                                                               |

| Vss                   | 8, 19                       | 5, 16       | Р             | _                     | Ground reference for logic and I/O pins.                                                                              |

|                       |                             |             |               |                       |                                                                                                                       |

Legend: I = input

O = output

I/O = input/output

P = power

— = Not used

t used TTL = TTL input

ST = Schmitt Trigger input

Note 1: This buffer is a Schmitt Trigger input when configured as the external interrupt.

2: This buffer is a Schmitt Trigger input when used in Serial Programming mode.

3: This buffer is a Schmitt Trigger input when configured in RC Oscillator mode and a CMOS input otherwise.

### 3.0 READING PROGRAM MEMORY

The FLASH Program Memory is readable during normal operation over the entire VDD range. It is indirectly addressed through Special Function Registers (SFR). Up to 14-bit numbers can be stored in memory for use as calibration parameters, serial numbers, packed 7-bit ASCII, etc. Executing a program memory location containing data that forms an invalid instruction results in a

There are five SFRs used to read the program and memory. These registers are:

- PMCON1

- PMDATA

- PMDATH

- PMADR

- PMADRH

The program memory allows word reads. Program memory access allows for checksum calculation and reading calibration tables.

When interfacing to the program memory block, the PMDATH:PMDATA registers form a two-byte word, which holds the 14-bit data for reads. The PMADRH:PMADR registers form a two-byte word, which holds the 13-bit address of the FLASH location being accessed. These devices can have up to 8K words of program FLASH, with an address range from 0h to 3FFFh. The unused upper bits in both the PMDATH and PMADRH registers are not implemented and read as "0's".

### 3.1 PMADR

The address registers can address up to a maximum of 8K words of program FLASH.

When selecting a program address value, the MSByte of the address is written to the PMADRH register and the LSByte is written to the PMADR register. The upper MSbits of PMADRH must always be clear.

### 3.2 PMCON1 Register

PMCON1 is the control register for memory accesses.

The control bit RD initiates read operations. This bit cannot be cleared, only set, in software. It is cleared in hardware at the completion of the read operation.

### REGISTER 3-1: PMCON1 REGISTER (ADDRESS 18Ch)

| R-1      | U-0 | U-0 | U-0 | U-x | U-0 | U-0 | R/S-0 |

|----------|-----|-----|-----|-----|-----|-----|-------|

| reserved | _   | _   | _   | _   | _   | _   | RD    |

| bit 7    |     |     |     |     |     |     | bit 0 |

bit 7 **Reserved:** Read as '1'

bit 6-1 **Unimplemented**: Read as '0'

bit 0 RD: Read Control bit

1 = Initiates a FLASH read, RD is cleared in hardware. The RD bit can only be set (not cleared)

in software.

0 = FLASH read completed

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

- n = Value at POR reset '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

## 3.3 Reading the FLASH Program Memory

A program memory location may be read by writing two bytes of the address to the PMADR and PMADRH registers and then setting control bit RD (PMCON1<0>). Once the read control bit is set, the microcontroller will use the next two instruction cycles to read the data. The data is available in the PMDATA and PMDATH registers after the second NOP instruction. Therefore, it can be read as two bytes in the following instructions. The PMDATA and PMDATH registers will hold this value until the next read operation.

### 3.4 Operation During Code Protect

FLASH program memory has its own code protect mechanism. External Read and Write operations by programmers are disabled if this mechanism is enabled.

The microcontroller can read and execute instructions out of the internal FLASH program memory, regardless of the state of the code protect configuration bits.

### **EXAMPLE 3-1: FLASH PROGRAM READ**

```

STATUS, RP1

; Bank 2

BCF

STATUS, RPO

MOVF

ADDRH, W

MOVWF

PMADRH

; MSByte of Program Address to read

MOVF

ADDRL, W

;

MOVWF

PMADR

; LSByte of Program Address to read

BSF

STATUS, RPO ; Bank 3 Required

Required

BSF

PMCON1, RD

; EEPROM Read Sequence

; memory is read in the next two cycles after BSF PMCON1,RD

Sequence

NOP

NOP

BCF

STATUS, RPO

; Bank 2

; W = LSByte of Program PMDATA

MOVF

PMDATA, W

MOVF

PMDATH, W

; W = MSByte of Program PMDATA

```

### TABLE 3-1: REGISTERS ASSOCIATED WITH PROGRAM FLASH

| Address | Name   | Bit 7     | Bit 6                          | Bit 5   | Bit 4 | Bit 3 | Bit 2 | Bit 1     | Bit 0     | Value on:<br>POR,<br>BOR | Value on<br>all other<br>RESETS |

|---------|--------|-----------|--------------------------------|---------|-------|-------|-------|-----------|-----------|--------------------------|---------------------------------|

| 10Dh    | PMADR  | Address F | Register Lo                    | ow Byte |       |       |       |           |           | xxxx xxxx                | uuuu uuuu                       |

| 10Fh    | PMADRH | _         | — — Address Register High Byte |         |       |       |       |           | xxxx xxxx | uuuu uuuu                |                                 |

| 10Ch    | PMDATA | Data Reg  | ister Low I                    | Byte    |       |       |       |           |           | xxxx xxxx                | uuuu uuuu                       |

| 10Eh    | PMDATH | _         | — — Data Register High Byte    |         |       |       |       | xxxx xxxx | uuuu uuuu |                          |                                 |

| 18Ch    | PMCON1 | (1)       | _                              | _       | _     | _     | _     | _         | RD        | 10                       | 10                              |

Legend: x = unknown, u = unchanged, r = reserved, - = unimplemented read as '0'. Shaded cells are not used during FLASH access. **Note 1:** This bit always reads as a '1'.

### 8.5.3 SETUP FOR PWM OPERATION

The following steps should be taken when configuring the CCP module for PWM operation:

- 1. Set the PWM period by writing to the PR2 register.

- 2. Set the PWM duty cycle by writing to the CCPR1L register and CCP1CON<5:4> bits.

- Make the CCP1 pin an output by clearing the TRISC<2> bit.

- 4. Set the TMR2 prescale value and enable Timer2 by writing to T2CON.

- 5. Configure the CCP1 module for PWM operation.

TABLE 8-4: EXAMPLE PWM FREQUENCIES AND RESOLUTIONS (Fosc = 20 MHz)

| PWM Frequency             | 1.22 kHz | 4.88 kHz | 19.53 kHz | 78.12 kHz | 156.3 kHz | 208.3 kHz |

|---------------------------|----------|----------|-----------|-----------|-----------|-----------|

| Timer Prescale (1, 4, 16) | 16       | 4        | 1         | 1         | 1         | 1         |

| PR2 Value                 | 0xFF     | 0xFF     | 0xFF      | 0x3F      | 0x1F      | 0x17      |

| Maximum Resolution (bits) | 10       | 10       | 10        | 8         | 7         | 5.5       |

TABLE 8-5: REGISTERS ASSOCIATED WITH PWM AND TIMER2

| Address               | Name    | Bit 7                | Bit 6                               | Bit 5       | Bit 4     | Bit 3   | Bit 2  | Bit 1   | Bit 0   | PC   | e on:<br>OR,<br>OR | all o | e on<br>other<br>SETS |

|-----------------------|---------|----------------------|-------------------------------------|-------------|-----------|---------|--------|---------|---------|------|--------------------|-------|-----------------------|

| 0Bh,8Bh,<br>10Bh,18Bh | INTCON  | GIE                  | PEIE                                | TMR0IE      | INTE      | RBIE    | TMR0IF | INTF    | RBIF    | 0000 | 000x               | 0000  | 000u                  |

| 0Ch                   | PIR1    | PSPIF <sup>(1)</sup> | ADIF                                | RCIF        | TXIF      | SSPIF   | CCP1IF | TMR2IF  | TMR1IF  | 0000 | 0000               | 0000  | 0000                  |

| 0Dh                   | PIR2    | _                    | _                                   | _           | _         | _       | _      | _       | CCP2IF  |      | 0                  |       | 0                     |

| 8Ch                   | PIE1    | PSPIE <sup>(1)</sup> | ADIE                                | RCIE        | TXIE      | SSPIE   | CCP1IE | TMR2IE  | TMR1IE  | 0000 | 0000               | 0000  | 0000                  |

| 8Dh                   | PIE2    | _                    | _                                   | _           | _         | _       | _      | _       | CCP2IE  |      | 0                  |       | 0                     |

| 87h                   | TRISC   | PORTC D              | Data Direction                      | on Register | •         |         |        |         |         | 1111 | 1111               | 1111  | 1111                  |

| 11h                   | TMR2    | Timer2 M             | odule Regi                          | ster        |           |         |        |         |         | 0000 | 0000               | 0000  | 0000                  |

| 92h                   | PR2     | Timer2 M             | odule Perio                         | d Register  |           |         |        |         |         | 1111 | 1111               | 1111  | 1111                  |

| 12h                   | T2CON   | _                    | TOUTPS3                             | TOUTPS2     | TOUTPS1   | TOUTPS0 | TMR2ON | T2CKPS1 | T2CKPS0 | -000 | 0000               | -000  | 0000                  |

| 15h                   | CCPR1L  | Capture/0            | Compare/P\                          | VM Regist   | er1 (LSB) |         |        |         |         | xxxx | xxxx               | uuuu  | uuuu                  |

| 16h                   | CCPR1H  | Capture/0            | Compare/P\                          | VM Regist   | er1 (MSB) |         |        |         |         | xxxx | xxxx               | uuuu  | uuuu                  |

| 17h                   | CCP1CON | _                    | _                                   | CCP1X       | CCP1Y     | CCP1M3  | CCP1M2 | CCP1M1  | CCP1M0  | 00   | 0000               | 00    | 0000                  |

| 1Bh                   | CCPR2L  | Capture/0            | Capture/Compare/PWM Register2 (LSB) |             |           |         |        |         |         | xxxx | xxxx               | uuuu  | uuuu                  |

| 1Ch                   | CCPR2H  | Capture/0            | Compare/P\                          | WM Regist   | er2 (MSB) |         |        |         |         | xxxx | xxxx               | uuuu  | uuuu                  |

| 1Dh                   | CCP2CON | _                    | _                                   | CCP2X       | CCP2Y     | ССР2М3  | CCP2M2 | CCP2M1  | CCP2M0  | 00   | 0000               | 00    | 0000                  |

$\label{eq:local_local_local} \textbf{Legend:} \quad \textbf{x} = \textbf{unknown}, \, \textbf{u} = \textbf{unchanged}, \, \textbf{-} = \textbf{unimplemented}, \, \textbf{read as '0'}. \, \textbf{Shaded cells are not used by PWM and Timer2}.$

Note 1: Bits PSPIE and PSPIF are reserved on the PIC16F73/76; always maintain these bits clear.

### 9.3.2 MASTER MODE

Master mode of operation is supported in firmware using interrupt generation on the detection of the START and STOP conditions. The STOP (P) and START (S) bits are cleared from a RESET or when the SSP module is disabled. The STOP (P) and START (S) bits will toggle based on the START and STOP conditions. Control of the I<sup>2</sup>C bus may be taken when the P bit is set, or the bus is IDLE and both the S and P bits are clear.

In Master mode, the SCL and SDA lines are manipulated by clearing the corresponding TRISC<4:3> bit(s). The output level is always low, irrespective of the value(s) in PORTC<4:3>. So when transmitting data, a '1' data bit must have the TRISC<4> bit set (input) and a '0' data bit must have the TRISC<4> bit cleared (output). The same scenario is true for the SCL line with the TRISC<3> bit. Pull-up resistors must be provided externally to the SCL and SDA pins for proper operation of the I<sup>2</sup>C module.

The following events will cause SSP Interrupt Flag bit, SSPIF, to be set (SSP Interrupt will occur if enabled):

- START condition

- · STOP condition

- · Data transfer byte transmitted/received

Master mode of operation can be done with either the Slave mode IDLE (SSPM3:SSPM0 = 1011), or with the Slave active. When both Master and Slave modes are enabled, the software needs to differentiate the source(s) of the interrupt.

### 9.3.3 MULTI-MASTER MODE

In Multi-Master mode, the interrupt generation on the detection of the START and STOP conditions, allows the determination of when the bus is free. The STOP (P) and START (S) bits are cleared from a RESET or when the SSP module is disabled. The STOP (P) and START (S) bits will toggle based on the START and STOP conditions. Control of the I<sup>2</sup>C bus may be taken when bit P (SSPSTAT<4>) is set, or the bus is IDLE and both the S and P bits clear. When the bus is busy, enabling the SSP Interrupt will generate the interrupt when the STOP condition occurs.

In Multi-Master operation, the SDA line must be monitored to see if the signal level is the expected output level. This check only needs to be done when a high level is output. If a high level is expected and a low level is present, the device needs to release the SDA and SCL lines (set TRISC<4:3>). There are two stages where this arbitration can be lost, these are:

- Address Transfer

- Data Transfer

When the slave logic is enabled, the slave continues to receive. If arbitration was lost during the address transfer stage, communication to the device may be in progress. If addressed, an  $\overline{ACK}$  pulse will be generated. If arbitration was lost during the data transfer stage, the device will need to retransfer the data at a later time.

TABLE 9-3: REGISTERS ASSOCIATED WITH I<sup>2</sup>C OPERATION

| Address                | Name    | Bit 7                | Bit 6                        | Bit 5                  | Bit 4     | Bit 3     | Bit 2      | Bit 1  | Bit 0  | Value on:<br>POR,<br>BOR | Value on<br>all other<br>RESETS |

|------------------------|---------|----------------------|------------------------------|------------------------|-----------|-----------|------------|--------|--------|--------------------------|---------------------------------|

| 0Bh, 8Bh,<br>10Bh,18Bh | INTCON  | GIE                  | PEIE                         | TMR0IE                 | INTE      | RBIE      | TMR0IF     | INTF   | RBIF   | 0000 000x                | 0000 000u                       |

| 0Ch                    | PIR1    | PSPIF <sup>(1)</sup> | ADIF                         | RCIF                   | TXIF      | SSPIF     | CCP1IF     | TMR2IF | TMR1IF | 0000 0000                | 0000 0000                       |

| 8Ch                    | PIE1    | PSPIE <sup>(1)</sup> | ADIE                         | RCIE                   | TXIE      | SSPIE     | CCP1IE     | TMR2IE | TMR1IE | 0000 0000                | 0000 0000                       |

| 13h                    | SSPBUF  | Synchrono            | us Serial                    | Port Rece              | eive Buff | er/Transn | nit Regist | er     |        | xxxx xxxx                | uuuu uuuu                       |

| 93h                    | SSPADD  | Synchrono            | us Serial                    | Port (I <sup>2</sup> C | mode) A   | ddress R  | egister    |        |        | 0000 0000                | 0000 0000                       |

| 14h                    | SSPCON  | WCOL                 | SSPOV                        | SSPEN                  | CKP       | SSPM3     | SSPM2      | SSPM1  | SSPM0  | 0000 0000                | 0000 0000                       |

| 94h                    | SSPSTAT | SMP <sup>(2)</sup>   | CKE <sup>(2)</sup>           | D/Ā                    | Р         | S         | R/W        | UA     | BF     | 0000 0000                | 0000 0000                       |

| 87h                    | TRISC   | PORTC Da             | DRTC Data Direction Register |                        |           |           |            |        |        |                          | 1111 1111                       |

Legend: x = unknown, u = unchanged, - = unimplemented locations read as '0'. Shaded cells are not used by SSP module in I<sup>2</sup>C mode.

Note 1: PSPIF and PSPIE are reserved on the PIC16F73/76; always maintain these bits clear.

2: Maintain these bits clear in I<sup>2</sup>C mode.

# PIC16F7X

NOTES:

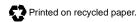

### 12.4 MCLR

PIC16F7X devices have a noise filter in the MCLR Reset path. The filter will detect and ignore small pulses.

It should be noted that a WDT Reset does not drive  $\overline{\text{MCLR}}$  pin low.

The behavior of the ESD protection on the MCLR pin has been altered from previous devices of this family. Voltages applied to the pin that exceed its specification can result in both MCLR Resets and excessive current beyond the device specification during the ESD event. For this reason, Microchip recommends that the MCLR pin no longer be tied directly to VDD. The use of an RC network, as shown in Figure 12-5, is suggested.

FIGURE 12-5: RECOMMENDED MCLR

CIRCUIT

### 12.5 Power-on Reset (POR)

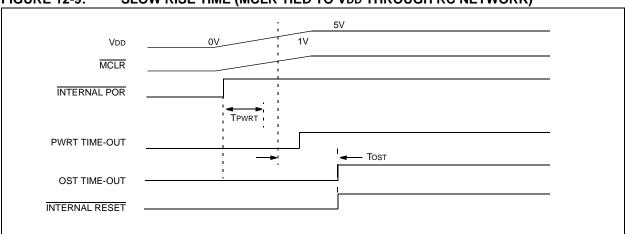

A Power-on Reset pulse is generated on-chip when VDD rise is detected (in the range of 1.2V - 1.7V). To take advantage of the POR, tie the MCLR pin to VDD as described in Section 12.4. A maximum rise time for VDD is specified. See the Electrical Specifications for details.

When the device starts normal operation (exits the RESET condition), device operating parameters (voltage, frequency, temperature,...) must be met to ensure operation. If these conditions are not met, the device must be held in RESET until the operating conditions are met. For additional information, refer to Application Note, AN607, "Power-up Trouble Shooting" (DS00607).

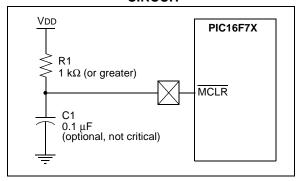

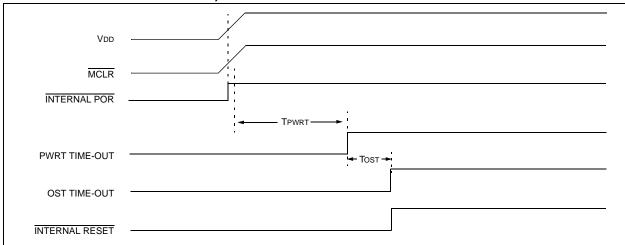

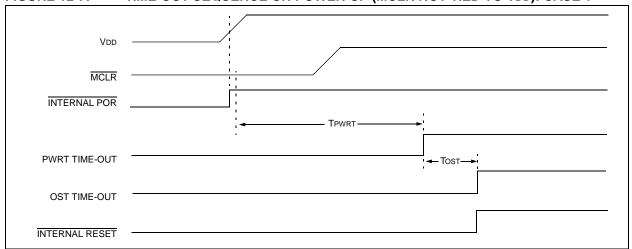

### 12.6 Power-up Timer (PWRT)

The Power-up Timer provides a fixed 72 ms nominal time-out on power-up only from the POR. The Power-up Timer operates on an internal RC oscillator. The chip is kept in RESET as long as the PWRT is active. The PWRT's time delay allows VDD to rise to an acceptable level. A configuration bit is provided to enable/ disable the PWRT.

The power-up time delay will vary from chip to chip, due to VDD, temperature and process variation. See DC parameters for details (TPWRT, parameter #33).

### 12.7 Oscillator Start-up Timer (OST)

The Oscillator Start-up Timer (OST) provides 1024 oscillator cycles (from OSC1 input) delay after the PWRT delay is over (if enabled). This helps to ensure that the crystal oscillator or resonator has started and stabilized.

The OST time-out is invoked only for XT, LP and HS modes and only on Power-on Reset, or wake-up from SLEEP.

### 12.8 Brown-out Reset (BOR)

The configuration bit, BODEN, can enable or disable the Brown-out Reset circuit. If VDD falls below VBOR (parameter D005, about 4V) for longer than TBOR (parameter #35, about 100  $\mu\text{S}$ ), the brown-out situation will reset the device. If VDD falls below VBOR for less than TBOR, a RESET may not occur.

Once the brown-out occurs, the device will remain in Brown-out Reset until VDD rises above VBOR. The Power-up Timer then keeps the device in RESET for TPWRT (parameter #33, about 72 mS). If VDD should fall below VBOR during TPWRT, the Brown-out Reset process will restart when VDD rises above VBOR, with the Power-up Timer Reset. The Power-up Timer is always enabled when the Brown-out Reset circuit is enabled, regardless of the state of the PWRT configuration bit.

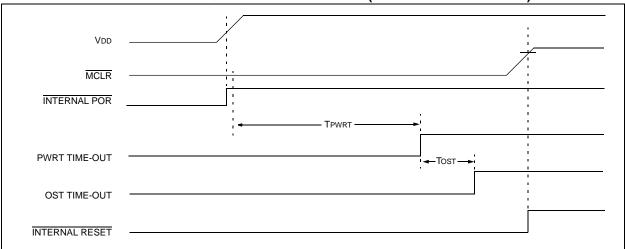

### 12.9 Time-out Sequence

On power-up, the time-out sequence is as follows: the PWRT delay starts (if enabled) when a POR Reset occurs. Then, OST starts counting 1024 oscillator cycles when PWRT ends (LP, XT, HS). When the OST ends, the device comes out of RESET.

If MCLR is kept low long enough, all delays will expire. Bringing MCLR high will begin execution immediately. This is useful for testing purposes or to synchronize more than one PIC16F7X device operating in parallel.

Table 12-5 shows the RESET conditions for the STATUS, PCON and PC registers, while Table 12-6 shows the RESET conditions for all the registers.

TABLE 12-6: INITIALIZATION CONDITIONS FOR ALL REGISTERS (CONTINUED)

| Register | Devices |    | Power-on Reset,<br>Brown-out Reset | MCLR Reset,<br>WDT Reset | Wake-up via WDT or<br>Interrupt |           |           |

|----------|---------|----|------------------------------------|--------------------------|---------------------------------|-----------|-----------|

| PIE2     | 73      | 74 | 76                                 | 77                       | 0                               | 0         | u         |

| PCON     | 73      | 74 | 76                                 | 77                       | qq                              | uu        | uu        |

| PR2      | 73      | 74 | 76                                 | 77                       | 1111 1111                       | 1111 1111 | 1111 1111 |

| SSPSTAT  | 73      | 74 | 76                                 | 77                       | 00 0000                         | 00 0000   | uu uuuu   |

| SSPADD   | 73      | 74 | 76                                 | 77                       | 0000 0000                       | 0000 0000 | uuuu uuuu |

| TXSTA    | 73      | 74 | 76                                 | 77                       | 0000 -010                       | 0000 -010 | uuuu -uuu |

| SPBRG    | 73      | 74 | 76                                 | 77                       | 0000 0000                       | 0000 0000 | uuuu uuuu |

| ADCON1   | 73      | 74 | 76                                 | 77                       | 000                             | 000       | uuu       |

| PMDATA   | 73      | 74 | 76                                 | 77                       | 0 0000                          | 0 0000    | u uuuu    |

| PMADR    | 73      | 74 | 76                                 | 77                       | xxxx xxxx                       | uuuu uuuu | uuuu uuuu |

| PMDATH   | 73      | 74 | 76                                 | 77                       | xxxx xxxx                       | uuuu uuuu | uuuu uuuu |

| PMADRH   | 73      | 74 | 76                                 | 77                       | xxxx xxxx                       | uuuu uuuu | uuuu uuuu |

| PMCON1   | 73      | 74 | 76                                 | 77                       | 10                              | 10        | 1u        |

Legend: u = unchanged, x = unknown, - = unimplemented bit, read as '0', q = value depends on condition, r = reserved, maintain clear

- Note 1: One or more bits in INTCON, PIR1 and/or PIR2 will be affected (to cause wake-up).

- 2: When the wake-up is due to an interrupt and the GIE bit is set, the PC is loaded with the interrupt vector (0004h).

- 3: See Table 12-5 for RESET value for specific condition.

FIGURE 12-6: TIME-OUT SEQUENCE ON POWER-UP (MCLR TIED TO VDD THROUGH RC NETWORK)

FIGURE 12-7: TIME-OUT SEQUENCE ON POWER-UP (MCLR NOT TIED TO VDD): CASE 1

FIGURE 12-8: TIME-OUT SEQUENCE ON POWER-UP (MCLR NOT TIED TO VDD): CASE 2

FIGURE 12-9: SLOW RISE TIME (MCLR TIED TO VDD THROUGH RC NETWORK)

# PIC16F7X

NOTES:

# PIC16F7X

NOTES:

### 15.0 ELECTRICAL CHARACTERISTICS

### **Absolute Maximum Ratings †**

| Ambient temperature under bias                                                                            | 55 to +125°C                                       |

|-----------------------------------------------------------------------------------------------------------|----------------------------------------------------|

| Storage temperature                                                                                       | 65°C to +150°C                                     |

| Voltage on any pin with respect to Vss (except VDD, MCLR. and RA4)                                        | 0.3V to (VDD + 0.3V)                               |

| Voltage on VDD with respect to Vss                                                                        | 0.3 to +6.5V                                       |

| Voltage on MCLR with respect to Vss (Note 2)                                                              | 0 to +13.5V                                        |

| Voltage on RA4 with respect to Vss                                                                        | 0 to +12V                                          |

| Total power dissipation (Note 1)                                                                          | 1.0W                                               |

| Maximum current out of Vss pin                                                                            | 300 mA                                             |

| Maximum current into VDD pin                                                                              | 250 mA                                             |

| Input clamp current, IiK (VI < 0 or VI > VDD)                                                             | ± 20 mA                                            |

| Output clamp current, lok (Vo < 0 or Vo > VDD)                                                            |                                                    |

| Maximum output current sunk by any I/O pin                                                                | 25 mA                                              |

| Maximum output current sourced by any I/O pin                                                             | 25 mA                                              |

| Maximum current sunk by PORTA, PORTB, and PORTE (combined) (Note 3)                                       | 200 mA                                             |

| Maximum current sourced by PORTA, PORTB, and PORTE (combined) (Note 3)                                    | 200 mA                                             |

| Maximum current sunk by PORTC and PORTD (combined) (Note 3)                                               | 200 mA                                             |

| Maximum current sourced by PORTC and PORTD (combined) (Note 3)                                            | 200 mA                                             |

| Note 4. Dower discipation is calculated as follows: Ddis. Vpp v (lpp. \(\nabla\) is \(\nabla\) \(\nabla\) | Vouly loui + \(\frac{\chi}{2}\) \(\frac{\chi}{2}\) |

- Note 1: Power dissipation is calculated as follows: Pdis = VDD x {IDD  $\Sigma$  IOH} +  $\Sigma$  {(VDD VOH) x IOH} +  $\Sigma$ (VOI x IOL)

- 2: Voltage spikes at the  $\overline{MCLR}$  pin may cause latchup. A series resistor of greater than 1 k $\Omega$  should be used to pull  $\overline{MCLR}$  to VDD, rather than tying the pin directly to VDD.

- 3: PORTD and PORTE are not implemented on the PIC16F73/76 devices.

† NOTICE: Stresses above those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress rating only and functional operation of the device at those or any other conditions above those indicated in the operation listings of this specification is not implied. Exposure to maximum rating conditions for extended periods may affect device reliability.

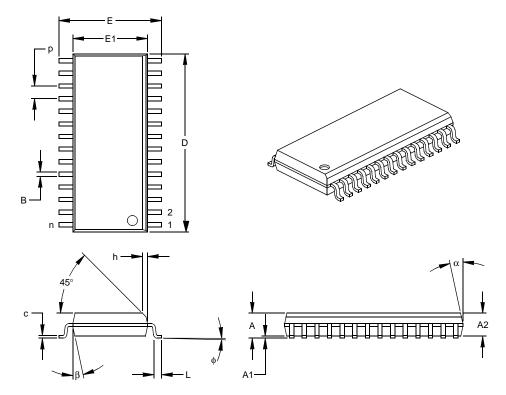

## 28-Lead Plastic Small Outline (SO) - Wide, 300 mil (SOIC)

|                          | Units    |      | INCHES* |      | N     | 1ILLIMETERS | 3     |

|--------------------------|----------|------|---------|------|-------|-------------|-------|

| Dimensio                 | n Limits | MIN  | NOM     | MAX  | MIN   | NOM         | MAX   |

| Number of Pins           | n        |      | 28      |      |       | 28          |       |

| Pitch                    | р        |      | .050    |      |       | 1.27        |       |

| Overall Height           | Α        | .093 | .099    | .104 | 2.36  | 2.50        | 2.64  |

| Molded Package Thickness | A2       | .088 | .091    | .094 | 2.24  | 2.31        | 2.39  |

| Standoff §               | A1       | .004 | .008    | .012 | 0.10  | 0.20        | 0.30  |

| Overall Width            | Е        | .394 | .407    | .420 | 10.01 | 10.34       | 10.67 |

| Molded Package Width     | E1       | .288 | .295    | .299 | 7.32  | 7.49        | 7.59  |

| Overall Length           | D        | .695 | .704    | .712 | 17.65 | 17.87       | 18.08 |

| Chamfer Distance         | h        | .010 | .020    | .029 | 0.25  | 0.50        | 0.74  |

| Foot Length              | L        | .016 | .033    | .050 | 0.41  | 0.84        | 1.27  |

| Foot Angle Top           | ф        | 0    | 4       | 8    | 0     | 4           | 8     |

| Lead Thickness           | С        | .009 | .011    | .013 | 0.23  | 0.28        | 0.33  |

| Lead Width               | В        | .014 | .017    | .020 | 0.36  | 0.42        | 0.51  |

| Mold Draft Angle Top     | α        | 0    | 12      | 15   | 0     | 12          | 15    |

| Mold Draft Angle Bottom  | β        | 0    | 12      | 15   | 0     | 12          | 15    |

Dimensions D and E1 do not include mold flash or protrusions. Mold flash or protrusions shall not exceed

.010" (0.254mm) per side. JEDEC Equivalent: MS-013 Drawing No. C04-052

<sup>\*</sup> Controlling Parameter § Significant Characteristic

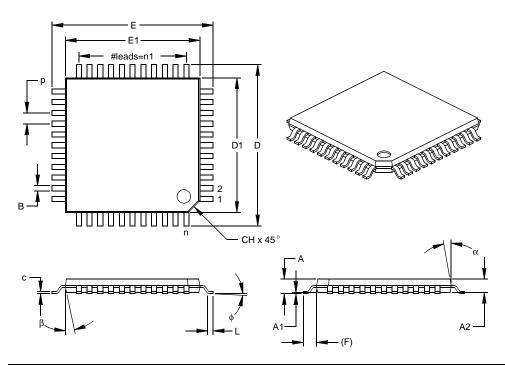

## 44-Lead Plastic Thin Quad Flatpack (PT) 10x10x1 mm Body, 1.0/0.10 mm Lead Form (TQFP)

|                          | Units  |      |      |      | М     | MILLIMETERS* |       |  |

|--------------------------|--------|------|------|------|-------|--------------|-------|--|

| Dimension                | Limits | MIN  | MOM  | MAX  | MIN   | NOM          | MAX   |  |

| Number of Pins           | n      |      | 44   |      |       | 44           |       |  |

| Pitch                    | р      |      | .031 |      |       | 0.80         |       |  |

| Pins per Side            | n1     |      | 11   |      |       | 11           |       |  |

| Overall Height           | Α      | .039 | .043 | .047 | 1.00  | 1.10         | 1.20  |  |

| Molded Package Thickness | A2     | .037 | .039 | .041 | 0.95  | 1.00         | 1.05  |  |

| Standoff §               | A1     | .002 | .004 | .006 | 0.05  | 0.10         | 0.15  |  |

| Foot Length              | L      | .018 | .024 | .030 | 0.45  | 0.60         | 0.75  |  |

| Footprint (Reference)    | (F)    |      | .039 |      | 1.00  |              |       |  |

| Foot Angle               | ф      | 0    | 3.5  | 7    | 0     | 3.5          | 7     |  |

| Overall Width            | Е      | .463 | .472 | .482 | 11.75 | 12.00        | 12.25 |  |

| Overall Length           | D      | .463 | .472 | .482 | 11.75 | 12.00        | 12.25 |  |

| Molded Package Width     | E1     | .390 | .394 | .398 | 9.90  | 10.00        | 10.10 |  |

| Molded Package Length    | D1     | .390 | .394 | .398 | 9.90  | 10.00        | 10.10 |  |

| Lead Thickness           | С      | .004 | .006 | .008 | 0.09  | 0.15         | 0.20  |  |

| Lead Width               | В      | .012 | .015 | .017 | 0.30  | 0.38         | 0.44  |  |

| Pin 1 Corner Chamfer     | CH     | .025 | .035 | .045 | 0.64  | 0.89         | 1.14  |  |

| Mold Draft Angle Top     | α      | 5    | 10   | 15   | 5     | 10           | 15    |  |

| Mold Draft Angle Bottom  | β      | 5    | 10   | 15   | 5     | 10           | 15    |  |

<sup>\*</sup> Controlling Parameter § Significant Characteristic

Dimensions D1 and E1 do not include mold flash or protrusions. Mold flash or protrusions shall not exceed

.010" (0.254mm) per side.

JEDEC Equivalent: MS-026

Drawing No. C04-076

## **APPENDIX A: REVISION HISTORY**

| Version | Date | Revision Description                                                                                                                                                       |

|---------|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| A       | 2000 | This is a new data sheet. However, these devices are similar to the PIC16C7X devices found in the PIC16C7X Data Sheet (DS30390) or the PIC16F87X devices (DS30292).        |

| В       | 2001 | Final data sheet. Includes device characterization data. Addition of extended temperature devices. Addition of 28-pin MLF package. Minor typographic revisions throughout. |

# APPENDIX B: DEVICE DIFFERENCES

The differences between the devices in this data sheet are listed in Table B-1.

TABLE B-1: DEVICE DIFFERENCES

| Difference                          | PIC16F73                                                | PIC16F74                                  | PIC16F76                                                | PIC16F77                                  |

|-------------------------------------|---------------------------------------------------------|-------------------------------------------|---------------------------------------------------------|-------------------------------------------|

| FLASH Program Memory (14-bit words) | 4K                                                      | 4K                                        | 8K                                                      | 8K                                        |

| Data Memory (bytes)                 | 192                                                     | 192                                       | 368                                                     | 368                                       |

| I/O Ports                           | 3                                                       | 5                                         | 3                                                       | 5                                         |

| A/D                                 | 5 channels,<br>8 bits                                   | 8 channels,<br>8 bits                     | 5 channels,<br>8 bits                                   | 8 channels,<br>8 bits                     |

| Parallel Slave Port                 | no                                                      | yes                                       | no                                                      | yes                                       |

| Interrupt Sources                   | 11                                                      | 12                                        | 11                                                      | 12                                        |

| Packages                            | 28-pin PDIP<br>28-pin SOIC<br>28-pin SSOP<br>28-pin MLF | 40-pin PDIP<br>44-pin TQFP<br>44-pin PLCC | 28-pin PDIP<br>28-pin SOIC<br>28-pin SSOP<br>28-pin MLF | 40-pin PDIP<br>44-pin TQFP<br>44-pin PLCC |

### **ON-LINE SUPPORT**

Microchip provides on-line support on the Microchip World Wide Web (WWW) site.

The web site is used by Microchip as a means to make files and information easily available to customers. To view the site, the user must have access to the Internet and a web browser, such as Netscape or Microsoft Explorer. Files are also available for FTP download from our FTP site.

### Connecting to the Microchip Internet Web Site

The Microchip web site is available by using your favorite Internet browser to attach to:

### www.microchip.com

The file transfer site is available by using an FTP service to connect to:

### ftp://ftp.microchip.com

The web site and file transfer site provide a variety of services. Users may download files for the latest Development Tools, Data Sheets, Application Notes, User's Guides, Articles and Sample Programs. A variety of Microchip specific business information is also available, including listings of Microchip sales offices, distributors and factory representatives. Other data available for consideration is:

- · Latest Microchip Press Releases

- Technical Support Section with Frequently Asked Questions

- Design Tips

- · Device Errata

- Job Postings

- · Microchip Consultant Program Member Listing

- Links to other useful web sites related to Microchip Products

- Conferences for products, Development Systems, technical information and more

- · Listing of seminars and events

### **Systems Information and Upgrade Hot Line**

The Systems Information and Upgrade Line provides system users a listing of the latest versions of all of Microchip's development systems software products. Plus, this line provides information on how customers can receive any currently available upgrade kits. The Hot Line Numbers are:

1-800-755-2345 for U.S. and most of Canada, and 1-480-792-7302 for the rest of the world.

013001

### PIC16F7X PRODUCT IDENTIFICATION SYSTEM

To order or obtain information, e.g., on pricing or delivery, refer to the factory or the listed sales office.

| <u>x</u>                                          | <u>xxx</u>                                                                                                                                                                                                                                                                          | Examples:                                                                                                                                                                                                                                                                                                                                                                                    |  |

|---------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Range                                             |                                                                                                                                                                                                                                                                                     | a) PIC16F77-I/P 301 = Industrial temp., PDIP package, normal VDD limits, QTP pattern #301. b) PIC16LF76-I/SO = Industrial temp., SOIC package, Extended VDD limits. c) PIC16F74-E/P = Extended temp., PDIP package, normal VDD limits.                                                                                                                                                       |  |

| $I = -40^{\circ}C \text{ to } +85^{\circ}C$       | (Industrial)                                                                                                                                                                                                                                                                        | Note 1: F = CMOS FLASH  LF = Low Power CMOS FLASH                                                                                                                                                                                                                                                                                                                                            |  |

| PT = TQFP (Thin Quad<br>SO = SOIC                 | d Flatpack)                                                                                                                                                                                                                                                                         | 2: T = in tape and reel - SOIC, PLCC, SSOP, TQFP packages only.                                                                                                                                                                                                                                                                                                                              |  |

| QTP, SQTP, Code or Special I<br>(blank otherwise) | Requirements                                                                                                                                                                                                                                                                        |                                                                                                                                                                                                                                                                                                                                                                                              |  |

|                                                   | PIC16F7X <sup>(1)</sup> , PIC16F7XT <sup>(1)</sup> ; PIC16LF7X <sup>(1)</sup> , PIC16LF7XT <sup>(1)</sup> I = -40°C to +85°C E = -40°C to +125°C  ML = MLF (Micro Lead PT = TQFP (Thin Qua SO = SOIC SP = Skinny Plastic DI P = PDIP L = PLCC SS = SSOP  QTP, SQTP, Code or Special | PIC16F7X <sup>(1)</sup> , PIC16F7XT <sup>(1)</sup> ; VDD range 4.0V to 5.5V PIC16LF7X <sup>(1)</sup> , PIC16LF7XT <sup>(1)</sup> ; VDD range 2.0V to 5.5V  I = -40°C to +85°C (Industrial) E = -40°C to +125°C (Extended)  ML = MLF (Micro Lead Frame) PT = TQFP (Thin Quad Flatpack) SO = SOIC SP = Skinny Plastic DIP P = PDIP L = PLCC SS = SSOP  QTP, SQTP, Code or Special Requirements |  |

### **Sales and Support**

### Data Sheets

Products supported by a preliminary Data Sheet may have an errata sheet describing minor operational differences and recommended workarounds. To determine if an errata sheet exists for a particular device, please contact one of the following:

- 1. Your local Microchip sales office

- 2. The Microchip Corporate Literature Center U.S. FAX: (480) 792-7277

- 3. The Microchip Worldwide Site (www.microchip.com)

Please specify which device, revision of silicon and Data Sheet (include Literature #) you are using.

### **New Customer Notification System**

Register on our web site (www.microchip.com/cn) to receive the most current information on our products.

## WORLDWIDE SALES AND SERVICE

### **AMERICAS**

### **Corporate Office**

2355 West Chandler Blvd. Chandler, AZ 85224-6199 Tel: 480-792-7200 Fax: 480-792-7277 Technical Support: 480-792-7627 Web Address: http://www.microchip.com

### **Rocky Mountain**

2355 West Chandler Blvd. Chandler, AZ 85224-6199 Tel: 480-792-7966 Fax: 480-792-7456

### Atlanta

500 Sugar Mill Road, Suite 200B Atlanta, GA 30350 Tel: 770-640-0034 Fax: 770-640-0307

### **Boston**

2 Lan Drive, Suite 120 Westford, MA 01886 Tel: 978-692-3848 Fax: 978-692-3821

### Chicago

333 Pierce Road, Suite 180 Itasca, IL 60143 Tel: 630-285-0071 Fax: 630-285-0075

### Dallas

4570 Westgrove Drive, Suite 160 Addison, TX 75001 Tel: 972-818-7423 Fax: 972-818-2924

### Detroit

Tri-Atria Office Building 32255 Northwestern Highway, Suite 190 Farmington Hills, MI 48334 Tel: 248-538-2250 Fax: 248-538-2260

### Kokomo

2767 S. Albright Road Kokomo, Indiana 46902 Tel: 765-864-8360 Fax: 765-864-8387

Los Angeles 18201 Von Karman, Suite 1090

Irvine, CA 92612 Tel: 949-263-1888 Fax: 949-263-1338

### **New York**

150 Motor Parkway, Suite 202 Hauppauge, NY 11788 Tel: 631-273-5305 Fax: 631-273-5335

### San Jose

Microchip Technology Inc. 2107 North First Street, Suite 590 San Jose, CA 95131 Tel: 408-436-7950 Fax: 408-436-7955

6285 Northam Drive, Suite 108 Mississauga, Ontario L4V 1X5, Canada Tel: 905-673-0699 Fax: 905-673-6509

### ASIA/PACIFIC

### Australia

Microchip Technology Australia Pty Ltd Suite 22, 41 Rawson Street Epping 2121, NSW

Tel: 61-2-9868-6733 Fax: 61-2-9868-6755

### China - Beijing

Microchip Technology Consulting (Shanghai) Co., Ltd., Beijing Liaison Office Unit 915

Bei Hai Wan Tai Bldg. No. 6 Chaoyangmen Beidajie Beijing, 100027, No. China Tel: 86-10-85282100 Fax: 86-10-85282104

### China - Chengdu

Microchip Technology Consulting (Shanghai) Co., Ltd., Chengdu Liaison Office Rm. 2401, 24th Floor, Ming Xing Financial Tower No. 88 TIDU Street Chengdu 610016, China Tel: 86-28-6766200 Fax: 86-28-6766599

### China - Fuzhou

Microchip Technology Consulting (Shanghai) Co., Ltd., Fuzhou Liaison Office Unit 28F, World Trade Plaza No. 71 Wusi Road Fuzhou 350001, China Tel: 86-591-7503506 Fax: 86-591-7503521

### China - Shanghai

Microchip Technology Consulting (Shanghai)

Co., Ltd. Room 701, Bldg. B Far East International Plaza No. 317 Xian Xia Road Shanghai, 200051

Tel: 86-21-6275-5700 Fax: 86-21-6275-5060

### China - Shenzhen

Microchip Technology Consulting (Shanghai) Co., Ltd., Shenzhen Liaison Office Rm. 1315, 13/F, Shenzhen Kerry Centre, Renminnan Lu Shenzhen 518001, China Tel: 86-755-2350361 Fax: 86-755-2366086

### Hong Kong

Microchip Technology Hongkong Ltd. Unit 901-6, Tower 2, Metroplaza 223 Hing Fong Road Kwai Fong, N.T., Hong Kong Tel: 852-2401-1200 Fax: 852-2401-3431

### India

Microchip Technology Inc. India Liaison Office Divyasree Chambers 1 Floor, Wing A (A3/A4) No. 11, O'Shaugnessey Road Bangalore, 560 025, India Tel: 91-80-2290061 Fax: 91-80-2290062

### Japan

Microchip Technology Japan K.K. Benex S-1 6F 3-18-20, Shinyokohama Kohoku-Ku, Yokohama-shi Kanagawa, 222-0033, Japan Tel: 81-45-471- 6166 Fax: 81-45-471-6122

Korea

Microchip Technology Korea 168-1, Youngbo Bldg. 3 Floor Samsung-Dong, Kangnam-Ku Seoul, Korea 135-882

Tel: 82-2-554-7200 Fax: 82-2-558-5934

### Singapore

Microchip Technology Singapore Pte Ltd. 200 Middle Road #07-02 Prime Centre Singapore, 188980 Tel: 65-334-8870 Fax: 65-334-8850

### Taiwan

Microchip Technology Taiwan 11F-3, No. 207 Tung Hua North Road Taipei, 105, Taiwan Tel: 886-2-2717-7175 Fax: 886-2-2545-0139

### **EUROPE**

### Denmark

Microchip Technology Nordic ApS Regus Business Centre Lautrup hoj 1-3 Ballerup DK-2750 Denmark Tel: 45 4420 9895 Fax: 45 4420 9910

### France

Microchip Technology SARL Parc d'Activite du Moulin de Massy 43 Rue du Saule Trapu Batiment A - Ier Etage 91300 Massy, France Tel: 33-1-69-53-63-20 Fax: 33-1-69-30-90-79

### Germany

Microchip Technology GmbH Gustav-Heinemann Ring 125 D-81739 Munich, Germany Tel: 49-89-627-144 0 Fax: 49-89-627-144-44

### Italy

Microchip Technology SRL Centro Direzionale Colleoni Palazzo Taurus 1 V. Le Colleoni 1 20041 Agrate Brianza Milan, Italy

Tel: 39-039-65791-1 Fax: 39-039-6899883

### **United Kingdom**

Arizona Microchip Technology Ltd. 505 Eskdale Road Winnersh Triangle Wokingham Berkshire, England RG41 5TU Tel: 44 118 921 5869 Fax: 44-118 921-5820

01/18/02