Welcome to E-XFL.COM

### What is "Embedded - Microcontrollers"?

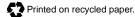

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

### Details

| Decails                    |                                                                        |

|----------------------------|------------------------------------------------------------------------|

| Product Status             | Active                                                                 |

| Core Processor             | PIC                                                                    |

| Core Size                  | 8-Bit                                                                  |

| Speed                      | 20MHz                                                                  |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                                      |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                  |

| Number of I/O              | 33                                                                     |

| Program Memory Size        | 14KB (8K x 14)                                                         |

| Program Memory Type        | FLASH                                                                  |

| EEPROM Size                | -                                                                      |

| RAM Size                   | 368 x 8                                                                |

| Voltage - Supply (Vcc/Vdd) | 4V ~ 5.5V                                                              |

| Data Converters            | A/D 8x8b                                                               |

| Oscillator Type            | External                                                               |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                     |

| Mounting Type              | Surface Mount                                                          |

| Package / Case             | 44-LCC (J-Lead)                                                        |

| Supplier Device Package    | 44-PLCC (16.59x16.59)                                                  |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16f77-e-l |

|                            |                                                                        |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

### Note the following details of the code protection feature on PICmicro<sup>®</sup> MCUs.

- The PICmicro family meets the specifications contained in the Microchip Data Sheet.

- Microchip believes that its family of PICmicro microcontrollers is one of the most secure products of its kind on the market today, when used in the intended manner and under normal conditions.

- There are dishonest and possibly illegal methods used to breach the code protection feature. All of these methods, to our knowledge, require using the PICmicro microcontroller in a manner outside the operating specifications contained in the data sheet. The person doing so may be engaged in theft of intellectual property.

- Microchip is willing to work with the customer who is concerned about the integrity of their code.

- Neither Microchip nor any other semiconductor manufacturer can guarantee the security of their code. Code protection does not mean that we are guaranteeing the product as "unbreakable".

- Code protection is constantly evolving. We at Microchip are committed to continuously improving the code protection features of our product.

If you have any further questions about this matter, please contact the local sales office nearest to you.

Information contained in this publication regarding device applications and the like is intended through suggestion only and may be superseded by updates. It is your responsibility to ensure that your application meets with your specifications. No representation or warranty is given and no liability is assumed by Microchip Technology Incorporated with respect to the accuracy or use of such information, or infringement of patents or other intellectual property rights arising from such use or otherwise. Use of Microchip's products as critical components in life support systems is not authorized except with express written approval by Microchip. No licenses are conveyed, implicitly or otherwise, under any intellectual property rights.

#### Trademarks

The Microchip name and logo, the Microchip logo, FilterLab, KEELOQ, MPLAB, PIC, PICmicro, PICMASTER, PICSTART, PRO MATE, SEEVAL and The Embedded Control Solutions Company are registered trademarks of Microchip Technology Incorporated in the U.S.A. and other countries.

dsPIC, ECONOMONITOR, FanSense, FlexROM, fuzzyLAB, In-Circuit Serial Programming, ICSP, ICEPIC, microID, microPort, Migratable Memory, MPASM, MPLIB, MPLINK, MPSIM, MXDEV, PICC, PICDEM, PICDEM.net, rfPIC, Select Mode and Total Endurance are trademarks of Microchip Technology Incorporated in the U.S.A.

Serialized Quick Term Programming (SQTP) is a service mark of Microchip Technology Incorporated in the U.S.A.

All other trademarks mentioned herein are property of their respective companies.

© 2002, Microchip Technology Incorporated, Printed in the U.S.A., All Rights Reserved.

Microchip received QS-9000 quality system certification for its worldwide headquarters, design and wafer fabrication facilities in Chandler and Tempe, Arizona in July 1999. The Company's quality system processes and procedures are QS-9000 compliant for its PICmicro® 8-bit MCUs, KEEL00® code hopping devices, Serial EEPROMs and microperipheral products. In addition, Microchip's quality system for the design and manufacture of development systems is ISO 9001 certified.

# PIC16F7X

| Address              | Name       | Bit 7                                                                                          | Bit 6         | Bit 5                      | Bit 4          | Bit 3   | Bit 2    | Bit 1         | Bit 0  | Value on:<br>POR,<br>BOR | Details<br>on page |

|----------------------|------------|------------------------------------------------------------------------------------------------|---------------|----------------------------|----------------|---------|----------|---------------|--------|--------------------------|--------------------|

| Bank 1               |            |                                                                                                |               |                            |                |         |          |               |        |                          |                    |

| 80h <sup>(4)</sup>   | INDF       | Addressing this location uses contents of FSR to address data memory (not a physical register) |               |                            |                |         |          |               |        |                          | 27, 96             |

| 81h                  | OPTION_REG | RBPU                                                                                           | INTEDG        | TOCS                       | T0SE           | PSA     | PS2      | PS1           | PS0    | 1111 1111                | 20, 44, 96         |

| 82h <sup>(4)</sup>   | PCL        | Program C                                                                                      | Counter's (PC | C) Least Sigr              | ificant Byte   |         |          |               |        | 0000 0000                | 26, 96             |

| 83h <sup>(4)</sup>   | STATUS     | IRP                                                                                            | RP1           | RP0                        | TO             | PD      | Z        | DC            | С      | 0001 1xxx                | 19, 96             |

| 84h <sup>(4)</sup>   | FSR        | Indirect da                                                                                    | ata memory a  | ddress point               | ier            |         |          |               |        | xxxx xxxx                | 27, 96             |

| 85h                  | TRISA      |                                                                                                | _             | PORTA Dat                  | a Direction Re | egister |          |               |        | 11 1111                  | 32, 96             |

| 86h                  | TRISB      | PORTB D                                                                                        | ata Direction | Register                   |                | •       |          |               |        | 1111 1111                | 34, 96             |

| 87h                  | TRISC      | PORTC D                                                                                        | ata Direction | Register                   |                |         |          |               |        | 1111 1111                | 35, 96             |

| 88h <sup>(5)</sup>   | TRISD      | PORTD D                                                                                        | ata Direction | Register                   |                |         |          |               |        | 1111 1111                | 36, 96             |

| 89h <sup>(5)</sup>   | TRISE      | IBF                                                                                            | OBF           | IBOV                       | PSPMODE        |         | PORTE Da | ata Direction | Bits   | 0000 -111                | 38, 96             |

| 8Ah <sup>(1,4)</sup> | PCLATH     | — — — Write Buffer for the upper 5 bits of the Program Counter                                 |               |                            |                |         |          |               |        | 0 0000                   | 21,96              |

| 8Bh <sup>(4)</sup>   | INTCON     | GIE                                                                                            | PEIE          | TMR0IE                     | INTE           | RBIE    | TMR0IF   | INTF          | RBIF   | 0000 000x                | 23, 96             |

| 8Ch                  | PIE1       | PSPIE <sup>(3)</sup>                                                                           | ADIE          | RCIE                       | TXIE           | SSPIE   | CCP1IE   | TMR2IE        | TMR1IE | 0000 0000                | 22,96              |

| 8Dh                  | PIE2       | _                                                                                              | _             | _                          | _              | _       |          | _             | CCP2IE | 0                        | 24, 97             |

| 8Eh                  | PCON       | _                                                                                              | _             | _                          | _              |         | _        | POR           | BOR    | dd                       | 25, 97             |

| 8Fh                  | —          | Unimplem                                                                                       | ented         |                            |                |         |          |               |        | _                        | _                  |

| 90h                  | —          | Unimplem                                                                                       | ented         |                            |                |         |          |               |        | _                        | _                  |

| 91h                  | —          | Unimplem                                                                                       | ented         |                            |                |         |          |               |        | —                        | —                  |

| 92h                  | PR2        | Timer2 Pe                                                                                      | riod Registe  | r                          |                |         |          |               |        | 1111 1111                | 52, 97             |

| 93h                  | SSPADD     | Synchrono                                                                                      | ous Serial Po | ort (I <sup>2</sup> C mode | ) Address Reg  | gister  |          |               |        | 0000 0000                | 68, 97             |

| 94h                  | SSPSTAT    | SMP                                                                                            | CKE           | D/A                        | Р              | S       | R/W      | UA            | BF     | 0000 0000                | 60, 97             |

| 95h                  | —          | Unimplem                                                                                       | ented         |                            |                |         |          |               |        | —                        | —                  |

| 96h                  | —          | Unimplem                                                                                       | ented         |                            |                |         |          |               |        | —                        | —                  |

| 97h                  | —          | Unimplem                                                                                       | ented         |                            |                |         | _        |               | -      | —                        | —                  |

| 98h                  | TXSTA      | CSRC                                                                                           | TX9           | TXEN                       | SYNC           |         | BRGH     | TRMT          | TX9D   | 0000 -010                | 69, 97             |

| 99h                  | SPBRG      | Baud Rate Generator Register                                                                   |               |                            |                |         |          |               |        | 0000 0000                | 71, 97             |

| 9Ah                  | —          | Unimplem                                                                                       | ented         |                            |                |         |          |               |        | —                        |                    |

| 9Bh                  | —          | Unimplem                                                                                       | ented         |                            |                |         |          |               |        | -                        |                    |

| 9Ch                  | —          | Unimplem                                                                                       | ented         |                            |                |         |          |               |        | _                        |                    |

| 9Dh                  | —          | Unimplem                                                                                       | ented         |                            |                |         |          |               |        | _                        |                    |

| 9Eh                  | —          | Unimplem                                                                                       | ented         |                            |                |         |          |               |        | -                        |                    |

| 9Fh                  | ADCON1     | _                                                                                              | _             | _                          | _              | _       | PCFG2    | PCFG1         | PCFG0  | 000                      | 84, 97             |

| TABLE 2-1: SPECIAL FUNCTION REGISTER SUMMARY (CONTINUED) |

|----------------------------------------------------------|

|----------------------------------------------------------|

$\label{eq:legend: Legend: Legend: u = unchanged, q = value depends on condition, - = unimplemented, read as '0', r = reserved.$ Shaded locations are unimplemented, read as '0'.

Note 1: The upper byte of the program counter is not directly accessible. PCLATH is a holding register for the PC<12:8>, whose contents are transferred to the upper byte of the program counter during branches (CALL or GOTO).

2: Other (non power-up) RESETS include external RESET through MCLR and Watchdog Timer Reset. 3: Bits PSPIE and PSPIF are reserved on the 28-pin devices; always maintain these bits clear.

4: These registers can be addressed from any bank.

5: PORTD, PORTE, TRISD, and TRISE are not physically implemented on the 28-pin devices, read as '0'.

6: This bit always reads as a '1'.

| <b>TABLE 2-1:</b> | SPECIAL FUNCTION REGISTER SUMMARY | (CONTINUED) |

|-------------------|-----------------------------------|-------------|

|-------------------|-----------------------------------|-------------|

| Address               | Name       | Bit 7                                                                                          | Bit 6                       | Bit 5         | Bit 4          | Bit 3          | Bit 2         | Bit 1         | Bit 0        | Value on:<br>POR,<br>BOR | Details<br>on page |

|-----------------------|------------|------------------------------------------------------------------------------------------------|-----------------------------|---------------|----------------|----------------|---------------|---------------|--------------|--------------------------|--------------------|

| Bank 2                |            |                                                                                                |                             |               |                |                |               |               |              |                          |                    |

| 100h <sup>(4)</sup>   | INDF       | Addressing this location uses contents of FSR to address data memory (not a physical register) |                             |               |                |                |               |               |              | 0000 0000                | 27, 96             |

| 101h                  | TMR0       | Timer0 Mo                                                                                      | Timer0 Module Register      |               |                |                |               |               |              |                          | 45, 96             |

| 102h <sup>(4)</sup>   | PCL        | Program C                                                                                      | Counter (PC)                | Least Signif  | icant Byte     |                |               |               |              | 0000 0000                | 26, 96             |

| 103h <sup>(4)</sup>   | STATUS     | IRP                                                                                            | RP1                         | RP0           | ТО             | PD             | Z             | DC            | С            | 0001 1xxx                | 19, 96             |

| 104h <sup>(4)</sup>   | FSR        | Indirect Da                                                                                    | ata Memory /                | Address Poir  | nter           |                |               |               |              | xxxx xxxx                | 27, 96             |

| 105h                  | —          | Unimplem                                                                                       | ented                       |               |                |                |               |               |              | _                        | —                  |

| 106h                  | PORTB      | PORTB D                                                                                        | ata Latch wh                | en written: F | ORTB pins w    | hen read       |               |               |              | xxxx xxxx                | 34, 96             |

| 107h                  | _          | Unimplem                                                                                       | ented                       |               |                |                |               |               |              | —                        | —                  |

| 108h                  | —          | Unimplem                                                                                       | ented                       |               |                |                |               |               |              | —                        | —                  |

| 109h                  | —          | Unimplem                                                                                       | ented                       |               |                |                |               |               |              | _                        | —                  |

| 10Ah <sup>(1,4)</sup> | PCLATH     | —                                                                                              | _                           | _             | Write Buffer   | for the upper  | 5 bits of the | Program C     | ounter       | 0 0000                   | 21, 96             |

| 10Bh <sup>(4)</sup>   | INTCON     | GIE                                                                                            | PEIE                        | TMR0IE        | INTE           | RBIE           | TMR0IF        | INTF          | RBIF         | 0000 000x                | 23, 96             |

| 10Ch                  | PMDATA     | Data Register Low Byte                                                                         |                             |               |                |                |               |               |              | XXXX XXXX                | 29, 97             |

| 10Dh                  | PMADR      | Address Register Low Byte                                                                      |                             |               |                |                |               |               | xxxx xxxx    | 29, 97                   |                    |

| 10Eh                  | PMDATH     | —                                                                                              | — — Data Register High Byte |               |                |                |               |               |              | xxxx xxxx                | 29, 97             |

| 10Fh                  | PMADRH     |                                                                                                | _                           | _             | Address Reg    | gister High By | /te           |               |              | XXXX XXXX                | 29, 97             |

| Bank 3                |            |                                                                                                |                             |               |                |                |               |               |              |                          |                    |

| 180h <sup>(4)</sup>   | INDF       | Addressin                                                                                      | g this locatio              | n uses conte  | ents of FSR to | address data   | a memory (r   | not a physica | al register) | 0000 0000                | 27, 96             |

| 181h                  | OPTION_REG | RBPU                                                                                           | INTEDG                      | TOCS          | TOSE           | PSA            | PS2           | PS1           | PS0          | 1111 1111                | 20, 44, 96         |

| 182h <sup>(4)</sup>   | PCL        | Program C                                                                                      | Counter (PC)                | Least Signif  | icant Byte     |                |               |               |              | 0000 0000                | 26, 96             |

| 183h <sup>(4)</sup>   | STATUS     | IRP                                                                                            | RP1                         | RP0           | TO             | PD             | Z             | DC            | С            | 0001 1xxx                | 19, 96             |

| 184h <sup>(4)</sup>   | FSR        | Indirect Da                                                                                    | ata Memory /                | Address Poir  | nter           |                |               |               |              | xxxx xxxx                | 27, 96             |

| 185h                  | —          | Unimplem                                                                                       | ented                       |               |                |                |               |               |              | _                        | _                  |

| 186h                  | TRISB      | PORTB D                                                                                        | ata Direction               | Register      |                |                |               |               |              | 1111 1111                | 34, 96             |

| 187h                  | —          | Unimplem                                                                                       | ented                       |               |                |                |               |               |              | _                        | _                  |

| 188h                  | —          | Unimplemented                                                                                  |                             |               |                |                |               |               |              | _                        | _                  |

| 189h                  | —          | Unimplemented                                                                                  |                             |               |                |                |               |               | _            | _                        |                    |

| 18Ah <sup>(1,4)</sup> | PCLATH     | _                                                                                              |                             | _             | Write Buffer   | for the upper  | 5 bits of the | Program C     | ounter       | 0 0000                   | 21, 96             |

| 18Bh <sup>(4)</sup>   | INTCON     | GIE                                                                                            | PEIE                        | TMR0IE        | INTE           | RBIE           | TMR0IF        | INTF          | RBIF         | 0000 000x                | 23, 96             |

| 18Ch                  | PMCON1     | (6)                                                                                            | _                           | —             | —              | _              | _             | —             | RD           | 10                       | 29, 97             |

| 18Dh                  | —          | Unimplem                                                                                       | ented                       |               |                |                |               |               |              | _                        |                    |

| 18Eh                  | —          | Reserved                                                                                       | maintain clea               | ar            |                |                |               |               |              | 0000 0000                |                    |

| 18Fh                  | _          | Reserved                                                                                       | maintain clea               | ar            |                |                |               |               |              | 0000 0000                |                    |

Legend: x = unknown, u = unchanged, q = value depends on condition, - = unimplemented, read as '0', r = reserved. Shaded locations are unimplemented, read as '0'.

**Note** 1: The upper byte of the program counter is not directly accessible. PCLATH is a holding register for the PC<12:8>, whose contents are transferred to the upper byte of the program counter during branches (CALL or GOTO).

2: Other (non power-up) RESETS include external RESET through MCLR and Watchdog Timer Reset.

3: Bits PSPIE and PSPIF are reserved on the 28-pin devices; always maintain these bits clear.

4: These registers can be addressed from any bank.

5: PORTD, PORTE, TRISD, and TRISE are not physically implemented on the 28-pin devices, read as '0'.

6: This bit always reads as a '1'.

x = Bit is unknown

#### **PCON Register** 2.2.2.8

The Power Control (PCON) register contains flag bits to allow differentiation between a Power-on Reset (POR), a Brown-out Reset (BOR), a Watchdog Reset (WDT) and an external MCLR Reset.

BOR is unknown on POR. It must be set by Note: the user and checked on subsequent RESETS to see if BOR is clear, indicating a brown-out has occurred. The BOR status bit is not predictable if the brown-out circuit is disabled (by clearing the BODEN bit in the configuration word).

#### **REGISTER 2-8:** PCON REGISTER (ADDRESS 8Eh)

- n = Value at POR reset

|         | U-0        | U-0         | U-0           | U-0            | U-0          | U-0         | R/W-0         | R/W-1   |

|---------|------------|-------------|---------------|----------------|--------------|-------------|---------------|---------|

|         | _          | _           | _             |                | —            |             | POR           | BOR     |

|         | bit 7      |             |               |                |              |             |               | bit 0   |

|         |            |             |               |                |              |             |               |         |

| bit 7-2 | Unimplem   | ented: Rea  | d as '0'      |                |              |             |               |         |

| bit 1   | POR: Pow   | er-on Reset | Status bit    |                |              |             |               |         |

|         | 1 = No Pov | wer-on Rese | et occurred   |                |              |             |               |         |

|         | 0 = A Pow  | er-on Reset | occurred (m   | ust be set in  | software aft | er a Power- | on Reset or   | ccurs)  |

| bit 0   | BOR: Brov  | vn-out Rese | t Status bit  |                |              |             |               |         |

|         | 1 = No Bro | wn-out Res  | et occurred   |                |              |             |               |         |

|         | 0 = A Brow | n-out Rese  | t occurred (m | lust be set in | software af  | ter a Brown | -out Reset of | occurs) |

|         |            |             |               |                |              |             |               |         |

|         | Legend:    |             |               |                |              |             |               |         |

|         | R = Reada  | ble bit     | W = W         | ritable bit    | U = Unim     | plemented l | bit, read as  | '0'     |

'0' = Bit is cleared

'1' = Bit is set

| Name    | Bit# | Buffer                | Function                                                                                                               |

|---------|------|-----------------------|------------------------------------------------------------------------------------------------------------------------|

| RB0/INT | bit0 | TTL/ST <sup>(1)</sup> | Input/output pin or external interrupt input. Internal software programmable weak pull-up.                             |

| RB1     | bit1 | TTL                   | Input/output pin. Internal software programmable weak pull-up.                                                         |

| RB2     | bit2 | TTL                   | Input/output pin. Internal software programmable weak pull-up.                                                         |

| RB3     | bit3 | TTL                   | Input/output pin. Internal software programmable weak pull-up.                                                         |

| RB4     | bit4 | TTL                   | Input/output pin (with interrupt-on-change). Internal software programmable weak pull-up.                              |

| RB5     | bit5 | TTL                   | Input/output pin (with interrupt-on-change). Internal software programmable weak pull-up.                              |

| RB6     | bit6 | TTL/ST <sup>(2)</sup> | Input/output pin (with interrupt-on-change).<br>Internal software programmable weak pull-up. Serial programming clock. |

| RB7     | bit7 | TTL/ST <sup>(2)</sup> | Input/output pin (with interrupt-on-change).<br>Internal software programmable weak pull-up. Serial programming data.  |

### TABLE 4-3: PORTB FUNCTIONS

Legend: TTL = TTL input, ST = Schmitt Trigger input

Note 1: This buffer is a Schmitt Trigger input when configured as the external interrupt.

2: This buffer is a Schmitt Trigger input when used in Serial Programming mode.

## TABLE 4-4: SUMMARY OF REGISTERS ASSOCIATED WITH PORTB

| Address   | Name       | Bit 7   | Bit 6                         | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 | Value on:<br>POR,<br>BOR | Value on<br>all other<br>RESETS |

|-----------|------------|---------|-------------------------------|-------|-------|-------|-------|-------|-------|--------------------------|---------------------------------|

| 06h, 106h | PORTB      | RB7     | RB6                           | RB5   | RB4   | RB3   | RB2   | RB1   | RB0   | xxxx xxxx                | uuuu uuuu                       |

| 86h, 186h | TRISB      | PORTB I | PORTB Data Direction Register |       |       |       |       |       |       |                          | 1111 1111                       |

| 81h, 181h | OPTION_REG | RBPU    | INTEDG                        | TOCS  | T0SE  | PSA   | PS2   | PS1   | PS0   | 1111 1111                | 1111 1111                       |

Legend: x = unknown, u = unchanged. Shaded cells are not used by PORTB.

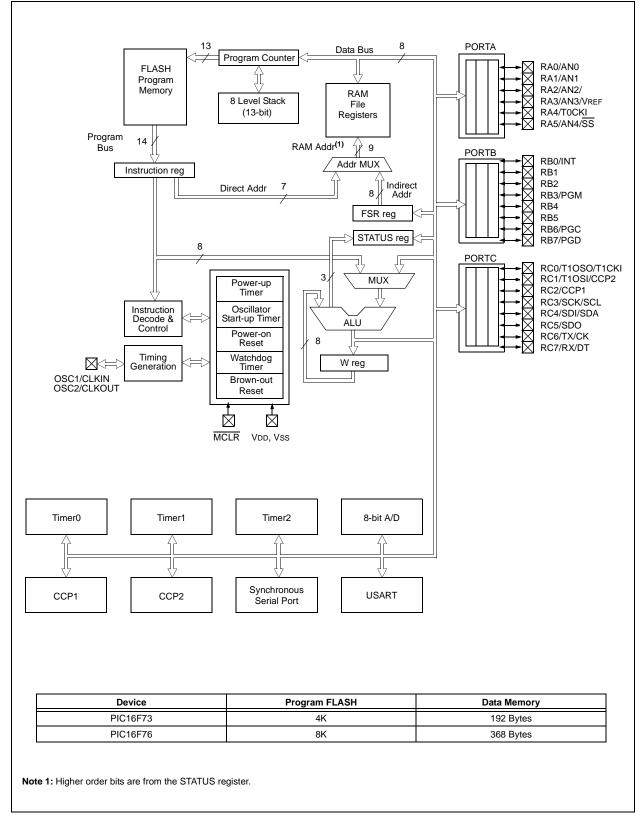

## 5.0 TIMER0 MODULE

The Timer0 module timer/counter has the following features:

- 8-bit timer/counter

- Readable and writable

- 8-bit software programmable prescaler

- · Internal or external clock select

- Interrupt on overflow from FFh to 00h

- Edge select for external clock

Additional information on the Timer0 module is available in the PICmicro<sup>™</sup> Mid-Range MCU Family Reference Manual (DS33023).

Figure 5-1 is a block diagram of the Timer0 module and the prescaler shared with the WDT.

Timer0 operation is controlled through the OPTION\_REG register (Register 5-1 on the following page). Timer mode is selected by clearing bit TOCS (OPTION\_REG<5>). In Timer mode, the Timer0 module will increment every instruction cycle (without prescaler). If the TMR0 register is written, the increment is inhibited for the following two instruction cycles. The user can work around this by writing an adjusted value to the TMR0 register.

Counter mode is selected by setting bit T0CS (OPTION\_REG<5>). In Counter mode, Timer0 will increment, either on every rising or falling edge of pin RA4/T0CKI. The incrementing edge is determined by the Timer0 Source Edge Select bit T0SE (OPTION\_REG<4>). Clearing bit T0SE selects the rising edge. Restrictions on the external clock input are discussed in detail in Section 5.2.

The prescaler is mutually exclusively shared between the Timer0 module and the Watchdog Timer. The prescaler is not readable or writable. Section 5.3 details the operation of the prescaler.

## 5.1 Timer0 Interrupt

The TMR0 interrupt is generated when the TMR0 register overflows from FFh to 00h. This overflow sets bit TMR0IF (INTCON<2>). The interrupt can be masked by clearing bit TMR0IE (INTCON<5>). Bit TMR0IF must be cleared in software by the Timer0 module Interrupt Service Routine, before re-enabling this interrupt. The TMR0 interrupt cannot awaken the processor from SLEEP, since the timer is shut-off during SLEEP.

# PIC16F7X

## REGISTER 8-1: CCP1CON REGISTER/CCP2CON REGISTER (ADDRESS: 17h/1Dh)

| bit 7-6                                                                                          | U-0<br>—                                                                                                 | U-0            | R/W-0<br>CCPxX               | R/W-0    | R/W-0        | R/W-0       | R/W-0       | R/W-0   |  |  |  |  |

|--------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------|----------------|------------------------------|----------|--------------|-------------|-------------|---------|--|--|--|--|

| bit 7-6                                                                                          | —<br>bit 7                                                                                               | _              | CCDvV                        |          |              |             |             |         |  |  |  |  |

| Dit 7-6                                                                                          | bit 7                                                                                                    |                | COFXA                        | CCPxY    | CCPxM3       | CCPxM2      | CCPxM1      | CCPxM0  |  |  |  |  |

| bit 5-4 ()<br>()<br>()<br>()<br>()<br>()<br>()<br>()<br>()<br>()<br>()<br>()<br>()<br>(          |                                                                                                          |                |                              |          |              |             |             | bit 0   |  |  |  |  |

| ()<br>()<br>()<br>()<br>()<br>()<br>()<br>()<br>()<br>()<br>()<br>()<br>()<br>(                  | Unimplem                                                                                                 | ented: Rea     | ad as '0'                    |          |              |             |             |         |  |  |  |  |

| 1<br>1<br>1<br>2<br>2<br>2<br>2<br>2<br>1<br>2<br>2<br>2<br>1<br>1<br>1<br>1<br>1<br>1<br>1<br>1 | CCPxX:CCPxY: PWM Least Significant bits                                                                  |                |                              |          |              |             |             |         |  |  |  |  |

| bit 3-0                                                                                          | <u>Capture mo</u><br>Unused                                                                              | ode:           |                              |          |              |             |             |         |  |  |  |  |

| -<br>bit 3-0                                                                                     | <u>Compare n</u><br>Unused                                                                               | <u>node:</u>   |                              |          |              |             |             |         |  |  |  |  |

| bit 3-0                                                                                          | PWM mode                                                                                                 | <del>)</del> : |                              |          |              |             |             |         |  |  |  |  |

|                                                                                                  | These bits                                                                                               | are the two    | LSbs of the                  | PWM duty | cycle. The e | ight MSbs a | re found in | CCPRxL. |  |  |  |  |

| ,                                                                                                | CCPxM3:CCPxM0: CCPx Mode Select bits                                                                     |                |                              |          |              |             |             |         |  |  |  |  |

|                                                                                                  | 0000 = Capture/Compare/PWM disabled (resets CCPx module)                                                 |                |                              |          |              |             |             |         |  |  |  |  |

|                                                                                                  |                                                                                                          |                | , every fallin               |          |              |             |             |         |  |  |  |  |

| (                                                                                                | 0101 <b>= Ca</b>                                                                                         | pture mode     | , every rising               | g edge   |              |             |             |         |  |  |  |  |

| (                                                                                                | 0110 = Capture mode, every 4th rising edge                                                               |                |                              |          |              |             |             |         |  |  |  |  |

|                                                                                                  | 0111 = Capture mode, every 16th rising edge                                                              |                |                              |          |              |             |             |         |  |  |  |  |

|                                                                                                  | 1000 = Compare mode, set output on match (CCPxIF bit is set)                                             |                |                              |          |              |             |             |         |  |  |  |  |

|                                                                                                  | 1001 = Compare mode, clear output on match (CCPxIF bit is set)                                           |                |                              |          |              |             |             |         |  |  |  |  |

| -                                                                                                | 1010 = Compare mode, generate software interrupt on match (CCPxIF bit is set, CCPx pin is<br>unaffected) |                |                              |          |              |             |             |         |  |  |  |  |

| :                                                                                                | CC                                                                                                       |                | e, trigger sp<br>ïmer1; CCP2 |          | •            |             | •           |         |  |  |  |  |

| :                                                                                                | 11xx = PW                                                                                                | /M mode        |                              |          |              |             |             |         |  |  |  |  |

|                                                                                                  |                                                                                                          |                |                              |          |              |             |             |         |  |  |  |  |

|                                                                                                  | Legend:                                                                                                  |                |                              |          |              |             |             |         |  |  |  |  |

| Legend:                  |                  |                      |                    |

|--------------------------|------------------|----------------------|--------------------|

| R = Readable bit         | W = Writable bit | U = Unimplemented    | l bit, read as '0' |

| - n = Value at POR reset | '1' = Bit is set | '0' = Bit is cleared | x = Bit is unknown |

## 8.5 PWM Mode (PWM)

In Pulse Width Modulation mode, the CCPx pin produces up to a 10-bit resolution PWM output. Since the CCP1 pin is multiplexed with the PORTC data latch, the TRISC<2> bit must be cleared to make the CCP1 pin an output.

| Note: | Clearing the CCP1CON register will force  |

|-------|-------------------------------------------|

|       | the CCP1 PWM output latch to the default  |

|       | low level. This is not the PORTC I/O data |

|       | latch.                                    |

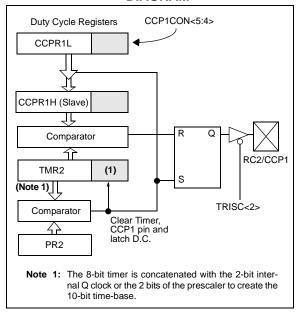

Figure 8-3 shows a simplified block diagram of the CCP module in PWM mode.

For a step-by-step procedure on how to set up the CCP module for PWM operation, see Section 8.5.3.

### FIGURE 8-3: SIMPLIFIED PWM BLOCK DIAGRAM

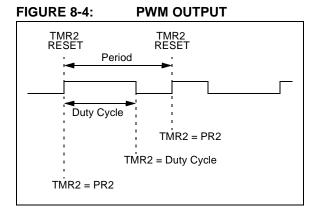

A PWM output (Figure 8-4) has a time-base (period) and a time that the output stays high (duty cycle). The frequency of the PWM is the inverse of the period (1/period).

### 8.5.1 PWM PERIOD

The PWM period is specified by writing to the PR2 register. The PWM period can be calculated using the following formula:

$PWM period = [(PR2) + 1] \cdot 4 \cdot Tosc \cdot (TMR2 prescale value)$

PWM frequency is defined as 1 / [PWM period].

When TMR2 is equal to PR2, the following three events occur on the next increment cycle:

- TMR2 is cleared

- The CCP1 pin is set (exception: if PWM duty cycle = 0%, the CCP1 pin will not be set)

- The PWM duty cycle is latched from CCPR1L into CCPR1H

Note: The Timer2 postscaler (see Section 8.3) is not used in the determination of the PWM frequency. The postscaler could be used to have a servo update rate at a different frequency than the PWM output.

### 8.5.2 PWM DUTY CYCLE

The PWM duty cycle is specified by writing to the CCPR1L register and to the CCP1CON<5:4> bits. Up to 10-bit resolution is available. The CCPR1L contains the eight MSbs and the CCP1CON<5:4> contains the two LSbs. This 10-bit value is represented by CCPR1L:CCP1CON<5:4>. The following equation is used to calculate the PWM duty cycle in time:

```

PWM duty cycle = (CCPR1L:CCP1CON<5:4>)•

TOSC • (TMR2 prescale value)

```

CCPR1L and CCP1CON<5:4> can be written to at any time, but the duty cycle value is not latched into CCPR1H until after a match between PR2 and TMR2 occurs (i.e., the period is complete). In PWM mode, CCPR1H is a read only register.

The CCPR1H register and a 2-bit internal latch are used to double buffer the PWM duty cycle. This double buffering is essential for glitchless PWM operation.

When the CCPR1H and 2-bit latch match TMR2, concatenated with an internal 2-bit Q clock or 2 bits of the TMR2 prescaler, the CCP1 pin is cleared.

The maximum PWM resolution (bits) for a given PWM frequency is given by the formula:

Resolution =

$$\frac{\log(\frac{FOSC}{FPWM})}{\log(2)}$$

bits

Note: If the PWM duty cycle value is longer than the PWM period, the CCP1 pin will not be cleared.

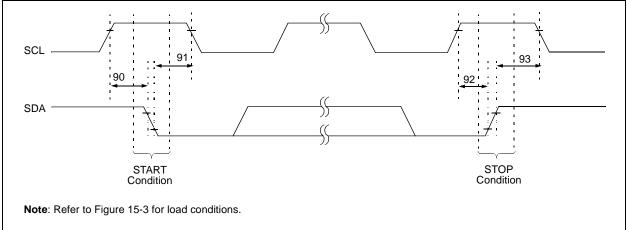

| REGISTER 9-1: SSPSTAT: SYNC SERIAL PORT STATUS REGISTER (ADDRESS 94                                                                                   | SSPSTAT: SYNC SERIAL PORT STATUS REGISTER (ADDRESS 94h) |  |  |  |  |  |  |  |

|-------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------|--|--|--|--|--|--|--|

| R/W-0 R/W-0 R-0 R-0 R-0 R-0 R-0 R-0 R-0 R-0 R-0 R                                                                                                     | -0 R-0                                                  |  |  |  |  |  |  |  |

| SMP CKE D/A P S R/W U                                                                                                                                 | A BF                                                    |  |  |  |  |  |  |  |

| bit 7                                                                                                                                                 | bit C                                                   |  |  |  |  |  |  |  |

| bit 7 SMP: SPI Data Input Sample Phase bit                                                                                                            |                                                         |  |  |  |  |  |  |  |

| SPI Master mode:                                                                                                                                      |                                                         |  |  |  |  |  |  |  |

| 1 = Input data sampled at end of data output time                                                                                                     |                                                         |  |  |  |  |  |  |  |

| 0 = Input data sampled at middle of data output time (Microwire®)                                                                                     |                                                         |  |  |  |  |  |  |  |

| <u>SPI Slave mode:</u><br>SMP must be cleared when SPI is used in Slave mode                                                                          |                                                         |  |  |  |  |  |  |  |

| I <sup>2</sup> C mode:                                                                                                                                |                                                         |  |  |  |  |  |  |  |

| This bit must be maintained clear                                                                                                                     |                                                         |  |  |  |  |  |  |  |

| bit 6 <b>CKE</b> : SPI Clock Edge Select bit (Figure 9-2, Figure 9-3, and Figure 9-4)                                                                 |                                                         |  |  |  |  |  |  |  |

| <u>SPI mode, CKP = 0:</u>                                                                                                                             |                                                         |  |  |  |  |  |  |  |

| <ul> <li>1 = Data transmitted on rising edge of SCK (Microwire<sup>®</sup> alternate)</li> <li>0 = Data transmitted on falling edge of SCK</li> </ul> |                                                         |  |  |  |  |  |  |  |

| SPI mode, $CKP = 1$ :                                                                                                                                 |                                                         |  |  |  |  |  |  |  |

| 1 = Data transmitted on falling edge of SCK (Microwire <sup>®</sup> default)                                                                          |                                                         |  |  |  |  |  |  |  |

| 0 = Data transmitted on rising edge of SCK                                                                                                            |                                                         |  |  |  |  |  |  |  |

| I <sup>2</sup> C mode:<br>This bit must be maintained clear                                                                                           |                                                         |  |  |  |  |  |  |  |

| bit 5 <b>D/A</b> : Data/Address bit (I <sup>2</sup> C mode only)                                                                                      |                                                         |  |  |  |  |  |  |  |

| 1 = Indicates that the last byte received or transmitted was data                                                                                     |                                                         |  |  |  |  |  |  |  |

| 0 = Indicates that the last byte received or transmitted was address                                                                                  |                                                         |  |  |  |  |  |  |  |

| bit 4 <b>P</b> : STOP bit (I <sup>2</sup> C mode only)                                                                                                |                                                         |  |  |  |  |  |  |  |

| This bit is cleared when the SSP module is disabled, or when the START bit is<br>SSPEN is cleared.                                                    | s detected last.                                        |  |  |  |  |  |  |  |

| 1 = Indicates that a STOP bit has been detected last (this bit is '0' on RESET)                                                                       |                                                         |  |  |  |  |  |  |  |

| 0 = STOP bit was not detected last                                                                                                                    |                                                         |  |  |  |  |  |  |  |

| bit 3 <b>S</b> : START bit (I <sup>2</sup> C mode only)                                                                                               |                                                         |  |  |  |  |  |  |  |

| This bit is cleared when the SSP module is disabled, or when the STOP bit is SSPEN is cleared.                                                        | detected last.                                          |  |  |  |  |  |  |  |

| 1 = Indicates that a START bit has been detected last (this bit is '0' on RESET                                                                       | )                                                       |  |  |  |  |  |  |  |

| 0 = START bit was not detected last                                                                                                                   |                                                         |  |  |  |  |  |  |  |

| bit 2 <b>R/W</b> : Read/Write bit Information (I <sup>2</sup> C mode only)                                                                            |                                                         |  |  |  |  |  |  |  |

| This bit holds the R/W bit information following the last address match. This bit i<br>the address match to the next START bit, STOP bit, or ACK bit. | s only valid from                                       |  |  |  |  |  |  |  |

| 1 = Read                                                                                                                                              |                                                         |  |  |  |  |  |  |  |

| 0 = Write                                                                                                                                             |                                                         |  |  |  |  |  |  |  |

| bit 1 <b>UA</b> : Update Address bit (10-bit I <sup>2</sup> C mode only)                                                                              |                                                         |  |  |  |  |  |  |  |

| 1 = Indicates that the user needs to update the address in the SSPADD regist                                                                          | er                                                      |  |  |  |  |  |  |  |

| <ul> <li>0 = Address does not need to be updated</li> <li>bit 0</li> <li><b>BF</b>: Buffer Full Status bit</li> </ul>                                 |                                                         |  |  |  |  |  |  |  |

| Receive (SPI and I <sup>2</sup> C modes):                                                                                                             |                                                         |  |  |  |  |  |  |  |

| 1 = Receive complete, SSPBUF is full                                                                                                                  |                                                         |  |  |  |  |  |  |  |

| 0 = Receive not complete, SSPBUF is empty                                                                                                             |                                                         |  |  |  |  |  |  |  |

| Transmit (I <sup>2</sup> C mode only):                                                                                                                |                                                         |  |  |  |  |  |  |  |

| 1 = Transmit in progress, SSPBUF is full                                                                                                              |                                                         |  |  |  |  |  |  |  |

| 0 = Transmit complete, SSPBUF is empty                                                                                                                |                                                         |  |  |  |  |  |  |  |

| Legend:                                                                                                                                               |                                                         |  |  |  |  |  |  |  |

| R = Readable bit W = Writable bit U = Unimplemented bit, rea                                                                                          | id as '0'                                               |  |  |  |  |  |  |  |

| - n = Value at POR reset $'1'$ = Bit is set $'0'$ = Bit is cleared x = B                                                                              | Bit is unknown                                          |  |  |  |  |  |  |  |

\_

| Address               | Name    | Bit 7                | Bit 6                                                    | Bit 5                         | Bit 4 | Bit 3 | Bit 2  | Bit 1   | Bit 0   | Value on:<br>POR,<br>BOR | Value on<br>all other<br>RESETS |

|-----------------------|---------|----------------------|----------------------------------------------------------|-------------------------------|-------|-------|--------|---------|---------|--------------------------|---------------------------------|

| 0Bh,8Bh.<br>10Bh,18Bh | INTCON  | GIE                  | PEIE                                                     | TMR0IE                        | INTE  | RBIE  | TMR0IF | INTF    | RBIF    | x000 0000                | 0000 000u                       |

| 0Ch                   | PIR1    | PSPIF <sup>(1)</sup> | ADIF                                                     | RCIF                          | TXIF  | SSPIF | CCP1IF | TMR2IF  | TMR1IF  | 0000 0000                | 0000 0000                       |

| 8Ch                   | PIE1    | PSPIE <sup>(1)</sup> | ADIE                                                     | RCIE                          | TXIE  | SSPIE | CCP1IE | TMR2IE  | TMR1IE  | 0000 0000                | 0000 0000                       |

| 87h                   | TRISC   | PORTC Da             | PORTC Data Direction Register                            |                               |       |       |        |         |         | 1111 1111                | 1111 1111                       |

| 13h                   | SSPBUF  | Synchronou           | Synchronous Serial Port Receive Buffer/Transmit Register |                               |       |       |        |         |         | XXXX XXXX                | uuuu uuuu                       |

| 14h                   | SSPCON  | WCOL                 | SSPOV                                                    | SSPEN                         | СКР   | SSPM3 | SSPM2  | SSPM1   | SSPM0   | 0000 0000                | 0000 0000                       |

| 85h                   | TRISA   | —                    | _                                                        | PORTA Data Direction Register |       |       |        | 11 1111 | 11 1111 |                          |                                 |

| 94h                   | SSPSTAT | SMP                  | CKE                                                      | D/A                           | Р     | S     | R/W    | UA      | BF      | 0000 0000                | 0000 0000                       |

### TABLE 9-1:REGISTERS ASSOCIATED WITH SPI OPERATION

Legend: x = unknown, u = unchanged, - = unimplemented, read as '0'. Shaded cells are not used by the SSP in SPI mode.

**Note 1:** Bits PSPIE and PSPIF are reserved on the PIC16F73/76; always maintain these bits clear.

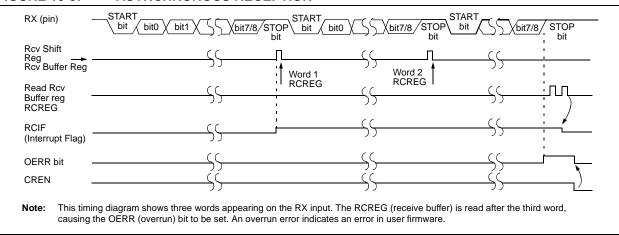

### FIGURE 10-5: ASYNCHRONOUS RECEPTION

Steps to follow when setting up an Asynchronous Reception:

- 1. Initialize the SPBRG register for the appropriate baud rate. If a high speed baud rate is desired, set bit BRGH (Section 10.1).

- 2. Enable the asynchronous serial port by clearing bit SYNC and setting bit SPEN.

- 3. If interrupts are desired, then set enable bit RCIE.

- 4. If 9-bit reception is desired, then set bit RX9.

- 5. Enable the reception by setting bit CREN.

- 6. Flag bit RCIF will be set when reception is complete and an interrupt will be generated if enable bit RCIE is set.

- 7. Read the RCSTA register to get the ninth bit (if enabled) and determine if any error occurred during reception.

- 8. Read the 8-bit received data by reading the RCREG register.

- 9. If any error occurred, clear the error by clearing enable bit CREN.

- 10. If using interrupts, ensure that GIE and PEIE in the INTCON register are set.

| Address                | Name   | Bit 7                        | Bit 6     | Bit 5  | Bit 4 | Bit 3 | Bit 2  | Bit 1  | Bit 0  | Value on:<br>POR,<br>BOR | Value on<br>all other<br>RESETS |

|------------------------|--------|------------------------------|-----------|--------|-------|-------|--------|--------|--------|--------------------------|---------------------------------|

| 0Bh, 8Bh,<br>10Bh,18Bh | INTCON | GIE                          | PEIE      | TMR0IE | INTE  | RBIE  | TMR0IF | INTF   | RBIF   | 0000 000x                | 0000 000u                       |

| 0Ch                    | PIR1   | PSPIF <sup>(1)</sup>         | ADIF      | RCIF   | TXIF  | SSPIF | CCP1IF | TMR2IF | TMR1IF | 0000 0000                | 0000 0000                       |

| 18h                    | RCSTA  | SPEN                         | RX9       | SREN   | CREN  |       | FERR   | OERR   | RX9D   | 0000 -00x                | 0000 -00x                       |

| 1Ah                    | RCREG  | USART R                      | eceive Re | gister |       |       |        |        |        | 0000 0000                | 0000 0000                       |

| 8Ch                    | PIE1   | PSPIE <sup>(1)</sup>         | ADIE      | RCIE   | TXIE  | SSPIE | CCP1IE | TMR2IE | TMR1IE | 0000 0000                | 0000 0000                       |

| 98h                    | TXSTA  | CSRC                         | TX9       | TXEN   | SYNC  |       | BRGH   | TRMT   | TX9D   | 0000 -010                | 0000 -010                       |

| 99h                    | SPBRG  | Baud Rate Generator Register |           |        |       |       |        |        |        | 0000 0000                | 0000 0000                       |

### TABLE 10-6: REGISTERS ASSOCIATED WITH ASYNCHRONOUS RECEPTION

Legend: x = unknown, - = unimplemented locations read as '0'. Shaded cells are not used for asynchronous reception. Note 1: Bits PSPIE and PSPIF are reserved on the PIC16F73/76 devices; always maintain these bits clear.

# PIC16F7X

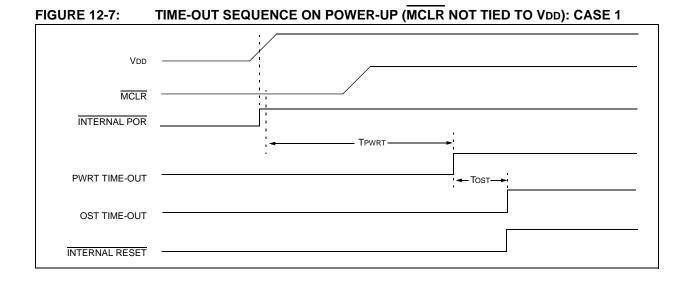

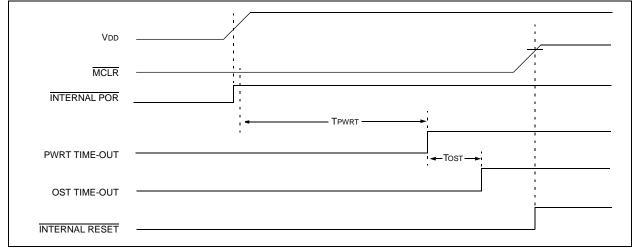

## FIGURE 12-8: TIME-OUT SEQUENCE ON POWER-UP (MCLR NOT TIED TO VDD): CASE 2

## FIGURE 12-9: SLOW RISE TIME (MCLR TIED TO VDD THROUGH RC NETWORK)

### 12.11.1 INT INTERRUPT

External interrupt on the RB0/INT pin is edge triggered, either rising, if bit INTEDG (OPTION\_REG<6>) is set, or falling, if the INTEDG bit is clear. When a valid edge appears on the RB0/INT pin, flag bit INTF (INTCON<1>) is set. This interrupt can be disabled by clearing enable bit INTE (INTCON<4>). Flag bit INTF must be cleared in software in the Interrupt Service Routine before re-enabling this interrupt. The INT interrupt can wake-up the processor from SLEEP, if bit INTE was set prior to going into SLEEP. The status of global interrupt enable bit GIE decides whether or not the processor branches to the interrupt vector following wakeup. See Section 12.14 for details on SLEEP mode.

### 12.11.2 TMR0 INTERRUPT

An overflow (FFh  $\rightarrow$  00h) in the TMR0 register will set flag bit TMR0IF (INTCON<2>). The interrupt can be enabled/disabled by setting/clearing enable bit TMR0IE (INTCON<5>). (Section 5.0)

### 12.11.3 PORTB INTCON CHANGE

An input change on PORTB<7:4> sets flag bit RBIF (INTCON<0>). The interrupt can be enabled/disabled by setting/clearing enable bit RBIE (INTCON<4>), see Section 4.2.

## 12.12 Context Saving During Interrupts

During an interrupt, only the return PC value is saved on the stack. Typically, users may wish to save key registers during an interrupt (i.e., W, PCLATH and STA-TUS registers). This will have to be implemented in software, as shown in Example 12-1.

For the PIC16F73/74 devices, the register W\_TEMP must be defined in both banks 0 and 1 and must be defined at the same offset from the bank base address (i.e., If W\_TEMP is defined at 20h in bank 0, it must also be defined at A0h in bank 1.). The registers, PCLATH\_TEMP and STATUS\_TEMP, are only defined in bank 0.

Since the upper 16 bytes of each bank are common in the PIC16F76/77 devices, temporary holding registers W\_TEMP, STATUS\_TEMP and PCLATH\_TEMP should be placed in here. These 16 locations don't require banking and, therefore, make it easier for context save and restore. The same code shown in Example 12-1 can be used.

|     | LL 1 <u>2</u> -1. | SAVING STATUS, | W, AND FCEATH REGISTERS IN RAM                    |

|-----|-------------------|----------------|---------------------------------------------------|

| MOV | WF W_TEMP         | ; Copy         | W to TEMP register                                |

| SWA | PF STATUS         | ,W ;Swap       | status to be saved into W                         |

| CLR | F STATUS          | ;bank          | 0, regardless of current bank, Clears IRP,RP1,RP0 |

| MOV | WF STATUS         | _TEMP ;Save    | status to bank zero STATUS_TEMP register          |

| MOV | F PCLATH          | , W ;Only      | required if using pages 1, 2 and/or 3             |

| MOV | WF PCLATH         | _TEMP ;Save    | PCLATH into W                                     |

| CLR | F PCLATH          | ; Page         | zero, regardless of current page                  |

| :   |                   |                |                                                   |

| :(I | SR)               | ;Inse          | rt user code here                                 |

| :   |                   |                |                                                   |

| MOV | F PCLATH          | _TEMP, W ;Rest | ore PCLATH                                        |

| MOV | WF PCLATH         | ;Move          | W into PCLATH                                     |

| SWA | PF STATUS         | _TEMP,W ;Swap  | STATUS_TEMP register into W                       |

|     |                   | ;(set          | s bank to original state)                         |

| MOV | WF STATUS         | ;Move          | W into STATUS register                            |

| SWA | .PF W_TEMP        | ,F ;Swap       | W_TEMP                                            |

| SWA | PF W_TEMP         | ,W ;Swap       | W_TEMP into W                                     |

|     |                   |                |                                                   |

### EXAMPLE 12-1: SAVING STATUS, W, AND PCLATH REGISTERS IN RAM

## 13.0 INSTRUCTION SET SUMMARY

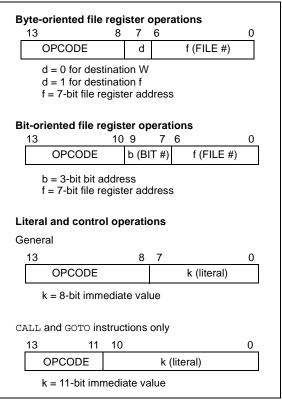

The PIC16 instruction set is highly orthogonal and is comprised of three basic categories:

- Byte-oriented operations

- Bit-oriented operations

- Literal and control operations

Each PIC16 instruction is a 14-bit word divided into an **opcode**, which specifies the instruction type and one or more **operands**, which further specify the operation of the instruction. The formats for each of the categories are presented in Figure 13-1, while the various opcode fields are summarized in Table 13-1.

Table 13-2 lists the instructions recognized by the MPASM<sup>™</sup> Assembler. A complete description of each instruction is also available in the PICmicro<sup>™</sup> Mid-Range Reference Manual (DS33023).

For **byte-oriented** instructions, ' $\pm$ ' represents a file register designator and 'a' represents a destination designator. The file register designator specifies which file register is to be used by the instruction.

The destination designator specifies where the result of the operation is to be placed. If 'd' is zero, the result is placed in the W register. If 'd' is one, the result is placed in the file register specified in the instruction.

For **bit-oriented** instructions, 'b' represents a bit field designator, which selects the bit affected by the operation, while 'f' represents the address of the file in which the bit is located.

For **literal and control** operations, 'k' represents an eight- or eleven-bit constant or literal value

One instruction cycle consists of four oscillator periods; for an oscillator frequency of 4 MHz, this gives a normal instruction execution time of 1  $\mu$ s. All instructions are executed within a single instruction cycle, unless a conditional test is true, or the program counter is changed as a result of an instruction. When this occurs, the execution takes two instruction cycles, with the second cycle executed as a NOP.

| Note: | To maintain upward compatibility with    |  |  |  |  |  |

|-------|------------------------------------------|--|--|--|--|--|

|       | future PIC16F7X products, do not use the |  |  |  |  |  |

|       | OPTION and TRIS instructions.            |  |  |  |  |  |

All instruction examples use the format '0xhh' to represent a hexadecimal number, where 'h' signifies a hexadecimal digit.

## 13.1 READ-MODIFY-WRITE OPERATIONS

Any instruction that specifies a file register as part of the instruction performs a Read-Modify-Write (R-M-W) operation. The register is read, the data is modified, and the result is stored according to either the instruction, or the destination designator 'd'. A read operation is performed on a register even if the instruction writes to that register. For example, a "clrf PORTB" instruction will read PORTB, clear all the data bits, then write the result back to PORTB. This example would have the unintended result that the condition that sets the RBIF flag would be cleared for pins configured as inputs and using the PORTB interrupt-on-change feature.

# TABLE 13-1: OPCODE FIELD DESCRIPTIONS

| Field | Description                                                                                                                                                                     |

|-------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| f     | Register file address (0x00 to 0x7F)                                                                                                                                            |

| W     | Working register (accumulator)                                                                                                                                                  |

| b     | Bit address within an 8-bit file register                                                                                                                                       |

| k     | Literal field, constant data or label                                                                                                                                           |

| x     | Don't care location (= 0 or 1).<br>The assembler will generate code with $x = 0$ .<br>It is the recommended form of use for<br>compatibility with all Microchip software tools. |

| d     | Destination select; $d = 0$ : store result in W,<br>d = 1: store result in file register f.<br>Default is $d = 1$ .                                                             |

| PC    | Program Counter                                                                                                                                                                 |

| TO    | Time-out bit                                                                                                                                                                    |

| PD    | Power-down bit                                                                                                                                                                  |

## FIGURE 13-1: GENERAL FORMAT FOR INSTRUCTIONS

| Param<br>No. | Symbol                | Characteristic                                                        | Min                                           | Тур†        | Max      | Units     | Conditions |  |

|--------------|-----------------------|-----------------------------------------------------------------------|-----------------------------------------------|-------------|----------|-----------|------------|--|

| 70*          | TssL2scH,<br>TssL2scL | $\overline{SS}\downarrow$ to SCK $\downarrow$ or SCK $\uparrow$ input | Тсү                                           |             | —        | ns        |            |  |

| 71*          | TscH                  | SCK input high time (Slave mo                                         | de)                                           | TCY + 20    | _        | —         | ns         |  |

| 72*          | TscL                  | SCK input low time (Slave mod                                         | le)                                           | TCY + 20    | _        | —         | ns         |  |

| 73*          | TdiV2scH,<br>TdiV2scL | Setup time of SDI data input to                                       | 100                                           | _           | —        | ns        |            |  |

| 74*          | TscH2diL,<br>TscL2diL | Hold time of SDI data input to S                                      | 100                                           |             | —        | ns        |            |  |

| 75*          | TdoR                  | SDO data output rise time                                             | Standard( <b>F</b> )<br>Extended( <b>LF</b> ) | _           | 10<br>25 | 25<br>50  | ns<br>ns   |  |

| 76*          | TdoF                  | SDO data output fall time                                             | —                                             | 10          | 25       | ns        |            |  |

| 77*          | TssH2doZ              | SS↑ to SDO output hi-impedan                                          | 10                                            | _           | 50       | ns        |            |  |

| 78*          | TscR                  | SCK output rise time<br>(Master mode)                                 | Standard( <b>F</b> )<br>Extended( <b>LF</b> ) | _           | 10<br>25 | 25<br>50  | ns<br>ns   |  |

| 79*          | TscF                  | SCK output fall time (Master m                                        | ode)                                          | _           | 10       | 25        | ns         |  |

| 80*          | TscH2doV,<br>TscL2doV | SDO data output valid after<br>SCK edge                               | Standard( <b>F</b> )<br>Extended( <b>LF</b> ) | _           |          | 50<br>145 | ns<br>ns   |  |

| 81*          | TdoV2scH,<br>TdoV2scL | SDO data output setup to SCK                                          | Тсу                                           |             |          | ns        |            |  |

| 82*          | TssL2doV              | SDO data output valid after SS                                        | —                                             | _           | 50       | ns        |            |  |