Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                  |

|----------------------------|-------------------------------------------------------------------------|

| Core Processor             | PIC                                                                     |

| Core Size                  | 8-Bit                                                                   |

| Speed                      | 20MHz                                                                   |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                                       |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                   |

| Number of I/O              | 33                                                                      |

| Program Memory Size        | 14KB (8K x 14)                                                          |

| Program Memory Type        | FLASH                                                                   |

| EEPROM Size                | -                                                                       |

| RAM Size                   | 368 x 8                                                                 |

| Voltage - Supply (Vcc/Vdd) | 4V ~ 5.5V                                                               |

| Data Converters            | A/D 8x8b                                                                |

| Oscillator Type            | External                                                                |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                      |

| Mounting Type              | Surface Mount                                                           |

| Package / Case             | 44-TQFP                                                                 |

| Supplier Device Package    | 44-TQFP (10x10)                                                         |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16f77-e-pt |

|                            |                                                                         |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### Note the following details of the code protection feature on PICmicro<sup>®</sup> MCUs.

- The PICmicro family meets the specifications contained in the Microchip Data Sheet.

- Microchip believes that its family of PICmicro microcontrollers is one of the most secure products of its kind on the market today, when used in the intended manner and under normal conditions.

- There are dishonest and possibly illegal methods used to breach the code protection feature. All of these methods, to our knowledge, require using the PICmicro microcontroller in a manner outside the operating specifications contained in the data sheet. The person doing so may be engaged in theft of intellectual property.

- Microchip is willing to work with the customer who is concerned about the integrity of their code.

- Neither Microchip nor any other semiconductor manufacturer can guarantee the security of their code. Code protection does not mean that we are guaranteeing the product as "unbreakable".

- Code protection is constantly evolving. We at Microchip are committed to continuously improving the code protection features of our product.

If you have any further questions about this matter, please contact the local sales office nearest to you.

Information contained in this publication regarding device applications and the like is intended through suggestion only and may be superseded by updates. It is your responsibility to ensure that your application meets with your specifications. No representation or warranty is given and no liability is assumed by Microchip Technology Incorporated with respect to the accuracy or use of such information, or infringement of patents or other intellectual property rights arising from such use or otherwise. Use of Microchip's products as critical components in life support systems is not authorized except with express written approval by Microchip. No licenses are conveyed, implicitly or otherwise, under any intellectual property rights.

#### Trademarks

The Microchip name and logo, the Microchip logo, FilterLab, KEELOQ, MPLAB, PIC, PICmicro, PICMASTER, PICSTART, PRO MATE, SEEVAL and The Embedded Control Solutions Company are registered trademarks of Microchip Technology Incorporated in the U.S.A. and other countries.

dsPIC, ECONOMONITOR, FanSense, FlexROM, fuzzyLAB, In-Circuit Serial Programming, ICSP, ICEPIC, microID, microPort, Migratable Memory, MPASM, MPLIB, MPLINK, MPSIM, MXDEV, PICC, PICDEM, PICDEM.net, rfPIC, Select Mode and Total Endurance are trademarks of Microchip Technology Incorporated in the U.S.A.

Serialized Quick Term Programming (SQTP) is a service mark of Microchip Technology Incorporated in the U.S.A.

All other trademarks mentioned herein are property of their respective companies.

© 2002, Microchip Technology Incorporated, Printed in the U.S.A., All Rights Reserved.

Microchip received QS-9000 quality system certification for its worldwide headquarters, design and wafer fabrication facilities in Chandler and Tempe, Arizona in July 1999. The Company's quality system processes and procedures are QS-9000 compliant for its PICmicro® 8-bit MCUs, KEEL00® code hopping devices, Serial EEPROMs and microperipheral products. In addition, Microchip's quality system for the design and manufacture of development systems is ISO 9001 certified.

PIC16F7X

## 28/40-Pin 8-Bit CMOS FLASH Microcontrollers

#### **Devices Included in this Data Sheet:**

- PIC16F73PIC16F74

- PIC16F76PIC16F77

#### **High Performance RISC CPU:**

- High performance RISC CPU

- Only 35 single word instructions to learn

- All single cycle instructions except for program branches which are two-cycle

- Operating speed: DC 20 MHz clock input DC - 200 ns instruction cycle

- Up to 8K x 14 words of FLASH Program Memory, Up to 368 x 8 bytes of Data Memory (RAM)

- Pinout compatible to the PIC16C73B/74B/76/77

- Pinout compatible to the PIC16F873/874/876/877

- Interrupt capability (up to 12 sources)

- Eight level deep hardware stack

- Direct, Indirect and Relative Addressing modes

- Processor read access to program memory

#### **Special Microcontroller Features:**

- Power-on Reset (POR)

- Power-up Timer (PWRT) and Oscillator Start-up Timer (OST)

- Watchdog Timer (WDT) with its own on-chip RC oscillator for reliable operation

- Programmable code protection

- Power saving SLEEP mode

- Selectable oscillator options

- In-Circuit Serial Programming<sup>™</sup> (ICSP<sup>™</sup>) via two pins

#### **Peripheral Features:**

- Timer0: 8-bit timer/counter with 8-bit prescaler

- Timer1: 16-bit timer/counter with prescaler, can be incremented during SLEEP via external crystal/clock

- Timer2: 8-bit timer/counter with 8-bit period register, prescaler and postscaler

- Two Capture, Compare, PWM modules

- Capture is 16-bit, max. resolution is 12.5 ns

- Compare is 16-bit, max. resolution is 200 ns

PWM max. resolution is 10-bit

- 8-bit, up to 8-channel Analog-to-Digital converter

- Synchronous Serial Port (SSP) with SPI™ (Master mode) and I<sup>2</sup>C<sup>™</sup> (Slave)

- Universal Synchronous Asynchronous Receiver Transmitter (USART/SCI)

- Parallel Slave Port (PSP), 8-bits wide with external RD, WR and CS controls (40/44-pin only)

- Brown-out detection circuitry for Brown-out Reset (BOR)

#### **CMOS Technology:**

- Low power, high speed CMOS FLASH technology

- Fully static design

- Wide operating voltage range: 2.0V to 5.5V

- High Sink/Source Current: 25 mA

- Industrial temperature range

- Low power consumption:

- < 2 mA typical @ 5V, 4 MHz

- 20 μA typical @ 3V, 32 kHz

- < 1 µA typical standby current

|          | Program Memory                  | Data            |     |            | 8-bit CCP         |       | SS              | P                           |       | Timere             |  |

|----------|---------------------------------|-----------------|-----|------------|-------------------|-------|-----------------|-----------------------------|-------|--------------------|--|

| Device   | (# Single Word<br>Instructions) | SRAM<br>(Bytes) | I/O | Interrupts | 8-bit<br>A/D (ch) | (PWM) | SPI<br>(Master) | l <sup>2</sup> C<br>(Slave) | USART | Timers<br>8/16-bit |  |

| PIC16F73 | 4096                            | 192             | 22  | 11         | 5                 | 2     | Yes             | Yes                         | Yes   | 2 / 1              |  |

| PIC16F74 | 4096                            | 192             | 33  | 12         | 8                 | 2     | Yes             | Yes                         | Yes   | 2/1                |  |

| PIC16F76 | 8192                            | 368             | 22  | 11         | 5                 | 2     | Yes             | Yes                         | Yes   | 2 / 1              |  |

| PIC16F77 | 8192                            | 368             | 33  | 12         | 8                 | 2     | Yes             | Yes                         | Yes   | 2 / 1              |  |

#### PIC16F77/76 REGISTER FILE MAP FIGURE 2-2:

| A                              | File<br>ddress | A                                          | File<br>ddress |                                            | File<br>Address |                                            | File<br>Addres |

|--------------------------------|----------------|--------------------------------------------|----------------|--------------------------------------------|-----------------|--------------------------------------------|----------------|

| Indirect addr.(*)              | 00h            | Indirect addr.(*)                          | 80h            | Indirect addr.(*)                          | 100h            | Indirect addr.(*)                          | 180h           |

| TMR0                           | 01h            | OPTION_REG                                 | 81h            | TMR0                                       | 101h            | OPTION_REG                                 | 181h           |

| PCL                            | 02h            | PCL                                        | 82h            | PCL                                        | 102h            | PCL                                        | 182h           |

| STATUS                         | 03h            | STATUS                                     | 83h            | STATUS                                     | 103h            | STATUS                                     | 183h           |

| FSR                            | 04h            | FSR                                        | 84h            | FSR                                        | 104h            | FSR                                        | 184h           |

| PORTA                          | 05h            | TRISA                                      | 85h            |                                            | 105h            |                                            | 185h           |

| PORTB                          | 06h            | TRISB                                      | 86h            | PORTB                                      | 106h            | TRISB                                      | 186h           |

| PORTC                          | 07h            | TRISC                                      | 87h            |                                            | 107h            |                                            | 187h           |

| PORTD <sup>(1)</sup>           | 08h            | TRISD <sup>(1)</sup>                       | 88h            |                                            | 108h            |                                            | 188h           |

| PORTE <sup>(1)</sup>           | 09h            | TRISE <sup>(1)</sup>                       | 89h            |                                            | 109h            |                                            | 189h           |

| PCLATH                         | 0Ah            | PCLATH                                     | 8Ah            | PCLATH                                     | 10Ah            | PCLATH                                     | 18Ah           |

| INTCON                         | 0Bh            | INTCON                                     | 8Bh            | INTCON                                     | 10Bh            | INTCON                                     | 18Bh           |

| PIR1                           | 0Ch            | PIE1                                       | 8Ch            | PMDATA                                     | 10Ch            | PMCON1                                     | 18Ch           |

| PIR2                           | 0Dh            | PIE2                                       | 8Dh            | PMADR                                      | 10Dh            |                                            | 18Dh           |

| TMR1L                          | 0Eh            | PCON                                       | 8Eh            | PMDATH                                     | 10Eh            |                                            | 18Eh           |

| TMR1H                          | 0Fh            |                                            | 8Fh            | PMADRH                                     | 10Fh            |                                            | 18Fh           |

| T1CON                          | 10h            |                                            | 90h            |                                            | 110h            |                                            | 190h           |

| TMR2                           | 11h            |                                            | 91h            |                                            | 111h            |                                            | 191h           |

| T2CON                          | 12h            | PR2                                        | 92h            |                                            | 112h            |                                            | 192h           |

| SSPBUF                         | 13h            | SSPADD                                     | 93h            |                                            | 113h            |                                            | 193h           |

| SSPCON                         | 14h            | SSPSTAT                                    | 94h            |                                            | 114h            |                                            | 194h           |

| CCPR1L                         | 15h            |                                            | 95h            |                                            | 115h            |                                            | 195h           |

| CCPR1H                         | 16h            |                                            | 96h            |                                            | 116h            |                                            | 196h           |

| CCP1CON                        | 17h            |                                            | 97h            | General                                    | 117h            | General                                    | 197h           |

| RCSTA                          | 18h            | TXSTA                                      | 98h            | Purpose<br>Register                        | 118h            | Purpose<br>Register                        | 198h           |

| TXREG                          | 19h            | SPBRG                                      | 99h            | 16 Bytes                                   | 119h            | 16 Bytes                                   | 199h           |

| RCREG                          | 1Ah            | OF BITO                                    | 9Ah            |                                            | 11Ah            | ,                                          | 19Ah           |

| CCPR2L                         | 1Bh            |                                            | 9Bh            |                                            | 11Bh            |                                            | 19Bh           |

| CCPR2H                         | 1Ch            |                                            | 9Ch            |                                            | 11Ch            |                                            | 19Ch           |

| CCP2CON                        | 1Dh            |                                            | 9Dh            |                                            | 11Dh            |                                            | 19Dh           |

| ADRES                          | 1Eh            |                                            | 9Eh            |                                            | 11Eh            |                                            | 19Eh           |

| ADCON0                         | 1Fh            | ADCON1                                     | 9Fh            |                                            | 11Fh            |                                            | 19Fh           |

| 71200110                       | 20h            | 7.000111                                   |                |                                            | 120h            |                                            |                |

|                                | 2011           |                                            | A0h            |                                            | 12011           |                                            | 1A0h           |

| General<br>Purpose<br>Register |                | General<br>Purpose<br>Register<br>80 Bytes |                | General<br>Purpose<br>Register<br>80 Bytes |                 | General<br>Purpose<br>Register<br>80 Bytes |                |

| 96 Bytes                       |                | accesses                                   | EFh<br>F0h     | accesses                                   | 16Fh<br>170h    | accesses                                   | 1EFh<br>1F0h   |

|                                | 7Fh            | 70h-7Fh                                    | FFh            | 70h-7Fh                                    | 17Fh            | 70h - 7Fh                                  | 1FFh           |

| Bank 0                         |                | Bank 1                                     |                | Bank 2                                     |                 | Bank 3                                     |                |

Unimplemented data memory locations, read as '0'. \* Not a physical register.

Note 1: These registers are not implemented on 28-pin devices.

x = Bit is unknown

#### **PCON Register** 2.2.2.8

The Power Control (PCON) register contains flag bits to allow differentiation between a Power-on Reset (POR), a Brown-out Reset (BOR), a Watchdog Reset (WDT) and an external MCLR Reset.

BOR is unknown on POR. It must be set by Note: the user and checked on subsequent RESETS to see if BOR is clear, indicating a brown-out has occurred. The BOR status bit is not predictable if the brown-out circuit is disabled (by clearing the BODEN bit in the configuration word).

#### **REGISTER 2-8:** PCON REGISTER (ADDRESS 8Eh)

- n = Value at POR reset

|         | U-0                                                                                   | U-0         | U-0           | U-0            | U-0         | U-0         | R/W-0         | R/W-1   |  |  |  |  |

|---------|---------------------------------------------------------------------------------------|-------------|---------------|----------------|-------------|-------------|---------------|---------|--|--|--|--|

|         | _                                                                                     | _           | _             |                | —           |             | POR           | BOR     |  |  |  |  |

|         | bit 7                                                                                 |             |               |                |             |             |               | bit 0   |  |  |  |  |

|         |                                                                                       |             |               |                |             |             |               |         |  |  |  |  |

| bit 7-2 | Unimplem                                                                              | ented: Rea  | d as '0'      |                |             |             |               |         |  |  |  |  |

| bit 1   | POR: Pow                                                                              | er-on Reset | Status bit    |                |             |             |               |         |  |  |  |  |

|         | 1 = No Power-on Reset occurred                                                        |             |               |                |             |             |               |         |  |  |  |  |

|         | 0 = A Power-on Reset occurred (must be set in software after a Power-on Reset occurs) |             |               |                |             |             |               |         |  |  |  |  |

| bit 0   | BOR: Brov                                                                             | vn-out Rese | t Status bit  |                |             |             |               |         |  |  |  |  |

|         | 1 = No Bro                                                                            | wn-out Res  | et occurred   |                |             |             |               |         |  |  |  |  |

|         | 0 = A Brow                                                                            | n-out Rese  | t occurred (m | lust be set in | software af | ter a Brown | -out Reset of | occurs) |  |  |  |  |

|         |                                                                                       |             |               |                |             |             |               |         |  |  |  |  |

|         | Legend:                                                                               |             |               |                |             |             |               |         |  |  |  |  |

|         | R = Reada                                                                             | ble bit     | W = W         | ritable bit    | U = Unim    | plemented l | bit, read as  | '0'     |  |  |  |  |

'0' = Bit is cleared

'1' = Bit is set

NOTES:

| Name         | Bit# | Buffer | Function                                                                        |

|--------------|------|--------|---------------------------------------------------------------------------------|

| RA0/AN0      | bit0 | TTL    | Input/output or analog input.                                                   |

| RA1/AN1      | bit1 | TTL    | Input/output or analog input.                                                   |

| RA2/AN2      | bit2 | TTL    | Input/output or analog input.                                                   |

| RA3/AN3/VREF | bit3 | TTL    | Input/output or analog input or VREF.                                           |

| RA4/T0CKI    | bit4 | ST     | Input/output or external clock input for Timer0. Output is open drain type.     |

| RA5/SS/AN4   | bit5 | TTL    | Input/output or slave select input for synchronous serial port or analog input. |

#### TABLE 4-1: PORTA FUNCTIONS

Legend: TTL = TTL input, ST = Schmitt Trigger input

#### TABLE 4-2: SUMMARY OF REGISTERS ASSOCIATED WITH PORTA

| Address | Name   | Bit 7 | Bit 6 | Bit 5 | Bit 4                         | Bit 3 | Bit 2 | Bit 1 | Bit 0 | Value on:<br>POR,<br>BOR | Value on all<br>other<br>RESETS |

|---------|--------|-------|-------|-------|-------------------------------|-------|-------|-------|-------|--------------------------|---------------------------------|

| 05h     | PORTA  | _     | _     | RA5   | RA4                           | RA3   | RA2   | RA1   | RA0   | 0x 0000                  | 0u 0000                         |

| 85h     | TRISA  | _     | _     | PORTA | PORTA Data Direction Register |       |       |       |       |                          | 11 1111                         |

| 9Fh     | ADCON1 |       | _     | _     | _                             | _     | PCFG2 | PCFG1 | PCFG0 | 000                      | 000                             |

Legend: x = unknown, u = unchanged, - = unimplemented locations read as '0'. Shaded cells are not used by PORTA.

**Note:** When using the SSP module in SPI Slave mode and  $\overline{SS}$  enabled, the A/D converter must be set to one of the following modes where PCFG2:PCFG0 = 100, 101, 11x.

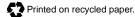

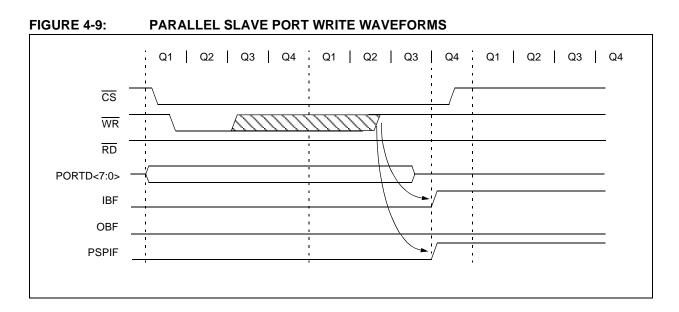

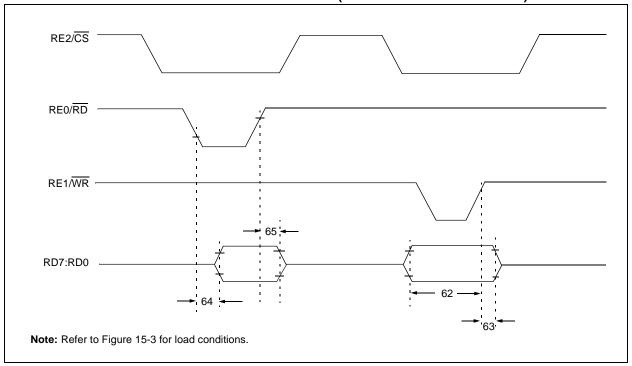

#### FIGURE 4-10: PARALLEL SLAVE PORT READ WAVEFORMS

#### TABLE 4-11: REGISTERS ASSOCIATED WITH PARALLEL SLAVE PORT

| Address | Name   | Bit 7                                             | Bit 6 | Bit 5 | Bit 4   | Bit 3 | Bit 2   | Bit 1       | Bit 0    | Value on:<br>POR,<br>BOR | Value on<br>all other<br>RESETS |

|---------|--------|---------------------------------------------------|-------|-------|---------|-------|---------|-------------|----------|--------------------------|---------------------------------|

| 08h     | PORTD  | Port data latch when written: Port pins when read |       |       |         |       |         |             |          | xxxx xxxx                | uuuu uuuu                       |

| 09h     | PORTE  | —                                                 |       | —     |         | —     | RE2     | RE1         | RE0      | xxx                      | uuu                             |

| 89h     | TRISE  | IBF                                               | OBF   | IBOV  | PSPMODE | _     | PORTE D | Data Direct | ion Bits | 0000 -111                | 0000 -111                       |

| 0Ch     | PIR1   | PSPIF <sup>(1)</sup>                              | ADIF  | RCIF  | TXIF    | SSPIF | CCP1IF  | TMR2IF      | TMR1IF   | 0000 0000                | 0000 0000                       |

| 8Ch     | PIE1   | PSPIE <sup>(1)</sup>                              | ADIE  | RCIE  | TXIE    | SSPIE | CCP1IE  | TMR2IE      | TMR1IE   | 0000 0000                | 0000 0000                       |

| 9Fh     | ADCON1 | _                                                 | _     | _     | _       | _     | PCFG2   | PCFG1       | PCFG0    | 000                      | 000                             |

Legend: x = unknown, u = unchanged, - = unimplemented, read as '0'. Shaded cells are not used by the Parallel Slave Port.

**Note 1:** Bits PSPIE and PSPIF are reserved on the PIC16F73/76; always maintain these bits clear.

#### 5.2 Using Timer0 with an External Clock

When no prescaler is used, the external clock input is the same as the prescaler output. The synchronization of T0CKI, with the internal phase clocks, is accomplished by sampling the prescaler output on the Q2 and Q4 cycles of the internal phase clocks. Therefore, it is necessary for T0CKI to be high for at least 2Tosc (and a small RC delay of 20 ns) and low for at least 2Tosc (and a small RC delay of 20 ns). Refer to the electrical specification of the desired device.

| REGISTER 5-1: | <b>OPTION_REG REGISTER</b> |

|---------------|----------------------------|

|---------------|----------------------------|

|         | R/W-1                                                                                                            | R/W-1                                                | R/W-1        | R/W-1        | R/W-1      | R/W-1      | R/W-1        | R/W-1   |  |  |  |  |  |

|---------|------------------------------------------------------------------------------------------------------------------|------------------------------------------------------|--------------|--------------|------------|------------|--------------|---------|--|--|--|--|--|

|         | RBPU                                                                                                             | INTEDG                                               | TOCS         | T0SE         | PSA        | PS2        | PS1          | PS0     |  |  |  |  |  |

|         | bit 7                                                                                                            |                                                      |              |              |            |            |              | bit 0   |  |  |  |  |  |

|         |                                                                                                                  |                                                      |              |              |            |            |              |         |  |  |  |  |  |

| bit 7   | RBPU: PC                                                                                                         | ORTB Pull-up                                         | Enable bit   | (see Sectior | n 2.2.2.2) |            |              |         |  |  |  |  |  |

| bit 6   | INTEDG:                                                                                                          | Interrupt Edg                                        | e Select bit | (see Section | n 2.2.2.2) |            |              |         |  |  |  |  |  |

| bit 5   | TOCS: TM                                                                                                         | IR0 Clock Sc                                         | ource Select | bit          |            |            |              |         |  |  |  |  |  |

|         |                                                                                                                  | tion on T0Ck<br>al instruction                       |              | (CLKOUT)     |            |            |              |         |  |  |  |  |  |

| bit 4   | TOSE: TM                                                                                                         | R0 Source E                                          | Edge Select  | bit          |            |            |              |         |  |  |  |  |  |

|         | 1 = Incren                                                                                                       | 1 = Increment on high-to-low transition on T0CKI pin |              |              |            |            |              |         |  |  |  |  |  |

|         | 0 = Incren                                                                                                       | nent on low-t                                        | o-high trans | ition on TOC | KI pin     |            |              |         |  |  |  |  |  |

| bit 3   | PSA: Pres                                                                                                        | SA: Prescaler Assignment bit                         |              |              |            |            |              |         |  |  |  |  |  |

|         | <ul> <li>1 = Prescaler is assigned to the WDT</li> <li>0 = Prescaler is assigned to the Timer0 module</li> </ul> |                                                      |              |              |            |            |              |         |  |  |  |  |  |

| bit 2-0 | PS2:PS0:                                                                                                         | PS2:PS0: Prescaler Rate Select bits                  |              |              |            |            |              |         |  |  |  |  |  |

|         | Bit Value                                                                                                        | TMR0 Rate                                            | WDT Rate     |              |            |            |              |         |  |  |  |  |  |

|         | 000                                                                                                              | 1:2                                                  | 1:1          |              |            |            |              |         |  |  |  |  |  |

|         | 001                                                                                                              | 1:4<br>1:8                                           | 1:2<br>1:4   |              |            |            |              |         |  |  |  |  |  |

|         | 010<br>011                                                                                                       | 1:16                                                 | 1:4          |              |            |            |              |         |  |  |  |  |  |

|         | 100                                                                                                              | 1:32                                                 | 1:16         |              |            |            |              |         |  |  |  |  |  |

|         | 101                                                                                                              | 1:64                                                 | 1:32         |              |            |            |              |         |  |  |  |  |  |

|         | 110                                                                                                              | 1:128                                                | 1:64         |              |            |            |              |         |  |  |  |  |  |

|         | 111                                                                                                              | 1 : 256                                              | 1 : 128      |              |            |            |              |         |  |  |  |  |  |

|         | Legend:                                                                                                          |                                                      |              |              |            |            |              |         |  |  |  |  |  |

|         | R = Reada                                                                                                        | able bit                                             | W = V        | Vritable bit | U = Unii   | mplemented | bit, read as | '0'     |  |  |  |  |  |

|         | - n = Value                                                                                                      | e at POR res                                         | et '1' = B   | Bit is set   | '0' = Bit  | is cleared | x = Bit is ι | unknown |  |  |  |  |  |

|         |                                                                                                                  |                                                      |              |              |            |            |              |         |  |  |  |  |  |

|         |                                                                                                                  | To avoid ar                                          |              |              |            |            |              |         |  |  |  |  |  |

|         |                                                                                                                  | Example 5-1<br>caler assigni<br>even if the W        | ment betwee  | en Timer0 a  |            |            |              |         |  |  |  |  |  |

# PIC16F7X

## REGISTER 11-2: ADCON1 REGISTER (ADDRESS 9Fh)

| U-0   | U-0 | U-0 | U-0 | U-0 | R/W-0 | R/W-0 | R/W-0 |

|-------|-----|-----|-----|-----|-------|-------|-------|

| _     | —   |     | —   |     | PCFG2 | PCFG1 | PCFG0 |

| bit 7 |     |     |     |     |       |       | bit 0 |

bit 7-3 Unimplemented: Read as '0'

bit 2-0 PCFG2:PCFG0: A/D Port Configuration Control bits

| PCFG2:PCFG0 | RA0 | RA1 | RA2 | RA5 | RA3  | RE0 <sup>(1)</sup> | RE1 <sup>(1)</sup> | RE2 <sup>(1)</sup> | VREF |

|-------------|-----|-----|-----|-----|------|--------------------|--------------------|--------------------|------|

| 000         | Α   | Α   | Α   | Α   | Α    | Α                  | А                  | А                  | Vdd  |

| 001         | Α   | Α   | Α   | Α   | VREF | Α                  | А                  | Α                  | RA3  |

| 010         | Α   | Α   | Α   | Α   | Α    | D                  | D                  | D                  | Vdd  |

| 011         | Α   | Α   | Α   | Α   | VREF | D                  | D                  | D                  | RA3  |

| 100         | Α   | Α   | D   | D   | Α    | D                  | D                  | D                  | Vdd  |

| 101         | Α   | Α   | D   | D   | VREF | D                  | D                  | D                  | RA3  |

| 11x         | D   | D   | D   | D   | D    | D                  | D                  | D                  | Vdd  |

A = Analog input

D = Digital I/O

Note 1: RE0, RE1 and RE2 are implemented on the PIC16F74/77 only.

| Legend:                  |                  |                      |                    |

|--------------------------|------------------|----------------------|--------------------|

| R = Readable bit         | W = Writable bit | U = Unimplemented    | bit, read as '0'   |

| - n = Value at POR reset | '1' = Bit is set | '0' = Bit is cleared | x = Bit is unknown |

#### **12.2 Oscillator Configurations**

#### 12.2.1 OSCILLATOR TYPES

The PIC16F7X can be operated in four different oscillator modes. The user can program two configuration bits (FOSC1 and FOSC0) to select one of these four modes:

- LP Low Power Crystal

- XT Crystal/Resonator

- HS High Speed Crystal/Resonator

- RC Resistor/Capacitor

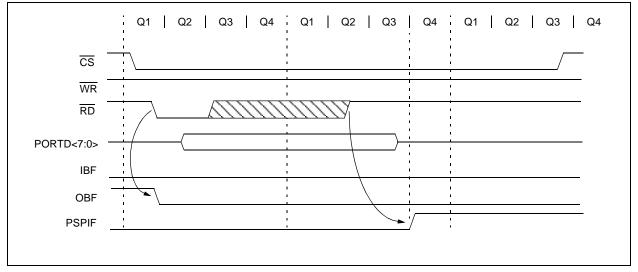

## 12.2.2 CRYSTAL OSCILLATOR/CERAMIC RESONATORS

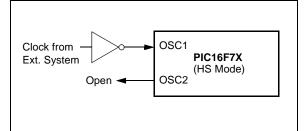

In XT, LP or HS modes, a crystal or ceramic resonator is connected to the OSC1/CLKIN and OSC2/CLKOUT pins to establish oscillation (Figure 12-1). The PIC16F7X oscillator design requires the use of a parallel cut crystal. Use of a series cut crystal may give a frequency out of the crystal manufacturers specifications. When in HS mode, the device can accept an external clock source to drive the OSC1/CLKIN pin (Figure 12-2). See Figure 15-1 or Figure 15-2 (depending on the part number and VDD range) for valid external clock frequencies.

#### FIGURE 12-1: CRYSTAL/CERAMIC RESONATOR OPERATION (HS, XT OR LP OSC CONFIGURATION)

3: RF varies with the crystal chosen.

#### FIGURE 12-2:

#### EXTERNAL CLOCK INPUT OPERATION (HS OSC CONFIGURATION)

#### TABLE 12-1: CERAMIC RESONATORS (FOR DESIGN GUIDANCE ONLY)

| Typical Capacitor Values Used: |          |       |       |

|--------------------------------|----------|-------|-------|

| Mode                           | Freq     | OSC1  | OSC2  |

| XT                             | 455 kHz  | 56 pF | 56 pF |

|                                | 2.0 MHz  | 47 pF | 47 pF |

|                                | 4.0 MHz  | 33 pF | 33 pF |

| HS                             | 8.0 MHz  | 27 pF | 27 pF |

|                                | 16.0 MHz | 22 pF | 22 pF |

Capacitor values are for design guidance only.

These capacitors were tested with the resonators listed below for basic start-up and operation. These values were not optimized.

Different capacitor values may be required to produce acceptable oscillator operation. The user should test the performance of the oscillator over the expected VDD and temperature range for the application.

See the notes at the bottom of page 92 for additional information.

| Resonators Used: |                        |

|------------------|------------------------|

| 455 kHz          | Panasonic EFO-A455K04B |

| 2.0 MHz          | Murata Erie CSA2.00MG  |

| 4.0 MHz          | Murata Erie CSA4.00MG  |

| 8.0 MHz          | Murata Erie CSA8.00MT  |

| 16.0 MHz         | Murata Erie CSA16.00MX |

## 13.0 INSTRUCTION SET SUMMARY

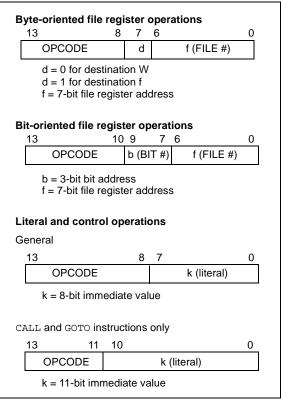

The PIC16 instruction set is highly orthogonal and is comprised of three basic categories:

- Byte-oriented operations

- Bit-oriented operations

- Literal and control operations

Each PIC16 instruction is a 14-bit word divided into an **opcode**, which specifies the instruction type and one or more **operands**, which further specify the operation of the instruction. The formats for each of the categories are presented in Figure 13-1, while the various opcode fields are summarized in Table 13-1.

Table 13-2 lists the instructions recognized by the MPASM<sup>™</sup> Assembler. A complete description of each instruction is also available in the PICmicro<sup>™</sup> Mid-Range Reference Manual (DS33023).

For **byte-oriented** instructions, ' $\pm$ ' represents a file register designator and 'a' represents a destination designator. The file register designator specifies which file register is to be used by the instruction.

The destination designator specifies where the result of the operation is to be placed. If 'd' is zero, the result is placed in the W register. If 'd' is one, the result is placed in the file register specified in the instruction.

For **bit-oriented** instructions, 'b' represents a bit field designator, which selects the bit affected by the operation, while 'f' represents the address of the file in which the bit is located.

For **literal and control** operations, 'k' represents an eight- or eleven-bit constant or literal value

One instruction cycle consists of four oscillator periods; for an oscillator frequency of 4 MHz, this gives a normal instruction execution time of 1  $\mu$ s. All instructions are executed within a single instruction cycle, unless a conditional test is true, or the program counter is changed as a result of an instruction. When this occurs, the execution takes two instruction cycles, with the second cycle executed as a NOP.

| Note: | To maintain upward compatibility with    |

|-------|------------------------------------------|

|       | future PIC16F7X products, do not use the |

|       | OPTION and TRIS instructions.            |

All instruction examples use the format '0xhh' to represent a hexadecimal number, where 'h' signifies a hexadecimal digit.

#### 13.1 READ-MODIFY-WRITE OPERATIONS

Any instruction that specifies a file register as part of the instruction performs a Read-Modify-Write (R-M-W) operation. The register is read, the data is modified, and the result is stored according to either the instruction, or the destination designator 'd'. A read operation is performed on a register even if the instruction writes to that register. For example, a "clrf PORTB" instruction will read PORTB, clear all the data bits, then write the result back to PORTB. This example would have the unintended result that the condition that sets the RBIF flag would be cleared for pins configured as inputs and using the PORTB interrupt-on-change feature.

# TABLE 13-1: OPCODE FIELD DESCRIPTIONS

| Field | Description                                                                                                                                                                     |

|-------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| f     | Register file address (0x00 to 0x7F)                                                                                                                                            |

| W     | Working register (accumulator)                                                                                                                                                  |

| b     | Bit address within an 8-bit file register                                                                                                                                       |

| k     | Literal field, constant data or label                                                                                                                                           |

| x     | Don't care location (= 0 or 1).<br>The assembler will generate code with $x = 0$ .<br>It is the recommended form of use for<br>compatibility with all Microchip software tools. |

| d     | Destination select; $d = 0$ : store result in W,<br>d = 1: store result in file register f.<br>Default is $d = 1$ .                                                             |

| PC    | Program Counter                                                                                                                                                                 |

| TO    | Time-out bit                                                                                                                                                                    |

| PD    | Power-down bit                                                                                                                                                                  |

## FIGURE 13-1: GENERAL FORMAT FOR INSTRUCTIONS

# PIC16F7X

| CALL             | Call Subroutine                                                                                                                                                                                                                               |

|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [ <i>label</i> ] CALL k                                                                                                                                                                                                                       |

| Operands:        | $0 \le k \le 2047$                                                                                                                                                                                                                            |

| Operation:       | $\begin{array}{l} (PC)+1 \rightarrow TOS, \\ k \rightarrow PC < 10:0>, \\ (PCLATH < 4:3>) \rightarrow PC < 12:11> \end{array}$                                                                                                                |

| Status Affected: | None                                                                                                                                                                                                                                          |

| Description:     | Call Subroutine. First, return<br>address (PC+1) is pushed onto<br>the stack. The eleven-bit immedi-<br>ate address is loaded into PC bits<br><10:0>. The upper bits of the PC<br>are loaded from PCLATH. CALL is<br>a two-cycle instruction. |

| CLRWDT                         | Clear Watchdog Timer                                                                                                                                                                 |

|--------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:                        | [label] CLRWDT                                                                                                                                                                       |

| Operands:                      | None                                                                                                                                                                                 |

| Operation:<br>Status Affected: | $\begin{array}{l} 00h \rightarrow WDT \\ 0 \rightarrow WDT \ prescaler, \\ 1 \rightarrow \overline{TO} \\ 1 \rightarrow \overline{PD} \\ \overline{TO}, \ \overline{PD} \end{array}$ |

| Description:                   | CLRWDT instruction resets the<br>Watchdog Timer. It also resets the<br>prescaler of the WDT. Status bits<br>TO and PD are set.                                                       |

| CLRF             | Clear f                                                               |

|------------------|-----------------------------------------------------------------------|

| Syntax:          | [label] CLRF f                                                        |

| Operands:        | $0 \le f \le 127$                                                     |

| Operation:       | $\begin{array}{l} 00h \rightarrow (f) \\ 1 \rightarrow Z \end{array}$ |

| Status Affected: | Z                                                                     |

| Description:     | The contents of register 'f' are cleared and the Z bit is set.        |

| COMF             | Complement f                                                                                                                                            |

|------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [ <i>label</i> ] COMF f,d                                                                                                                               |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ d \in \ [0,1] \end{array}$                                                                                       |

| Operation:       | $(\overline{f}) \rightarrow (destination)$                                                                                                              |

| Status Affected: | Z                                                                                                                                                       |

| Description:     | The contents of register 'f' are<br>complemented. If 'd' is 0, the<br>result is stored in W. If 'd' is 1, the<br>result is stored back in register 'f'. |

| CLRW             | Clear W                                                               |

|------------------|-----------------------------------------------------------------------|

| Syntax:          | [label] CLRW                                                          |

| Operands:        | None                                                                  |

| Operation:       | $\begin{array}{l} 00h \rightarrow (W) \\ 1 \rightarrow Z \end{array}$ |

| Status Affected: | Z                                                                     |

| Description:     | W register is cleared. Zero bit (Z) is set.                           |

| DECF             | Decrement f                                                                                                                                   |

|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [ label ] DECF f,d                                                                                                                            |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ d \in \ [0,1] \end{array}$                                                                             |

| Operation:       | (f) - 1 $\rightarrow$ (destination)                                                                                                           |

| Status Affected: | Z                                                                                                                                             |

| Description:     | Decrement register 'f'. If 'd' is 0,<br>the result is stored in the W<br>register. If 'd' is 1, the result is<br>stored back in register 'f'. |

# PIC16F7X

| SWAPF            | Swap Nibbles in f                                                                                                                                                  |

|------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [label] SWAPF f,d                                                                                                                                                  |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ d \in \ [0,1] \end{array}$                                                                                                  |

| Operation:       | $(f<3:0>) \rightarrow (destination<7:4>), (f<7:4>) \rightarrow (destination<3:0>)$                                                                                 |

| Status Affected: | None                                                                                                                                                               |

| Description:     | The upper and lower nibbles of register 'f' are exchanged. If 'd' is 0, the result is placed in the W register. If 'd' is 1, the result is placed in register 'f'. |

| XORWF            | Exclusive OR W with f                                                                                                                                                       |

|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [label] XORWF f,d                                                                                                                                                           |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ d \in \left[0,1\right] \end{array}$                                                                                                  |

| Operation:       | (W) .XOR. (f) $\rightarrow$ (destination)                                                                                                                                   |

| Status Affected: | Z                                                                                                                                                                           |

| Description:     | Exclusive OR the contents of the W register with register 'f'. If 'd' is 0, the result is stored in the W register. If 'd' is 1, the result is stored back in register 'f'. |

| XORLW            | Exclusive OR Literal with W                                                                                                |

|------------------|----------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [ <i>label</i> ] XORLW k                                                                                                   |

| Operands:        | $0 \le k \le 255$                                                                                                          |

| Operation:       | (W) .XOR. $k \rightarrow (W)$                                                                                              |

| Status Affected: | Z                                                                                                                          |

| Description:     | The contents of the W register<br>are XOR'ed with the eight-bit<br>literal 'k'. The result is placed in<br>the W register. |

### 15.3 Timing Parameter Symbology

The timing parameter symbols have been created using one of the following formats:

| 1. TppS2p             | 1. TppS2ppS                         |       | (I <sup>2</sup> C specifications only) |

|-----------------------|-------------------------------------|-------|----------------------------------------|

| 2. TppS               |                                     | 4. Ts | (I <sup>2</sup> C specifications only) |

| Т                     |                                     |       |                                        |

| F                     | Frequency                           | Т     | Time                                   |

| Lowerca               | se letters (pp) and their meanings: |       |                                        |

| рр                    |                                     |       |                                        |

| сс                    | CCP1                                | OSC   | OSC1                                   |

| ck                    | CLKOUT                              | rd    | RD                                     |

| CS                    | CS                                  | rw    | RD or WR                               |

| di                    | SDI                                 | SC    | SCK                                    |

| do                    | SDO                                 | SS    | SS                                     |

| dt                    | Data in                             | tO    | TOCKI                                  |

| io                    | I/O port                            | t1    | T1CKI                                  |

| mc                    | MCLR                                | wr    | WR                                     |

|                       | se letters and their meanings:      |       |                                        |

| S                     |                                     |       |                                        |

| F                     | Fall                                | Р     | Period                                 |

| Н                     | High                                | R     | Rise                                   |

| I                     | Invalid (Hi-impedance)              | V     | Valid                                  |

| L                     | Low                                 | Z     | Hi-impedance                           |

| I <sup>2</sup> C only |                                     |       |                                        |

| AA                    | output access                       | High  | High                                   |

| BUF                   | Bus free                            | Low   | Low                                    |

| TCC:ST (I             | <sup>2</sup> C specifications only) |       |                                        |

| CC                    |                                     |       |                                        |

| HD                    | Hold                                | SU    | Setup                                  |

| ST                    |                                     |       |                                        |

| DAT                   | DATA input hold                     | STO   | STOP condition                         |

| STA                   | START condition                     |       |                                        |

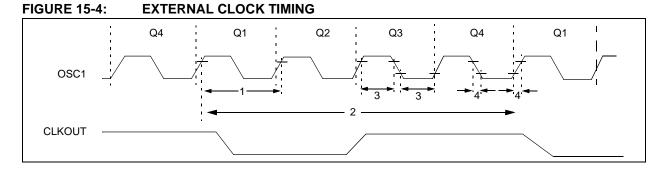

#### TABLE 15-1: EXTERNAL CLOCK TIMING REQUIREMENTS

| Parameter<br>No. | Symbol | Characteristic                     | Min  | Тур† | Max    | Units | Conditions    |

|------------------|--------|------------------------------------|------|------|--------|-------|---------------|

|                  | Fosc   | External CLKIN Frequency           | DC   |      | 1      | MHz   | XT osc mode   |

|                  |        | (Note 1)                           | DC   | —    | 20     | MHz   | HS osc mode   |

|                  |        |                                    | DC   | _    | 32     | kHz   | LP osc mode   |

|                  |        | Oscillator Frequency               | DC   | _    | 4      | MHz   | RC osc mode   |

|                  |        | (Note 1)                           | 0.1  | _    | 4      | MHz   | XT osc mode   |

|                  |        |                                    | 4    | —    | 20     | MHz   | HS osc mode   |

|                  |        |                                    | 5    | _    | 200    | kHz   | LP osc mode   |

| 1                | Tosc   | External CLKIN Period              | 1000 | _    | _      | ns    | XT osc mode   |

|                  |        | (Note 1)                           | 50   | —    |        | ns    | HS osc mode   |

|                  |        |                                    | 5    | —    |        | ms    | LP osc mode   |

|                  |        | Oscillator Period                  | 250  | _    | —      | ns    | RC osc mode   |

|                  |        | (Note 1)                           | 250  | —    | 10,000 | ns    | XT osc mode   |

|                  |        |                                    | 50   | —    | 250    | ns    | HS osc mode   |

|                  |        |                                    | 5    | —    |        | ms    | LP osc mode   |

| 2                | Тсү    | Instruction Cycle Time<br>(Note 1) | 200  | Тсү  | DC     | ns    | Tcy = 4/Fosc  |

| 3                | TosL,  | External Clock in (OSC1)           | 500  |      |        | ns    | XT oscillator |

|                  | TosH   | High or Low Time                   | 2.5  | —    | —      | ms    | LP oscillator |

|                  |        |                                    | 15   | —    | —      | ns    | HS oscillator |

| 4                | TosR,  | External Clock in (OSC1)           | —    | —    | 25     | ns    | XT oscillator |

|                  | TosF   | Rise or Fall Time                  | —    | —    | 50     | ns    | LP oscillator |

|                  |        |                                    | —    | —    | 15     | ns    | HS oscillator |

† Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

**Note 1:** Instruction cycle period (TcY) equals four times the input oscillator time-base period. All specified values are based on characterization data for that particular oscillator type under standard operating conditions, with the device executing code. Exceeding these specified limits may result in an unstable oscillator operation and/or higher than expected current consumption. All devices are tested to operate at "min." values with an external clock applied to the OSC1/CLKIN pin. When an external clock input is used, the "max." cycle time limit is "DC" (no clock) for all devices.

#### TABLE 15-6: PARALLEL SLAVE PORT REQUIREMENTS (PIC16F74/77 DEVICES ONLY)

| Parameter<br>No. | Symbol   | Characteristic                                                            |                                               |          | Тур† | Max      | Units    | Conditions          |

|------------------|----------|---------------------------------------------------------------------------|-----------------------------------------------|----------|------|----------|----------|---------------------|

| 62               | TdtV2wrH | Data in valid before WR↑ or CS1                                           | `(setup time)                                 | 20<br>25 | _    | _        | ns<br>ns | Extended range only |

| 63*              | TwrH2dtl | ₩R↑ or CS↑ to data in invalid<br>(hold time)                              | Standard( <b>F</b> )<br>Extended( <b>LF</b> ) | 20<br>35 |      |          | ns<br>ns |                     |

| 64               | TrdL2dtV | $\overline{RD}\downarrow$ and $\overline{CS}\downarrow$ to data out valid |                                               |          |      | 80<br>90 | ns<br>ns | Extended range only |

| 65               | TrdH2dtl | $\overline{RD}$ or $\overline{CS}$ to data out invalid                    |                                               | 10       | —    | 30       | ns       |                     |

\* These parameters are characterized but not tested.

† Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

| Param.<br>No. | Symbol Characteristic |                        | eristic      | Min        | Max  | Units | Conditions                                  |

|---------------|-----------------------|------------------------|--------------|------------|------|-------|---------------------------------------------|

| 100*          | Тнідн                 | Clock high time        | 100 kHz mode | 4.0        |      | μs    | Device must operate at a minimum of 1.5 MHz |

|               |                       |                        | 400 kHz mode | 0.6        |      | μs    | Device must operate at a minimum of 10 MHz  |

|               |                       |                        | SSP Module   | 1.5Tcy     |      |       |                                             |

| 101*          | 101* TLOW             | Clock low time         | 100 kHz mode | 4.7        |      | μs    | Device must operate at a minimum of 1.5 MHz |

|               |                       |                        | 400 kHz mode | 1.3        |      | μs    | Device must operate at a minimum of 10 MHz  |

|               |                       |                        | SSP Module   | 1.5Tcy     | _    |       |                                             |

| 102*          | Tr                    | SDA and SCL rise       | 100 kHz mode | —          | 1000 | ns    |                                             |

|               |                       | time                   | 400 kHz mode | 20 + 0.1Св | 300  | ns    | CB is specified to be from 10 - 400 pF      |

| 103*          | TF                    | SDA and SCL fall       | 100 kHz mode | —          | 300  | ns    |                                             |

|               |                       | time                   | 400 kHz mode | 20 + 0.1Св | 300  | ns    | CB is specified to be from 10 - 400 pF      |

| 90*           | TSU:STA               | START condition        | 100 kHz mode | 4.7        |      |       | Only relevant for                           |

|               |                       | setup time             | 400 kHz mode | 0.6        |      | μs    | Repeated START condition                    |

| 91*           | THD:STA               | START condition        | 100 kHz mode | 4.0        | _    | μs    | After this period the first                 |

|               |                       | hold time              | 400 kHz mode | 0.6        | _    | μs    | clock pulse is generated                    |

| 106*          | THD:DAT               | Data input hold time   | 100 kHz mode | 0          | —    | ns    |                                             |

|               |                       |                        | 400 kHz mode | 0          | 0.9  | μs    |                                             |

| 107*          | TSU:DAT               | Data input setup       | 100 kHz mode | 250        | —    | ns    | (Note 2)                                    |

|               |                       | time                   | 400 kHz mode | 100        | _    | ns    |                                             |

| 92*           | Tsu:sto               | STOP condition         | 100 kHz mode | 4.7        | _    | μs    | -                                           |

|               |                       | setup time             | 400 kHz mode | 0.6        | _    | μs    |                                             |

| 109*          | ΤΑΑ                   | Output valid from      | 100 kHz mode | —          | 3500 | ns    | (Note 1)                                    |

|               |                       | clock                  | 400 kHz mode | —          |      | ns    |                                             |

| 110*          | TBUF                  | Bus free time          | 100 kHz mode | 4.7        | _    | μs    | Time the bus must be free                   |

|               |                       |                        | 400 kHz mode | 1.3        | _    | μs    | before a new transmission<br>can start      |

|               | Св                    | Bus capacitive loading | ng           | -          | 400  | pF    |                                             |

#### TABLE 15-9: I<sup>2</sup>C BUS DATA REQUIREMENTS

\* These parameters are characterized but not tested.

**Note 1:** As a transmitter, the device must provide this internal minimum delay time to bridge the undefined region (min. 300 ns) of the falling edge of SCL to avoid unintended generation of START or STOP conditions.

2: A Fast mode (400 kHz) I<sup>2</sup>C bus device can be used in a Standard mode (100 kHz) I<sup>2</sup>C bus system, but the requirement TsU:DAT ≥ 250 ns must then be met. This will automatically be the case if the device does not stretch the LOW period of the SCL signal. If such a device does stretch the LOW period of the SCL signal, it must output the next data bit to the SDA line TR max. + TSU:DAT = 1000 + 250 = 1250 ns (according to the Standard mode I<sup>2</sup>C bus specification), before the SCL line is released.

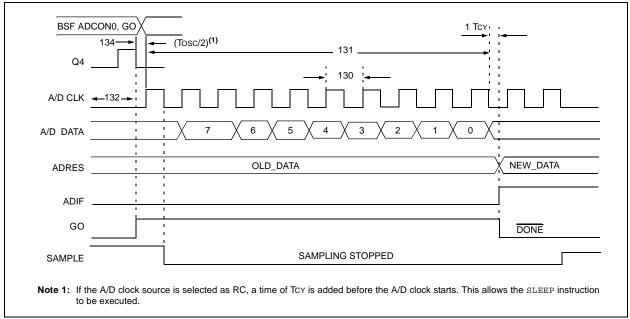

#### TABLE 15-13: A/D CONVERSION REQUIREMENTS

| Param<br>No. | Sym  | Characteristic                                       |           | Min | Тур†   | Мах | Units | Conditions                                                                                                                                                                                                                       |

|--------------|------|------------------------------------------------------|-----------|-----|--------|-----|-------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 130          | Tad  | A/D clock period PIC16F7X                            |           | 1.6 |        |     | μs    | Tosc based, VREF $\geq 3.0V$                                                                                                                                                                                                     |

|              |      |                                                      | PIC16LF7X | 2.0 | _      | _   | μs    | Tosc based, $2.0V \le VREF \le 5.5V$                                                                                                                                                                                             |

|              |      |                                                      | PIC16F7X  | 2.0 | 4.0    | 6.0 | μs    | A/D RC mode                                                                                                                                                                                                                      |

|              |      |                                                      | PIC16LF7X | 3.0 | 6.0    | 9.0 | μs    | A/D RC mode                                                                                                                                                                                                                      |

| 131          | Тслу | Conversion time (not in<br>S/H time) <b>(Note 1)</b> | 9         |     | 9      | Tad |       |                                                                                                                                                                                                                                  |

| 132          | TACQ | Acquisition time                                     |           | 5*  | _      |     | μs    | The minimum time is the<br>amplifier settling time. This<br>may be used if the "new" input<br>voltage has not changed by<br>more than 1 LSb (i.e.,<br>20.0 mV @ 5.12V) from the<br>last sampled voltage (as<br>stated on CHOLD). |

| 134          | TGO  | Q4 to A/D clock start                                |           |     | Tosc/2 |     |       | If the A/D clock source is selected as RC, a time of TCY is added before the A/D clock starts. This allows the SLEEP instruction to be executed.                                                                                 |

\* These parameters are characterized but not tested.

† Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

**Note 1:** ADRES register may be read on the following TCY cycle.

2: See Section 11.1 for minimum conditions.

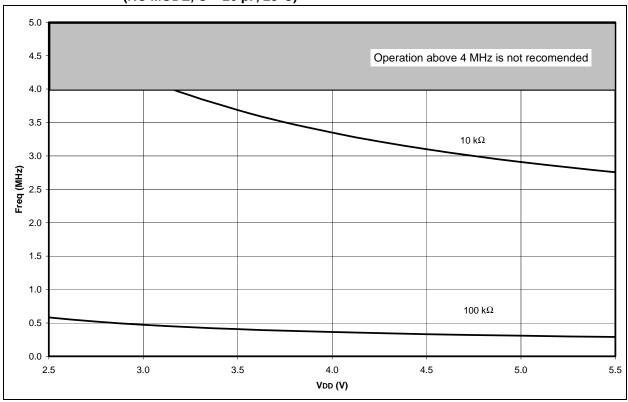

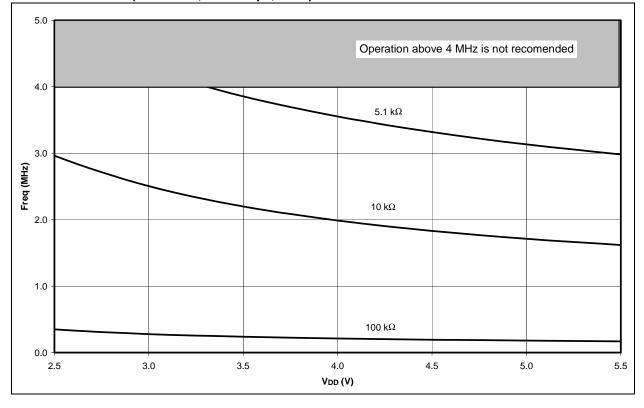

#### FIGURE 16-7: AVERAGE FOSC vs. VDD FOR VARIOUS VALUES OF R (RC MODE, C = 20 pF, 25°C)

FIGURE 16-8: AVERAGE Fosc vs. VDD FOR VARIOUS VALUES OF R (RC MODE, C = 100 pF, 25°C)

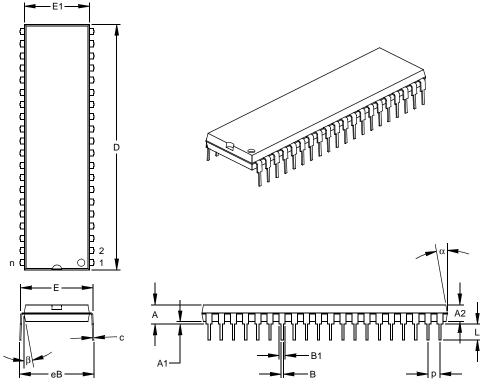

## 40-Lead Plastic Dual In-line (P) - 600 mil (PDIP)

| Units            |                                                                                     | INCHES*                                                                                                                                                                                                                                                                                                                                                       |                                                        | MILLIMETERS                                            |                                                        |                                                        |  |

|------------------|-------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------|--------------------------------------------------------|--------------------------------------------------------|--------------------------------------------------------|--|

| Dimension Limits |                                                                                     |                                                                                                                                                                                                                                                                                                                                                               |                                                        | MIN                                                    | NOM                                                    | MAX                                                    |  |

| n                |                                                                                     | 40                                                                                                                                                                                                                                                                                                                                                            |                                                        |                                                        | 40                                                     |                                                        |  |

| р                |                                                                                     | .100                                                                                                                                                                                                                                                                                                                                                          |                                                        |                                                        | 2.54                                                   |                                                        |  |