Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                        |

|----------------------------|------------------------------------------------------------------------|

| Product Status             | Active                                                                 |

| Core Processor             | PIC                                                                    |

| Core Size                  | 8-Bit                                                                  |

| Speed                      | 20MHz                                                                  |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                                      |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                  |

| Number of I/O              | 33                                                                     |

| Program Memory Size        | 14KB (8K x 14)                                                         |

| Program Memory Type        | FLASH                                                                  |

| EEPROM Size                | -                                                                      |

| RAM Size                   | 368 x 8                                                                |

| Voltage - Supply (Vcc/Vdd) | 4V ~ 5.5V                                                              |

| Data Converters            | A/D 8x8b                                                               |

| Oscillator Type            | External                                                               |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                      |

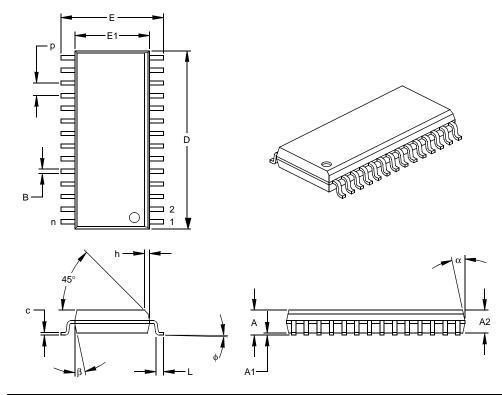

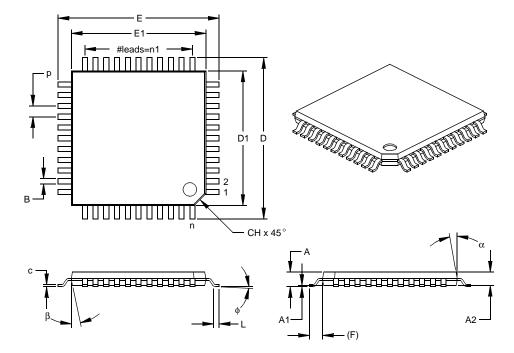

| Mounting Type              | Surface Mount                                                          |

| Package / Case             | 44-LCC (J-Lead)                                                        |

| Supplier Device Package    | 44-PLCC (16.59x16.59)                                                  |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16f77-i-l |

|                            |                                                                        |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### TABLE 1-3:PIC16F74 AND PIC16F77 PINOUT DESCRIPTION

| OSC1/CLKI<br>OSC1<br>CLKI<br>OSC2/CLKO<br>OSC2<br>CLKO<br>MCLR/VPP<br>MCLR<br>VPP | 13 | 14<br>15 | 30<br>31 | 1        | ST/CMOS <sup>(4)</sup> | Oscillator crystal or external clock input.<br>Oscillator crystal input or external clock source input.<br>ST buffer when configured in RC mode. Otherwise<br>CMOS.<br>External clock source input. Always associated with pin |

|-----------------------------------------------------------------------------------|----|----------|----------|----------|------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| CLKI<br>OSC2/CLKO<br>OSC2<br>CLKO<br><u>MCLR/VPP</u><br>MCLR                      | 14 | 15       | 31       | I        |                        | Oscillator crystal input or external clock source input.<br>ST buffer when configured in RC mode. Otherwise<br>CMOS.<br>External clock source input. Always associated with pin                                                |

| OSC2/CLKO<br>OSC2<br>CLKO<br>MCLR/VPP<br>MCLR                                     | 14 | 15       | 31       |          |                        | CMOS.<br>External clock source input. Always associated with pin                                                                                                                                                               |

| OSC2/CLKO<br>OSC2<br>CLKO<br>MCLR/VPP<br>MCLR                                     | 14 | 15       | 31       |          |                        | External clock source input. Always associated with pin                                                                                                                                                                        |

| OSC2<br>CLKO<br>MCLR/VPP<br>MCLR                                                  | 14 | 15       | 31       |          |                        |                                                                                                                                                                                                                                |

| OSC2<br>CLKO<br>MCLR/VPP<br>MCLR                                                  | 14 | 15       | 31       | 0        |                        | function OSC1 (see OSC1/CLKI, OSC2/CLKO pins).                                                                                                                                                                                 |

| CLKO<br>MCLR/VPP<br>MCLR                                                          |    |          |          | <u> </u> | I —                    | Oscillator crystal or clock output.                                                                                                                                                                                            |

| MCLR/Vpp<br>MCLR                                                                  |    |          |          | 0        |                        | Oscillator crystal output.                                                                                                                                                                                                     |

| MCLR/Vpp<br>MCLR                                                                  |    |          |          |          |                        | Connects to crystal or resonator in Crystal Oscillator                                                                                                                                                                         |

| MCLR/Vpp<br>MCLR                                                                  |    |          |          |          |                        | mode.                                                                                                                                                                                                                          |

| MCLR                                                                              |    |          |          | 0        |                        | In RC mode, OSC2 pin outputs CLKO, which has 1/4                                                                                                                                                                               |

| MCLR                                                                              |    |          |          |          |                        | the frequency of OSC1 and denotes the instruction                                                                                                                                                                              |

| MCLR                                                                              |    |          |          |          |                        | cycle rate.                                                                                                                                                                                                                    |

|                                                                                   | 1  | 2        | 18       |          | ST                     | Master Clear (input) or programming voltage (output).                                                                                                                                                                          |

| Vpp                                                                               |    |          |          | I        |                        | Master Clear (Reset) input. This pin is an active low                                                                                                                                                                          |

| VPP                                                                               |    |          |          |          |                        | RESET to the device.                                                                                                                                                                                                           |

|                                                                                   |    |          |          | Р        |                        | Programming voltage input.                                                                                                                                                                                                     |

|                                                                                   |    |          |          |          |                        | PORTA is a bi-directional I/O port.                                                                                                                                                                                            |

| RA0/AN0                                                                           | 2  | 3        | 19       |          | TTL                    |                                                                                                                                                                                                                                |

| RA0                                                                               |    |          |          | I/O      |                        | Digital I/O.                                                                                                                                                                                                                   |

| AN0                                                                               |    |          |          | I        |                        | Analog input 0.                                                                                                                                                                                                                |

| RA1/AN1                                                                           | 3  | 4        | 20       |          | TTL                    |                                                                                                                                                                                                                                |

| RA1                                                                               |    |          |          | I/O      |                        | Digital I/O.                                                                                                                                                                                                                   |

| AN1                                                                               |    |          |          | I        |                        | Analog input 1.                                                                                                                                                                                                                |

| RA2/AN2                                                                           | 4  | 5        | 21       |          | TTL                    |                                                                                                                                                                                                                                |

| RA2                                                                               |    |          |          | I/O      |                        | Digital I/O.                                                                                                                                                                                                                   |

| AN2                                                                               |    |          |          | I        |                        | Analog input 2.                                                                                                                                                                                                                |

| RA3/AN3/Vref                                                                      | 5  | 6        | 22       |          | TTL                    |                                                                                                                                                                                                                                |

| RA3                                                                               |    |          |          | I/O      |                        | Digital I/O.                                                                                                                                                                                                                   |

| AN3                                                                               |    |          |          | I        |                        | Analog input 3.                                                                                                                                                                                                                |

| VREF                                                                              |    |          |          | I        |                        | A/D reference voltage input.                                                                                                                                                                                                   |

| RA4/T0CKI                                                                         | 6  | 7        | 23       |          | ST                     |                                                                                                                                                                                                                                |

| RA4                                                                               |    |          |          | I/O      |                        | Digital I/O – Open drain when configured as output.                                                                                                                                                                            |

| TOCKI                                                                             |    |          |          | I        |                        | Timer0 external clock input.                                                                                                                                                                                                   |

| RA5/SS/AN4                                                                        | 7  | 8        | 24       |          | TTL                    |                                                                                                                                                                                                                                |

| RA5                                                                               |    | -        |          | I/O      |                        | Digital I/O.                                                                                                                                                                                                                   |

| SS                                                                                | 1  |          |          | 1        |                        | SPI slave select input.                                                                                                                                                                                                        |

| AN4                                                                               |    |          |          |          | 1                      |                                                                                                                                                                                                                                |

| Legend: I = inpu                                                                  |    | 1        |          |          |                        | Analog input 4.                                                                                                                                                                                                                |

— = Not used TTL = TTL input ST = Schmitt Trigger input

**Note 1:** This buffer is a Schmitt Trigger input when configured as an external interrupt.

2: This buffer is a Schmitt Trigger input when used in Serial Programming mode.

**3:** This buffer is a Schmitt Trigger input when configured as general purpose I/O and a TTL input when used in the Parallel Slave Port mode (for interfacing to a microprocessor bus).

4: This buffer is a Schmitt Trigger input when configured in RC Oscillator mode and a CMOS input otherwise.

# PIC16F7X

| FIGL | JRE | 2-3: |

|------|-----|------|

|      |     |      |

## PIC16F74/73 REGISTER FILE MAP

| ŀ                                                                      | File<br>Address |                                           | File<br>Address |                           | File<br>Address | ļ                 | File<br>Addre |

|------------------------------------------------------------------------|-----------------|-------------------------------------------|-----------------|---------------------------|-----------------|-------------------|---------------|

| Indirect addr.(*)                                                      | 00h             | Indirect addr.(*)                         | 80h             | Indirect addr.(*)         | 100h            | Indirect addr.(*) | 180           |

| TMR0                                                                   | 01h             | OPTION_REG                                | 81h             | TMR0                      | 101h            | OPTION_REG        | 181           |

| PCL                                                                    | 02h             | PCL                                       | 82h             | PCL                       | 102h            | PCL               | 182           |

| STATUS                                                                 | 03h             | STATUS                                    | 83h             | STATUS                    | 103h            | STATUS            | 183           |

| FSR                                                                    | 04h             | FSR                                       | 84h             | FSR                       | 104h            | FSR               | 184           |

| PORTA                                                                  | 05h             | TRISA                                     | 85h             |                           | 105h            |                   | 185           |

| PORTB                                                                  | 06h             | TRISB                                     | 86h             | PORTB                     | 106h            | TRISB             | 186           |

| PORTC                                                                  | 07h             | TRISC                                     | 87h             |                           | 107h            |                   | 187           |

| PORTD <sup>(1)</sup>                                                   | 08h             | TRISD <sup>(1)</sup>                      | 88h             |                           | 108h            |                   | 188           |

| PORTE <sup>(1)</sup>                                                   | 09h             | TRISE <sup>(1)</sup>                      | 89h             |                           | 109h            |                   | 189           |

| PCLATH                                                                 | 0Ah             | PCLATH                                    | 8Ah             | PCLATH                    | 10Ah            | PCLATH            | 18A           |

| INTCON                                                                 | 0Bh             | INTCON                                    | 8Bh             | INTCON                    | 10Bh            | INTCON            | 18E           |

| PIR1                                                                   | 0Ch             | PIE1                                      | 8Ch             | PMDATA                    | 10Ch            | PMCON1            | 180           |

| PIR2                                                                   | 0Dh             | PIE2                                      | 8Dh             | PMADR                     | 10Dh            |                   | 180           |

| TMR1L                                                                  | 0Eh             | PCON                                      | 8Eh             | PMDATH                    | 10Eh            |                   | 18E           |

| TMR1H                                                                  | 0Fh             |                                           | 8Fh             | PMADRH                    | 10Fh            |                   | 18F           |

| T1CON                                                                  | 10h             |                                           | 90h             |                           | 110h            |                   | 190           |

| TMR2                                                                   | 11h             |                                           | 91h             |                           |                 |                   |               |

| T2CON                                                                  | 12h             | PR2                                       | 92h             |                           |                 |                   |               |

| SSPBUF                                                                 | 13h             | SSPADD                                    | 93h             |                           |                 |                   |               |

| SSPCON                                                                 | 14h             | SSPSTAT                                   | 94h             |                           |                 |                   |               |

| CCPR1L                                                                 | 15h             |                                           | 95h             |                           |                 |                   |               |

| CCPR1H                                                                 | 16h             |                                           | 96h             |                           |                 |                   |               |

| CCP1CON                                                                | 17h             |                                           | 97h             |                           |                 |                   |               |

| RCSTA                                                                  | 18h             | TXSTA                                     | 98h             |                           |                 |                   |               |

| TXREG                                                                  | 19h             | SPBRG                                     | 99h             |                           |                 |                   |               |

| RCREG                                                                  | 1Ah             |                                           | 9Ah             |                           |                 |                   |               |

| CCPR2L                                                                 | 1Bh             |                                           | 9Bh             |                           |                 |                   |               |

| CCPR2H                                                                 | 1Ch             |                                           | 9Ch             |                           |                 |                   |               |

| CCP2CON                                                                | 1Dh             |                                           | 9Dh             |                           |                 |                   |               |

| ADRES                                                                  | 1Eh             |                                           | 9Eh             |                           |                 |                   |               |

| ADCON0                                                                 | 1Fh             | ADCON1                                    | 9Fh             |                           | 1001            |                   | 4.4.0         |

|                                                                        | 20h             |                                           | A0h             |                           | 120h            |                   | 1A0           |

|                                                                        |                 |                                           | 7,011           |                           |                 |                   |               |

| General                                                                |                 | General                                   |                 |                           |                 |                   |               |

|                                                                        |                 | Purpose<br>Register                       |                 | accesses                  |                 | accesses          |               |

| -                                                                      |                 | -                                         |                 | 20h-7Fh                   |                 | A0h - FFh         | 4             |

| 96 Bytes                                                               |                 | 96 Bytes                                  |                 |                           | 16Fh<br>170b    |                   | 1EF<br>1FC    |

|                                                                        |                 |                                           |                 |                           | 17011           |                   |               |

| Bank 0                                                                 | 7Fh             | Bank 1                                    | FFh             | Bank 2                    | 17Fh            | Bank 3            | 1FF           |

| Purpose<br>Register<br>96 Bytes<br>Bank 0<br>Unimpleme<br>* Not a phys | ented data      | Purpose<br>Register<br>96 Bytes<br>Bank 1 | s, read as      | 20h-7Fh<br>Bank 2<br>'0'. | 170h            | A0h - FFh         |               |

| <b>TABLE 2-1:</b> | SPECIAL FUNCTION REGISTER SUMMARY | (CONTINUED) |

|-------------------|-----------------------------------|-------------|

|-------------------|-----------------------------------|-------------|

| Address               | Name       | Bit 7                          | Bit 6                  | Bit 5         | Bit 4                                                      | Bit 3         | Bit 2         | Bit 1         | Bit 0        | Value on:<br>POR,<br>BOR | Details<br>on page |

|-----------------------|------------|--------------------------------|------------------------|---------------|------------------------------------------------------------|---------------|---------------|---------------|--------------|--------------------------|--------------------|

| Bank 2                |            |                                |                        |               |                                                            |               |               |               |              |                          |                    |

| 100h <sup>(4)</sup>   | INDF       | Addressin                      | g this locatio         | n uses conte  | ents of FSR to                                             | address data  | a memory (r   | not a physica | al register) | 0000 0000                | 27, 96             |

| 101h                  | TMR0       | Timer0 Mo                      | dule Registe           | er            |                                                            |               |               |               |              | xxxx xxxx                | 45, 96             |

| 102h <sup>(4)</sup>   | PCL        | Program C                      | Counter (PC)           | Least Signif  | icant Byte                                                 |               |               |               |              | 0000 0000                | 26, 96             |

| 103h <b>(4)</b>       | STATUS     | IRP                            | RP1                    | RP0           | ТО                                                         | 0001 1xxx     | 19, 96        |               |              |                          |                    |

| 104h <sup>(4)</sup>   | FSR        | Indirect Da                    | ata Memory /           |               | xxxx xxxx                                                  | 27, 96        |               |               |              |                          |                    |

| 105h                  | —          | Unimplem                       | ented                  |               |                                                            |               |               |               |              | _                        | —                  |

| 106h                  | PORTB      | PORTB D                        | ata Latch wh           | en written: F | ORTB pins w                                                | hen read      |               |               |              | xxxx xxxx                | 34, 96             |

| 107h                  | _          | Unimplem                       | ented                  |               |                                                            |               |               |               |              | —                        | —                  |

| 108h                  | —          | Unimplem                       | ented                  |               |                                                            |               |               |               |              | —                        | —                  |

| 109h                  | —          | Unimplem                       | ented                  |               |                                                            |               |               |               |              | _                        | —                  |

| 10Ah <sup>(1,4)</sup> | PCLATH     | —                              | _                      | _             | — Write Buffer for the upper 5 bits of the Program Counter |               |               |               |              |                          | 21, 96             |

| 10Bh <sup>(4)</sup>   | INTCON     | GIE                            | PEIE                   | TMR0IE        | INTE                                                       | RBIE          | TMR0IF        | INTF          | RBIF         | 0000 000x                | 23, 96             |

| 10Ch                  | PMDATA     | Data Regi                      | Data Register Low Byte |               |                                                            |               |               |               |              |                          |                    |

| 10Dh                  | PMADR      | Address Register Low Byte      |                        |               |                                                            |               |               |               |              | xxxx xxxx                | 29, 97             |

| 10Eh                  | PMDATH     | — — Data Register High Byte    |                        |               |                                                            |               |               |               |              | xxxx xxxx                | 29, 97             |

| 10Fh                  | PMADRH     | — — Address Register High Byte |                        |               |                                                            |               |               |               |              | XXXX XXXX                | 29, 97             |

| Bank 3                |            |                                |                        |               |                                                            |               |               |               |              |                          |                    |

| 180h <sup>(4)</sup>   | INDF       | Addressin                      | g this locatio         | n uses conte  | ents of FSR to                                             | address data  | a memory (r   | not a physica | al register) | 0000 0000                | 27, 96             |

| 181h                  | OPTION_REG | RBPU                           | INTEDG                 | TOCS          | TOSE                                                       | PSA           | PS2           | PS1           | PS0          | 1111 1111                | 20, 44, 96         |

| 182h <sup>(4)</sup>   | PCL        | Program C                      | Counter (PC)           | Least Signif  | icant Byte                                                 |               |               |               |              | 0000 0000                | 26, 96             |

| 183h <sup>(4)</sup>   | STATUS     | IRP                            | RP1                    | RP0           | TO                                                         | PD            | Z             | DC            | С            | 0001 1xxx                | 19, 96             |

| 184h <sup>(4)</sup>   | FSR        | Indirect Da                    | ata Memory /           | Address Poir  | nter                                                       |               |               |               |              | xxxx xxxx                | 27, 96             |

| 185h                  | —          | Unimplem                       | ented                  |               |                                                            |               |               |               |              | _                        | _                  |

| 186h                  | TRISB      | PORTB D                        | ata Direction          | Register      |                                                            |               |               |               |              | 1111 1111                | 34, 96             |

| 187h                  | —          | Unimplem                       | ented                  |               |                                                            |               |               |               |              | _                        | _                  |

| 188h                  | —          | Unimplem                       | ented                  |               |                                                            |               |               |               |              | _                        | _                  |

| 189h                  | —          | Unimplem                       | ented                  |               |                                                            |               |               |               |              | _                        | _                  |

| 18Ah <sup>(1,4)</sup> | PCLATH     | _                              |                        | _             | Write Buffer                                               | for the upper | 5 bits of the | Program C     | ounter       | 0 0000                   | 21, 96             |

| 18Bh <sup>(4)</sup>   | INTCON     | GIE                            | PEIE                   | TMR0IE        | INTE                                                       | RBIE          | TMR0IF        | INTF          | RBIF         | 0000 000x                | 23, 96             |

| 18Ch                  | PMCON1     | (6)                            | _                      | —             | —                                                          | _             | _             | —             | RD           | 10                       | 29, 97             |

| 18Dh                  | —          | Unimplem                       | ented                  |               |                                                            |               |               |               |              | _                        |                    |

| 18Eh                  | —          | Reserved                       | maintain clea          | ar            |                                                            |               |               |               |              | 0000 0000                |                    |

| 18Fh                  | _          | Reserved                       | maintain clea          | ar            |                                                            |               |               |               |              | 0000 0000                |                    |

Legend: x = unknown, u = unchanged, q = value depends on condition, - = unimplemented, read as '0', r = reserved. Shaded locations are unimplemented, read as '0'.

**Note** 1: The upper byte of the program counter is not directly accessible. PCLATH is a holding register for the PC<12:8>, whose contents are transferred to the upper byte of the program counter during branches (CALL or GOTO).

2: Other (non power-up) RESETS include external RESET through MCLR and Watchdog Timer Reset.

3: Bits PSPIE and PSPIF are reserved on the 28-pin devices; always maintain these bits clear.

4: These registers can be addressed from any bank.

5: PORTD, PORTE, TRISD, and TRISE are not physically implemented on the 28-pin devices, read as '0'.

6: This bit always reads as a '1'.

#### 2.2.2.1 STATUS Register

The STATUS register contains the arithmetic status of the ALU, the RESET status and the bank select bits for data memory.

The STATUS register can be the destination for any instruction, as with any other register. If the STATUS register is the destination for an instruction that affects the Z, DC, or C bits, then the write to these three bits is disabled. These bits are set or cleared according to the device logic. Furthermore, the TO and PD bits are not writable, therefore, the result of an instruction with the STATUS register as destination may be different than intended.

For example, CLRF STATUS will clear the upper three bits and set the Z bit. This leaves the STATUS register as  $000u \ u1uu$  (where u = unchanged).

It is recommended, therefore, that only BCF, BSF, SWAPF and MOVWF instructions are used to alter the STATUS register, because these instructions do not affect the Z, C, or DC bits from the STATUS register. For other instructions not affecting any status bits, see the "Instruction Set Summary."

Note 1: The <u>C</u> and <u>DC</u> bits operate as a borrow and digit borrow bit, respectively, in subtraction. See the <u>SUBLW</u> and <u>SUBWF</u> instructions for examples.

#### REGISTER 2-1: STATUS REGISTER (ADDRESS 03h, 83h, 103h, 183h)

|         | R/W-0                               | R/W-0                                                                                                                                  | R/W-0         | R-1            | R-1           | R/W-x        | R/W-x       | R/W-x |  |  |  |  |  |  |

|---------|-------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------|---------------|----------------|---------------|--------------|-------------|-------|--|--|--|--|--|--|

|         | IRP                                 | RP1                                                                                                                                    | RP0           | TO             | PD            | Z            | DC          | С     |  |  |  |  |  |  |

|         | bit 7                               |                                                                                                                                        |               |                |               |              |             | bit 0 |  |  |  |  |  |  |

| bit 7   | 1 = Bank 2                          | ter Bank Sele<br>2, 3 (100h - 1F                                                                                                       | Fh)           | or indirect ac | ldressing)    |              |             |       |  |  |  |  |  |  |

|         |                                     | = Bank 0, 1 (00h - FFh)                                                                                                                |               |                |               |              |             |       |  |  |  |  |  |  |

| bit 6-5 |                                     | RP1:RP0: Register Bank Select bits (used for direct addressing)                                                                        |               |                |               |              |             |       |  |  |  |  |  |  |

|         | 10 = Bank<br>01 = Bank<br>00 = Bank | L1 = Bank 3 (180h - 1FFh)<br>L0 = Bank 2 (100h - 17Fh)<br>D1 = Bank 1 (80h - FFh)<br>D0 = Bank 0 (00h - 7Fh)<br>Each bank is 128 bytes |               |                |               |              |             |       |  |  |  |  |  |  |

| bit 4   | TO: Time-c                          | out bit                                                                                                                                |               |                |               |              |             |       |  |  |  |  |  |  |

|         |                                     | ower-up, CLR<br>time-out occ                                                                                                           |               | on, or SLEEP   | o instruction |              |             |       |  |  |  |  |  |  |

| bit 3   | PD: Power                           | -down bit                                                                                                                              |               |                |               |              |             |       |  |  |  |  |  |  |

|         |                                     | ower-up or by<br>cution of the                                                                                                         |               |                |               |              |             |       |  |  |  |  |  |  |

| bit 2   | z: Zero bit                         |                                                                                                                                        |               |                |               |              |             |       |  |  |  |  |  |  |

|         |                                     | sult of an arith<br>sult of an arith                                                                                                   |               |                |               |              |             |       |  |  |  |  |  |  |

| bit 1   | DC: Digit c                         | arry/borrow b                                                                                                                          | it (addwf, ae | DLW, SUBL      | W, SUBWF      | instructions | 5)          |       |  |  |  |  |  |  |

|         | •                                   | r-out from the<br>ry-out from th                                                                                                       |               |                |               | d            |             |       |  |  |  |  |  |  |

| bit 0   | C: Carry/b                          | orrow bit (ADI                                                                                                                         | WF, ADDLW     | , SUBLW, S     | SUBWF instr   | uctions)     |             |       |  |  |  |  |  |  |

|         |                                     | -out from the<br>ry-out from th                                                                                                        |               |                |               |              |             |       |  |  |  |  |  |  |

|         | Note:                               | For borrow, t<br>complement<br>loaded with e                                                                                           | of the secon  | d operand. F   | or rotate (R  | RF, RLF)     | instruction |       |  |  |  |  |  |  |

|         | Legend:                             |                                                                                                                                        |               |                |               |              |             |       |  |  |  |  |  |  |

| Legend:                                    |                  |                      |                    |

|--------------------------------------------|------------------|----------------------|--------------------|

| R = Readable bit                           | W = Writable bit | U = Unimplemented    | bit, read as '0'   |

| <ul> <li>n = Value at POR reset</li> </ul> | '1' = Bit is set | '0' = Bit is cleared | x = Bit is unknown |

#### 3.3 Reading the FLASH Program Memory

A program memory location may be read by writing two bytes of the address to the PMADR and PMADRH registers and then setting control bit RD (PMCON1<0>). Once the read control bit is set, the microcontroller will use the next two instruction cycles to read the data. The data is available in the PMDATA and PMDATH registers after the second NOP instruction. Therefore, it can be read as two bytes in the following instructions. The PMDATA and PMDATH registers will hold this value until the next read operation.

## 3.4 Operation During Code Protect

FLASH program memory has its own code protect mechanism. External Read and Write operations by programmers are disabled if this mechanism is enabled.

The microcontroller can read and execute instructions out of the internal FLASH program memory, regardless of the state of the code protect configuration bits.

|                      | BSF               | STATUS, RP1 | ;                                                                                          |

|----------------------|-------------------|-------------|--------------------------------------------------------------------------------------------|

|                      | BCF               | STATUS, RP0 | ; Bank 2                                                                                   |

|                      | MOVF              | ADDRH, W    | ;                                                                                          |

|                      | MOVWF             | PMADRH      | ; MSByte of Program Address to read                                                        |

|                      | MOVF              | ADDRL, W    | ;                                                                                          |

|                      | MOVWF             | PMADR       | ; LSByte of Program Address to read                                                        |

|                      | BSF               | STATUS, RP0 | ; Bank 3 Required                                                                          |

| Required<br>Sequence | BSF<br>NOP<br>NOP | PMCON1, RD  | ; EEPROM Read Sequence<br>; memory is read in the next two cycles after BSF PMCON1,RD<br>; |

|                      | BCF               | STATUS, RPO | ; Bank 2                                                                                   |

|                      | MOVF              | PMDATA, W   | ; W = LSByte of Program PMDATA                                                             |

|                      | MOVF              | PMDATH, W   | ; W = MSByte of Program PMDATA                                                             |

#### EXAMPLE 3-1: FLASH PROGRAM READ

#### TABLE 3-1: REGISTERS ASSOCIATED WITH PROGRAM FLASH

| Address | Name   | Bit 7     | Bit 6                     | Bit 5    | Bit 4                      | Bit 3 | Bit 2 | Bit 1 | Bit 0 | Value on:<br>POR,<br>BOR | Value on<br>all other<br>RESETS |

|---------|--------|-----------|---------------------------|----------|----------------------------|-------|-------|-------|-------|--------------------------|---------------------------------|

| 10Dh    | PMADR  | Address F | Address Register Low Byte |          |                            |       |       |       |       |                          | uuuu uuuu                       |

| 10Fh    | PMADRH | _         | _                         | _        | Address Register High Byte |       |       |       |       |                          | uuuu uuuu                       |

| 10Ch    | PMDATA | Data Reg  | Data Register Low Byte    |          |                            |       |       |       |       | xxxx xxxx                | uuuu uuuu                       |

| 10Eh    | PMDATH | _         | _                         | Data Reg | Pata Register High Byte    |       |       |       |       |                          | uuuu uuuu                       |

| 18Ch    | PMCON1 | _(1)      | —                         | _        | — — — RD                   |       |       |       |       | 10                       | 10                              |

Legend: x = unknown, u = unchanged, r = reserved, - = unimplemented read as '0'. Shaded cells are not used during FLASH access. **Note 1:** This bit always reads as a '1'.

| Name         | Bit# | Buffer | Function                                                                        |

|--------------|------|--------|---------------------------------------------------------------------------------|

| RA0/AN0      | bit0 | TTL    | Input/output or analog input.                                                   |

| RA1/AN1      | bit1 | TTL    | Input/output or analog input.                                                   |

| RA2/AN2      | bit2 | TTL    | Input/output or analog input.                                                   |

| RA3/AN3/VREF | bit3 | TTL    | Input/output or analog input or VREF.                                           |

| RA4/T0CKI    | bit4 | ST     | Input/output or external clock input for Timer0. Output is open drain type.     |

| RA5/SS/AN4   | bit5 | TTL    | Input/output or slave select input for synchronous serial port or analog input. |

#### TABLE 4-1: PORTA FUNCTIONS

Legend: TTL = TTL input, ST = Schmitt Trigger input

#### TABLE 4-2: SUMMARY OF REGISTERS ASSOCIATED WITH PORTA

| Address | Name   | Bit 7 | Bit 6 | Bit 5 | Bit 4                         | Bit 3 | Bit 2 | Bit 1 | Bit 0 | Value on:<br>POR,<br>BOR | Value on all<br>other<br>RESETS |

|---------|--------|-------|-------|-------|-------------------------------|-------|-------|-------|-------|--------------------------|---------------------------------|

| 05h     | PORTA  | _     | _     | RA5   | RA4                           | RA3   | RA2   | RA1   | RA0   | 0x 0000                  | 0u 0000                         |

| 85h     | TRISA  | _     | _     | PORTA | PORTA Data Direction Register |       |       |       |       | 11 1111                  | 11 1111                         |

| 9Fh     | ADCON1 |       | _     | _     | _                             | _     | PCFG2 | PCFG1 | PCFG0 | 000                      | 000                             |

Legend: x = unknown, u = unchanged, - = unimplemented locations read as '0'. Shaded cells are not used by PORTA.

**Note:** When using the SSP module in SPI Slave mode and  $\overline{SS}$  enabled, the A/D converter must be set to one of the following modes where PCFG2:PCFG0 = 100, 101, 11x.

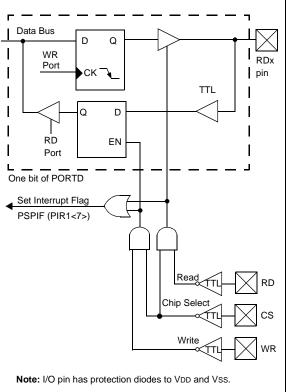

## 4.6 Parallel Slave Port

The Parallel Slave Port (PSP) is not implemented on the PIC16F73 or PIC16F76.

PORTD operates as an 8-bit wide Parallel Slave Port, or Microprocessor Port, when control bit PSPMODE (TRISE<4>) is set. In Slave mode, it is asynchronously readable and writable by an external system using the read control input pin RE0/RD, the write control input pin RE1/WR, and the chip select control input pin RE2/CS.

The PSP can directly interface to an 8-bit microprocessor data bus. The external microprocessor can read or write the PORTD latch as an 8-bit latch. Setting bit PSPMODE enables port pin RE0/RD to be the RD input, RE1/WR to be the WR input and RE2/CS to be the CS (chip select) input. For this functionality, the corresponding data direction bits of the TRISE register (TRISE<2:0>) must be configured as inputs (i.e., set). The A/D port configuration bits PCFG3:PCFG0 (ADCON1<3:0>) must be set to configure pins RE2:RE0 as digital I/O.

There are actually two 8-bit latches, one for data output (external reads) and one for data input (external writes). The firmware writes 8-bit data to the PORTD output data latch and reads data from the PORTD input data latch (note that they have the same address). In this mode, the TRISD register is ignored, since the external device is controlling the direction of data flow.

An external write to the PSP occurs when the  $\overline{CS}$  and  $\overline{WR}$  lines are both detected low. Firmware can read the actual data on the PORTD pins during this time. When either the CS or WR lines become high (level triggered), the data on the PORTD pins is latched, and the Input Buffer Full (IBF) status flag bit (TRISE<7>) and interrupt flag bit PSPIF (PIR1<7>) are set on the Q4 clock cycle, following the next Q2 cycle to signal the write is complete (Figure 4-9). Firmware clears the IBF flag by reading the latched PORTD data, and clears the PSPIF bit.

The Input Buffer Overflow (IBOV) status flag bit (TRISE<5>) is set if an external write to the PSP occurs while the IBF flag is set from a previous external write. The previous PORTD data is overwritten with the new data. IBOV is cleared by reading PORTD and clearing IBOV.

A read from the PSP occurs when both the  $\overline{CS}$  and  $\overline{RD}$  lines are detected low. The data in the PORTD output latch is output to the PORTD pins. The Output Buffer Full (OBF) status flag bit (TRISE<6>) is cleared immediately (Figure 4-10), indicating that the PORTD latch is being read, or has been read by the external bus. If firmware writes new data to the output latch during this time, it is immediately output to the PORTD pins, but OBF will remain cleared.

When either the  $\overline{CS}$  or  $\overline{RD}$  pins are detected high, the PORTD outputs are disabled, and the interrupt flag bit PSPIF is set on the Q4 clock cycle following the next Q2 cycle, indicating that the read is complete. OBF remains low until firmware writes new data to PORTD.

When not in PSP mode, the IBF and OBF bits are held clear. Flag bit IBOV remains unchanged. The PSPIF bit must be cleared by the user in firmware; the interrupt can be disabled by clearing the interrupt enable bit PSPIE (PIE1<7>).

## FIGURE 4-8:

#### PORTD AND PORTE BLOCK DIAGRAM (PARALLEL SLAVE PORT)

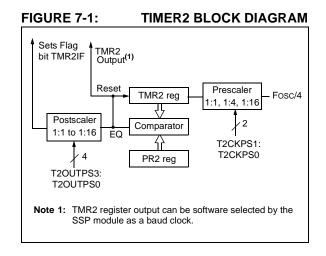

## 7.0 TIMER2 MODULE

Timer2 is an 8-bit timer with a prescaler and a postscaler. It can be used as the PWM time-base for the PWM mode of the CCP module(s). The TMR2 register is readable and writable, and is cleared on any device RESET.

The input clock (Fosc/4) has a prescale option of 1:1, 1:4 or 1:16, selected by control bits T2CKPS1:T2CKPS0 (T2CON<1:0>).

The Timer2 module has an 8-bit period register, PR2. Timer2 increments from 00h until it matches PR2 and then resets to 00h on the next increment cycle. PR2 is a readable and writable register. The PR2 register is initialized to FFh upon RESET.

The match output of TMR2 goes through a 4-bit postscaler (which gives a 1:1 to 1:16 scaling inclusive) to generate a TMR2 interrupt (latched in flag bit TMR2IF, (PIR1<1>)).

Timer2 can be shut-off by clearing control bit TMR2ON (T2CON<2>) to minimize power consumption.

Register 7-1 shows the Timer2 control register.

Additional information on timer modules is available in the PICmicro<sup>™</sup> Mid-Range MCU Family Reference Manual (DS33023).

#### 7.1 Timer2 Prescaler and Postscaler

The prescaler and postscaler counters are cleared when any of the following occurs:

- a write to the TMR2 register

- a write to the T2CON register

- any device RESET (POR, MCLR Reset, WDT Reset or BOR)

TMR2 is not cleared when T2CON is written.

## 7.2 Output of TMR2

The output of TMR2 (before the postscaler) is fed to the SSP module, which optionally uses it to generate shift clock.

#### 8.5.3 SETUP FOR PWM OPERATION

The following steps should be taken when configuring the CCP module for PWM operation:

- 1. Set the PWM period by writing to the PR2 register.

- 2. Set the PWM duty cycle by writing to the CCPR1L register and CCP1CON<5:4> bits.

- 3. Make the CCP1 pin an output by clearing the TRISC<2> bit.

- 4. Set the TMR2 prescale value and enable Timer2 by writing to T2CON.

- 5. Configure the CCP1 module for PWM operation.

#### TABLE 8-4: EXAMPLE PWM FREQUENCIES AND RESOLUTIONS (Fosc = 20 MHz)

| PWM Frequency             | 1.22 kHz | 4.88 kHz | 19.53 kHz | 78.12 kHz | 156.3 kHz | 208.3 kHz |

|---------------------------|----------|----------|-----------|-----------|-----------|-----------|

| Timer Prescale (1, 4, 16) | 16       | 4        | 1         | 1         | 1         | 1         |

| PR2 Value                 | 0xFF     | 0xFF     | 0xFF      | 0x3F      | 0x1F      | 0x17      |

| Maximum Resolution (bits) | 10       | 10       | 10        | 8         | 7         | 5.5       |

#### TABLE 8-5: REGISTERS ASSOCIATED WITH PWM AND TIMER2

| Address               | Name    | Bit 7                               | Bit 6                                                   | Bit 5      | Bit 4   | Bit 3   | Bit 2  | Bit 1   | Bit 0   | PC   | e on:<br>DR,<br>DR | all o | e on<br>other<br>SETS |

|-----------------------|---------|-------------------------------------|---------------------------------------------------------|------------|---------|---------|--------|---------|---------|------|--------------------|-------|-----------------------|

| 0Bh,8Bh,<br>10Bh,18Bh | INTCON  | GIE                                 | PEIE                                                    | TMR0IE     | INTE    | RBIE    | TMR0IF | INTF    | RBIF    | 0000 | 000x               | 0000  | 000u                  |

| 0Ch                   | PIR1    | PSPIF <sup>(1)</sup>                | ADIF                                                    | RCIF       | TXIF    | SSPIF   | CCP1IF | TMR2IF  | TMR1IF  | 0000 | 0000               | 0000  | 0000                  |

| 0Dh                   | PIR2    | _                                   | —                                                       | —          |         | _       | —      |         | CCP2IF  |      | 0                  |       | 0                     |

| 8Ch                   | PIE1    | PSPIE <sup>(1)</sup>                | ADIE                                                    | RCIE       | TXIE    | SSPIE   | CCP1IE | TMR2IE  | TMR1IE  | 0000 | 0000               | 0000  | 0000                  |

| 8Dh                   | PIE2    | —                                   | _                                                       | _          | _       | —       | —      | _       | CCP2IE  |      | 0                  |       | 0                     |

| 87h                   | TRISC   | PORTC D                             | PORTC Data Direction Register                           |            |         |         |        |         |         | 1111 | 1111               | 1111  | 1111                  |

| 11h                   | TMR2    | Timer2 M                            | Timer2 Module Register 0                                |            |         |         |        |         | 0000    | 0000 | 0000               | 0000  |                       |

| 92h                   | PR2     | Timer2 M                            | odule Peric                                             | d Register |         |         |        |         |         | 1111 | 1111               | 1111  | 1111                  |

| 12h                   | T2CON   | _                                   | TOUTPS3                                                 | TOUTPS2    | TOUTPS1 | TOUTPS0 | TMR2ON | T2CKPS1 | T2CKPS0 | -000 | 0000               | -000  | 0000                  |

| 15h                   | CCPR1L  | Capture/C                           | Capture/Compare/PWM Register1 (LSB)                     |            |         |         |        |         | xxxx    | xxxx | uuuu               | uuuu  |                       |

| 16h                   | CCPR1H  | Capture/C                           | Capture/Compare/PWM Register1 (MSB)                     |            |         |         |        |         | uuuu    | uuuu |                    |       |                       |

| 17h                   | CCP1CON | _                                   | _                                                       | CCP1X      | CCP1Y   | CCP1M3  | CCP1M2 | CCP1M1  | CCP1M0  | 00   | 0000               | 00    | 0000                  |

| 1Bh                   | CCPR2L  | Capture/Compare/PWM Register2 (LSB) |                                                         |            |         |         |        | xxxx    | xxxx    | uuuu | uuuu               |       |                       |

| 1Ch                   | CCPR2H  | Capture/C                           | Capture/Compare/PWM Register2 (MSB) xxxx xxxx uuuu uuuu |            |         |         |        |         |         |      |                    |       |                       |

| 1Dh                   | CCP2CON | —                                   | —                                                       | CCP2X      | CCP2Y   | CCP2M3  | CCP2M2 | CCP2M1  | CCP2M0  | 00   | 0000               | 00    | 0000                  |

Legend: x = unknown, u = unchanged, - = unimplemented, read as '0'. Shaded cells are not used by PWM and Timer2.

Note 1: Bits PSPIE and PSPIF are reserved on the PIC16F73/76; always maintain these bits clear.

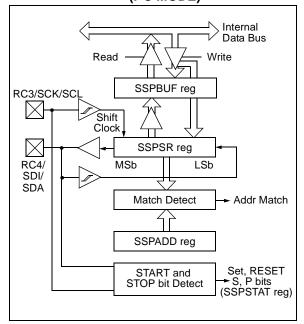

## 9.3 SSP I<sup>2</sup>C Operation

The SSP module in  $l^2C$  mode, fully implements all slave functions, except general call support, and provides interrupts on START and STOP bits in hardware to facilitate firmware implementations of the master functions. The SSP module implements the standard mode specifications as well as 7-bit and 10-bit addressing.

Two pins are used for data transfer. These are the RC3/ SCK/SCL pin, which is the clock (SCL), and the RC4/ SDI/SDA pin, which is the data (SDA). The user must configure these pins as inputs or outputs through the TRISC<4:3> bits.

The SSP module functions are enabled by setting SSP enable bit SSPEN (SSPCON<5>).

FIGURE 9-5: SSP BLOCK DIAGRAM (I<sup>2</sup>C MODE)

The SSP module has five registers for  $\mathsf{I}^2\mathsf{C}$  operation. These are the:

- SSP Control Register (SSPCON)

- SSP Status Register (SSPSTAT)

- Serial Receive/Transmit Buffer (SSPBUF)

- SSP Shift Register (SSPSR) Not directly accessible

- SSP Address Register (SSPADD)

The SSPCON register allows control of the  $I^2C$  operation. Four mode selection bits (SSPCON<3:0>) allow one of the following  $I^2C$  modes to be selected:

- I<sup>2</sup>C Slave mode (7-bit address)

- I<sup>2</sup>C Slave mode (10-bit address)

- I<sup>2</sup>C Slave mode (7-bit address), with START and STOP bit interrupts enabled to support Firmware Master mode

- I<sup>2</sup>C Slave mode (10-bit address), with START and STOP bit interrupts enabled to support Firmware Master mode

- I<sup>2</sup>C START and STOP bit interrupts enabled to support Firmware Master mode, Slave is IDLE

Selection of any  $I^2C$  mode with the SSPEN bit set, forces the SCL and SDA pins to be open drain, provided these pins are programmed to inputs by setting the appropriate TRISC bits. Pull-up resistors must be provided externally to the SCL and SDA pins for proper operation of the  $I^2C$  module.

Additional information on SSP I<sup>2</sup>C operation can be found in the PICmicro<sup>™</sup> Mid-Range MCU Family Reference Manual (DS33023A).

#### 9.3.1 SLAVE MODE

In Slave mode, the SCL and SDA pins must be configured as inputs (TRISC<4:3> set). The SSP module will override the input state with the output data when required (slave-transmitter).

When an address is matched, or the data transfer after an address match is received, the hardware automatically will generate the Acknowledge ( $\overline{ACK}$ ) pulse, and then load the SSPBUF register with the received value currently in the SSPSR register.

There are certain conditions that will cause the SSP module not to give this ACK pulse. They include (either or both):

- a) The buffer full bit BF (SSPSTAT<0>) was set before the transfer was received.

- b) The overflow bit SSPOV (SSPCON<6>) was set before the transfer was received.

In this case, the SSPSR register value is not loaded into the SSPBUF, but bit SSPIF (PIR1<3>) is set. Table 9-2 shows what happens when a data transfer byte is received, given the status of bits BF and SSPOV. The shaded cells show the condition where user software did not properly clear the overflow condition. Flag bit BF is cleared by reading the SSPBUF register, while bit SSPOV is cleared through software.

The SCL clock input must have a minimum high and low for proper operation. The high and low times of the  $I^2C$  specification, as well as the requirements of the SSP module, are shown in timing parameter #100 and parameter #101.

## 10.0 UNIVERSAL SYNCHRONOUS ASYNCHRONOUS RECEIVER TRANSMITTER (USART)

The Universal Synchronous Asynchronous Receiver Transmitter (USART) module is one of the two serial I/O modules. (USART is also known as a Serial Communications Interface or SCI.) The USART can be configured as a full duplex asynchronous system that can communicate with peripheral devices, such as CRT terminals and personal computers, or it can be configured as a half duplex synchronous system that can communicate with peripheral devices, such as A/D or D/A integrated circuits, serial EEPROMs, etc. The USART can be configured in the following modes:

- Asynchronous (full duplex)

- Synchronous Master (half duplex)

- Synchronous Slave (half duplex)

Bit SPEN (RCSTA<7>) and bits TRISC<7:6> have to be set in order to configure pins RC6/TX/CK and RC7/RX/DT as the Universal Synchronous Asynchronous Receiver Transmitter.

#### REGISTER 10-1: TXSTA: TRANSMIT STATUS AND CONTROL REGISTER (ADDRESS 98h)

|        | R/W-0                     | R/W-0                        | R/W-0         | R/W-0        | U-0      | R/W-0      | R-1          | R/W-0 |

|--------|---------------------------|------------------------------|---------------|--------------|----------|------------|--------------|-------|

|        | CSRC                      | TX9                          | TXEN          | SYNC         |          | BRGH       | TRMT         | TX9D  |

|        | bit 7                     |                              |               |              |          |            |              | bit 0 |

| bit 7  | CSRC: Clo                 | ock Source S                 | Select bit    |              |          |            |              |       |

|        | Asynchronous mode:        |                              |               |              |          |            |              |       |

|        | Don't care                |                              |               |              |          |            |              |       |

|        | Synchrono                 |                              |               |              |          |            |              |       |

|        |                           | · mode (clock<br>mode (clock |               |              | om BRG)  |            |              |       |

| bit 6  | <b>TX9</b> : 9-bit        | Transmit Ena                 | able bit      |              |          |            |              |       |

|        |                           | s 9-bit transn               |               |              |          |            |              |       |

| 1.11.5 |                           | s 8-bit transn               |               |              |          |            |              |       |

| bit 5  |                           | nsmit Enable<br>nit enabled  | e dit         |              |          |            |              |       |

|        |                           | nit disabled                 |               |              |          |            |              |       |

|        | Note:                     | SREN/CRE                     | N overrides   | TXEN in Sy   | nc mode. |            |              |       |

| bit 4  | SYNC: US                  | ART Mode S                   | Select bit    |              |          |            |              |       |

|        |                           | ronous mode                  |               |              |          |            |              |       |

|        | -                         | nronous mod                  |               |              |          |            |              |       |

| bit 3  | -                         | ented: Read                  |               |              |          |            |              |       |

| bit 2  | -                         | gh Baud Rate                 | e Select bit  |              |          |            |              |       |

|        | Asynchron                 |                              |               |              |          |            |              |       |

|        | 1 = High sp<br>0 = Low sp |                              |               |              |          |            |              |       |

|        | Synchrono                 |                              |               |              |          |            |              |       |

|        | Unused in                 |                              |               |              |          |            |              |       |

| bit 1  | TRMT: Tra                 | nsmit Shift R                | Register Stat | us bit       |          |            |              |       |

|        | 1 = TSR ei                |                              |               |              |          |            |              |       |

| 1 1 0  | 0 = TSR fu                |                              |               |              |          |            |              |       |

| bit 0  | Can be par                | bit of Transr                | nit Data      |              |          |            |              |       |

|        | oun be pu                 |                              |               |              |          |            |              |       |

|        | Legend:                   |                              |               |              |          |            |              |       |

|        | R = Reada                 | ble bit                      | W = W         | /ritable bit | U = Unir | nplemented | bit, read as | ʻ0'   |

| R = Readable bit         | W = Writable bit | U = Unimplemented    | bit, read as '0'   |

|--------------------------|------------------|----------------------|--------------------|

| - n = Value at POR reset | '1' = Bit is set | '0' = Bit is cleared | x = Bit is unknown |

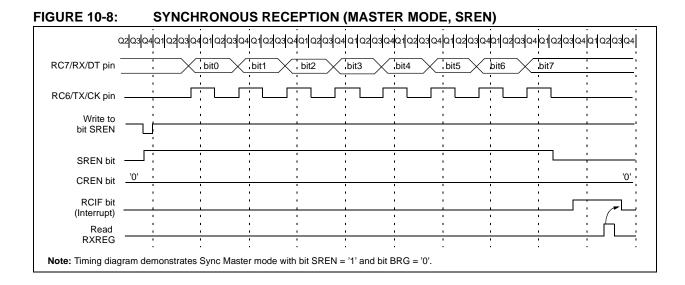

#### 10.3.2 USART SYNCHRONOUS MASTER RECEPTION

Once synchronous mode is selected, reception is enabled by setting either enable bit SREN (RCSTA<5>), or enable bit CREN (RCSTA<4>). Data is sampled on the RC7/RX/DT pin on the falling edge of the clock. If enable bit SREN is set, then only a single word is received. If enable bit CREN is set, the reception is continuous until CREN is cleared. If both bits are set, CREN takes precedence. After clocking the last bit, the received data in the Receive Shift Register (RSR) is transferred to the RCREG register (if it is empty). When the transfer is complete, interrupt flag bit RCIF (PIR1<5>) is set. The actual interrupt can be enabled/ disabled by setting/clearing enable bit RCIE (PIE1<5>). Flag bit RCIF is a read only bit, which is reset by the hardware. In this case, it is reset when the RCREG register has been read and is empty. The RCREG is a double buffered register (i.e., it is a two deep FIFO). It is possible for two bytes of data to be received and transferred to the RCREG FIFO and a third byte to begin shifting into the RSR register. On the clocking of the last bit of the third byte, if the RCREG register is still full, then overrun error bit OERR (RCSTA<1>) is set. The word in the RSR will be lost. The RCREG register can be read twice to retrieve the two bytes in the FIFO. Bit OERR has to be cleared in software (by clearing bit CREN). If bit OERR is set, transfers from the RSR to the RCREG are inhibited, so it is essential to clear bit OERR if it is set. The ninth receive bit is buffered the same way as the

receive data. Reading the RCREG register will load bit RX9D with a new value, therefore, it is essential for the user to read the RCSTA register before reading RCREG, in order not to lose the old RX9D information.

Steps to follow when setting up a Synchronous Master Reception:

- 1. Initialize the SPBRG register for the appropriate baud rate (Section 10.1).

- 2. Enable the synchronous master serial port by setting bits SYNC, SPEN and CSRC.

- 3. Ensure bits CREN and SREN are clear.

- 4. If interrupts are desired, then set enable bit RCIE.

- 5. If 9-bit reception is desired, then set bit RX9.

- 6. If a single reception is required, set bit SREN. For continuous reception set bit CREN.

- 7. Interrupt flag bit RCIF will be set when reception is complete and an interrupt will be generated if enable bit RCIE was set.

- 8. Read the RCSTA register to get the ninth bit (if enabled) and determine if any error occurred during reception.

- 9. Read the 8-bit received data by reading the RCREG register.

- 10. If any error occurred, clear the error by clearing bit CREN.

- 11. If using interrupts, ensure that GIE and PEIE in the INTCON register are set.

#### 11.2 Selecting the A/D Conversion Clock

The A/D conversion time per bit is defined as TAD. The A/D conversion requires 9.0 TAD per 8-bit conversion. The source of the A/D conversion clock is software selectable. The four possible options for TAD are:

- 2 Tosc (Fosc/2)

- 8 Tosc (Fosc/8)

- 32 Tosc (Fosc/32)

- Internal RC oscillator (2-6 μs)

For correct A/D conversions, the A/D conversion clock (TAD) must be selected to ensure a minimum TAD time as small as possible, but no less than  $1.6 \,\mu s$ .

## 11.3 Configuring Analog Port Pins

The ADCON1, TRISA and TRISE registers control the operation of the A/D port pins. The port pins that are desired as analog inputs must have their corresponding TRIS bits set (input). If the TRIS bit is cleared (output), the digital output level (VOH or VOL) will be converted.

The A/D operation is independent of the state of the CHS2:CHS0 bits and the TRIS bits.