Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                  |

|----------------------------|-------------------------------------------------------------------------|

| Core Processor             | PIC                                                                     |

| Core Size                  | 8-Bit                                                                   |

| Speed                      | 20MHz                                                                   |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                                       |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                   |

| Number of I/O              | 33                                                                      |

| Program Memory Size        | 14KB (8K x 14)                                                          |

| Program Memory Type        | FLASH                                                                   |

| EEPROM Size                | -                                                                       |

| RAM Size                   | 368 x 8                                                                 |

| Voltage - Supply (Vcc/Vdd) | 4V ~ 5.5V                                                               |

| Data Converters            | A/D 8x8b                                                                |

| Oscillator Type            | External                                                                |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                       |

| Mounting Type              | Surface Mount                                                           |

| Package / Case             | 44-TQFP                                                                 |

| Supplier Device Package    | 44-TQFP (10x10)                                                         |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16f77-i-pt |

|                            |                                                                         |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### 1.0 **DEVICE OVERVIEW**

This document contains device specific information about the following devices:

- PIC16F73

- PIC16F74

- PIC16F76

- PIC16F77

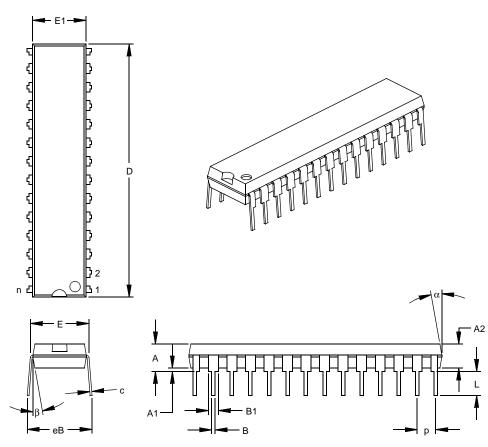

PIC16F73/76 devices are available only in 28-pin packages, while PIC16F74/77 devices are available in 40-pin and 44-pin packages. All devices in the PIC16F7X family share common architecture, with the following differences:

- The PIC16F73 and PIC16F76 have one-half of the total on-chip memory of the PIC16F74 and **PIC16F77**

- The 28-pin devices have 3 I/O ports, while the 40/44-pin devices have 5

- · The 28-pin devices have 11 interrupts, while the 40/44-pin devices have 12

- The 28-pin devices have 5 A/D input channels, while the 40/44-pin devices have 8

- The Parallel Slave Port is implemented only on the 40/44-pin devices

PIC16F7X DEVICE FEATURES **PIC16F74 PIC16F76 Key Features PIC16F73 PIC16F77 Operating Frequency** DC - 20 MHz DC - 20 MHz DC - 20 MHz DC - 20 MHz **RESETS** (and Delays) POR, BOR POR. BOR POR. BOR POR, BOR (PWRT, OST) (PWRT, OST) (PWRT, OST) (PWRT, OST) FLASH Program Memory 4K 4K 8K 8K (14-bit words) Data Memory (bytes) 368 192 192 368 Interrupts 11 12 11 12 I/O Ports Ports A,B,C Ports A,B,C Ports A,B,C,D,E Ports A,B,C,D,E Timers 3 3 3 3 Capture/Compare/PWM Modules 2 2 2 2 SSP, USART Serial Communications SSP, USART SSP. USART SSP, USART Parallel Communications PSP PSP 8-bit Analog-to-Digital Module **5 Input Channels** 8 Input Channels 5 Input Channels 8 Input Channels Instruction Set **35 Instructions 35 Instructions** 35 Instructions **35 Instructions** Packaging 28-pin DIP 40-pin PDIP 28-pin DIP 40-pin PDIP 28-pin SOIC 44-pin PLCC 28-pin SOIC 44-pin PLCC 28-pin SSOP 44-pin TQFP 28-pin SSOP 44-pin TQFP 28-pin MLF 28-pin MLF

## **TABLE 1-1:**

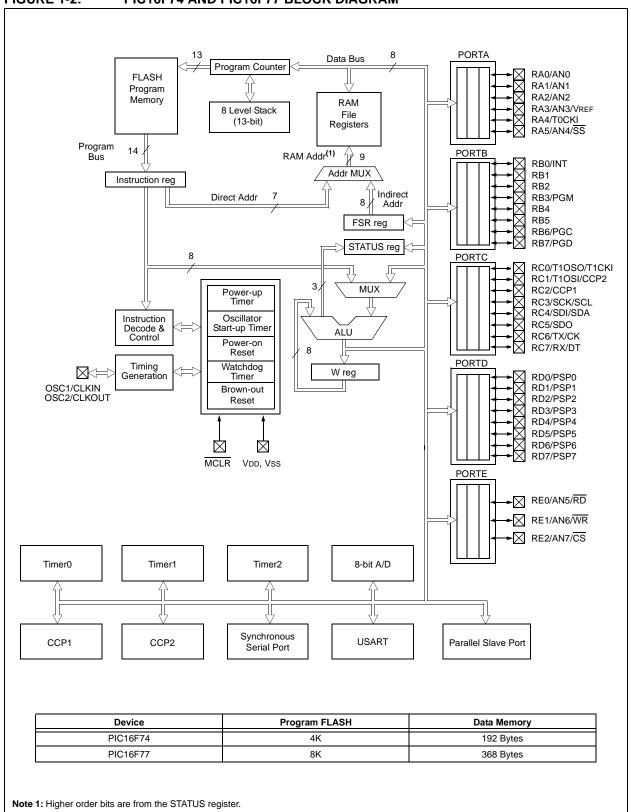

The available features are summarized in Table 1-1. Block diagrams of the PIC16F73/76 and PIC16F74/77 devices are provided in Figure 1-1 and Figure 1-2, respectively. The pinouts for these device families are listed in Table 1-2 and Table 1-3.

Additional information may be found in the PICmicro™ Mid-Range Reference Manual (DS33023), which may be obtained from your local Microchip Sales Representative or downloaded from the Microchip website. The Reference Manual should be considered a complementary document to this data sheet, and is highly recommended reading for a better understanding of the device architecture and operation of the peripheral modules.

FIGURE 1-2: PIC16F74 AND PIC16F77 BLOCK DIAGRAM

#### PIC16F73 AND PIC16F76 PINOUT DESCRIPTION **TABLE 1-2:**

| Pin Name          | DIP<br>SSOP<br>SOIC<br>Pin# | MLF<br>Pin# | I/O/P<br>Type | Buffer<br>Type         | Description                                                                                                                                                      |

|-------------------|-----------------------------|-------------|---------------|------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| OSC1/CLKI<br>OSC1 | 9                           | 6           | Ι             | ST/CMOS <sup>(3)</sup> | Oscillator crystal or external clock input.<br>Oscillator crystal input or external clock source input. ST<br>buffer when configured in RC mode. Otherwise CMOS. |

| CLKI              |                             |             | I             |                        | External clock source input. Always associated with pin<br>function OSC1 (see OSC1/CLKI, OSC2/CLKO pins).                                                        |

| OSC2/CLKO<br>OSC2 | 10                          | 7           | 0             | _                      | Oscillator crystal or clock output.<br>Oscillator crystal output.<br>Connects to crystal or resonator in Crystal Oscillator<br>mode.                             |

| CLKO              |                             |             | 0             |                        | In RC mode, OSC2 pin outputs CLKO, which has 1/4 the frequency of OSC1 and denotes the instruction cycle rate.                                                   |

| MCLR/VPP<br>MCLR  | 1                           | 26          | I             | ST                     | Master Clear (input) or programming voltage (output).<br>Master Clear (Reset) input. This pin is an active low<br>RESET to the device.                           |

| Vpp               |                             |             | Р             |                        | Programming voltage input.                                                                                                                                       |

|                   |                             |             |               |                        | PORTA is a bi-directional I/O port.                                                                                                                              |

| RA0/AN0           | 2                           | 27          |               | TTL                    |                                                                                                                                                                  |

| RA0<br>AN0        |                             |             | I/O           |                        | Digital I/O.<br>Analog input 0.                                                                                                                                  |

| RA1/AN1           | 3                           | 28          | 1             | TTL                    | Analog input 0.                                                                                                                                                  |

| RA1/ANT<br>RA1    | 3                           | 20          | I/O           | 116                    | Digital I/O.                                                                                                                                                     |

| AN1               |                             |             | "c            |                        | Analog input 1.                                                                                                                                                  |

| RA2/AN2           | 4                           | 1           |               | TTL                    |                                                                                                                                                                  |

| RA2               |                             |             | I/O           |                        | Digital I/O.                                                                                                                                                     |

| AN2               |                             |             | I             |                        | Analog input 2.                                                                                                                                                  |

| RA3/AN3/VREF      | 5                           | 2           |               | TTL                    |                                                                                                                                                                  |

| RA3               |                             |             | I/O           |                        | Digital I/O.                                                                                                                                                     |

| AN3               |                             |             | I             |                        | Analog input 3.                                                                                                                                                  |

|                   | 0                           |             | I             | 07                     | A/D reference voltage input.                                                                                                                                     |

| RA4/T0CKI<br>RA4  | 6                           | 4           | I/O           | ST                     | Digital I/O – Open drain when configured as output.                                                                                                              |

| TOCKI             |                             |             | "U            |                        | Timer0 external clock input.                                                                                                                                     |

| RA5/SS/AN4        | 7                           | 5           |               | TTL                    |                                                                                                                                                                  |

| RA5               |                             | -           | I/O           |                        | Digital I/O.                                                                                                                                                     |

| SS                |                             |             | Ι             |                        | SPI slave select input.                                                                                                                                          |

| AN4               |                             |             | Ι             |                        | Analog input 4.                                                                                                                                                  |

| Legend: I = input | tucod                       | O = out     | put           | I/O = inpu             | ut/output P = power                                                                                                                                              |

— = Not used TTL = TTL input ST = Schmitt Trigger input

Note 1: This buffer is a Schmitt Trigger input when configured as the external interrupt.

This buffer is a Schmitt Trigger input when used in Serial Programming mode.

This buffer is a Schmitt Trigger input when configured in RC Oscillator mode and a CMOS input otherwise.

| TABLE 1-2: | PIC16F73 AND PIC16F76 PINOUT DESCRIPTION (CONTINUED) |

|------------|------------------------------------------------------|

|------------|------------------------------------------------------|

| Pin Name        | DIP<br>SSOP<br>SOIC<br>Pin# | MLF<br>Pin# | I/O/P<br>Type | Buffer<br>Type        | Description                                                      |  |  |  |

|-----------------|-----------------------------|-------------|---------------|-----------------------|------------------------------------------------------------------|--|--|--|

|                 |                             |             |               |                       | PORTB is a bi-directional I/O port. PORTB can be software        |  |  |  |

|                 |                             |             |               | (o(1)                 | programmed for internal weak pull-up on all inputs.              |  |  |  |

| RB0/INT         | 21                          | 18          | 1/0           | TTL/ST <sup>(1)</sup> |                                                                  |  |  |  |

| RB0             |                             |             | I/O           |                       | Digital I/O.                                                     |  |  |  |

| INT             |                             |             | I             |                       | External interrupt.                                              |  |  |  |

| RB1             | 22                          | 19          | I/O           | TTL                   | Digital I/O.                                                     |  |  |  |

| RB2             | 23                          | 20          | I/O           | TTL                   | Digital I/O.                                                     |  |  |  |

| RB3/PGM         | 24                          | 21          |               | TTL                   |                                                                  |  |  |  |

| RB3             |                             |             | I/O           |                       | Digital I/O.                                                     |  |  |  |

| PGM             |                             |             | I/O           |                       | Low voltage ICSP programming enable pin.                         |  |  |  |

| RB4             | 25                          | 22          | I/O           | TTL                   | Digital I/O.                                                     |  |  |  |

| RB5             | 26                          | 23          | I/O           | TTL                   | Digital I/O.                                                     |  |  |  |

| RB6/PGC         | 27                          | 24          | ., 0          | TTL/ST <sup>(2)</sup> | Digital i/ O.                                                    |  |  |  |

| RB6             | 21                          | 24          | I/O           | 112/31.7              | Digital I/O.                                                     |  |  |  |

| PGC             |                             |             | I/O           |                       | In-Circuit Debugger and ICSP programming clock.                  |  |  |  |

|                 | 20                          | 25          | ., O          | TTL/ST <sup>(2)</sup> |                                                                  |  |  |  |

| RB7/PGD<br>RB7  | 28                          | 25          | I/O           | 11L/51(-)             | Digital I/O.                                                     |  |  |  |

| PGD             |                             |             | 1/O           |                       | In-Circuit Debugger and ICSP programming data.                   |  |  |  |

| FGD             |                             |             | 1/0           |                       |                                                                  |  |  |  |

|                 |                             |             |               |                       | PORTC is a bi-directional I/O port.                              |  |  |  |

| RC0/T1OSO/T1CKI | 11                          | 8           |               | ST                    |                                                                  |  |  |  |

| RC0             |                             |             | I/O           |                       | Digital I/O.                                                     |  |  |  |

| T1OSO           |                             |             | 0             |                       | Timer1 oscillator output.                                        |  |  |  |

| T1CKI           |                             |             | I             |                       | Timer1 external clock input.                                     |  |  |  |

| RC1/T1OSI/CCP2  | 12                          | 9           |               | ST                    |                                                                  |  |  |  |

| RC1             |                             |             | I/O           |                       | Digital I/O.                                                     |  |  |  |

| T1OSI           |                             |             | I             |                       | Timer1 oscillator input.                                         |  |  |  |

| CCP2            |                             |             | I/O           |                       | Capture2 input, Compare2 output, PWM2 output.                    |  |  |  |

| RC2/CCP1        | 13                          | 10          |               | ST                    |                                                                  |  |  |  |

| RC2             |                             |             | I/O           |                       | Digital I/O.                                                     |  |  |  |

| CCP1            |                             |             | I/O           |                       | Capture1 input/Compare1 output/PWM1 output.                      |  |  |  |

| RC3/SCK/SCL     | 14                          | 11          |               | ST                    |                                                                  |  |  |  |

| RC3             |                             |             | I/O           |                       | Digital I/O.                                                     |  |  |  |

| SCK             |                             |             | I/O           |                       | Synchronous serial clock input/output for SPI mode.              |  |  |  |

| SCL             |                             |             | I/O           |                       | Synchronous serial clock input/output for I <sup>2</sup> C mode. |  |  |  |

| RC4/SDI/SDA     | 15                          | 12          |               | ST                    |                                                                  |  |  |  |

| RC4             |                             |             | I/O           |                       | Digital I/O.                                                     |  |  |  |

| SDI             |                             |             | I             |                       | SPI data in.                                                     |  |  |  |

| SDA             |                             |             | I/O           |                       | I <sup>2</sup> C data I/O.                                       |  |  |  |

| RC5/SDO         | 16                          | 13          |               | ST                    |                                                                  |  |  |  |

| RC5             |                             |             | I/O           |                       | Digital I/O.                                                     |  |  |  |

| SDO             |                             |             | 0             |                       | SPI data out.                                                    |  |  |  |

| RC6/TX/CK       | 17                          | 14          |               | ST                    |                                                                  |  |  |  |

| RC6             |                             |             | I/O           |                       | Digital I/O.                                                     |  |  |  |

| TX              |                             |             | 0             |                       | USART asynchronous transmit.                                     |  |  |  |

| СК              |                             |             | I/O           |                       | USART 1 synchronous clock.                                       |  |  |  |

| RC7/RX/DT       | 18                          | 15          |               | ST                    |                                                                  |  |  |  |

| RC7             |                             |             | I/O           |                       | Digital I/O.                                                     |  |  |  |

| RX              |                             |             | I             |                       | USART asynchronous receive.                                      |  |  |  |

| DT              |                             |             | I/O           |                       | USART synchronous data.                                          |  |  |  |

| Vss             | 8, 19                       | 5, 16       | Р             | —                     | Ground reference for logic and I/O pins.                         |  |  |  |

| V 55            | 1                           | 47          | Р             | 1                     | Desitive events for legic and 1/0 nine                           |  |  |  |

| VDD             | 20                          | 17          | Р             | —                     | Positive supply for logic and I/O pins.                          |  |  |  |

This buffer is a Schmitt Trigger input when used in Serial Programming mode.

This buffer is a Schmitt Trigger input when configured in RC Oscillator mode and a CMOS input otherwise.

## TABLE 1-3:PIC16F74 AND PIC16F77 PINOUT DESCRIPTION

| OSC1/CLKI<br>OSC1<br>CLKI<br>OSC2/CLKO<br>OSC2<br>CLKO<br>MCLR/VPP<br>MCLR<br>VPP | 13 | 14<br>15 | 30<br>31 | 1        | ST/CMOS <sup>(4)</sup> | Oscillator crystal or external clock input.<br>Oscillator crystal input or external clock source input.<br>ST buffer when configured in RC mode. Otherwise<br>CMOS.<br>External clock source input. Always associated with pin |

|-----------------------------------------------------------------------------------|----|----------|----------|----------|------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| CLKI<br>OSC2/CLKO<br>OSC2<br>CLKO<br><u>MCLR/VPP</u><br>MCLR                      | 14 | 15       | 31       | I        |                        | Oscillator crystal input or external clock source input.<br>ST buffer when configured in RC mode. Otherwise<br>CMOS.<br>External clock source input. Always associated with pin                                                |

| OSC2/CLKO<br>OSC2<br>CLKO<br>MCLR/VPP<br>MCLR                                     | 14 | 15       | 31       |          |                        | CMOS.<br>External clock source input. Always associated with pin                                                                                                                                                               |

| OSC2/CLKO<br>OSC2<br>CLKO<br>MCLR/VPP<br>MCLR                                     | 14 | 15       | 31       |          |                        | External clock source input. Always associated with pin                                                                                                                                                                        |

| OSC2<br>CLKO<br>MCLR/VPP<br>MCLR                                                  | 14 | 15       | 31       |          |                        |                                                                                                                                                                                                                                |

| OSC2<br>CLKO<br>MCLR/VPP<br>MCLR                                                  | 14 | 15       | 31       | 0        |                        | function OSC1 (see OSC1/CLKI, OSC2/CLKO pins).                                                                                                                                                                                 |

| CLKO<br>MCLR/VPP<br>MCLR                                                          |    |          |          | <u> </u> | I —                    | Oscillator crystal or clock output.                                                                                                                                                                                            |

| MCLR/Vpp<br>MCLR                                                                  |    |          |          | 0        |                        | Oscillator crystal output.                                                                                                                                                                                                     |

| MCLR/Vpp<br>MCLR                                                                  |    |          |          |          |                        | Connects to crystal or resonator in Crystal Oscillator                                                                                                                                                                         |

| MCLR/Vpp<br>MCLR                                                                  |    |          |          |          |                        | mode.                                                                                                                                                                                                                          |

| MCLR                                                                              |    |          |          | 0        |                        | In RC mode, OSC2 pin outputs CLKO, which has 1/4                                                                                                                                                                               |

| MCLR                                                                              |    |          |          |          |                        | the frequency of OSC1 and denotes the instruction                                                                                                                                                                              |

| MCLR                                                                              |    |          |          |          |                        | cycle rate.                                                                                                                                                                                                                    |

|                                                                                   | 1  | 2        | 18       |          | ST                     | Master Clear (input) or programming voltage (output).                                                                                                                                                                          |

| Vpp                                                                               |    |          |          | I        |                        | Master Clear (Reset) input. This pin is an active low                                                                                                                                                                          |

| VPP                                                                               |    |          |          |          |                        | RESET to the device.                                                                                                                                                                                                           |

|                                                                                   |    |          |          | Р        |                        | Programming voltage input.                                                                                                                                                                                                     |

|                                                                                   |    |          |          |          |                        | PORTA is a bi-directional I/O port.                                                                                                                                                                                            |

| RA0/AN0                                                                           | 2  | 3        | 19       |          | TTL                    |                                                                                                                                                                                                                                |

| RA0                                                                               |    |          |          | I/O      |                        | Digital I/O.                                                                                                                                                                                                                   |

| AN0                                                                               |    |          |          | I        |                        | Analog input 0.                                                                                                                                                                                                                |

| RA1/AN1                                                                           | 3  | 4        | 20       |          | TTL                    |                                                                                                                                                                                                                                |

| RA1                                                                               |    |          |          | I/O      |                        | Digital I/O.                                                                                                                                                                                                                   |

| AN1                                                                               |    |          |          | I        |                        | Analog input 1.                                                                                                                                                                                                                |

| RA2/AN2                                                                           | 4  | 5        | 21       |          | TTL                    |                                                                                                                                                                                                                                |

| RA2                                                                               |    |          |          | I/O      |                        | Digital I/O.                                                                                                                                                                                                                   |

| AN2                                                                               |    |          |          | I        |                        | Analog input 2.                                                                                                                                                                                                                |

| RA3/AN3/Vref                                                                      | 5  | 6        | 22       |          | TTL                    |                                                                                                                                                                                                                                |

| RA3                                                                               |    |          |          | I/O      |                        | Digital I/O.                                                                                                                                                                                                                   |

| AN3                                                                               |    |          |          | I        |                        | Analog input 3.                                                                                                                                                                                                                |

| VREF                                                                              |    |          |          | I        |                        | A/D reference voltage input.                                                                                                                                                                                                   |

| RA4/T0CKI                                                                         | 6  | 7        | 23       |          | ST                     |                                                                                                                                                                                                                                |

| RA4                                                                               |    |          |          | I/O      |                        | Digital I/O – Open drain when configured as output.                                                                                                                                                                            |

| TOCKI                                                                             |    |          |          | I        |                        | Timer0 external clock input.                                                                                                                                                                                                   |

| RA5/SS/AN4                                                                        | 7  | 8        | 24       |          | TTL                    |                                                                                                                                                                                                                                |

| RA5                                                                               |    | -        |          | I/O      |                        | Digital I/O.                                                                                                                                                                                                                   |

| SS                                                                                | 1  |          |          | 1        |                        | SPI slave select input.                                                                                                                                                                                                        |

| AN4                                                                               |    |          |          |          | 1                      |                                                                                                                                                                                                                                |

| Legend: I = inpu                                                                  |    | 1        |          |          |                        | Analog input 4.                                                                                                                                                                                                                |

— = Not used TTL = TTL input ST = Schmitt Trigger input

**Note 1:** This buffer is a Schmitt Trigger input when configured as an external interrupt.

2: This buffer is a Schmitt Trigger input when used in Serial Programming mode.

**3:** This buffer is a Schmitt Trigger input when configured as general purpose I/O and a TTL input when used in the Parallel Slave Port mode (for interfacing to a microprocessor bus).

4: This buffer is a Schmitt Trigger input when configured in RC Oscillator mode and a CMOS input otherwise.

| Pin Name          | DIP<br>Pin# | PLCC<br>Pin# | QFP<br>Pin# | I/O/P<br>Type | Buffer<br>Type        | Description                                                   |

|-------------------|-------------|--------------|-------------|---------------|-----------------------|---------------------------------------------------------------|

|                   |             |              |             |               |                       | PORTD is a bi-directional I/O port or parallel slave port     |

|                   |             |              |             |               |                       | when interfacing to a microprocessor bus.                     |

| RD0/PSP0          | 19          | 21           | 38          |               | ST/TTL <sup>(3)</sup> |                                                               |

| RD0               |             |              |             | I/O           |                       | Digital I/O.                                                  |

| PSP0              |             |              | 00          | I/O           | ot (3)                | Parallel Slave Port data.                                     |

| RD1/PSP1<br>RD1   | 20          | 22           | 39          | і<br>І/О      | ST/TTL <sup>(3)</sup> | Digital I/O.                                                  |

| PSP1              |             |              |             | 1/O           |                       | Parallel Slave Port data.                                     |

| RD2/PSP2          | 21          | 23           | 40          | 1,'C          | ST/TTL <sup>(3)</sup> |                                                               |

| RD2               | 21          | 20           | 40          | ı/O           | OI/TIE                | Digital I/O.                                                  |

| PSP2              |             |              |             | I/O           |                       | Parallel Slave Port data.                                     |

| RD3/PSP3          | 22          | 24           | 41          |               | ST/TTL <sup>(3)</sup> |                                                               |

| RD3               |             |              |             | I/O           |                       | Digital I/O.                                                  |

| PSP3              |             |              |             | I/O           |                       | Parallel Slave Port data.                                     |

| RD4/PSP4          | 27          | 30           | 2           |               | ST/TTL <sup>(3)</sup> |                                                               |

| RD4               |             |              |             | I/O           |                       | Digital I/O.                                                  |

| PSP4              |             |              |             | I/O           |                       | Parallel Slave Port data.                                     |

| RD5/PSP5          | 28          | 31           | 3           |               | ST/TTL <sup>(3)</sup> |                                                               |

| RD5               |             |              |             | I/O           |                       | Digital I/O.                                                  |

| PSP5              |             |              |             | I/O           |                       | Parallel Slave Port data.                                     |

| RD6/PSP6          | 29          | 32           | 4           |               | ST/TTL <sup>(3)</sup> | District I/O                                                  |

| RD6<br>PSP6       |             |              |             | I/O<br>I/O    |                       | Digital I/O.<br>Parallel Slave Port data.                     |

| RD7/PSP7          | 30          | 33           | 5           | 1/0           | ST/TTL <sup>(3)</sup> | Faraller Slave Folt data.                                     |

| RD7/PSP7          | 30          | - 33         | Э           | I/O           | 51/11L*/              | Digital I/O.                                                  |

| PSP7              |             |              |             | 1/O           |                       | Parallel Slave Port data.                                     |

| -                 |             |              |             |               |                       | PORTE is a bi-directional I/O port.                           |

| RE0/RD/AN5        | 8           | 9            | 25          |               | ST/TTL <sup>(3)</sup> |                                                               |

| RE0               | -           | -            |             | I/O           |                       | Digital I/O.                                                  |

| RD                |             |              |             | I             |                       | Read control for parallel slave port .                        |

| AN5               |             |              |             | I             |                       | Analog input 5.                                               |

| RE1/WR/AN6        | 9           | 10           | 26          |               | ST/TTL <sup>(3)</sup> |                                                               |

| RE1               |             |              |             | I/O           |                       | Digital I/O.                                                  |

| WR                |             |              |             | 1             |                       | Write control for parallel slave port .                       |

| AN6               |             |              |             | I             | o <i></i> (3)         | Analog input 6.                                               |

| RE2/CS/AN7        | 10          | 11           | 27          |               | ST/TTL <sup>(3)</sup> |                                                               |

| RE2<br>CS         |             |              |             | I/O<br>I      |                       | Digital I/O.<br>Chip select control for parallel slave port . |

| AN7               |             |              |             | 1             |                       | Analog input 7.                                               |

| Vss               | 12,31       | 13,34        | 6,29        | P             | _                     | Ground reference for logic and I/O pins.                      |

| VDD               | 11,32       | 12,35        | 7,28        | Р             | _                     | Positive supply for logic and I/O pins.                       |

| NC                | · -         | 1,17,2       | 12,13,      |               | _                     | These pins are not internally connected. These pins should    |

|                   |             | 8, 40        | 33, 34      |               |                       | be left unconnected.                                          |

| Legend: I = input |             | O = 0        |             | I/C           | ) = input/outpu       | ut P = power                                                  |

#### **TABLE 1-3:** PIC16F74 AND PIC16F77 PINOUT DESCRIPTION (CONTINUED)

**Note 1:** This buffer is a Schmitt Trigger input when configured as an external interrupt.

2: This buffer is a Schmitt Trigger input when used in Serial Programming mode.

3: This buffer is a Schmitt Trigger input when configured as general purpose I/O and a TTL input when used in the Parallel Slave Port mode (for interfacing to a microprocessor bus).

4: This buffer is a Schmitt Trigger input when configured in RC Oscillator mode and a CMOS input otherwise.

| <b>TABLE 2-1:</b> | SPECIAL FUNCTION REGISTER SUMMARY | (CONTINUED) |

|-------------------|-----------------------------------|-------------|

|-------------------|-----------------------------------|-------------|

| Address               | Name       | Bit 7                                                                                        | Bit 6                         | Bit 5        | Bit 4                                                      | Bit 3         | Bit 2         | Bit 1         | Bit 0        | Value on:<br>POR,<br>BOR | Details<br>on page |

|-----------------------|------------|----------------------------------------------------------------------------------------------|-------------------------------|--------------|------------------------------------------------------------|---------------|---------------|---------------|--------------|--------------------------|--------------------|

| Bank 2                |            |                                                                                              |                               |              |                                                            |               |               |               |              |                          |                    |

| 100h <sup>(4)</sup>   | INDF       | Addressing this location uses contents of FSR to address data memory (not a physical registe |                               |              |                                                            |               |               |               |              |                          | 27, 96             |

| 101h                  | TMR0       | Timer0 Mo                                                                                    | dule Registe                  |              | xxxx xxxx                                                  | 45, 96        |               |               |              |                          |                    |

| 102h <sup>(4)</sup>   | PCL        | Program C                                                                                    | Counter (PC)                  | Least Signif | icant Byte                                                 |               |               |               |              | 0000 0000                | 26, 96             |

| 103h <sup>(4)</sup>   | STATUS     | IRP                                                                                          | RP1                           | RP0          | ТО                                                         | PD            | Z             | DC            | С            | 0001 1xxx                | 19, 96             |

| 104h <sup>(4)</sup>   | FSR        | Indirect Data Memory Address Pointer                                                         |                               |              |                                                            |               |               |               |              | xxxx xxxx                | 27, 96             |

| 105h                  | —          | Unimplem                                                                                     | ented                         |              |                                                            |               |               |               |              | _                        | —                  |

| 106h                  | PORTB      | PORTB Data Latch when written: PORTB pins when read                                          |                               |              |                                                            |               |               |               |              | xxxx xxxx                | 34, 96             |

| 107h                  | _          | Unimplemented                                                                                |                               |              |                                                            |               |               |               |              | —                        | —                  |

| 108h                  | —          | Unimplem                                                                                     | ented                         |              |                                                            |               |               |               |              | —                        | —                  |

| 109h                  | —          | Unimplem                                                                                     | ented                         |              |                                                            |               |               |               |              | _                        | —                  |

| 10Ah <sup>(1,4)</sup> | PCLATH     | —                                                                                            | _                             | _            | Write Buffer                                               | for the upper | 5 bits of the | Program C     | ounter       | 0 0000                   | 21, 96             |

| 10Bh <sup>(4)</sup>   | INTCON     | GIE                                                                                          | PEIE                          | TMR0IE       | INTE                                                       | RBIE          | TMR0IF        | INTF          | RBIF         | 0000 000x                | 23, 96             |

| 10Ch                  | PMDATA     | Data Register Low Byte                                                                       |                               |              |                                                            |               |               |               |              |                          | 29, 97             |

| 10Dh                  | PMADR      | Address Register Low Byte                                                                    |                               |              |                                                            |               |               |               |              | xxxx xxxx                | 29, 97             |

| 10Eh                  | PMDATH     | — — Data Register High Byte                                                                  |                               |              |                                                            |               |               |               |              | xxxx xxxx                | 29, 97             |

| 10Fh                  | PMADRH     | — — — Address Register High Byte                                                             |                               |              |                                                            |               |               |               |              | XXXX XXXX                | 29, 97             |

| Bank 3                |            |                                                                                              |                               |              |                                                            |               |               |               |              |                          |                    |

| 180h <sup>(4)</sup>   | INDF       | Addressin                                                                                    | g this locatio                | n uses conte | ents of FSR to                                             | address data  | a memory (r   | not a physica | al register) | 0000 0000                | 27, 96             |

| 181h                  | OPTION_REG | RBPU                                                                                         | INTEDG                        | TOCS         | TOSE                                                       | PSA           | PS2           | PS1           | PS0          | 1111 1111                | 20, 44, 96         |

| 182h <sup>(4)</sup>   | PCL        | Program C                                                                                    | Counter (PC)                  | Least Signif | icant Byte                                                 |               |               |               |              | 0000 0000                | 26, 96             |

| 183h <sup>(4)</sup>   | STATUS     | IRP                                                                                          | RP1                           | RP0          | TO                                                         | PD            | Z             | DC            | С            | 0001 1xxx                | 19, 96             |

| 184h <sup>(4)</sup>   | FSR        | Indirect Da                                                                                  | ata Memory /                  | Address Poir | nter                                                       |               |               |               |              | xxxx xxxx                | 27, 96             |

| 185h                  | —          | Unimplem                                                                                     | ented                         |              |                                                            |               |               |               |              | _                        | _                  |

| 186h                  | TRISB      | PORTB D                                                                                      | PORTB Data Direction Register |              |                                                            |               |               |               |              | 1111 1111                | 34, 96             |

| 187h                  | —          | Unimplemented                                                                                |                               |              |                                                            |               |               |               |              | _                        | _                  |

| 188h                  | —          | Unimplemented                                                                                |                               |              |                                                            |               |               |               |              | _                        | _                  |

| 189h                  | —          | Unimplemented                                                                                |                               |              |                                                            |               |               |               |              | _                        | _                  |

| 18Ah <sup>(1,4)</sup> | PCLATH     | _                                                                                            |                               | _            | — Write Buffer for the upper 5 bits of the Program Counter |               |               |               |              |                          | 21, 96             |

| 18Bh <sup>(4)</sup>   | INTCON     | GIE                                                                                          | PEIE                          | TMR0IE       | INTE                                                       | RBIE          | TMR0IF        | INTF          | RBIF         | 0000 000x                | 23, 96             |

| 18Ch                  | PMCON1     | (6)                                                                                          | _                             | —            | —                                                          | —             | _             | —             | RD           | 10                       | 29, 97             |

| 18Dh                  | —          | Unimplem                                                                                     | ented                         |              |                                                            |               |               |               |              | _                        |                    |

| 18Eh                  | —          | Reserved                                                                                     | maintain clea                 | ar           |                                                            |               |               |               |              | 0000 0000                |                    |

| 18Fh                  | _          | Reserved                                                                                     | maintain clea                 | ar           |                                                            |               |               |               |              | 0000 0000                |                    |

Legend: x = unknown, u = unchanged, q = value depends on condition, - = unimplemented, read as '0', r = reserved. Shaded locations are unimplemented, read as '0'.

**Note** 1: The upper byte of the program counter is not directly accessible. PCLATH is a holding register for the PC<12:8>, whose contents are transferred to the upper byte of the program counter during branches (CALL or GOTO).

2: Other (non power-up) RESETS include external RESET through MCLR and Watchdog Timer Reset.

3: Bits PSPIE and PSPIF are reserved on the 28-pin devices; always maintain these bits clear.

4: These registers can be addressed from any bank.

5: PORTD, PORTE, TRISD, and TRISE are not physically implemented on the 28-pin devices, read as '0'.

6: This bit always reads as a '1'.

| Name         | Bit# | Buffer | Function                                                                        |  |  |  |  |

|--------------|------|--------|---------------------------------------------------------------------------------|--|--|--|--|

| RA0/AN0      | bit0 | TTL    | Input/output or analog input.                                                   |  |  |  |  |

| RA1/AN1      | bit1 | TTL    | Input/output or analog input.                                                   |  |  |  |  |

| RA2/AN2      | bit2 | TTL    | Input/output or analog input.                                                   |  |  |  |  |

| RA3/AN3/VREF | bit3 | TTL    | Input/output or analog input or VREF.                                           |  |  |  |  |

| RA4/T0CKI    | bit4 | ST     | Input/output or external clock input for Timer0. Output is open drain type.     |  |  |  |  |

| RA5/SS/AN4   | bit5 | TTL    | Input/output or slave select input for synchronous serial port or analog input. |  |  |  |  |

#### TABLE 4-1: PORTA FUNCTIONS

Legend: TTL = TTL input, ST = Schmitt Trigger input

#### TABLE 4-2: SUMMARY OF REGISTERS ASSOCIATED WITH PORTA

| Address | Name   | Bit 7 | Bit 6 | Bit 5 | Bit 4                         | Bit 3 | Bit 2 | Bit 1 | Bit 0 | Value on:<br>POR,<br>BOR | Value on all<br>other<br>RESETS |

|---------|--------|-------|-------|-------|-------------------------------|-------|-------|-------|-------|--------------------------|---------------------------------|

| 05h     | PORTA  | _     | _     | RA5   | RA4                           | RA3   | RA2   | RA1   | RA0   | 0x 0000                  | 0u 0000                         |

| 85h     | TRISA  | _     | _     | PORTA | PORTA Data Direction Register |       |       |       |       |                          | 11 1111                         |

| 9Fh     | ADCON1 |       | _     | _     | _                             | _     | PCFG2 | PCFG1 | PCFG0 | 000                      | 000                             |

Legend: x = unknown, u = unchanged, - = unimplemented locations read as '0'. Shaded cells are not used by PORTA.

**Note:** When using the SSP module in SPI Slave mode and  $\overline{SS}$  enabled, the A/D converter must be set to one of the following modes where PCFG2:PCFG0 = 100, 101, 11x.

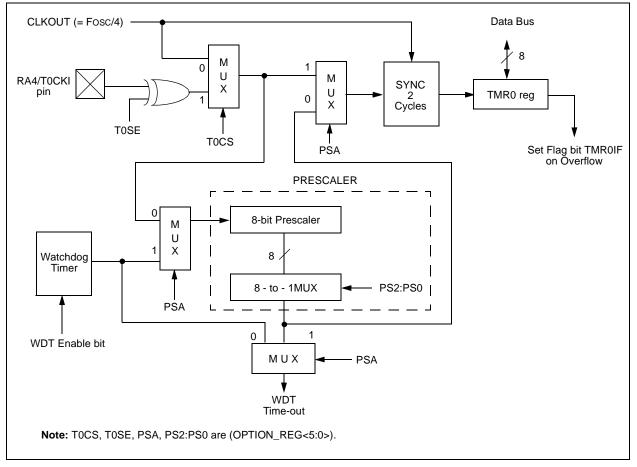

# 5.0 TIMER0 MODULE

The Timer0 module timer/counter has the following features:

- 8-bit timer/counter

- Readable and writable

- 8-bit software programmable prescaler

- · Internal or external clock select

- Interrupt on overflow from FFh to 00h

- Edge select for external clock

Additional information on the Timer0 module is available in the PICmicro<sup>™</sup> Mid-Range MCU Family Reference Manual (DS33023).

Figure 5-1 is a block diagram of the Timer0 module and the prescaler shared with the WDT.

Timer0 operation is controlled through the OPTION\_REG register (Register 5-1 on the following page). Timer mode is selected by clearing bit TOCS (OPTION\_REG<5>). In Timer mode, the Timer0 module will increment every instruction cycle (without prescaler). If the TMR0 register is written, the increment is inhibited for the following two instruction cycles. The user can work around this by writing an adjusted value to the TMR0 register.

Counter mode is selected by setting bit T0CS (OPTION\_REG<5>). In Counter mode, Timer0 will increment, either on every rising or falling edge of pin RA4/T0CKI. The incrementing edge is determined by the Timer0 Source Edge Select bit T0SE (OPTION\_REG<4>). Clearing bit T0SE selects the rising edge. Restrictions on the external clock input are discussed in detail in Section 5.2.

The prescaler is mutually exclusively shared between the Timer0 module and the Watchdog Timer. The prescaler is not readable or writable. Section 5.3 details the operation of the prescaler.

## 5.1 Timer0 Interrupt

The TMR0 interrupt is generated when the TMR0 register overflows from FFh to 00h. This overflow sets bit TMR0IF (INTCON<2>). The interrupt can be masked by clearing bit TMR0IE (INTCON<5>). Bit TMR0IF must be cleared in software by the Timer0 module Interrupt Service Routine, before re-enabling this interrupt. The TMR0 interrupt cannot awaken the processor from SLEEP, since the timer is shut-off during SLEEP.

NOTES:

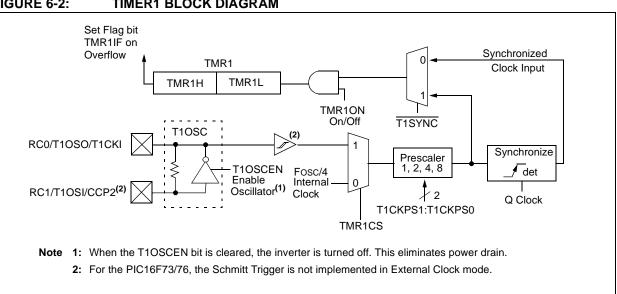

#### 6.1 **Timer1 Operation in Timer Mode**

Timer mode is selected by clearing the TMR1CS (T1CON<1>) bit. In this mode, the input clock to the timer is Fosc/4. The synchronize control bit T1SYNC (T1CON<2>) has no effect, since the internal clock is always in sync.

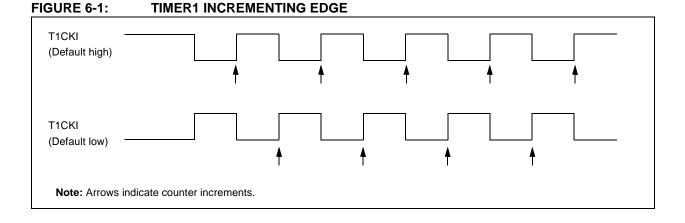

#### 6.2 **Timer1 Counter Operation**

Timer1 may operate in Asynchronous or Synchronous mode, depending on the setting of the TMR1CS bit.

When Timer1 is being incremented via an external source, increments occur on a rising edge. After Timer1 is enabled in Counter mode, the module must first have a falling edge before the counter begins to increment.

#### 6.3 **Timer1 Operation in Synchronized Counter Mode**

Counter mode is selected by setting bit TMR1CS. In this mode, the timer increments on every rising edge of clock input on pin RC1/T1OSI/CCP2, when bit T1OSCEN is set, or on pin RC0/T1OSO/T1CKI, when bit T1OSCEN is cleared.

If TISYNC is cleared, then the external clock input is synchronized with internal phase clocks. The synchronization is done after the prescaler stage. The prescaler stage is an asynchronous ripple counter.

In this configuration, during SLEEP mode, Timer1 will not increment even if the external clock is present, since the synchronization circuit is shut-off. The prescaler, however, will continue to increment.

#### FIGURE 6-2: TIMER1 BLOCK DIAGRAM

# PIC16F7X

# REGISTER 8-1: CCP1CON REGISTER/CCP2CON REGISTER (ADDRESS: 17h/1Dh)

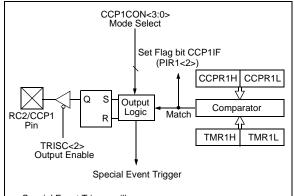

| bit 7-6                                                                                          | U-0<br>—                                                                                                 | U-0            | R/W-0<br>CCPxX               | R/W-0        | R/W-0        | R/W-0       | R/W-0       | R/W-0   |  |  |  |  |

|--------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------|----------------|------------------------------|--------------|--------------|-------------|-------------|---------|--|--|--|--|

| bit 7-6                                                                                          | —<br>bit 7                                                                                               | _              | CCDvV                        |              |              |             |             |         |  |  |  |  |

| Dit 7-6                                                                                          | bit 7                                                                                                    |                | COFXA                        | CCPxY        | CCPxM3       | CCPxM2      | CCPxM1      | CCPxM0  |  |  |  |  |

| bit 5-4 ()<br>()<br>()<br>()<br>()<br>()<br>()<br>()<br>()<br>()<br>()<br>()<br>()<br>(          |                                                                                                          |                |                              |              |              |             |             | bit 0   |  |  |  |  |

| ()<br>()<br>()<br>()<br>()<br>()<br>()<br>()<br>()<br>()<br>()<br>()<br>()<br>(                  | Unimplem                                                                                                 | ented: Rea     | ad as '0'                    |              |              |             |             |         |  |  |  |  |

| 1<br>1<br>1<br>2<br>2<br>2<br>2<br>1<br>2<br>1<br>2<br>1<br>1<br>1<br>1<br>1<br>1<br>1<br>1<br>1 | CCPxX:CC                                                                                                 | PxY: PWN       | l Least Signi                | ficant bits  |              |             |             |         |  |  |  |  |

| bit 3-0                                                                                          | <u>Capture mo</u><br>Unused                                                                              | ode:           |                              |              |              |             |             |         |  |  |  |  |

| -<br>bit 3-0                                                                                     | <u>Compare n</u><br>Unused                                                                               | <u>node:</u>   |                              |              |              |             |             |         |  |  |  |  |

| bit 3-0                                                                                          | PWM mode                                                                                                 | <del>)</del> : |                              |              |              |             |             |         |  |  |  |  |

|                                                                                                  | These bits                                                                                               | are the two    | LSbs of the                  | PWM duty     | cycle. The e | ight MSbs a | re found in | CCPRxL. |  |  |  |  |

| ,                                                                                                | CCPxM3:C                                                                                                 | CPxM0: C       | CPx Mode S                   | elect bits   |              |             |             |         |  |  |  |  |

|                                                                                                  | 0000 <b>= Ca</b>                                                                                         | oture/Comp     | oare/PWM di                  | sabled (rese | ets CCPx mo  | odule)      |             |         |  |  |  |  |

|                                                                                                  |                                                                                                          |                | , every fallin               |              |              |             |             |         |  |  |  |  |

| (                                                                                                | 0101 <b>= Ca</b>                                                                                         | pture mode     | , every rising               | g edge       |              |             |             |         |  |  |  |  |

| (                                                                                                | 0110 <b>= Ca</b>                                                                                         | pture mode     | , every 4th r                | ising edge   |              |             |             |         |  |  |  |  |

|                                                                                                  |                                                                                                          |                | , every 16th                 | •••          |              |             |             |         |  |  |  |  |

|                                                                                                  | 1000 = Compare mode, set output on match (CCPxIF bit is set)                                             |                |                              |              |              |             |             |         |  |  |  |  |

|                                                                                                  | 1001 = Compare mode, clear output on match (CCPxIF bit is set)                                           |                |                              |              |              |             |             |         |  |  |  |  |

| -                                                                                                | 1010 = Compare mode, generate software interrupt on match (CCPxIF bit is set, CCPx pin is<br>unaffected) |                |                              |              |              |             |             |         |  |  |  |  |

| :                                                                                                | CC                                                                                                       |                | e, trigger sp<br>ïmer1; CCP2 |              | •            |             | •           |         |  |  |  |  |

| :                                                                                                | 11xx = PW                                                                                                | /M mode        |                              |              |              |             |             |         |  |  |  |  |

|                                                                                                  |                                                                                                          |                |                              |              |              |             |             |         |  |  |  |  |

|                                                                                                  | Legend:                                                                                                  |                |                              |              |              |             |             |         |  |  |  |  |

| Legend:                  |                  |                      |                    |

|--------------------------|------------------|----------------------|--------------------|

| R = Readable bit         | W = Writable bit | U = Unimplemented    | bit, read as '0'   |

| - n = Value at POR reset | '1' = Bit is set | '0' = Bit is cleared | x = Bit is unknown |

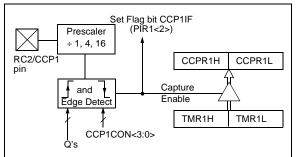

## 8.3 Capture Mode

In Capture mode, CCPR1H:CCPR1L captures the 16-bit value of the TMR1 register when an event occurs on pin RC2/CCP1. An event is defined as one of the following and is configured by CCPxCON<3:0>:

- · Every falling edge

- · Every rising edge

- Every 4th rising edge

- Every 16th rising edge

An event is selected by control bits CCP1M3:CCP1M0 (CCP1CON<3:0>). When a capture is made, the interrupt request flag bit CCP1IF (PIR1<2>) is set. The interrupt flag must be cleared in software. If another capture occurs before the value in register CCPR1 is read, the old captured value is overwritten by the new captured value.

## 8.3.1 CCP PIN CONFIGURATION

In Capture mode, the RC2/CCP1 pin should be configured as an input by setting the TRISC<2> bit.

**Note:** If the RC2/CCP1 pin is configured as an output, a write to the port can cause a capture condition.

#### FIGURE 8-1: CAPTURE MODE OPERATION BLOCK DIAGRAM

## 8.3.2 TIMER1 MODE SELECTION

Timer1 must be running in Timer mode or Synchronized Counter mode for the CCP module to use the capture feature. In Asynchronous Counter mode, the capture operation may not work.

## 8.3.3 SOFTWARE INTERRUPT

When the Capture mode is changed, a false capture interrupt may be generated. The user should keep bit CCP1IE (PIE1<2>) clear to avoid false interrupts and should clear the flag bit CCP1IF following any such change in operating mode.

## 8.3.4 CCP PRESCALER

There are four prescaler settings, specified by bits CCP1M3:CCP1M0. Whenever the CCP module is turned off, or the CCP module is not in Capture mode, the prescaler counter is cleared. Any RESET will clear the prescaler counter.

Switching from one capture prescaler to another may generate an interrupt. Also, the prescaler counter will not be cleared, therefore, the first capture may be from a non-zero prescaler. Example 8-1 shows the recommended method for switching between capture prescalers. This example also clears the prescaler counter and will not generate the "false" interrupt.

#### EXAMPLE 8-1: CHANGING BETWEEN CAPTURE PRESCALERS

| CLRF  | CCP1CON     | ;Turn CCP module off    |

|-------|-------------|-------------------------|

| MOVLW | NEW_CAPT_PS | ;Load the W reg with    |

|       |             | ;the new prescaler      |

|       |             | ;move value and CCP ON  |

| MOVWF | CCP1CON     | ;Load CCP1CON with this |

|       |             | ;value                  |

|       |             |                         |

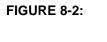

## 8.4 Compare Mode

In Compare mode, the 16-bit CCPR1 register value is constantly compared against the TMR1 register pair value. When a match occurs, the RC2/CCP1 pin is:

- Driven high

- Driven low

- Remains unchanged

The action on the pin is based on the value of control bits CCP1M3:CCP1M0 (CCP1CON<3:0>). At the same time, interrupt flag bit CCP1IF is set.

#### COMPARE MODE OPERATION BLOCK DIAGRAM

Special Event Trigger will: