# E·XFL

Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                   |

|----------------------------|--------------------------------------------------------------------------|

| Core Processor             | PIC                                                                      |

| Core Size                  | 8-Bit                                                                    |

| Speed                      | 20MHz                                                                    |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                                        |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                    |

| Number of I/O              | 22                                                                       |

| Program Memory Size        | 7KB (4K x 14)                                                            |

| Program Memory Type        | FLASH                                                                    |

| EEPROM Size                | -                                                                        |

| RAM Size                   | 192 x 8                                                                  |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 5.5V                                                                |

| Data Converters            | A/D 5x8b                                                                 |

| Oscillator Type            | External                                                                 |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                        |

| Mounting Type              | Surface Mount                                                            |

| Package / Case             | 28-VQFN Exposed Pad                                                      |

| Supplier Device Package    | 28-QFN (6x6)                                                             |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16lf73-i-ml |

|                            |                                                                          |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### Note the following details of the code protection feature on PICmicro<sup>®</sup> MCUs.

- The PICmicro family meets the specifications contained in the Microchip Data Sheet.

- Microchip believes that its family of PICmicro microcontrollers is one of the most secure products of its kind on the market today, when used in the intended manner and under normal conditions.

- There are dishonest and possibly illegal methods used to breach the code protection feature. All of these methods, to our knowledge, require using the PICmicro microcontroller in a manner outside the operating specifications contained in the data sheet. The person doing so may be engaged in theft of intellectual property.

- Microchip is willing to work with the customer who is concerned about the integrity of their code.

- Neither Microchip nor any other semiconductor manufacturer can guarantee the security of their code. Code protection does not mean that we are guaranteeing the product as "unbreakable".

- Code protection is constantly evolving. We at Microchip are committed to continuously improving the code protection features of our product.

If you have any further questions about this matter, please contact the local sales office nearest to you.

Information contained in this publication regarding device applications and the like is intended through suggestion only and may be superseded by updates. It is your responsibility to ensure that your application meets with your specifications. No representation or warranty is given and no liability is assumed by Microchip Technology Incorporated with respect to the accuracy or use of such information, or infringement of patents or other intellectual property rights arising from such use or otherwise. Use of Microchip's products as critical components in life support systems is not authorized except with express written approval by Microchip. No licenses are conveyed, implicitly or otherwise, under any intellectual property rights.

#### Trademarks

The Microchip name and logo, the Microchip logo, FilterLab, KEELOQ, MPLAB, PIC, PICmicro, PICMASTER, PICSTART, PRO MATE, SEEVAL and The Embedded Control Solutions Company are registered trademarks of Microchip Technology Incorporated in the U.S.A. and other countries.

dsPIC, ECONOMONITOR, FanSense, FlexROM, fuzzyLAB, In-Circuit Serial Programming, ICSP, ICEPIC, microID, microPort, Migratable Memory, MPASM, MPLIB, MPLINK, MPSIM, MXDEV, PICC, PICDEM, PICDEM.net, rfPIC, Select Mode and Total Endurance are trademarks of Microchip Technology Incorporated in the U.S.A.

Serialized Quick Term Programming (SQTP) is a service mark of Microchip Technology Incorporated in the U.S.A.

All other trademarks mentioned herein are property of their respective companies.

© 2002, Microchip Technology Incorporated, Printed in the U.S.A., All Rights Reserved.

Microchip received QS-9000 quality system certification for its worldwide headquarters, design and wafer fabrication facilities in Chandler and Tempe, Arizona in July 1999. The Company's quality system processes and procedures are QS-9000 compliant for its PICmicro® 8-bit MCUs, KEEL00® code hopping devices, Serial EEPROMs and microperipheral products. In addition, Microchip's quality system for the design and manufacture of development systems is ISO 9001 certified.

| Name    | Bit# | Buffer                | Function                                                                                                               |

|---------|------|-----------------------|------------------------------------------------------------------------------------------------------------------------|

| RB0/INT | bit0 | TTL/ST <sup>(1)</sup> | Input/output pin or external interrupt input. Internal software programmable weak pull-up.                             |

| RB1     | bit1 | TTL                   | Input/output pin. Internal software programmable weak pull-up.                                                         |

| RB2     | bit2 | TTL                   | Input/output pin. Internal software programmable weak pull-up.                                                         |

| RB3     | bit3 | TTL                   | Input/output pin. Internal software programmable weak pull-up.                                                         |

| RB4     | bit4 | TTL                   | Input/output pin (with interrupt-on-change). Internal software programmable weak pull-up.                              |

| RB5     | bit5 | TTL                   | Input/output pin (with interrupt-on-change). Internal software programmable weak pull-up.                              |

| RB6     | bit6 | TTL/ST <sup>(2)</sup> | Input/output pin (with interrupt-on-change).<br>Internal software programmable weak pull-up. Serial programming clock. |

| RB7     | bit7 | TTL/ST <sup>(2)</sup> | Input/output pin (with interrupt-on-change).<br>Internal software programmable weak pull-up. Serial programming data.  |

#### TABLE 4-3: PORTB FUNCTIONS

Legend: TTL = TTL input, ST = Schmitt Trigger input

Note 1: This buffer is a Schmitt Trigger input when configured as the external interrupt.

2: This buffer is a Schmitt Trigger input when used in Serial Programming mode.

#### TABLE 4-4: SUMMARY OF REGISTERS ASSOCIATED WITH PORTB

| Address   | Name       | Bit 7   | Bit 6                      | Bit 5     | Bit 4     | Bit 3     | Bit 2     | Bit 1 | Bit 0 | Value on:<br>POR,<br>BOR | Value on<br>all other<br>RESETS |

|-----------|------------|---------|----------------------------|-----------|-----------|-----------|-----------|-------|-------|--------------------------|---------------------------------|

| 06h, 106h | PORTB      | RB7     | RB6 RB5 RB4 RB3 RB2 RB1 RE |           | RB0       | xxxx xxxx | uuuu uuuu |       |       |                          |                                 |

| 86h, 186h | TRISB      | PORTB I | Data Directio              | 1111 1111 | 1111 1111 |           |           |       |       |                          |                                 |

| 81h, 181h | OPTION_REG | RBPU    | INTEDG                     | TOCS      | TOSE      | PSA       | PS2       | PS1   | PS0   | 1111 1111                | 1111 1111                       |

Legend: x = unknown, u = unchanged. Shaded cells are not used by PORTB.

| Name       | Bit# | Buffer Type           | Function                                                                                                                                                                                                                          |

|------------|------|-----------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

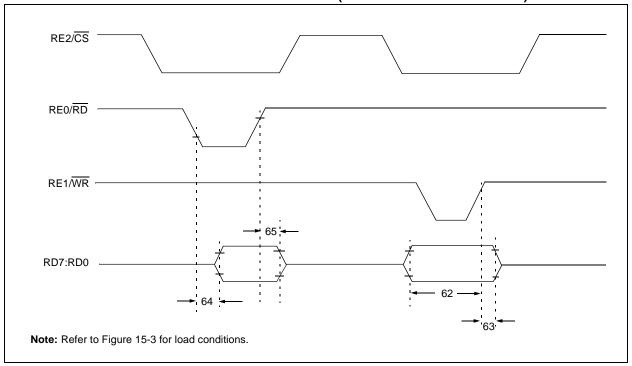

| RE0/RD/AN5 | bit0 | ST/TTL <sup>(1)</sup> | Input/output port pin or read control input in Parallel Slave Port mode or<br>analog input.<br>For RD (PSP mode):<br>1 = IDLE<br>0 = Read operation. Contents of PORTD register output to PORTD I/O<br>pins (if chip selected).   |

| RE1/WR/AN6 | bit1 | ST/TTL <sup>(1)</sup> | Input/output port pin or write control input in Parallel Slave Port mode<br>or analog input.<br>For WR (PSP mode):<br>1 = IDLE<br>0 = Write operation. Value of PORTD I/O pins latched into PORTD<br>register (if chip selected). |

| RE2/CS/AN7 | bit2 | ST/TTL <sup>(1)</sup> | Input/output port pin or chip select control input in Parallel Slave Port<br>mode or analog input.<br>For CS (PSP mode):<br>1 = Device is not selected<br>0 = Device is selected                                                  |

Legend: ST = Schmitt Trigger input, TTL = TTL input **Note 1:** Input buffers are Schmitt Triggers when in I/O mode and TTL buffers when in Parallel Slave Port mode.

| TABLE 4-10: SUMMARY OF REGISTERS ASSOCIATED WITH PORTE | <b>TABLE 4-10</b> : | SUMMARY OF REGISTERS ASSOCIATED WITH PORTE |

|--------------------------------------------------------|---------------------|--------------------------------------------|

|--------------------------------------------------------|---------------------|--------------------------------------------|

| Addr | Name   | Bit 7 | Bit 6 | Bit 5 | Bit 4   | Bit 3 | Bit 2 Bit 1 Bit 0 |             | Value on:<br>POR,<br>BOR | Value on all<br>other<br>RESETS |           |

|------|--------|-------|-------|-------|---------|-------|-------------------|-------------|--------------------------|---------------------------------|-----------|

| 09h  | PORTE  | —     | —     |       | —       |       | RE2               | RE1         | RE0                      | xxx                             | uuu       |

| 89h  | TRISE  | IBF   | OBF   | IBOV  | PSPMODE | _     | PORTE D           | ata Directi | on bits                  | 0000 -111                       | 0000 -111 |

| 9Fh  | ADCON1 | —     | _     |       | _       | _     | PCFG2             | PCFG1       | PCFG0                    | 000                             | 000       |

Legend: x = unknown, u = unchanged, - = unimplemented, read as '0'. Shaded cells are not used by PORTE.

#### 6.1 **Timer1 Operation in Timer Mode**

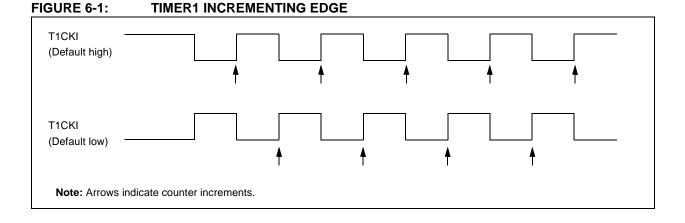

Timer mode is selected by clearing the TMR1CS (T1CON<1>) bit. In this mode, the input clock to the timer is Fosc/4. The synchronize control bit T1SYNC (T1CON<2>) has no effect, since the internal clock is always in sync.

#### 6.2 **Timer1 Counter Operation**

Timer1 may operate in Asynchronous or Synchronous mode, depending on the setting of the TMR1CS bit.

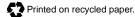

When Timer1 is being incremented via an external source, increments occur on a rising edge. After Timer1 is enabled in Counter mode, the module must first have a falling edge before the counter begins to increment.

#### 6.3 **Timer1 Operation in Synchronized Counter Mode**

Counter mode is selected by setting bit TMR1CS. In this mode, the timer increments on every rising edge of clock input on pin RC1/T1OSI/CCP2, when bit T1OSCEN is set, or on pin RC0/T1OSO/T1CKI, when bit T1OSCEN is cleared.

If TISYNC is cleared, then the external clock input is synchronized with internal phase clocks. The synchronization is done after the prescaler stage. The prescaler stage is an asynchronous ripple counter.

In this configuration, during SLEEP mode, Timer1 will not increment even if the external clock is present, since the synchronization circuit is shut-off. The prescaler, however, will continue to increment.

#### FIGURE 6-2: TIMER1 BLOCK DIAGRAM

#### 6.5 Timer1 Oscillator

A crystal oscillator circuit is built-in between pins T1OSI (input) and T1OSO (amplifier output). It is enabled by setting control bit T1OSCEN (T1CON<3>). The oscillator is a low power oscillator rated up to 200 kHz. It will continue to run during SLEEP. It is primarily intended for use with a 32 kHz crystal. Table 6-1 shows the capacitor selection for the Timer1 oscillator.

The Timer1 oscillator is identical to the LP oscillator. The user must provide a software time delay to ensure proper oscillator start-up.

#### 6.6 Resetting Timer1 using a CCP Trigger Output

If the CCP1 or CCP2 module is configured in Compare mode to generate a "special event trigger" (CCP1M3:CCP1M0 = '1011'), this signal will reset Timer1.

| Note: | The special event triggers from the CCP1 |

|-------|------------------------------------------|

|       | and CCP2 modules will not set interrupt  |

|       | flag bit TMR1IF (PIR1<0>).               |

Timer1 must be configured for either Timer or Synchronized Counter mode, to take advantage of this feature. If Timer1 is running in Asynchronous Counter mode, this RESET operation may not work.

In the event that a write to Timer1 coincides with a special event trigger from CCP1 or CCP2, the write will take precedence.

In this mode of operation, the CCPRxH:CCPRxL register pair effectively becomes the period register for Timer1.

#### 6.7 Resetting of Timer1 Register Pair (TMR1H, TMR1L)

TMR1H and TMR1L registers are not reset to 00h on a POR, or any other RESET, except by the CCP1 and CCP2 special event triggers.

## TABLE 6-1:CAPACITOR SELECTION FOR<br/>THE TIMER1 OSCILLATOR

|          | Frequency | Capacitors Used: |       |  |  |  |  |

|----------|-----------|------------------|-------|--|--|--|--|

| Osc Type | Frequency | OSC1             | OSC2  |  |  |  |  |

| LP       | 32 kHz    | 47 pF            | 47 pF |  |  |  |  |

|          | 100 kHz   | 33 pF            | 33 pF |  |  |  |  |

|          | 200 kHz   | 15 pF            | 15 pF |  |  |  |  |

| • •      |           |                  |       |  |  |  |  |

Capacitor values are for design guidance only.

These capacitors were tested with the crystals listed below for basic start-up and operation. These values were not optimized.

Different capacitor values may be required to produce acceptable oscillator operation. The user should test the performance of the oscillator over the expected VDD and temperature range for the application.

| See the notes (below) table for additional information. |

|---------------------------------------------------------|

|---------------------------------------------------------|

| Commonly Used Crystals:             |                                                                                                                                                                                                                                                                            |  |  |  |  |  |  |  |

|-------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|--|

| 32.768 kHz                          | Epson C-001R32.768K-A                                                                                                                                                                                                                                                      |  |  |  |  |  |  |  |

| 100 kHz                             | Epson C-2 100.00 KC-P                                                                                                                                                                                                                                                      |  |  |  |  |  |  |  |

| 200 kHz                             | STD XTL 200.000 kHz                                                                                                                                                                                                                                                        |  |  |  |  |  |  |  |

| of t<br>sta<br>2: Sin<br>cha<br>res | the capacitance increases the stability<br>the oscillator, but also increases the<br>rt-up time.<br>Ince each resonator/crystal has its own<br>aracteristics, the user should consult the<br>onator/crystal manufacturer for appro-<br>tate values of external components. |  |  |  |  |  |  |  |

T1CON register is reset to 00h on a Power-on Reset or a Brown-out Reset, which shuts off the timer and leaves a 1:1 prescale. In all other RESETS, the register is unaffected.

#### 6.8 Timer1 Prescaler

The prescaler counter is cleared on writes to the TMR1H or TMR1L registers.

| Address               | Name   | Bit 7                | Bit 6                                                                       | Bit 5   | Bit 4   | Bit 3   | Bit 2  | Bit 1  | Bit 0  | Value on:<br>POR,<br>BOR |      | Value on<br>all other<br>RESETS |      |

|-----------------------|--------|----------------------|-----------------------------------------------------------------------------|---------|---------|---------|--------|--------|--------|--------------------------|------|---------------------------------|------|

| 0Bh,8Bh,<br>10Bh,18Bh | INTCON | GIE                  | PEIE                                                                        | TMR0IE  | INTE    | RBIE    | TMR0IF | INTF   | RBIF   | 0000                     | 000x | 0000                            | 000u |

| 0Ch                   | PIR1   | PSPIF <sup>(1)</sup> | ADIF                                                                        | RCIF    | TXIF    | SSPIF   | CCP1IF | TMR2IF | TMR1IF | 0000                     | 0000 | 0000                            | 0000 |

| 8Ch                   | PIE1   | PSPIE <sup>(1)</sup> | ADIE                                                                        | RCIE    | TXIE    | SSPIE   | CCP1IE | TMR2IE | TMR1IE | 0000                     | 0000 | 0000                            | 0000 |

| 0Eh                   | TMR1L  | Holding re           | Holding register for the Least Significant Byte of the 16-bit TMR1 Register |         |         |         |        |        |        |                          | xxxx | uuuu                            | uuuu |

| 0Fh                   | TMR1H  | Holding re           | Holding register for the Most Significant Byte of the 16-bit TMR1 Register  |         |         |         |        |        |        |                          | xxxx | uuuu                            | uuuu |

| 10h                   | T1CON  | _                    | _                                                                           | T1CKPS1 | T1CKPS0 | T1OSCEN | T1SYNC | TMR1CS | TMR10N | 00                       | 0000 | uu                              | uuuu |

#### TABLE 6-2: REGISTERS ASSOCIATED WITH TIMER1 AS A TIMER/COUNTER

Legend: x = unknown, u = unchanged, - = unimplemented, read as '0'. Shaded cells are not used by the Timer1 module.

Note 1: Bits PSPIE and PSPIF are reserved on the PIC16F73/76; always maintain these bits clear.

## 8.0 CAPTURE/COMPARE/PWM MODULES

Each Capture/Compare/PWM (CCP) module contains a 16-bit register which can operate as a:

- 16-bit Capture register

- 16-bit Compare register

- PWM Master/Slave Duty Cycle register

Both the CCP1 and CCP2 modules are identical in operation, with the exception being the operation of the special event trigger. Table 8-1 and Table 8-2 show the resources and interactions of the CCP module(s). In the following sections, the operation of a CCP module is described with respect to CCP1. CCP2 operates the same as CCP1, except where noted.

#### 8.1 CCP1 Module

Capture/Compare/PWM Register1 (CCPR1) is comprised of two 8-bit registers: CCPR1L (low byte) and CCPR1H (high byte). The CCP1CON register controls the operation of CCP1. The special event trigger is generated by a compare match and will clear both TMR1H and TMR1L registers.

#### 8.2 CCP2 Module

Capture/Compare/PWM Register1 (CCPR1) is comprised of two 8-bit registers: CCPR1L (low byte) and CCPR1H (high byte). The CCP2CON register controls the operation of CCP2. The special event trigger is generated by a compare match; it will clear both TMR1H and TMR1L registers, and start an A/D conversion (if the A/D module is enabled).

Additional information on CCP modules is available in the PICmicro<sup>™</sup> Mid-Range MCU Family Reference Manual (DS33023) and in Application Note AN594, "Using the CCP Modules" (DS00594).

#### TABLE 8-1: CCP MODE - TIMER RESOURCES REQUIRED

| CCP Mode | Timer Resource |

|----------|----------------|

| Capture  | Timer1         |

| Compare  | Timer1         |

| PWM      | Timer2         |

#### TABLE 8-2:INTERACTION OF TWO CCP MODULES

| CCPx Mode | CCPy Mode | Interaction                                                                                           |

|-----------|-----------|-------------------------------------------------------------------------------------------------------|

| Capture   | Capture   | Same TMR1 time-base.                                                                                  |

| Capture   | Compare   | Same TMR1 time-base.                                                                                  |

| Compare   | Compare   | Same TMR1 time-base.                                                                                  |

| PWM       | PWM       | The PWMs will have the same frequency and update rate (TMR2 interrupt). The rising edges are aligned. |

| PWM       | Capture   | None.                                                                                                 |

| PWM       | Compare   | None.                                                                                                 |

| REGISTER 9-1: SSPSTAT: SYNC SERIAL PORT STATUS REGISTER (ADDRESS 94                                                                                   | ,                 |

|-------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------|

| R/W-0 R/W-0 R-0 R-0 R-0 R-0 R-0 R-0 R-0 R-0 R-0 R                                                                                                     | -0 R-0            |

| SMP CKE D/A P S R/W U                                                                                                                                 | A BF              |

| bit 7                                                                                                                                                 | bit C             |

| bit 7 SMP: SPI Data Input Sample Phase bit                                                                                                            |                   |

| SPI Master mode:                                                                                                                                      |                   |

| 1 = Input data sampled at end of data output time                                                                                                     |                   |

| 0 = Input data sampled at middle of data output time (Microwire®)                                                                                     |                   |

| <u>SPI Slave mode:</u><br>SMP must be cleared when SPI is used in Slave mode                                                                          |                   |

| I <sup>2</sup> C mode:                                                                                                                                |                   |

| This bit must be maintained clear                                                                                                                     |                   |

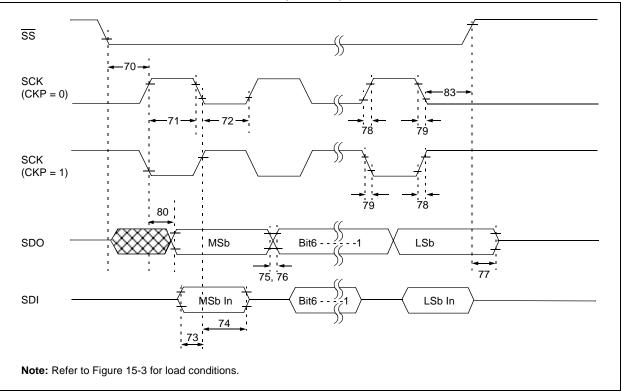

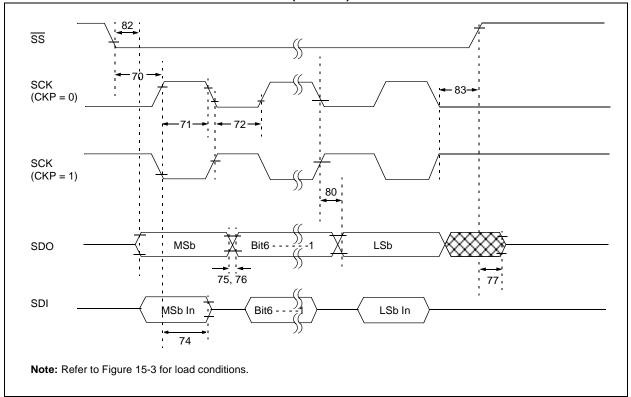

| bit 6 <b>CKE</b> : SPI Clock Edge Select bit (Figure 9-2, Figure 9-3, and Figure 9-4)                                                                 |                   |

| <u>SPI mode, CKP = 0:</u>                                                                                                                             |                   |

| <ul> <li>1 = Data transmitted on rising edge of SCK (Microwire<sup>®</sup> alternate)</li> <li>0 = Data transmitted on falling edge of SCK</li> </ul> |                   |

| SPI mode, $CKP = 1$ :                                                                                                                                 |                   |

| 1 = Data transmitted on falling edge of SCK (Microwire <sup>®</sup> default)                                                                          |                   |

| 0 = Data transmitted on rising edge of SCK                                                                                                            |                   |

| I <sup>2</sup> C mode:<br>This bit must be maintained clear                                                                                           |                   |

| bit 5 <b>D/A</b> : Data/Address bit (I <sup>2</sup> C mode only)                                                                                      |                   |

| 1 = Indicates that the last byte received or transmitted was data                                                                                     |                   |

| 0 = Indicates that the last byte received or transmitted was address                                                                                  |                   |

| bit 4 <b>P</b> : STOP bit (I <sup>2</sup> C mode only)                                                                                                |                   |

| This bit is cleared when the SSP module is disabled, or when the START bit is<br>SSPEN is cleared.                                                    | s detected last.  |

| 1 = Indicates that a STOP bit has been detected last (this bit is '0' on RESET)                                                                       |                   |

| 0 = STOP bit was not detected last                                                                                                                    |                   |

| bit 3 <b>S</b> : START bit (I <sup>2</sup> C mode only)                                                                                               |                   |

| This bit is cleared when the SSP module is disabled, or when the STOP bit is SSPEN is cleared.                                                        | detected last.    |

| 1 = Indicates that a START bit has been detected last (this bit is '0' on RESET                                                                       | )                 |

| 0 = START bit was not detected last                                                                                                                   |                   |

| bit 2 <b>R/W</b> : Read/Write bit Information (I <sup>2</sup> C mode only)                                                                            |                   |

| This bit holds the R/W bit information following the last address match. This bit i<br>the address match to the next START bit, STOP bit, or ACK bit. | s only valid from |

| 1 = Read                                                                                                                                              |                   |

| 0 = Write                                                                                                                                             |                   |

| bit 1 <b>UA</b> : Update Address bit (10-bit I <sup>2</sup> C mode only)                                                                              |                   |

| 1 = Indicates that the user needs to update the address in the SSPADD regist                                                                          | er                |

| <ul> <li>0 = Address does not need to be updated</li> <li>bit 0</li> <li><b>BF</b>: Buffer Full Status bit</li> </ul>                                 |                   |

| Receive (SPI and I <sup>2</sup> C modes):                                                                                                             |                   |

| 1 = Receive complete, SSPBUF is full                                                                                                                  |                   |

| 0 = Receive not complete, SSPBUF is empty                                                                                                             |                   |

| Transmit (I <sup>2</sup> C mode only):                                                                                                                |                   |

| 1 = Transmit in progress, SSPBUF is full                                                                                                              |                   |

| 0 = Transmit complete, SSPBUF is empty                                                                                                                |                   |

| Legend:                                                                                                                                               |                   |

| R = Readable bit W = Writable bit U = Unimplemented bit, rea                                                                                          | id as '0'         |

| - n = Value at POR reset $'1'$ = Bit is set $'0'$ = Bit is cleared x = B                                                                              | Bit is unknown    |

\_

|           | R/W-0                                                                        | R/W-0                                                                                                                                                                                                                                                                                                           | R/W-0                                      | R/W-0                                          | R/W-0                                              | R/W-0                                 | R/W-0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | R/W-0             |  |  |

|-----------|------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------|------------------------------------------------|----------------------------------------------------|---------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------|--|--|

|           | WCOL                                                                         | SSPOV                                                                                                                                                                                                                                                                                                           | SSPEN                                      | CKP                                            | SSPM3                                              |                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | SSPM0             |  |  |

|           | bit 7                                                                        | 331 0 1                                                                                                                                                                                                                                                                                                         |                                            | UN                                             | 30F 1013                                           |                                       | SPM2       SSPM1         e previous word       Iing the previous word         ling the previous word       Iing the previous date word         oid setting overflow eption (and transmostic the previous byte. in software in either is as serial port pins is         s as serial port pins is       Image: State of the previous byte in the pr | bit 0             |  |  |

| 1 : 1 - 7 |                                                                              |                                                                                                                                                                                                                                                                                                                 |                                            |                                                |                                                    |                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                   |  |  |

| bit 7     | 1 = The S                                                                    | be cleared i                                                                                                                                                                                                                                                                                                    | ster is writter                            | ו while it is stil                             | l transmittin                                      | g the previo                          | ous word                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                   |  |  |

| bit 6     | SSPOV: F                                                                     | Receive Ove                                                                                                                                                                                                                                                                                                     | rflow Indicate                             | or bit                                         |                                                    |                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                   |  |  |

|           | In SPI mo                                                                    |                                                                                                                                                                                                                                                                                                                 |                                            |                                                |                                                    |                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                   |  |  |

|           | of ove<br>must<br>Maste<br>initiate<br>0 = No ov                             | erflow, the da<br>read the SS<br>er mode, the<br>ed by writing<br>verflow                                                                                                                                                                                                                                       | ata in SSPSF<br>PBUF, even<br>overflow bit | R is lost. Overf<br>if only transmi            | flow can onl<br>tting data, t                      | y occur in S<br>o avoid sett          | Slave mode.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | The user<br>/. In |  |  |

|           |                                                                              | e is received<br>don't care" ir                                                                                                                                                                                                                                                                                 |                                            |                                                |                                                    |                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                   |  |  |

| bit 5     | <b>SSPEN</b> : S                                                             | Svnchronous                                                                                                                                                                                                                                                                                                     | Serial Port I                              | Enable bit                                     |                                                    |                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                   |  |  |

|           | <u>In SPI mo</u><br>1 = Enable<br>0 = Disabl<br><u>In I<sup>2</sup>C mod</u> | i <u>de:</u><br>es serial por<br>les serial po<br><u>de:</u>                                                                                                                                                                                                                                                    | t and configu<br>rt and configu            | ures SCK, SD0<br>ures these pin                | s as I/O poi                                       | rt pins                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                   |  |  |

|           |                                                                              |                                                                                                                                                                                                                                                                                                                 |                                            | nfigures the SI<br>ures these pin              |                                                    |                                       | rial port pine                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 6                 |  |  |

|           | In both mo                                                                   | odes, when a                                                                                                                                                                                                                                                                                                    | enabled, the                               | se pins must b                                 | e properly o                                       | configured a                          | as input or o                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | utput.            |  |  |

| bit 4     | CKP: Clock Polarity Select bit                                               |                                                                                                                                                                                                                                                                                                                 |                                            |                                                |                                                    |                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                   |  |  |

|           | <u>In SPI mo</u><br>1 = IDLE s                                               | de:<br>state for cloc                                                                                                                                                                                                                                                                                           | ck is a high le                            | evel (Microwire<br>vel (Microwire <sup>∉</sup> | e <sup>®</sup> default)<br><sup>®</sup> alternate) |                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                   |  |  |

|           | In I <sup>2</sup> C mod                                                      | <u>de:</u><br>ase control                                                                                                                                                                                                                                                                                       |                                            |                                                |                                                    |                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                   |  |  |

|           |                                                                              |                                                                                                                                                                                                                                                                                                                 | lock stretch)                              | . (Used to ens                                 | ure data se                                        | tup time.)                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                   |  |  |

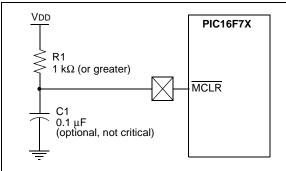

| bit 3-0   |                                                                              |                                                                                                                                                                                                                                                                                                                 | -                                          | rial Port Mode                                 |                                                    | , , , , , , , , , , , , , , , , , , , |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                   |  |  |