Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                          |

|----------------------------|--------------------------------------------------------------------------|

| Product Status             | Active                                                                   |

| Core Processor             | PIC                                                                      |

| Core Size                  | 8-Bit                                                                    |

| Speed                      | 20MHz                                                                    |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                                        |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                    |

| Number of I/O              | 22                                                                       |

| Program Memory Size        | 7KB (4K x 14)                                                            |

| Program Memory Type        | FLASH                                                                    |

| EEPROM Size                | -                                                                        |

| RAM Size                   | 192 x 8                                                                  |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 5.5V                                                                |

| Data Converters            | A/D 5x8b                                                                 |

| Oscillator Type            | External                                                                 |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                        |

| Mounting Type              | Surface Mount                                                            |

| Package / Case             | 28-SOIC (0.295", 7.50mm Width)                                           |

| Supplier Device Package    | 28-SOIC                                                                  |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16lf73-i-so |

|                            |                                                                          |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### 2.2.2.2 OPTION\_REG Register

The OPTION\_REG register is a readable and writable register, which contains various control bits to configure the TMR0 prescaler/WDT postscaler (single assignable register known also as the prescaler), the External INT Interrupt, TMR0 and the weak pull-ups on PORTB.

Note: To achieve a 1:1 prescaler assignment for the TMR0 register, assign the prescaler to the Watchdog Timer.

# **REGISTER 2-2: OPTION\_REG REGISTER (ADDRESS 81h, 181h)**

|                 | R/W-1       | R/W-1                                                                                                                                          | R/W-1       | R/W-1            | R/W-1          | R/W-1     | R/W-1        | R/W-1   |  |  |  |  |  |  |  |

|-----------------|-------------|------------------------------------------------------------------------------------------------------------------------------------------------|-------------|------------------|----------------|-----------|--------------|---------|--|--|--|--|--|--|--|

|                 | RBPU        | INTEDG                                                                                                                                         | TOCS        | T0SE             | PSA            | PS2       | PS1          | PS0     |  |  |  |  |  |  |  |

|                 | bit 7       |                                                                                                                                                |             |                  |                |           |              | bit 0   |  |  |  |  |  |  |  |

|                 |             |                                                                                                                                                |             |                  |                |           |              |         |  |  |  |  |  |  |  |

| bit 7           |             | DRTB Pull-up I                                                                                                                                 |             |                  |                |           |              |         |  |  |  |  |  |  |  |

|                 |             | B pull-ups are                                                                                                                                 |             | مرامينا ماريما م |                |           |              |         |  |  |  |  |  |  |  |

| <b>h</b> it C   |             | B pull-ups are                                                                                                                                 | •           | individual p     | ort latch valu | les       |              |         |  |  |  |  |  |  |  |

| bit 6           |             | Interrupt Edge                                                                                                                                 |             |                  |                |           |              |         |  |  |  |  |  |  |  |

|                 |             | ipt on rising eo<br>ipt on falling e                                                                                                           | •           | •                |                |           |              |         |  |  |  |  |  |  |  |

| bit 5           | TOCS: TM    | TOCS: TMR0 Clock Source Select bit                                                                                                             |             |                  |                |           |              |         |  |  |  |  |  |  |  |

|                 |             | 1 = Transition on RA4/T0CKI pin                                                                                                                |             |                  |                |           |              |         |  |  |  |  |  |  |  |

|                 |             | = Internal instruction cycle clock (CLKOUT)                                                                                                    |             |                  |                |           |              |         |  |  |  |  |  |  |  |

| bit 4           |             | T0SE: TMR0 Source Edge Select bit                                                                                                              |             |                  |                |           |              |         |  |  |  |  |  |  |  |

|                 |             | <ul> <li>1 = Increment on high-to-low transition on RA4/T0CKI pin</li> <li>0 = Increment on low-to-high transition on RA4/T0CKI pin</li> </ul> |             |                  |                |           |              |         |  |  |  |  |  |  |  |

| bit 3           |             | scaler Assignm                                                                                                                                 | -           |                  |                |           |              |         |  |  |  |  |  |  |  |

|                 | 1 = Presca  | aler is assigne                                                                                                                                | d to the WE |                  |                |           |              |         |  |  |  |  |  |  |  |

| <b>h</b> it 0 0 |             | aler is assigne                                                                                                                                |             |                  |                |           |              |         |  |  |  |  |  |  |  |

| bit 2-0         |             | Prescaler Rat                                                                                                                                  |             | -                |                |           |              |         |  |  |  |  |  |  |  |

|                 | Bit V       | alue TMR0 I                                                                                                                                    | Rate WDT    | Rate             |                |           |              |         |  |  |  |  |  |  |  |

|                 | 00          | 1.4                                                                                                                                            | 1:1         |                  |                |           |              |         |  |  |  |  |  |  |  |

|                 | 00<br>01    |                                                                                                                                                | 1:2         |                  |                |           |              |         |  |  |  |  |  |  |  |

|                 | 01          | 1.0                                                                                                                                            |             |                  |                |           |              |         |  |  |  |  |  |  |  |

|                 | 10          | 1.0                                                                                                                                            |             |                  |                |           |              |         |  |  |  |  |  |  |  |

|                 | 10<br>11    | 1.0                                                                                                                                            |             |                  |                |           |              |         |  |  |  |  |  |  |  |

|                 | 11          | 1.14                                                                                                                                           |             |                  |                |           |              |         |  |  |  |  |  |  |  |

|                 |             |                                                                                                                                                |             |                  |                |           |              |         |  |  |  |  |  |  |  |

|                 | Legend:     |                                                                                                                                                |             |                  |                |           |              |         |  |  |  |  |  |  |  |

|                 | R = Reada   | able bit                                                                                                                                       | W = W       | ritable bit      | U = Unimp      | olemented | bit, read as | '0'     |  |  |  |  |  |  |  |

|                 | - n = Value | e at POR rese                                                                                                                                  | t '1' = Bi  | t is set         | '0' = Bit is   | cleared   | x = Bit is ι | unknown |  |  |  |  |  |  |  |

|                 | L           |                                                                                                                                                |             |                  |                |           |              |         |  |  |  |  |  |  |  |

#### 2.2.2.4 PIE1 Register

The PIE1 register contains the individual enable bits for the peripheral interrupts.

Note: Bit PEIE (INTCON<6>) must be set to enable any peripheral interrupt.

# REGISTER 2-4: PIE1 REGISTER (ADDRESS 8Ch)

|              | R/W-0                                     | R/W-0                                                                      | R/W-0         | R/W-0        | R/W-0   | R/W-0  | R/W-0  | R/W-0  |  |  |  |  |  |  |

|--------------|-------------------------------------------|----------------------------------------------------------------------------|---------------|--------------|---------|--------|--------|--------|--|--|--|--|--|--|

|              | PSPIE <sup>(1)</sup>                      | ADIE                                                                       | RCIE          | TXIE         | SSPIE   | CCP1IE | TMR2IE | TMR1IE |  |  |  |  |  |  |

|              | bit 7                                     |                                                                            |               |              |         |        |        |        |  |  |  |  |  |  |

|              |                                           |                                                                            |               |              |         |        |        |        |  |  |  |  |  |  |

| bit 7        | PSPIE <sup>(1)</sup> :                    | PSPIE <sup>(1)</sup> : Parallel Slave Port Read/Write Interrupt Enable bit |               |              |         |        |        |        |  |  |  |  |  |  |

|              | 1 = Enable                                | 1 = Enables the PSP read/write interrupt                                   |               |              |         |        |        |        |  |  |  |  |  |  |

|              | 0 = Disables the PSP read/write interrupt |                                                                            |               |              |         |        |        |        |  |  |  |  |  |  |

| bit 6        | ADIE: A/D                                 | ADIE: A/D Converter Interrupt Enable bit                                   |               |              |         |        |        |        |  |  |  |  |  |  |

|              |                                           | es the A/D co                                                              |               |              |         |        |        |        |  |  |  |  |  |  |

|              | 0 = Disabl                                | es the A/D c                                                               | onverter inte | errupt       |         |        |        |        |  |  |  |  |  |  |

| bit 5        |                                           | ART Receive                                                                | •             |              |         |        |        |        |  |  |  |  |  |  |

|              |                                           | es the USAR                                                                |               | •            |         |        |        |        |  |  |  |  |  |  |

|              |                                           | es the USAF                                                                |               |              |         |        |        |        |  |  |  |  |  |  |

| bit 4        |                                           | RT Transmi                                                                 | -             |              |         |        |        |        |  |  |  |  |  |  |

|              |                                           | es the USAR                                                                |               |              |         |        |        |        |  |  |  |  |  |  |

| <b>h</b> # 0 |                                           | es the USAF                                                                |               |              | hla h:+ |        |        |        |  |  |  |  |  |  |

| bit 3        | •                                         | nchronous S                                                                |               | iterrupt Ena | DIE DIT |        |        |        |  |  |  |  |  |  |

|              |                                           | es the SSP in<br>es the SSP i                                              |               |              |         |        |        |        |  |  |  |  |  |  |

| bit 2        |                                           | CP1 Interru                                                                |               | i+           |         |        |        |        |  |  |  |  |  |  |

|              |                                           | es the CCP1                                                                | •             | it i         |         |        |        |        |  |  |  |  |  |  |

|              |                                           | es the CCP                                                                 | •             |              |         |        |        |        |  |  |  |  |  |  |

| bit 1        |                                           | MR2 to PR                                                                  |               | rrupt Enable | e bit   |        |        |        |  |  |  |  |  |  |

|              |                                           | es the TMR2                                                                |               | •            |         |        |        |        |  |  |  |  |  |  |

|              |                                           | es the TMR2                                                                |               |              |         |        |        |        |  |  |  |  |  |  |

| bit 0        | TMR1IE: T                                 | MR1 Overfl                                                                 | ow Interrupt  | Enable bit   |         |        |        |        |  |  |  |  |  |  |

|              |                                           | es the TMR1                                                                |               |              |         |        |        |        |  |  |  |  |  |  |

|              |                                           | es the TMR                                                                 |               | •            |         |        |        |        |  |  |  |  |  |  |

|              |                                           |                                                                            |               |              |         |        |        |        |  |  |  |  |  |  |

Note 1: PSPIE is reserved on 28-pin devices; always maintain this bit clear.

| Legend:                  |                  |                      |                    |

|--------------------------|------------------|----------------------|--------------------|

| R = Readable bit         | W = Writable bit | U = Unimplemented    | bit, read as '0'   |

| - n = Value at POR reset | '1' = Bit is set | '0' = Bit is cleared | x = Bit is unknown |

#### 3.0 **READING PROGRAM MEMORY**

The FLASH Program Memory is readable during normal operation over the entire VDD range. It is indirectly addressed through Special Function Registers (SFR). Up to 14-bit numbers can be stored in memory for use as calibration parameters, serial numbers, packed 7-bit ASCII, etc. Executing a program memory location containing data that forms an invalid instruction results in a NOP.

There are five SFRs used to read the program and memory. These registers are:

- PMCON1

- PMDATA

- PMDATH

- PMADR

- PMADRH

The program memory allows word reads. Program memory access allows for checksum calculation and reading calibration tables.

When interfacing to the program memory block, the PMDATH:PMDATA registers form a two-byte word, which holds the 14-bit data for reads. The PMADRH:PMADR registers form a two-byte word, which holds the 13-bit address of the FLASH location being accessed. These devices can have up to 8K words of program FLASH, with an address range from Oh to 3FFFh. The unused upper bits in both the PMDATH and PMADRH registers are not implemented and read as "0's".

#### 3.1 **PMADR**

The address registers can address up to a maximum of 8K words of program FLASH.

When selecting a program address value, the MSByte of the address is written to the PMADRH register and the LSByte is written to the PMADR register. The upper MSbits of PMADRH must always be clear.

#### 3.2 PMCON1 Register

PMCON1 is the control register for memory accesses.

The control bit RD initiates read operations. This bit cannot be cleared, only set, in software. It is cleared in hardware at the completion of the read operation.

#### **REGISTER 3-1:** PMCON1 REGISTER (ADDRESS 18Ch)

|         | R-1                                                                                                          | U-0         | U-0 | U-0 | U-x | U-0 | U-0 | R/S-0 |  |  |  |  |  |  |

|---------|--------------------------------------------------------------------------------------------------------------|-------------|-----|-----|-----|-----|-----|-------|--|--|--|--|--|--|

|         | reserved                                                                                                     | _           | —   | _   | _   | —   | —   | RD    |  |  |  |  |  |  |

|         | bit 7 bit 0                                                                                                  |             |     |     |     |     |     |       |  |  |  |  |  |  |

|         |                                                                                                              |             |     |     |     |     |     |       |  |  |  |  |  |  |

| bit 7   | Reserved: Read as '1'                                                                                        |             |     |     |     |     |     |       |  |  |  |  |  |  |

| bit 6-1 | Unimplemented: Read as '0'                                                                                   |             |     |     |     |     |     |       |  |  |  |  |  |  |

| bit 0   | RD: Read                                                                                                     | Control bit |     |     |     |     |     |       |  |  |  |  |  |  |

|         | 1 = Initiates a FLASH read, RD is cleared in hardware. The RD bit can only be set (not cleared) in software. |             |     |     |     |     |     |       |  |  |  |  |  |  |

|         | 0 = FLASH read completed                                                                                     |             |     |     |     |     |     |       |  |  |  |  |  |  |

|         | _                                                                                                            |             |     |     |     |     |     |       |  |  |  |  |  |  |

|         | Legend:                                                                                                      |             |     |     |     |     |     |       |  |  |  |  |  |  |

| Legend:                  |                  |                      |                    |

|--------------------------|------------------|----------------------|--------------------|

| R = Readable bit         | W = Writable bit | U = Unimplemented    | bit, read as '0'   |

| - n = Value at POR reset | '1' = Bit is set | '0' = Bit is cleared | x = Bit is unknown |

#### 5.2 Using Timer0 with an External Clock

When no prescaler is used, the external clock input is the same as the prescaler output. The synchronization of T0CKI, with the internal phase clocks, is accomplished by sampling the prescaler output on the Q2 and Q4 cycles of the internal phase clocks. Therefore, it is necessary for T0CKI to be high for at least 2Tosc (and a small RC delay of 20 ns) and low for at least 2Tosc (and a small RC delay of 20 ns). Refer to the electrical specification of the desired device.

| REGISTER 5-1: | <b>OPTION_REG REGISTER</b> |

|---------------|----------------------------|

|---------------|----------------------------|

|         | R/W-1                                                                                                            | R/W-1                                                | R/W-1        | R/W-1        | R/W-1      | R/W-1      | R/W-1        | R/W-1   |  |  |  |  |  |  |

|---------|------------------------------------------------------------------------------------------------------------------|------------------------------------------------------|--------------|--------------|------------|------------|--------------|---------|--|--|--|--|--|--|

|         | RBPU                                                                                                             | INTEDG                                               | TOCS         | T0SE         | PSA        | PS2        | PS1          | PS0     |  |  |  |  |  |  |

|         | bit 7                                                                                                            |                                                      |              |              |            |            |              | bit 0   |  |  |  |  |  |  |

|         |                                                                                                                  |                                                      |              |              |            |            |              |         |  |  |  |  |  |  |

| bit 7   | RBPU: PC                                                                                                         | ORTB Pull-up                                         | Enable bit   | (see Sectior | n 2.2.2.2) |            |              |         |  |  |  |  |  |  |

| bit 6   | INTEDG:                                                                                                          | Interrupt Edg                                        | e Select bit | (see Section | n 2.2.2.2) |            |              |         |  |  |  |  |  |  |

| bit 5   | TOCS: TM                                                                                                         | IR0 Clock Sc                                         | ource Select | bit          |            |            |              |         |  |  |  |  |  |  |

|         |                                                                                                                  | tion on T0Ck<br>al instruction                       |              | (CLKOUT)     |            |            |              |         |  |  |  |  |  |  |

| bit 4   | T0SE: TMR0 Source Edge Select bit                                                                                |                                                      |              |              |            |            |              |         |  |  |  |  |  |  |

|         | 1 = Increment on high-to-low transition on T0CKI pin                                                             |                                                      |              |              |            |            |              |         |  |  |  |  |  |  |

|         | 0 = Incren                                                                                                       | 0 = Increment on low-to-high transition on T0CKI pin |              |              |            |            |              |         |  |  |  |  |  |  |

| bit 3   | PSA: Prescaler Assignment bit                                                                                    |                                                      |              |              |            |            |              |         |  |  |  |  |  |  |

|         | <ul> <li>1 = Prescaler is assigned to the WDT</li> <li>0 = Prescaler is assigned to the Timer0 module</li> </ul> |                                                      |              |              |            |            |              |         |  |  |  |  |  |  |

| bit 2-0 | PS2:PS0:                                                                                                         | Prescaler R                                          | ate Select b | its          |            |            |              |         |  |  |  |  |  |  |

|         | Bit Value                                                                                                        | TMR0 Rate                                            | WDT Rate     |              |            |            |              |         |  |  |  |  |  |  |

|         | 000                                                                                                              | 1:2                                                  | 1:1          |              |            |            |              |         |  |  |  |  |  |  |

|         | 001                                                                                                              | 1:4<br>1:8                                           | 1:2<br>1:4   |              |            |            |              |         |  |  |  |  |  |  |

|         | 010<br>011                                                                                                       | 1:16                                                 | 1:4          |              |            |            |              |         |  |  |  |  |  |  |

|         | 100                                                                                                              | 1:32                                                 | 1:16         |              |            |            |              |         |  |  |  |  |  |  |

|         | 101                                                                                                              | 1:64                                                 | 1:32         |              |            |            |              |         |  |  |  |  |  |  |

|         | 110                                                                                                              | 1:128                                                | 1:64         |              |            |            |              |         |  |  |  |  |  |  |

|         | 111                                                                                                              | 1 : 256                                              | 1 : 128      |              |            |            |              |         |  |  |  |  |  |  |

|         | Legend:                                                                                                          |                                                      |              |              |            |            |              |         |  |  |  |  |  |  |

|         | R = Reada                                                                                                        | able bit                                             | W = V        | Vritable bit | U = Unii   | mplemented | bit, read as | '0'     |  |  |  |  |  |  |

|         | - n = Value                                                                                                      | e at POR res                                         | et '1' = B   | Bit is set   | '0' = Bit  | is cleared | x = Bit is ι | unknown |  |  |  |  |  |  |

|         |                                                                                                                  |                                                      |              |              |            |            |              |         |  |  |  |  |  |  |

|         |                                                                                                                  | To avoid ar                                          |              |              |            |            |              |         |  |  |  |  |  |  |

|         |                                                                                                                  | Example 5-1<br>caler assigni<br>even if the W        | ment betwee  | en Timer0 a  |            |            |              |         |  |  |  |  |  |  |

# 8.5 PWM Mode (PWM)

In Pulse Width Modulation mode, the CCPx pin produces up to a 10-bit resolution PWM output. Since the CCP1 pin is multiplexed with the PORTC data latch, the TRISC<2> bit must be cleared to make the CCP1 pin an output.

| Note: | Clearing the CCP1CON register will force  |

|-------|-------------------------------------------|

|       | the CCP1 PWM output latch to the default  |

|       | low level. This is not the PORTC I/O data |

|       | latch.                                    |

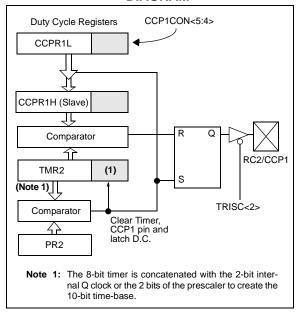

Figure 8-3 shows a simplified block diagram of the CCP module in PWM mode.

For a step-by-step procedure on how to set up the CCP module for PWM operation, see Section 8.5.3.

#### FIGURE 8-3: SIMPLIFIED PWM BLOCK DIAGRAM

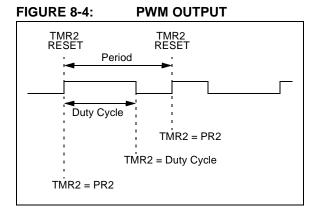

A PWM output (Figure 8-4) has a time-base (period) and a time that the output stays high (duty cycle). The frequency of the PWM is the inverse of the period (1/period).

#### 8.5.1 PWM PERIOD

The PWM period is specified by writing to the PR2 register. The PWM period can be calculated using the following formula:

$PWM period = [(PR2) + 1] \cdot 4 \cdot Tosc \cdot (TMR2 prescale value)$

PWM frequency is defined as 1 / [PWM period].

When TMR2 is equal to PR2, the following three events occur on the next increment cycle:

- TMR2 is cleared

- The CCP1 pin is set (exception: if PWM duty cycle = 0%, the CCP1 pin will not be set)

- The PWM duty cycle is latched from CCPR1L into CCPR1H

Note: The Timer2 postscaler (see Section 8.3) is not used in the determination of the PWM frequency. The postscaler could be used to have a servo update rate at a different frequency than the PWM output.

## 8.5.2 PWM DUTY CYCLE

The PWM duty cycle is specified by writing to the CCPR1L register and to the CCP1CON<5:4> bits. Up to 10-bit resolution is available. The CCPR1L contains the eight MSbs and the CCP1CON<5:4> contains the two LSbs. This 10-bit value is represented by CCPR1L:CCP1CON<5:4>. The following equation is used to calculate the PWM duty cycle in time:

```

PWM duty cycle = (CCPR1L:CCP1CON<5:4>)•

TOSC • (TMR2 prescale value)

```

CCPR1L and CCP1CON<5:4> can be written to at any time, but the duty cycle value is not latched into CCPR1H until after a match between PR2 and TMR2 occurs (i.e., the period is complete). In PWM mode, CCPR1H is a read only register.

The CCPR1H register and a 2-bit internal latch are used to double buffer the PWM duty cycle. This double buffering is essential for glitchless PWM operation.

When the CCPR1H and 2-bit latch match TMR2, concatenated with an internal 2-bit Q clock or 2 bits of the TMR2 prescaler, the CCP1 pin is cleared.

The maximum PWM resolution (bits) for a given PWM frequency is given by the formula:

Resolution =

$$\frac{\log(\frac{FOSC}{FPWM})}{\log(2)}$$

bits

Note: If the PWM duty cycle value is longer than the PWM period, the CCP1 pin will not be cleared.

#### 9.3.2 MASTER MODE

Master mode of operation is supported in firmware using interrupt generation on the detection of the START and STOP conditions. The STOP (P) and START (S) bits are cleared from a RESET or when the SSP module is disabled. The STOP (P) and START (S) bits will toggle based on the START and STOP conditions. Control of the I<sup>2</sup>C bus may be taken when the P bit is set, or the bus is IDLE and both the S and P bits are clear.

In Master mode, the SCL and SDA lines are manipulated by clearing the corresponding TRISC<4:3> bit(s). The output level is always low, irrespective of the value(s) in PORTC<4:3>. So when transmitting data, a '1' data bit must have the TRISC<4> bit set (input) and a '0' data bit must have the TRISC<4> bit cleared (output). The same scenario is true for the SCL line with the TRISC<3> bit. Pull-up resistors must be provided externally to the SCL and SDA pins for proper operation of the I<sup>2</sup>C module.

The following events will cause SSP Interrupt Flag bit, SSPIF, to be set (SSP Interrupt will occur if enabled):

- START condition

- STOP condition

- Data transfer byte transmitted/received

Master mode of operation can be done with either the Slave mode IDLE (SSPM3:SSPM0 = 1011), or with the Slave active. When both Master and Slave modes are enabled, the software needs to differentiate the source(s) of the interrupt.

#### 9.3.3 MULTI-MASTER MODE

In Multi-Master mode, the interrupt generation on the detection of the START and STOP conditions, allows the determination of when the bus is free. The STOP (P) and START (S) bits are cleared from a RESET or when the SSP module is disabled. The STOP (P) and START (S) bits will toggle based on the START and STOP conditions. Control of the  $I^2C$  bus may be taken when bit P (SSPSTAT<4>) is set, or the bus is IDLE and both the S and P bits clear. When the bus is busy, enabling the SSP Interrupt will generate the interrupt when the STOP condition occurs.

In Multi-Master operation, the SDA line must be monitored to see if the signal level is the expected output level. This check only needs to be done when a high level is output. If a high level is expected and a low level is present, the device needs to release the SDA and SCL lines (set TRISC<4:3>). There are two stages where this arbitration can be lost, these are:

- Address Transfer

- Data Transfer

When the slave logic is enabled, the slave continues to receive. If arbitration was lost during the address transfer stage, communication to the device may be in progress. If addressed, an ACK pulse will be generated. If arbitration was lost during the data transfer stage, the device will need to retransfer the data at a later time.

| Address                | Name    | Bit 7                | Bit 6              | Bit 5                  | Bit 4     | Bit 3     | Bit 2       | Bit 1  | Bit 0  | Value on:<br>POR,<br>BOR | Value on<br>all other<br>RESETS |

|------------------------|---------|----------------------|--------------------|------------------------|-----------|-----------|-------------|--------|--------|--------------------------|---------------------------------|

| 0Bh, 8Bh,<br>10Bh,18Bh | INTCON  | GIE                  | PEIE               | TMR0IE                 | INTE      | RBIE      | TMR0IF      | INTF   | RBIF   | 0000 000x                | 0000 000u                       |

| 0Ch                    | PIR1    | PSPIF <sup>(1)</sup> | ADIF               | RCIF                   | TXIF      | SSPIF     | CCP1IF      | TMR2IF | TMR1IF | 0000 0000                | 0000 0000                       |

| 8Ch                    | PIE1    | PSPIE <sup>(1)</sup> | ADIE               | RCIE                   | TXIE      | SSPIE     | CCP1IE      | TMR2IE | TMR1IE | 0000 0000                | 0000 0000                       |

| 13h                    | SSPBUF  | Synchrono            | us Serial          | Port Rece              | eive Buff | er/Transn | nit Registe | ər     |        | xxxx xxxx                | uuuu uuuu                       |

| 93h                    | SSPADD  | Synchrono            | us Serial          | Port (I <sup>2</sup> C | mode) A   | ddress R  | egister     |        |        | 0000 0000                | 0000 0000                       |

| 14h                    | SSPCON  | WCOL                 | SSPOV              | SSPEN                  | CKP       | SSPM3     | SSPM2       | SSPM1  | SSPM0  | 0000 0000                | 0000 0000                       |

| 94h                    | SSPSTAT | SMP <sup>(2)</sup>   | CKE <sup>(2)</sup> | D/A                    | Р         | S         | R/W         | UA     | BF     | 0000 0000                | 0000 0000                       |

| 87h                    | TRISC   | PORTC Da             | ata Direct         | •                      | 1111 1111 | 1111 1111 |             |        |        |                          |                                 |

TABLE 9-3:

REGISTERS ASSOCIATED WITH I<sup>2</sup>C OPERATION

Legend: x = unknown, u = unchanged, - = unimplemented locations read as '0'. Shaded cells are not used by SSP module in I<sup>2</sup>C mode. **Note 1:** PSPIF and PSPIE are reserved on the PIC16F73/76; always maintain these bits clear.

2: Maintain these bits clear in I<sup>2</sup>C mode.

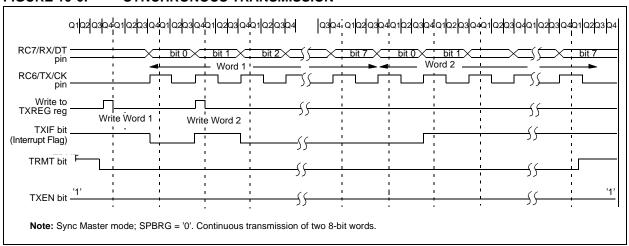

## FIGURE 10-6: SYNCHRONOUS TRANSMISSION

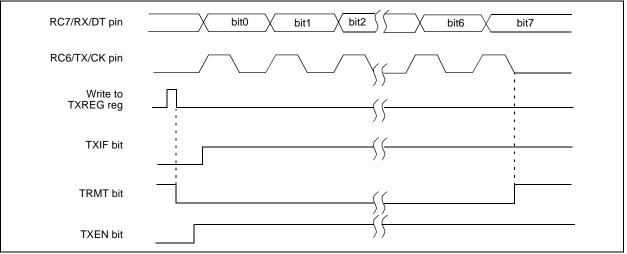

## FIGURE 10-7: SYNCHRONOUS TRANSMISSION (THROUGH TXEN)

#### TABLE 10-7: REGISTERS ASSOCIATED WITH SYNCHRONOUS MASTER TRANSMISSION

| Address                | Name   | Bit 7                | Bit 6     | Bit 5      | Bit 4 | Bit 3 | Bit 2  | Bit 1  | Bit 0  | Value on:<br>POR,<br>BOR | Value on<br>all other<br>RESETS |

|------------------------|--------|----------------------|-----------|------------|-------|-------|--------|--------|--------|--------------------------|---------------------------------|

| 0Bh, 8Bh,<br>10Bh,18Bh | INTCON | GIE                  | PEIE      | TMR0IE     | INTE  | RBIE  | TMR0IF | INTF   | RBIF   | 0000 000x                | 0000 000u                       |

| 0Ch                    | PIR1   | PSPIF <sup>(1)</sup> | ADIF      | RCIF       | TXIF  | SSPIF | CCP1IF | TMR2IF | TMR1IF | 0000 0000                | 0000 0000                       |

| 18h                    | RCSTA  | SPEN                 | RX9       | SREN       | CREN  | _     | FERR   | OERR   | RX9D   | 0000 -00x                | 0000 -00x                       |

| 19h                    | TXREG  | USART Tr             | ansmit Re | egister    |       |       |        |        |        | 0000 0000                | 0000 0000                       |

| 8Ch                    | PIE1   | PSPIE <sup>(1)</sup> | ADIE      | RCIE       | TXIE  | SSPIE | CCP1IE | TMR2IE | TMR1IE | 0000 0000                | 0000 0000                       |

| 98h                    | TXSTA  | CSRC                 | TX9       | TXEN       | SYNC  | _     | BRGH   | TRMT   | TX9D   | 0000 -010                | 0000 -010                       |

| 99h                    | SPBRG  | Baud Rate            | Generat   | or Registe | r     |       |        |        |        | 0000 0000                | 0000 0000                       |

Legend: x = unknown, - = unimplemented, read as '0'. Shaded cells are not used for synchronous master transmission.

Note 1: Bits PSPIE and PSPIF are reserved on the PIC16F73/76 devices; always maintain these bits clear.

# 11.7 Use of the CCP Trigger

An A/D conversion can be started by the "special event trigger" of the CCP2 module. This requires that the CCP2M3:CCP2M0 bits (CCP2CON<3:0>) be programmed as 1011 and that the A/D module is enabled (ADON bit is set). When the trigger occurs, the GO/DONE bit will be set, starting the A/D conversion, and the Timer1 counter will be reset to zero. Timer1 is reset to automatically repeat the A/D acquisition period with minimal software overhead (moving the ADRES to the desired location). The appropriate analog input channel must be selected and an appropriate acquisition time should pass before the "special event trigger" sets the GO/DONE bit (starts a conversion).

If the A/D module is not enabled (ADON is cleared), then the "special event trigger" will be ignored by the A/D module, but will still reset the Timer1 counter.

| Address                | Name                 | Bit 7                | Bit 6      | Bit 5   | Bit 4                         | Bit 3 | Bit 2    | Bit 1       | Bit 0   | Value on:<br>POR,<br>BOR | Value on<br>all other<br>RESETS |

|------------------------|----------------------|----------------------|------------|---------|-------------------------------|-------|----------|-------------|---------|--------------------------|---------------------------------|

| 0Bh,8Bh,<br>10Bh, 18Bh | INTCON               | GIE                  | PEIE       | TMR0IE  | INTE                          | RBIE  | TMR0IF   | INTF        | RBIF    | 0000 000x                | 0000 000u                       |

| 0Ch                    | PIR1                 | PSPIF <sup>(1)</sup> | ADIF       | RCIF    | TXIF                          | SSPIF | CCP1IF   | TMR2IF      | TMR1IF  | 0000 0000                | 0000 0000                       |

| 0Dh                    | PIR2                 |                      | _          | _       | _                             | —     |          | _           | CCP2IF  | 0                        | 0                               |

| 8Ch                    | PIE1                 | PSPIE <sup>(1)</sup> | ADIE       | RCIE    | TXIE                          | SSPIE | CCP1IE   | TMR2IE      | TMR1IE  | 0000 0000                | 0000 0000                       |

| 8Dh                    | PIE2                 |                      |            |         |                               |       | _        |             | CCP2IE  | 0                        | 0                               |

| 1Eh                    | ADRES                | A/D Resu             | It Registe | ər      |                               |       |          |             |         | XXXX XXXX                | uuuu uuuu                       |

| 1Fh                    | ADCON0               | ADCS1                | ADCS0      | CHS2    | CHS1                          | CHS0  | GO/DONE  | —           | ADON    | 0000 00-0                | 0000 00-0                       |

| 9Fh                    | ADCON1               | —                    | —          | —       | _                             |       | PCFG2    | PCFG1       | PCFG0   | 000                      | 000                             |

| 05h                    | PORTA                | —                    | _          | RA5     | RA4                           | RA3   | RA2      | RA1         | RA0     | 0x 0000                  | 0u 0000                         |

| 85h                    | TRISA                | —                    | _          | PORTA I | PORTA Data Direction Register |       |          |             |         |                          | 11 1111                         |

| 09h                    | PORTE <sup>(2)</sup> | _                    | _          | _       | _                             | _     | RE2      | RE1         | RE0     | xxx                      | uuu                             |

| 89h                    | TRISE <sup>(2)</sup> | IBF                  | OBF        | IBOV    | PSPMODE                       | _     | PORTE Da | ta Directio | on Bits | 0000 -111                | 0000 -111                       |

TABLE 11-2: SUMMARY OF A/D REGISTERS

Legend: x = unknown, u = unchanged, - = unimplemented, read as '0'. Shaded cells are not used for A/D conversion.

**Note** 1: Bits PSPIE and PSPIF are reserved on the PIC16F73/76; always maintain these bits clear.

2: These registers are reserved on the PIC16F73/76.

# 12.3 **RESET**

The PIC16F7X differentiates between various kinds of RESET:

- Power-on Reset (POR)

- MCLR Reset during normal operation

- MCLR Reset during SLEEP

- WDT Reset (during normal operation)

- WDT Wake-up (during SLEEP)

- Brown-out Reset (BOR)

Some registers are not affected in any RESET condition. Their status is unknown on POR and unchanged in any other RESET. Most other registers are reset to a "RESET state" on Power-on Reset (POR), on the MCLR and WDT Reset, on MCLR Reset during SLEEP, and Brown-out Reset (BOR). They are not affected by a WDT Wake-up, which is viewed as the resumption of normal operation. The TO and PD bits are set or cleared differently in different RESET situations, as indicated in Table 12-4. These bits are used in software to determine the nature of the RESET. See Table 12-6 for a full description of RESET states of all registers.

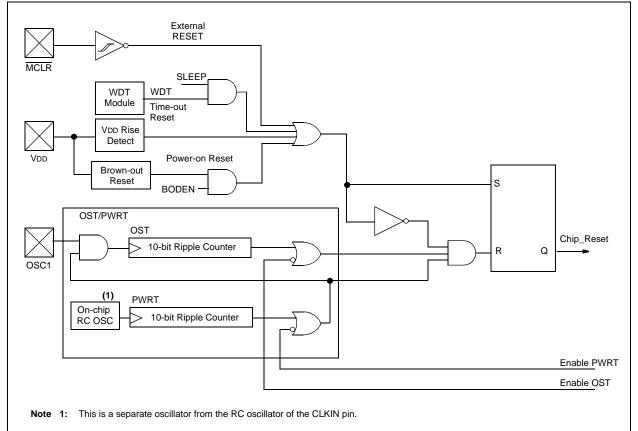

A simplified block diagram of the on-chip RESET circuit is shown in Figure 12-4.

# 12.4 MCLR

PIC16F7X devices have a noise filter in the  $\overline{\text{MCLR}}$ Reset path. The filter will detect and ignore small pulses.

It should be noted that a WDT Reset does not drive MCLR pin low.

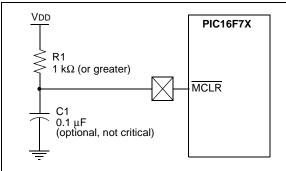

The behavior of the ESD protection on the  $\overline{\text{MCLR}}$  pin has been altered from previous devices of this family. Voltages applied to the pin that exceed its specification can result in both  $\overline{\text{MCLR}}$  Resets and excessive current beyond the device specification during the ESD event. For this reason, Microchip recommends that the  $\overline{\text{MCLR}}$ pin no longer be tied directly to VDD. The use of an RC network, as shown in Figure 12-5, is suggested.

# 12.5 Power-on Reset (POR)

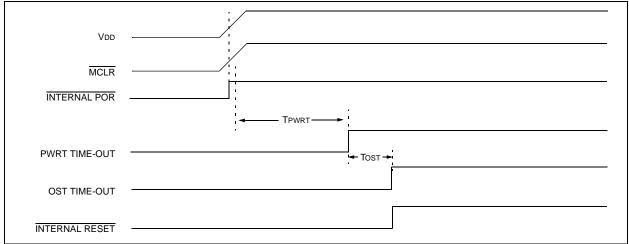

A Power-on Reset pulse is generated on-chip when VDD rise is detected (in the range of 1.2V - 1.7V). To take advantage of the POR, tie the MCLR pin to VDD as described in Section 12.4. A maximum rise time for VDD is specified. See the Electrical Specifications for details.

When the device starts normal operation (exits the RESET condition), device operating parameters (voltage, frequency, temperature,...) must be met to ensure operation. If these conditions are not met, the device must be held in RESET until the operating conditions are met. For additional information, refer to Application Note, AN607, "Power-up Trouble Shooting" (DS00607).

# 12.6 Power-up Timer (PWRT)

The Power-up Timer provides a fixed 72 ms nominal time-out on power-up only from the POR. The Power-up Timer operates on an internal RC oscillator. The chip is kept in RESET as long as the PWRT is active. The PWRT's time delay allows VDD to rise to an accept-able level. A configuration bit is provided to enable/ disable the PWRT.

The power-up time delay will vary from chip to chip, due to VDD, temperature and process variation. See DC parameters for details (TPWRT, parameter #33).

# 12.7 Oscillator Start-up Timer (OST)

The Oscillator Start-up Timer (OST) provides 1024 oscillator cycles (from OSC1 input) delay after the PWRT delay is over (if enabled). This helps to ensure that the crystal oscillator or resonator has started and stabilized.

The OST time-out is invoked only for XT, LP and HS modes and only on Power-on Reset, or wake-up from SLEEP.

# 12.8 Brown-out Reset (BOR)

The configuration bit, BODEN, can enable or disable the Brown-out Reset circuit. If VDD falls below VBOR (parameter D005, about 4V) for longer than TBOR (parameter #35, about 100  $\mu$ S), the brown-out situation will reset the device. If VDD falls below VBOR for less than TBOR, a RESET may not occur.

Once the brown-out occurs, the device will remain in Brown-out Reset until VDD rises above VBOR. The Power-up Timer then keeps the device in RESET for TPWRT (parameter #33, about 72 mS). If VDD should fall below VBOR during TPWRT, the Brown-out Reset process will restart when VDD rises above VBOR, with the Power-up Timer Reset. The Power-up Timer is always enabled when the Brown-out Reset circuit is enabled, regardless of the state of the PWRT configuration bit.

# 12.9 Time-out Sequence

On power-up, the time-out sequence is as follows: the PWRT delay starts (if enabled) when a POR Reset occurs. Then, OST starts counting 1024 oscillator cycles when PWRT ends (LP, XT, HS). When the OST ends, the device comes out of RESET.

If MCLR is kept low long enough, all delays will expire. Bringing MCLR high will begin execution immediately. This is useful for testing purposes or to synchronize more than one PIC16F7X device operating in parallel.

Table 12-5 shows the RESET conditions for the STATUS, PCON and PC registers, while Table 12-6 shows the RESET conditions for all the registers.

| Register            |    | Dev | rices |    | Power-on Reset,<br>Brown-out Reset | MCLR Reset,<br>WDT Reset | Wake-up via WDT or<br>Interrupt |

|---------------------|----|-----|-------|----|------------------------------------|--------------------------|---------------------------------|

| PIE2                | 73 | 74  | 76    | 77 | 0                                  | 0                        | u                               |

| PCON                | 73 | 74  | 76    | 77 | dd                                 | uu                       | uu                              |

| PR2                 | 73 | 74  | 76    | 77 | 1111 1111                          | 1111 1111                | 1111 1111                       |

| SSPSTAT             | 73 | 74  | 76    | 77 | 00 0000                            | 00 0000                  | uu uuuu                         |

| SSPADD              | 73 | 74  | 76    | 77 | 0000 0000                          | 0000 0000                | uuuu uuuu                       |

| TXSTA               | 73 | 74  | 76    | 77 | 0000 -010                          | 0000 -010                | uuuu -uuu                       |

| SPBRG               | 73 | 74  | 76    | 77 | 0000 0000                          | 0000 0000                | uuuu uuuu                       |

| ADCON1              | 73 | 74  | 76    | 77 | 000                                | 000                      | uuu                             |

| PMDATA              | 73 | 74  | 76    | 77 | 0 0000                             | 0 0000                   | u uuuu                          |

| PMADR               | 73 | 74  | 76    | 77 | xxxx xxxx                          | uuuu uuuu                | uuuu uuuu                       |

| PMDATH              | 73 | 74  | 76    | 77 | xxxx xxxx                          | uuuu uuuu                | uuuu uuuu                       |

| PMADRH              | 73 | 74  | 76    | 77 | xxxx xxxx                          | uuuu uuuu                | uuuu uuuu                       |

| PMCON1              | 73 | 74  | 76    | 77 | 10                                 | 10                       | 1u                              |

| La sua sa alu una a |    | •   |       | •  |                                    |                          |                                 |

TABLE 12-6: INITIALIZATION CONDITIONS FOR ALL REGISTERS (CONTINUED)

Legend: u = unchanged, x = unknown, - = unimplemented bit, read as '0', q = value depends on condition, r = reserved, maintain clear

Note 1: One or more bits in INTCON, PIR1 and/or PIR2 will be affected (to cause wake-up).

2: When the wake-up is due to an interrupt and the GIE bit is set, the PC is loaded with the interrupt vector (0004h).

3: See Table 12-5 for RESET value for specific condition.

# FIGURE 12-6: TIME-OUT SEQUENCE ON POWER-UP (MCLR TIED TO VDD THROUGH RC NETWORK)

# 12.14 Power-down Mode (SLEEP)

Power-down mode is entered by executing a  $\ensuremath{\mathtt{SLEEP}}$  instruction.

If enabled, the Watchdog Timer will be cleared but keeps running, the PD bit (STATUS<3>) is cleared, the TO (STATUS<4>) bit is set, and the oscillator driver is turned off. The I/O ports maintain the status they had before the SLEEP instruction was executed (driving high, low, or hi-impedance).

For lowest current consumption in this mode, place all I/O pins at either VDD or Vss, ensure no external circuitry is drawing current from the I/O pin, power-down the A/D and disable external clocks. Pull all I/O pins that are hi-impedance inputs, high or low externally, to avoid switching currents caused by floating inputs. The TOCKI input should also be at VDD or Vss for lowest current consumption. The contribution from on-chip pull-ups on PORTB should also be considered.

The  $\overline{\text{MCLR}}$  pin must be at a logic high level (VIHMC).

#### 12.14.1 WAKE-UP FROM SLEEP

The device can wake-up from SLEEP through one of the following events:

- 1. External RESET input on MCLR pin.

- 2. Watchdog Timer wake-up (if WDT was enabled).

- 3. Interrupt from INT pin, RB port change or a Peripheral Interrupt.

External MCLR Reset will cause a device RESET. All other events are considered a continuation of program execution and cause a "wake-up". The TO and PD bits in the STATUS register can be used to determine the cause of device RESET. The PD bit, which is set on power-up, is cleared when SLEEP is invoked. The TO bit is cleared if a WDT time-out occurred and caused wake-up.

The following peripheral interrupts can wake the device from SLEEP:

- 1. PSP read or write (PIC16F74/77 only).

- 2. TMR1 interrupt. Timer1 must be operating as an asynchronous counter.

- 3. CCP Capture mode interrupt.

- 4. Special event trigger (Timer1 in Asynchronous mode, using an external clock).

- 5. SSP (START/STOP) bit detect interrupt.

- SSP transmit or receive in Slave mode (SPI/I<sup>2</sup>C).

- 7. USART RX or TX (Synchronous Slave mode).

- 8. A/D conversion (when A/D clock source is RC).

Other peripherals cannot generate interrupts, since during SLEEP, no on-chip clocks are present.

When the SLEEP instruction is being executed, the next instruction (PC + 1) is pre-fetched. For the device to wake-up through an interrupt event, the corresponding interrupt enable bit must be set (enabled). Wake-up occurs, regardless of the state of the GIE bit. If the GIE bit is clear (disabled), the device continues execution at the instruction after the SLEEP instruction. If the GIE bit is set (enabled), the device executes the instruction after the SLEEP instruction and then branches to the interrupt address (0004h). In cases where the execution of the instruction following SLEEP is not desirable, the user should have a NOP after the SLEEP instruction.

## 12.14.2 WAKE-UP USING INTERRUPTS

When global interrupts are disabled (GIE cleared) and any interrupt source has both its interrupt enable bit and interrupt flag bit set, one of the following will occur:

- If the interrupt occurs **before** the execution of a SLEEP instruction, the SLEEP instruction will complete as a NOP. Therefore, the WDT and WDT postscaler will not be cleared, the TO bit will not be set and PD bits will not be cleared.

- If the interrupt occurs during or after the execution of a SLEEP instruction, the device will immediately wake-up from SLEEP. The SLEEP instruction will be completely executed before the wake-up. Therefore, the WDT and WDT postscaler will be cleared, the TO bit will be set and the PD bit will be cleared.

Even if the flag bits were checked before executing a SLEEP instruction, it may be possible for flag bits to become set before the SLEEP instruction completes. To determine whether a SLEEP instruction executed, test the PD bit. If the PD bit is set, the SLEEP instruction was executed as a NOP.

To ensure that the WDT is cleared, a CLRWDT instruction should be executed before a SLEEP instruction.

| DECFSZ           | Decrement f, Skip if 0                                                                                                                                                                                                                                                                                                       |

|------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [label] DECFSZ f,d                                                                                                                                                                                                                                                                                                           |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ d \in \ [0,1] \end{array}$                                                                                                                                                                                                                                                            |

| Operation:       | (f) - 1 $\rightarrow$ (destination);<br>skip if result = 0                                                                                                                                                                                                                                                                   |

| Status Affected: | None                                                                                                                                                                                                                                                                                                                         |

| Description:     | The contents of register 'f' are<br>decremented. If 'd' is 0, the result<br>is placed in the W register. If 'd' is<br>1, the result is placed back in<br>register 'f'.<br>If the result is 1, the next instruc-<br>tion is executed. If the result is 0,<br>then a NOP is executed instead,<br>making it a 2TCY instruction. |

| INCFSZ           | Increment f, Skip if 0                                                                                                                                                                                                                                                                                                  |  |  |

|------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Syntax:          | [label] INCFSZ f,d                                                                                                                                                                                                                                                                                                      |  |  |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ d \in \ [0,1] \end{array}$                                                                                                                                                                                                                                                       |  |  |

| Operation:       | (f) + 1 $\rightarrow$ (destination),<br>skip if result = 0                                                                                                                                                                                                                                                              |  |  |

| Status Affected: | None                                                                                                                                                                                                                                                                                                                    |  |  |

| Description:     | The contents of register 'f' are<br>incremented. If 'd' is 0, the result is<br>placed in the W register. If 'd' is 1,<br>the result is placed back in<br>register 'f'.<br>If the result is 1, the next instruc-<br>tion is executed. If the result is 0,<br>a NOP is executed instead, making<br>it a 2TCY instruction. |  |  |

| GOTO             | Unconditional Branch                                                                                                                                                                              |  |  |

|------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Syntax:          | [ <i>label</i> ] GOTO k                                                                                                                                                                           |  |  |

| Operands:        | $0 \le k \le 2047$                                                                                                                                                                                |  |  |

| Operation:       | $k \rightarrow PC<10:0>$<br>PCLATH<4:3> $\rightarrow$ PC<12:11>                                                                                                                                   |  |  |

| Status Affected: | None                                                                                                                                                                                              |  |  |

| Description:     | GOTO is an unconditional branch.<br>The eleven-bit immediate value is<br>loaded into PC bits <10:0>. The<br>upper bits of PC are loaded from<br>PCLATH<4:3>. GOTO is a two-<br>cycle instruction. |  |  |

| IORLW            | Inclusive OR Literal with W                                                                                               |  |

|------------------|---------------------------------------------------------------------------------------------------------------------------|--|

| Syntax:          | [ <i>label</i> ] IORLW k                                                                                                  |  |

| Operands:        | $0 \le k \le 255$                                                                                                         |  |

| Operation:       | (W) .OR. $k \rightarrow$ (W)                                                                                              |  |

| Status Affected: | Z                                                                                                                         |  |

| Description:     | The contents of the W register are<br>OR'ed with the eight-bit literal 'k'.<br>The result is placed in the W<br>register. |  |

| INCF             | Increment f                                                                                                                                                            | IORWF            | Inclusive OR W with f                                                                                                                                                   |

|------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [label] INCF f,d                                                                                                                                                       | Syntax:          | [ <i>label</i> ] IORWF f,d                                                                                                                                              |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ d \in \left[0,1\right] \end{array}$                                                                                             | Operands:        | 0 ≤ f ≤ 127<br>d ∈ [0,1]                                                                                                                                                |

| Operation:       | (f) + 1 $\rightarrow$ (destination)                                                                                                                                    | Operation:       | (W) .OR. (f) $\rightarrow$ (destination)                                                                                                                                |

| Status Affected: | Z                                                                                                                                                                      | Status Affected: | Z                                                                                                                                                                       |

| Description:     | The contents of register 'f' are<br>incremented. If 'd' is 0, the result<br>is placed in the W register. If 'd' is<br>1, the result is placed back in<br>register 'f'. | Description:     | Inclusive OR the W register with<br>register 'f'. If 'd' is 0, the result is<br>placed in the W register. If 'd' is 1,<br>the result is placed back in<br>register 'f'. |

| RLF              | Rotate Left f through Carry                                                                                                                                                                                   |

|------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [ <i>label</i> ] RLF f,d                                                                                                                                                                                      |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ d \in \left[0,1\right] \end{array}$                                                                                                                                    |

| Operation:       | See description below                                                                                                                                                                                         |

| Status Affected: | С                                                                                                                                                                                                             |

| Description:     | The contents of register 'f' are rotated<br>one bit to the left through the Carry<br>Flag. If 'd' is 0, the result is placed in<br>the W register. If 'd' is 1, the result is<br>stored back in register 'f'. |

# SLEEP

| Syntax:          | [label] SLEEP                                                                                                                                                                                                                        |

|------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Operands:        | None                                                                                                                                                                                                                                 |

| Operation:       | $\begin{array}{l} 00h \rightarrow WDT, \\ 0 \rightarrow WDT \text{ prescaler,} \\ 1 \rightarrow \overline{TO}, \\ 0 \rightarrow \overline{PD} \end{array}$                                                                           |

| Status Affected: | TO, PD                                                                                                                                                                                                                               |

| Description:     | The power-down status bit, $\overline{\text{PD}}$ is cleared. Time-out status bit, $\overline{\text{TO}}$ is set. Watchdog Timer and its prescaler are cleared.<br>The processor is put into SLEEP mode with the oscillator stopped. |

| RETURN           | Return from Subroutine                                                                                                                                     |  |  |

|------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Syntax:          | [label] RETURN                                                                                                                                             |  |  |

| Operands:        | None                                                                                                                                                       |  |  |

| Operation:       | $TOS\toPC$                                                                                                                                                 |  |  |

| Status Affected: | None                                                                                                                                                       |  |  |

| Description:     | Return from subroutine. The stack<br>is POPed and the top of the stack<br>(TOS) is loaded into the program<br>counter. This is a two-cycle<br>instruction. |  |  |

| RRF              | Rotate Right f through Carry                                                                                                                                                                                      |

|------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [ <i>label</i> ] RRF f,d                                                                                                                                                                                          |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ d \in \ [0,1] \end{array}$                                                                                                                                                 |

| Operation:       | See description below                                                                                                                                                                                             |

| Status Affected: | С                                                                                                                                                                                                                 |

| Description:     | The contents of register 'f' are<br>rotated one bit to the right through<br>the Carry Flag. If 'd' is 0, the result<br>is placed in the W register. If 'd' is<br>1, the result is placed back in<br>register 'f'. |

|                  | C Register f                                                                                                                                                                                                      |

| SUBLW            | Subtract W from Literal                                                                                                      |

|------------------|------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [ <i>label</i> ] SUBLW k                                                                                                     |

| Operands:        | $0 \le k \le 255$                                                                                                            |

| Operation:       | $k \text{ - (W)} \to (W)$                                                                                                    |

| Status Affected: | C, DC, Z                                                                                                                     |

| Description:     | The W register is subtracted (2's complement method) from the eight-bit literal 'k'. The result is placed in the W register. |

| SUBWF            | Subtract W from f                                                                                                                                                                       |  |

|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Syntax:          | [ <i>label</i> ] SUBWF f,d                                                                                                                                                              |  |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ d \in \ [0,1] \end{array}$                                                                                                                       |  |

| Operation:       | (f) - (W) $\rightarrow$ (destination)                                                                                                                                                   |  |