#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                          |

|----------------------------|--------------------------------------------------------------------------|

| Product Status             | Active                                                                   |

| Core Processor             | PIC                                                                      |

| Core Size                  | 8-Bit                                                                    |

| Speed                      | 20MHz                                                                    |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                                        |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                    |

| Number of I/O              | 22                                                                       |

| Program Memory Size        | 7KB (4K x 14)                                                            |

| Program Memory Type        | FLASH                                                                    |

| EEPROM Size                | -                                                                        |

| RAM Size                   | 192 x 8                                                                  |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 5.5V                                                                |

| Data Converters            | A/D 5x8b                                                                 |

| Oscillator Type            | External                                                                 |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                        |

| Mounting Type              | Through Hole                                                             |

| Package / Case             | 28-DIP (0.300", 7.62mm)                                                  |

| Supplier Device Package    | 28-SPDIP                                                                 |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16lf73-i-sp |

|                            |                                                                          |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

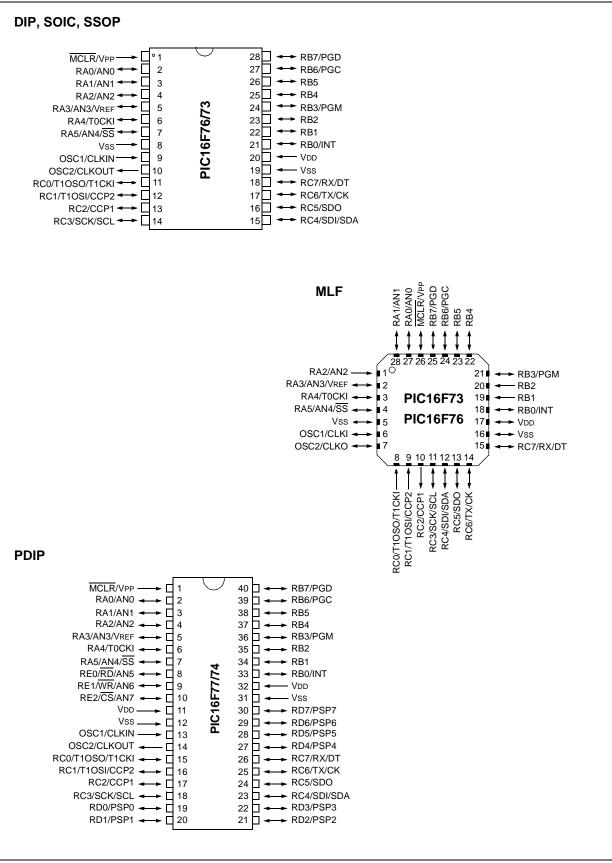

#### **Pin Diagrams**

#### 1.0 **DEVICE OVERVIEW**

This document contains device specific information about the following devices:

- PIC16F73

- PIC16F74

- PIC16F76

- PIC16F77

PIC16F73/76 devices are available only in 28-pin packages, while PIC16F74/77 devices are available in 40-pin and 44-pin packages. All devices in the PIC16F7X family share common architecture, with the following differences:

- The PIC16F73 and PIC16F76 have one-half of the total on-chip memory of the PIC16F74 and **PIC16F77**

- The 28-pin devices have 3 I/O ports, while the 40/44-pin devices have 5

- · The 28-pin devices have 11 interrupts, while the 40/44-pin devices have 12

- The 28-pin devices have 5 A/D input channels, while the 40/44-pin devices have 8

- The Parallel Slave Port is implemented only on the 40/44-pin devices

PIC16F7X DEVICE FEATURES **PIC16F74 PIC16F76 Key Features PIC16F73 PIC16F77 Operating Frequency** DC - 20 MHz DC - 20 MHz DC - 20 MHz DC - 20 MHz **RESETS** (and Delays) POR, BOR POR. BOR POR. BOR POR, BOR (PWRT, OST) (PWRT, OST) (PWRT, OST) (PWRT, OST) FLASH Program Memory 4K 4K 8K 8K (14-bit words) Data Memory (bytes) 368 192 192 368 Interrupts 11 12 11 12 I/O Ports Ports A,B,C Ports A,B,C Ports A,B,C,D,E Ports A,B,C,D,E Timers 3 3 3 3 Capture/Compare/PWM Modules 2 2 2 2 SSP, USART Serial Communications SSP, USART SSP. USART SSP, USART Parallel Communications PSP PSP 8-bit Analog-to-Digital Module **5 Input Channels** 8 Input Channels 5 Input Channels 8 Input Channels Instruction Set **35 Instructions 35 Instructions** 35 Instructions **35 Instructions** Packaging 28-pin DIP 40-pin PDIP 28-pin DIP 40-pin PDIP 28-pin SOIC 44-pin PLCC 28-pin SOIC 44-pin PLCC 28-pin SSOP 44-pin TQFP 28-pin SSOP 44-pin TQFP 28-pin MLF 28-pin MLF

#### **TABLE 1-1:**

The available features are summarized in Table 1-1. Block diagrams of the PIC16F73/76 and PIC16F74/77 devices are provided in Figure 1-1 and Figure 1-2, respectively. The pinouts for these device families are listed in Table 1-2 and Table 1-3.

Additional information may be found in the PICmicro™ Mid-Range Reference Manual (DS33023), which may be obtained from your local Microchip Sales Representative or downloaded from the Microchip website. The Reference Manual should be considered a complementary document to this data sheet, and is highly recommended reading for a better understanding of the device architecture and operation of the peripheral modules.

#### 2.2.2.4 PIE1 Register

The PIE1 register contains the individual enable bits for the peripheral interrupts.

Note: Bit PEIE (INTCON<6>) must be set to enable any peripheral interrupt.

## REGISTER 2-4: PIE1 REGISTER (ADDRESS 8Ch)

|              |                        | •                             |               | •             |             |        |        |        |

|--------------|------------------------|-------------------------------|---------------|---------------|-------------|--------|--------|--------|

|              | R/W-0                  | R/W-0                         | R/W-0         | R/W-0         | R/W-0       | R/W-0  | R/W-0  | R/W-0  |

|              | PSPIE <sup>(1)</sup>   | ADIE                          | RCIE          | TXIE          | SSPIE       | CCP1IE | TMR2IE | TMR1IE |

|              | bit 7                  |                               |               |               |             |        |        | bit 0  |

|              |                        |                               |               |               |             |        |        |        |

| bit 7        | PSPIE <sup>(1)</sup> : | Parallel Slav                 | e Port Read   | d/Write Inter | rupt Enable | bit    |        |        |

|              | 1 = Enable             | es the PSP r                  | ead/write int | terrupt       |             |        |        |        |

|              | 0 = Disabl             | es the PSP                    | read/write in | terrupt       |             |        |        |        |

| bit 6        | ADIE: A/D              | Converter I                   | nterrupt Ena  | able bit      |             |        |        |        |

|              |                        | es the A/D co                 |               |               |             |        |        |        |

|              | 0 = Disabl             | es the A/D c                  | onverter inte | errupt        |             |        |        |        |

| bit 5        |                        | ART Receive                   | •             |               |             |        |        |        |

|              |                        | es the USAR                   |               | •             |             |        |        |        |

|              |                        | es the USAF                   |               |               |             |        |        |        |

| bit 4        |                        | RT Transmi                    | -             |               |             |        |        |        |

|              |                        | es the USAR                   |               |               |             |        |        |        |

| <b>h</b> # 0 |                        | es the USAF                   |               |               | hla h:+     |        |        |        |

| bit 3        | •                      | nchronous S                   |               | iterrupt Ena  | DIE DIT     |        |        |        |

|              |                        | es the SSP in<br>es the SSP i |               |               |             |        |        |        |

| bit 2        |                        | CP1 Interru                   |               | i+            |             |        |        |        |

|              |                        | es the CCP1                   | •             | it i          |             |        |        |        |

|              |                        | es the CCP                    | •             |               |             |        |        |        |

| bit 1        |                        | MR2 to PR                     |               | rrupt Enable  | e bit       |        |        |        |

|              |                        | es the TMR2                   |               | •             |             |        |        |        |

|              |                        | es the TMR2                   |               |               |             |        |        |        |

| bit 0        | TMR1IE: T              | MR1 Overfl                    | ow Interrupt  | Enable bit    |             |        |        |        |

|              |                        | es the TMR1                   |               |               |             |        |        |        |

|              |                        | es the TMR'                   |               | •             |             |        |        |        |

|              |                        |                               |               |               |             |        |        |        |

Note 1: PSPIE is reserved on 28-pin devices; always maintain this bit clear.

| Legend:                  |                  |                      |                    |

|--------------------------|------------------|----------------------|--------------------|

| R = Readable bit         | W = Writable bit | U = Unimplemented    | bit, read as '0'   |

| - n = Value at POR reset | '1' = Bit is set | '0' = Bit is cleared | x = Bit is unknown |

x = Bit is unknown

#### **PCON Register** 2.2.2.8

The Power Control (PCON) register contains flag bits to allow differentiation between a Power-on Reset (POR), a Brown-out Reset (BOR), a Watchdog Reset (WDT) and an external MCLR Reset.

BOR is unknown on POR. It must be set by Note: the user and checked on subsequent RESETS to see if BOR is clear, indicating a brown-out has occurred. The BOR status bit is not predictable if the brown-out circuit is disabled (by clearing the BODEN bit in the configuration word).

#### **REGISTER 2-8:** PCON REGISTER (ADDRESS 8Eh)

- n = Value at POR reset

|         | U-0                                                                                   | U-0                            | U-0           | U-0            | U-0         | U-0         | R/W-0         | R/W-1   |  |  |  |  |  |

|---------|---------------------------------------------------------------------------------------|--------------------------------|---------------|----------------|-------------|-------------|---------------|---------|--|--|--|--|--|

|         | _                                                                                     | _                              | _             |                | —           |             | POR           | BOR     |  |  |  |  |  |

|         | bit 7                                                                                 |                                |               |                |             |             |               | bit 0   |  |  |  |  |  |

|         |                                                                                       |                                |               |                |             |             |               |         |  |  |  |  |  |

| bit 7-2 | Unimplem                                                                              | ented: Rea                     | d as '0'      |                |             |             |               |         |  |  |  |  |  |

| bit 1   | POR: Pow                                                                              | POR: Power-on Reset Status bit |               |                |             |             |               |         |  |  |  |  |  |

|         | 1 = No Power-on Reset occurred                                                        |                                |               |                |             |             |               |         |  |  |  |  |  |

|         | 0 = A Power-on Reset occurred (must be set in software after a Power-on Reset occurs) |                                |               |                |             |             |               |         |  |  |  |  |  |

| bit 0   | BOR: Brov                                                                             | vn-out Rese                    | t Status bit  |                |             |             |               |         |  |  |  |  |  |

|         | 1 = No Bro                                                                            | wn-out Res                     | et occurred   |                |             |             |               |         |  |  |  |  |  |

|         | 0 = A Brow                                                                            | n-out Rese                     | t occurred (m | lust be set in | software af | ter a Brown | -out Reset of | occurs) |  |  |  |  |  |

|         |                                                                                       |                                |               |                |             |             |               |         |  |  |  |  |  |

|         | Legend:                                                                               |                                |               |                |             |             |               |         |  |  |  |  |  |

|         | R = Reada                                                                             | ble bit                        | W = W         | ritable bit    | U = Unim    | plemented l | bit, read as  | '0'     |  |  |  |  |  |

'0' = Bit is cleared

'1' = Bit is set

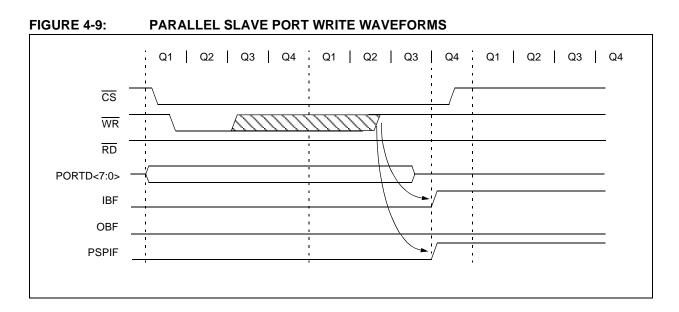

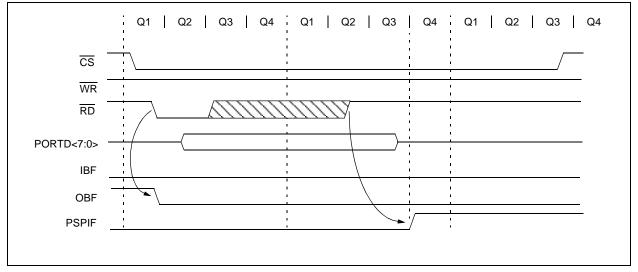

#### FIGURE 4-10: PARALLEL SLAVE PORT READ WAVEFORMS

#### TABLE 4-11: REGISTERS ASSOCIATED WITH PARALLEL SLAVE PORT

| Address | Name   | Bit 7                | Bit 6                                             | Bit 5 | Bit 4   | Bit 3 | Bit 2   | Bit 1                     | Bit 0  | Value on:<br>POR,<br>BOR | Value on<br>all other<br>RESETS |

|---------|--------|----------------------|---------------------------------------------------|-------|---------|-------|---------|---------------------------|--------|--------------------------|---------------------------------|

| 08h     | PORTD  | Port data I          | Port data latch when written: Port pins when read |       |         |       |         |                           |        | xxxx xxxx                | uuuu uuuu                       |

| 09h     | PORTE  | —                    |                                                   | —     |         | —     | RE2     | RE1                       | RE0    | xxx                      | uuu                             |

| 89h     | TRISE  | IBF                  | OBF                                               | IBOV  | PSPMODE | _     | PORTE D | PORTE Data Direction Bits |        | 0000 -111                | 0000 -111                       |

| 0Ch     | PIR1   | PSPIF <sup>(1)</sup> | ADIF                                              | RCIF  | TXIF    | SSPIF | CCP1IF  | TMR2IF                    | TMR1IF | 0000 0000                | 0000 0000                       |

| 8Ch     | PIE1   | PSPIE <sup>(1)</sup> | ADIE                                              | RCIE  | TXIE    | SSPIE | CCP1IE  | TMR2IE                    | TMR1IE | 0000 0000                | 0000 0000                       |

| 9Fh     | ADCON1 | _                    | _                                                 | _     | _       | _     | PCFG2   | PCFG1                     | PCFG0  | 000                      | 000                             |

Legend: x = unknown, u = unchanged, - = unimplemented, read as '0'. Shaded cells are not used by the Parallel Slave Port.

**Note 1:** Bits PSPIE and PSPIF are reserved on the PIC16F73/76; always maintain these bits clear.

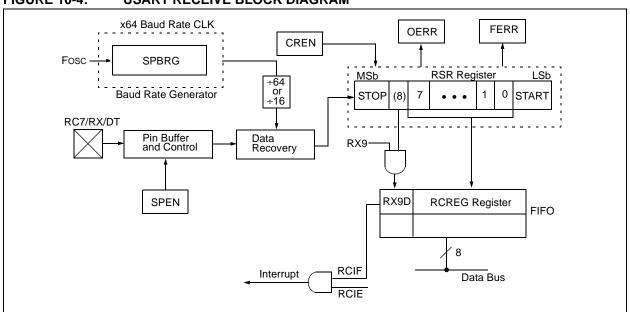

## 10.0 UNIVERSAL SYNCHRONOUS ASYNCHRONOUS RECEIVER TRANSMITTER (USART)

The Universal Synchronous Asynchronous Receiver Transmitter (USART) module is one of the two serial I/O modules. (USART is also known as a Serial Communications Interface or SCI.) The USART can be configured as a full duplex asynchronous system that can communicate with peripheral devices, such as CRT terminals and personal computers, or it can be configured as a half duplex synchronous system that can communicate with peripheral devices, such as A/D or D/A integrated circuits, serial EEPROMs, etc. The USART can be configured in the following modes:

- Asynchronous (full duplex)

- Synchronous Master (half duplex)

- Synchronous Slave (half duplex)

Bit SPEN (RCSTA<7>) and bits TRISC<7:6> have to be set in order to configure pins RC6/TX/CK and RC7/RX/DT as the Universal Synchronous Asynchronous Receiver Transmitter.

#### REGISTER 10-1: TXSTA: TRANSMIT STATUS AND CONTROL REGISTER (ADDRESS 98h)

|        | R/W-0                     | R/W-0                        | R/W-0         | R/W-0        | U-0      | R/W-0      | R-1          | R/W-0 |

|--------|---------------------------|------------------------------|---------------|--------------|----------|------------|--------------|-------|

|        | CSRC                      | TX9                          | TXEN          | SYNC         |          | BRGH       | TRMT         | TX9D  |

|        | bit 7                     |                              |               |              |          |            |              | bit 0 |

| bit 7  | CSRC: Clo                 | ock Source S                 | Select bit    |              |          |            |              |       |

|        | Asynchron                 | ous mode:                    |               |              |          |            |              |       |

|        | Don't care                |                              |               |              |          |            |              |       |

|        | Synchrono                 |                              |               |              |          |            |              |       |

|        |                           | · mode (clock<br>mode (clock |               |              | om BRG)  |            |              |       |

| bit 6  | <b>TX9</b> : 9-bit        | Transmit Ena                 | able bit      |              |          |            |              |       |

|        |                           | s 9-bit transn               |               |              |          |            |              |       |

| 1.11.5 |                           | s 8-bit transn               |               |              |          |            |              |       |

| bit 5  |                           | nsmit Enable<br>nit enabled  | e dit         |              |          |            |              |       |

|        |                           | nit disabled                 |               |              |          |            |              |       |

|        | Note:                     | SREN/CRE                     | N overrides   | TXEN in Sy   | nc mode. |            |              |       |

| bit 4  | SYNC: US                  | ART Mode S                   | Select bit    |              |          |            |              |       |

|        |                           | ronous mode                  |               |              |          |            |              |       |

|        | -                         | nronous mod                  |               |              |          |            |              |       |

| bit 3  | -                         | ented: Read                  |               |              |          |            |              |       |

| bit 2  | -                         | gh Baud Rate                 | e Select bit  |              |          |            |              |       |

|        | Asynchron                 |                              |               |              |          |            |              |       |

|        | 1 = High sp<br>0 = Low sp |                              |               |              |          |            |              |       |

|        | Synchrono                 |                              |               |              |          |            |              |       |

|        | Unused in                 |                              |               |              |          |            |              |       |

| bit 1  | TRMT: Tra                 | nsmit Shift R                | Register Stat | us bit       |          |            |              |       |

|        | 1 = TSR ei                |                              |               |              |          |            |              |       |

| 1 1 0  | 0 = TSR fu                |                              |               |              |          |            |              |       |

| bit 0  | Can be par                | bit of Transr                | nit Data      |              |          |            |              |       |

|        | oun be pu                 |                              |               |              |          |            |              |       |

|        | Legend:                   |                              |               |              |          |            |              |       |

|        | R = Reada                 | ble bit                      | W = W         | /ritable bit | U = Unir | nplemented | bit, read as | ʻ0'   |

| R = Readable bit         | W = Writable bit | U = Unimplemented bit, read as '0' |                    |  |  |  |

|--------------------------|------------------|------------------------------------|--------------------|--|--|--|

| - n = Value at POR reset | '1' = Bit is set | '0' = Bit is cleared               | x = Bit is unknown |  |  |  |

#### 10.2.2 USART ASYNCHRONOUS RECEIVER

The receiver block diagram is shown in Figure 10-4. The data is received on the RC7/RX/DT pin and drives the data recovery block. The data recovery block is actually a high speed shifter operating at x16 times the baud rate, whereas the main receive serial shifter operates at the bit rate, or at FOSC.

Once Asynchronous mode is selected, reception is enabled by setting bit CREN (RCSTA<4>).

The heart of the receiver is the receive (serial) shift register (RSR). After sampling the STOP bit, the received data in the RSR is transferred to the RCREG register (if it is empty). If the transfer is complete, flag bit RCIF (PIR1<5>) is set. The actual interrupt can be enabled/ disabled by setting/clearing enable bit RCIE (PIE1<5>). Flag bit RCIF is a read only bit which is cleared by the hardware. It is cleared when the RCREG register has been read and is empty. The RCREG is a double buffered register (i.e., it is a two deep FIFO). It is possible for two bytes of data to be received and transferred to the RCREG FIFO and a third byte to begin shifting to the RSR register. On the detection of the STOP bit of the third byte, if the RCREG register is still full, the overrun error bit OERR (RCSTA<1>) will be set. The word in the RSR will be lost. The RCREG register can be read twice to retrieve the two bytes in the FIFO. Overrun bit OERR has to be cleared in software. This is done by resetting the receive logic (CREN is cleared and then set). If bit OERR is set, transfers from the RSR register to the RCREG register are inhibited and no further data will be received, therefore, it is essential to clear error bit OERR if it is set. Framing error bit FERR (RCSTA<2>) is set if a STOP bit is detected as clear. Bit FERR and the 9th receive bit are buffered the same way as the receive data. Reading the RCREG will load bits RX9D and FERR with new values, therefore, it is essential for the user to read the RCSTA register before reading RCREG register, in order not to lose the old FERR and RX9D information.

NOTES:

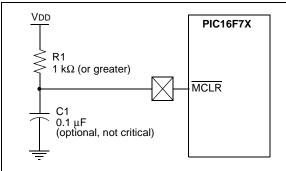

# 12.4 MCLR

PIC16F7X devices have a noise filter in the  $\overline{\text{MCLR}}$ Reset path. The filter will detect and ignore small pulses.

It should be noted that a WDT Reset does not drive MCLR pin low.

The behavior of the ESD protection on the  $\overline{\text{MCLR}}$  pin has been altered from previous devices of this family. Voltages applied to the pin that exceed its specification can result in both  $\overline{\text{MCLR}}$  Resets and excessive current beyond the device specification during the ESD event. For this reason, Microchip recommends that the  $\overline{\text{MCLR}}$ pin no longer be tied directly to VDD. The use of an RC network, as shown in Figure 12-5, is suggested.

#### 12.5 Power-on Reset (POR)

A Power-on Reset pulse is generated on-chip when VDD rise is detected (in the range of 1.2V - 1.7V). To take advantage of the POR, tie the MCLR pin to VDD as described in Section 12.4. A maximum rise time for VDD is specified. See the Electrical Specifications for details.

When the device starts normal operation (exits the RESET condition), device operating parameters (voltage, frequency, temperature,...) must be met to ensure operation. If these conditions are not met, the device must be held in RESET until the operating conditions are met. For additional information, refer to Application Note, AN607, "Power-up Trouble Shooting" (DS00607).

## 12.6 Power-up Timer (PWRT)

The Power-up Timer provides a fixed 72 ms nominal time-out on power-up only from the POR. The Power-up Timer operates on an internal RC oscillator. The chip is kept in RESET as long as the PWRT is active. The PWRT's time delay allows VDD to rise to an accept-able level. A configuration bit is provided to enable/ disable the PWRT.

The power-up time delay will vary from chip to chip, due to VDD, temperature and process variation. See DC parameters for details (TPWRT, parameter #33).

## 12.7 Oscillator Start-up Timer (OST)

The Oscillator Start-up Timer (OST) provides 1024 oscillator cycles (from OSC1 input) delay after the PWRT delay is over (if enabled). This helps to ensure that the crystal oscillator or resonator has started and stabilized.

The OST time-out is invoked only for XT, LP and HS modes and only on Power-on Reset, or wake-up from SLEEP.

### 12.8 Brown-out Reset (BOR)

The configuration bit, BODEN, can enable or disable the Brown-out Reset circuit. If VDD falls below VBOR (parameter D005, about 4V) for longer than TBOR (parameter #35, about 100  $\mu$ S), the brown-out situation will reset the device. If VDD falls below VBOR for less than TBOR, a RESET may not occur.

Once the brown-out occurs, the device will remain in Brown-out Reset until VDD rises above VBOR. The Power-up Timer then keeps the device in RESET for TPWRT (parameter #33, about 72 mS). If VDD should fall below VBOR during TPWRT, the Brown-out Reset process will restart when VDD rises above VBOR, with the Power-up Timer Reset. The Power-up Timer is always enabled when the Brown-out Reset circuit is enabled, regardless of the state of the PWRT configuration bit.

#### 12.9 Time-out Sequence

On power-up, the time-out sequence is as follows: the PWRT delay starts (if enabled) when a POR Reset occurs. Then, OST starts counting 1024 oscillator cycles when PWRT ends (LP, XT, HS). When the OST ends, the device comes out of RESET.

If MCLR is kept low long enough, all delays will expire. Bringing MCLR high will begin execution immediately. This is useful for testing purposes or to synchronize more than one PIC16F7X device operating in parallel.

Table 12-5 shows the RESET conditions for the STATUS, PCON and PC registers, while Table 12-6 shows the RESET conditions for all the registers.

| OSC1 //<br>CLKOUT <sup>(4)</sup>                    | Q1  Q2  Q3  Q4'; Q1 <br>\/                                     |                 | Q1  Q2  Q3  Q4 <br>\\_\_\_\ | ; Q1  Q2  Q3  Q4;<br>/~~~~~/<br>\/ | Q1  Q2  Q3  Q4; (<br> | 21  Q2  Q3  Q4'<br>\/_\/\_' |

|-----------------------------------------------------|----------------------------------------------------------------|-----------------|-----------------------------|------------------------------------|-----------------------|-----------------------------|

| INT pin                                             | 1                                                              |                 |                             | <u> </u>                           | <u> </u>              | I                           |

| INTF Flag<br>(INTCON<1>)                            |                                                                | <u>`</u>        |                             | Interrupt Latency<br>(Note 2)      |                       |                             |

| GIE bit<br>(INTCON<7>)                              | Processo<br>SLEEF                                              |                 |                             |                                    | i                     | <br><br>1                   |

| INSTRUCTION FLOW                                    | 1                                                              | · · · ·         | 1                           |                                    | 1                     | 1                           |

| PC X PC X                                           | PC+1 X                                                         | PC+2 X          | PC+2                        | <u> PC+2</u>                       | <u>    0004h    X</u> | 0005h                       |

| Instruction<br>Fetched Inst(PC) = SLEEP             | Inst(PC + 1)                                                   | 1<br>1<br>1     | Inst(PC + 2)                |                                    | Inst(0004h)           | Inst(0005h)                 |

| Instruction<br>Executed { Inst(PC - 1)              | SLEEP                                                          | 1<br>1<br>1     | Inst(PC + 1)                | Dummy cycle                        | Dummy cycle           | Inst(0004h)                 |

| 3: GIE = '1' assumed. In<br>If GIE = '0', execution | awing not to scale) This dela<br>this case after wake- up, the | e processor jum | ps to the interrup          | ot routine.                        |                       |                             |

#### FIGURE 12-12: WAKE-UP FROM SLEEP THROUGH INTERRUPT

12.15 Program Verification/Code Protection

If the code protection bit(s) have not been programmed, the on-chip program memory can be read out for verification purposes.

#### 12.16 ID Locations

Four memory locations (2000h - 2003h) are designated as ID locations, where the user can store checksum or other code identification numbers. These locations are not accessible during normal execution, but are readable and writable during program/verify. It is recommended that only the 4 Least Significant bits of the ID location are used.

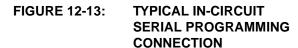

#### 12.17 In-Circuit Serial Programming

PIC16F7X microcontrollers can be serially programmed while in the end application circuit. This is simply done, with two lines for clock and data and three other lines for power, ground, and the programming voltage (see Figure 12-13 for an example). This allows customers to manufacture boards with unprogrammed devices, and then program the microcontroller just before shipping the product. This also allows the most recent firmware or a custom firmware to be programmed. For general information of serial programming, please refer to the In-Circuit Serial Programming (ICSP<sup>™</sup>) Guide (DS30277). For specific details on programming commands and operations for the PIC16F7X devices, please refer to the latest version of the PIC16F7X FLASH Program Memory Programming Specification (DS30324).

# PIC16F7X

| SWAPF            | Swap Nibbles in f                                                                                                                                                  |  |  |  |  |  |

|------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| Syntax:          | [label] SWAPF f,d                                                                                                                                                  |  |  |  |  |  |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ d \in \ [0,1] \end{array}$                                                                                                  |  |  |  |  |  |

| Operation:       | $(f<3:0>) \rightarrow (destination<7:4>), (f<7:4>) \rightarrow (destination<3:0>)$                                                                                 |  |  |  |  |  |

| Status Affected: | None                                                                                                                                                               |  |  |  |  |  |

| Description:     | The upper and lower nibbles of register 'f' are exchanged. If 'd' is 0, the result is placed in the W register. If 'd' is 1, the result is placed in register 'f'. |  |  |  |  |  |

| XORWF            | Exclusive OR W with f                                                                                                                                                       |  |  |  |

|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| Syntax:          | [label] XORWF f,d                                                                                                                                                           |  |  |  |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ d \in \left[0,1\right] \end{array}$                                                                                                  |  |  |  |

| Operation:       | (W) .XOR. (f) $\rightarrow$ (destination)                                                                                                                                   |  |  |  |

| Status Affected: | Z                                                                                                                                                                           |  |  |  |

| Description:     | Exclusive OR the contents of the W register with register 'f'. If 'd' is 0, the result is stored in the W register. If 'd' is 1, the result is stored back in register 'f'. |  |  |  |

| XORLW            | Exclusive OR Literal with W                                                                                                |  |  |  |  |  |

|------------------|----------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| Syntax:          | [ <i>label</i> ] XORLW k                                                                                                   |  |  |  |  |  |

| Operands:        | $0 \le k \le 255$                                                                                                          |  |  |  |  |  |

| Operation:       | (W) .XOR. $k \rightarrow (W)$                                                                                              |  |  |  |  |  |

| Status Affected: | Z                                                                                                                          |  |  |  |  |  |

| Description:     | The contents of the W register<br>are XOR'ed with the eight-bit<br>literal 'k'. The result is placed in<br>the W register. |  |  |  |  |  |

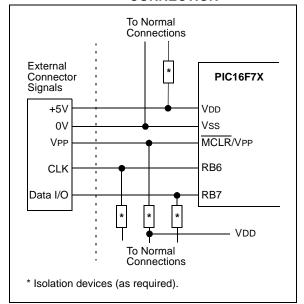

#### **FIGURE 15-9:** CAPTURE/COMPARE/PWM TIMINGS (CCP1 AND CCP2)

#### TABLE 15-5: CAPTURE/COMPARE/PWM REQUIREMENTS (CCP1 AND CCP2)

| Param<br>No. | Symbol |                  | Characteristic                | Min          | Тур†                  | Max | Units | Conditions |                                   |

|--------------|--------|------------------|-------------------------------|--------------|-----------------------|-----|-------|------------|-----------------------------------|

| 50*          | TccL   | CCP1 and CCP2    | No Prescaler                  |              | 0.5Tcy + 20           |     |       | ns         |                                   |

|              |        | nput low time    |                               | Standard(F)  | 10                    | —   |       | ns         |                                   |

|              |        | With Prescaler   | Extended(LF)                  | 20           | —                     |     | ns    |            |                                   |

| 51*          | ТссН   | CCP1 and CCP2    | No Prescaler                  |              | 0.5Tcy + 20           | —   |       | ns         |                                   |

|              |        | input high time  |                               | Standard(F)  | 10                    | —   |       | ns         |                                   |

|              |        |                  | With Prescaler                | Extended(LF) | 20                    | —   |       | ns         |                                   |

| 52*          | TccP   | CCP1 and CCP2 in | nput period                   |              | <u>3Tcy + 40</u><br>N | -   | _     | ns         | N = prescale<br>value (1,4 or 16) |

| 53*          | TccR   | CCP1 and CCP2 of | output rise time              | Standard(F)  | —                     | 10  | 25    | ns         |                                   |

|              |        |                  |                               | Extended(LF) | —                     | 25  | 50    | ns         |                                   |

| 54*          | TccF   | CCP1 and CCP2 of | CP1 and CCP2 output fall time |              | —                     | 10  | 25    | ns         |                                   |

|              |        |                  |                               | Extended(LF) | —                     | 25  | 45    | ns         |                                   |

These parameters are characterized but not tested.

† Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

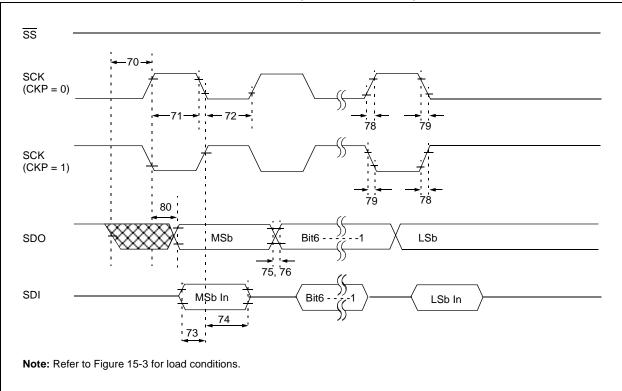

#### FIGURE 15-11: SPI MASTER MODE TIMING (CKE = 0, SMP = 0)

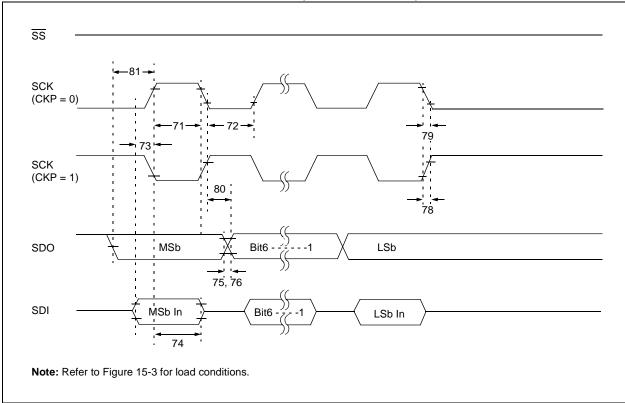

#### FIGURE 15-12: SPI MASTER MODE TIMING (CKE = 1, SMP = 1)

# TABLE 15-12: A/D CONVERTER CHARACTERISTICS: PIC16F7X (INDUSTRIAL, EXTENDED) PIC16LF7X (INDUSTRIAL)

| Param<br>No. | Sym                     | Characteristic                                 |           | Min        | Тур†       | Max        | Units    | Conditions                                                                                                             |

|--------------|-------------------------|------------------------------------------------|-----------|------------|------------|------------|----------|------------------------------------------------------------------------------------------------------------------------|

| A01          | Nr                      | Resolution PIC16F7X                            |           |            | _          | 8 bits     | bit      | $\begin{array}{l} \text{VREF} = \text{VDD} = 5.12\text{V},\\ \text{VSS} \leq \text{VAIN} \leq \text{VREF} \end{array}$ |

|              |                         |                                                | PIC16LF7X | —          | _          | 8 bits     | bit      | VREF = VDD = 2.2V                                                                                                      |

| A02          | Eabs                    | Total absolute error                           |           | —          | —          | < ±1       | LSb      | VREF = VDD = 5.12V,<br>VSS ≤ VAIN ≤ VREF                                                                               |

| A03          | EIL                     | Integral linearity error                       |           | —          | _          | < ±1       | LSb      | VREF = VDD = 5.12V,<br>VSS ≤ VAIN ≤ VREF                                                                               |

| A04          | Edl                     | Differential linearity error                   |           | —          | —          | < ±1       | LSb      | VREF = VDD = 5.12V,<br>$VSS \le VAIN \le VREF$                                                                         |

| A05          | Efs                     | Full scale error                               |           | —          | —          | < ±1       | LSb      | VREF = VDD = 5.12V,<br>$VSS \le VAIN \le VREF$                                                                         |

| A06          | EOFF                    | Offset error                                   |           | —          | —          | < ±1       | LSb      | VREF = VDD = 5.12V,<br>$VSS \le VAIN \le VREF$                                                                         |

| A10          | —                       | Monotonicity (No                               | ote 3)    | _          | guaranteed | _          | —        | $VSS \le VAIN \le VREF$                                                                                                |

| A20          | Vref                    | Reference voltage                              |           | 2.5<br>2.2 |            | 5.5<br>5.5 | V<br>V   | -40°C to +125°C<br>0°C to +125°C                                                                                       |

| A25          | VAIN                    | Analog input vol                               | age       | Vss - 0.3  |            | Vref + 0.3 | V        |                                                                                                                        |

| A30          | ZAIN                    | Recommended impedance of analog voltage source |           | —          | —          | 10.0       | kΩ       |                                                                                                                        |

| A40          | IAD                     | A/D conversion                                 | PIC16F7X  | _          | 180        | _          | μΑ       | Average current                                                                                                        |

|              | current (VDD) PIC16LF7X |                                                | PIC16LF7X |            | 90         | —          | μA       | consumption when A/D is on <b>(Note 1)</b> .                                                                           |

| A50          | IREF                    | VREF input current (Note 2)                    |           | N/A<br>—   |            | ±5<br>500  | μΑ<br>μΑ | During VAIN acquisition.<br>During A/D Conversion<br>cycle.                                                            |

\* These parameters are characterized but not tested.

† Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

**Note 1:** When A/D is off, it will not consume any current other than minor leakage current. The power-down current spec includes any such leakage from the A/D module.

2: VREF current is from the RA3 pin or the VDD pin, whichever is selected as a reference input.

**3:** The A/D conversion result never decreases with an increase in the input voltage and has no missing codes.

NOTES:

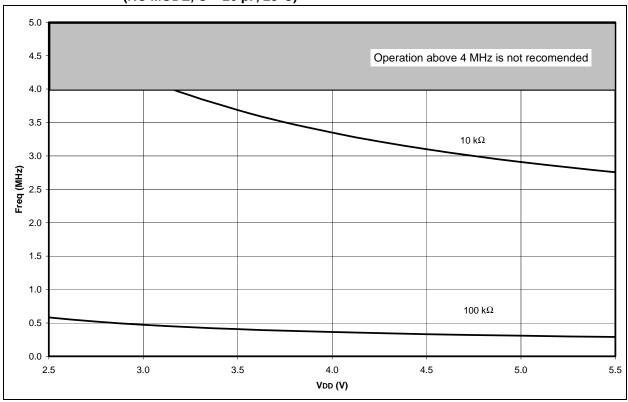

#### FIGURE 16-7: AVERAGE FOSC vs. VDD FOR VARIOUS VALUES OF R (RC MODE, C = 20 pF, 25°C)

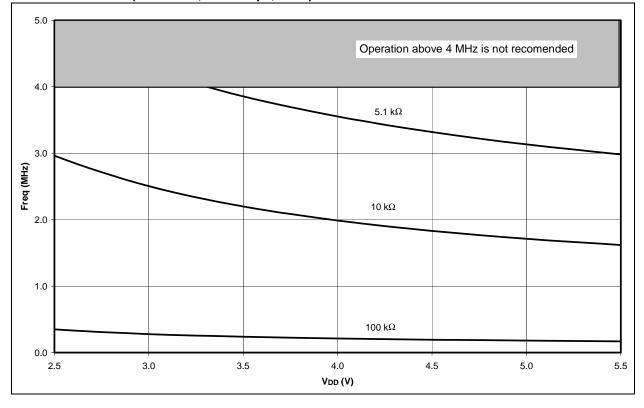

FIGURE 16-8: AVERAGE Fosc vs. VDD FOR VARIOUS VALUES OF R (RC MODE, C = 100 pF, 25°C)

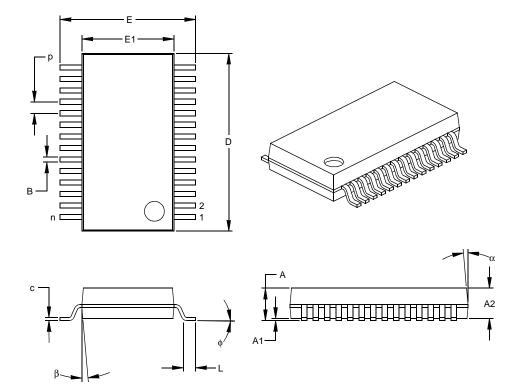

# 28-Lead Plastic Shrink Small Outline (SS) – 209 mil, 5.30 mm (SSOP)

|                           | INCHES   |      |      | MILLIMETERS* |       |        |        |

|---------------------------|----------|------|------|--------------|-------|--------|--------|

| Dimensior                 | n Limits | MIN  | NOM  | MAX          | MIN   | NOM    | MAX    |

| Number of Pins            | n        |      | 28   |              |       | 28     |        |

| Pitch                     | р        |      | .026 |              |       | 0.65   |        |

| Overall Height            | Α        | .068 | .073 | .078         | 1.73  | 1.85   | 1.98   |

| Molded Package Thickness  | A2       | .064 | .068 | .072         | 1.63  | 1.73   | 1.83   |

| Standoff §                | A1       | .002 | .006 | .010         | 0.05  | 0.15   | 0.25   |

| Overall Width             | Е        | .299 | .309 | .319         | 7.59  | 7.85   | 8.10   |

| Molded Package Width      | E1       | .201 | .207 | .212         | 5.11  | 5.25   | 5.38   |

| Overall Length            | D        | .396 | .402 | .407         | 10.06 | 10.20  | 10.34  |

| Foot Length               | L        | .022 | .030 | .037         | 0.56  | 0.75   | 0.94   |

| Lead Thickness            | С        | .004 | .007 | .010         | 0.10  | 0.18   | 0.25   |

| Foot Angle                | ¢        | 0    | 4    | 8            | 0.00  | 101.60 | 203.20 |

| Lead Width                | В        | .010 | .013 | .015         | 0.25  | 0.32   | 0.38   |

| Mold Draft Angle Top      | α        | 0    | 5    | 10           | 0     | 5      | 10     |

| Mold Draft Angle Bottom β |          | 0    | 5    | 10           | 0     | 5      | 10     |

\* Controlling Parameter § Significant Characteristic

Notes:

Dimensions D and E1 do not include mold flash or protrusions. Mold flash or protrusions shall not exceed .010" (0.254mm) per side. JEDEC Equivalent: MS-150 Drawing No. C04-073

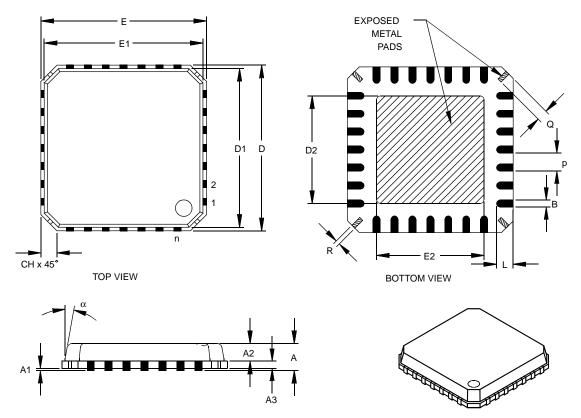

# 28-Lead Plastic Micro Leadframe Package (MF) 6x6 mm Body (MLF)

|                          | INCHES |          |           | MILLIMETERS*    |           |      |             |

|--------------------------|--------|----------|-----------|-----------------|-----------|------|-------------|

| Dimensi                  | MIN    | NOM      | MAX       | MIN             | NOM       | MAX  |             |

| Number of Pins           |        |          | 28        |                 |           | 28   |             |

| Pitch                    | р      | .026 BSC |           | 0.65 BSC        |           |      |             |

| Overall Height           | А      |          | .033      | .039            |           | 0.85 | 1.00        |

| Molded Package Thickness | A2     |          | .026      | .031            |           | 0.65 | 0.80        |

| Standoff                 | A1     | .000     | .0004     | .002            | 0.00      | 0.01 | 0.05        |

| Base Thickness A3        |        |          | .008 REF. |                 | 0.20 REF. |      |             |

| Overall Width E          |        | .236 BSC |           |                 | 6.00 BSC  |      |             |

| Molded Package Width E1  |        | .226 BSC |           |                 | 5.75 BSC  |      |             |

| Exposed Pad Width        | E2     | .140     | .146      | .152            | 3.55      | 3.70 | 3.85        |

| Overall Length           | D      | .236 BSC |           |                 | 6.00 BSC  |      |             |

| Molded Package Length    | D1     |          | .226 BSC  |                 | 5.75 BSC  |      |             |

| Exposed Pad Length       | D2     | .140     | .146      | .152            | 3.55      | 3.70 | 3.85        |

| Lead Width               | В      | .009     | .011      | .014            | 0.23      | 0.28 | 0.35        |

| Lead Length              | L      | .020     | .024      | .030            | 0.50      | 0.60 | 0.75        |

| Tie Bar Width            | R      | .005     | .007      | .010            | 0.13      | 0.17 | 0.23        |

| Tie Bar Length           | Q      | .012     | .016      | .026            | 0.30      | 0.40 | 0.65        |

| Chamfer                  | СН     | .009     | .017      | .024            | 0.24      | 0.42 | 0.60        |

| Mold Draft Angle Top     | α      |          |           | 12 <sup>°</sup> |           |      | 12 <b>°</b> |

A3

\*Controlling Parameter

Notes:

Dimensions D and E1 do not include mold flash or protrusions. Mold flash or protrusions shall not exceed .010" (0.254mm) per side. JEDEC equivalent: pending

Drawing No. C04-114

# APPENDIX A: REVISION HISTORY

| Version | Date | Revision Description                                                                                                                                                                      |

|---------|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| A       | 2000 | This is a new data sheet. How-<br>ever, these devices are similar to<br>the PIC16C7X devices found in<br>the PIC16C7X Data Sheet<br>(DS30390) or the PIC16F87X<br>devices (DS30292).      |

| В       | 2001 | Final data sheet. Includes device<br>characterization data. Addition of<br>extended temperature devices.<br>Addition of 28-pin MLF package.<br>Minor typographic revisions<br>throughout. |

# APPENDIX B: DEVICE DIFFERENCES

The differences between the devices in this data sheet are listed in Table B-1.

### TABLE B-1:DEVICE DIFFERENCES

| Difference                             | PIC16F73                                                | PIC16F74                                  | PIC16F76                                                | PIC16F77                                  |

|----------------------------------------|---------------------------------------------------------|-------------------------------------------|---------------------------------------------------------|-------------------------------------------|

| FLASH Program Memory<br>(14-bit words) | 4K                                                      | 4K                                        | 8K                                                      | 8K                                        |

| Data Memory (bytes)                    | 192                                                     | 192                                       | 368                                                     | 368                                       |

| I/O Ports                              | 3                                                       | 5                                         | 3                                                       | 5                                         |

| A/D                                    | 5 channels,<br>8 bits                                   | 8 channels,<br>8 bits                     | 5 channels,<br>8 bits                                   | 8 channels,<br>8 bits                     |

| Parallel Slave Port                    | no                                                      | yes                                       | no                                                      | yes                                       |

| Interrupt Sources                      | 11                                                      | 12                                        | 11                                                      | 12                                        |

| Packages                               | 28-pin PDIP<br>28-pin SOIC<br>28-pin SSOP<br>28-pin MLF | 40-pin PDIP<br>44-pin TQFP<br>44-pin PLCC | 28-pin PDIP<br>28-pin SOIC<br>28-pin SSOP<br>28-pin MLF | 40-pin PDIP<br>44-pin TQFP<br>44-pin PLCC |

| PORTE Register                          |      |        | . 37 |

|-----------------------------------------|------|--------|------|

| Postscaler, WDT                         |      |        |      |

| Assignment (PSA bit)                    |      |        |      |

| Rate Select (PS2:PS0 bits)              |      |        | . 20 |

| Power-down Mode. See SLEEP              |      |        |      |

| Power-on Reset (POR)89,                 |      |        |      |

| Oscillator Start-up Timer (OST)         |      | 89,    | 94   |

| POR Status (POR bit)                    |      |        | .25  |

| Power Control (PCON) Register           |      |        | .95  |

| Power-down (PD bit)                     |      |        | .93  |

| Power-up Timer (PWRT)                   |      | 89,    | 94   |

| Time-out (TO bit)                       |      |        |      |

| PR2 Register                            |      |        | .51  |

| Prescaler, Timer0                       |      |        |      |

| Assignment (PSA bit)                    |      |        | .20  |

| Rate Select (PS2:PS0 bits)              |      |        |      |

| PRO MATE II Universal Device Programmer |      |        |      |

| Program Counter                         |      |        |      |

| RESET Conditions                        |      |        | . 95 |

| Program Memory                          |      |        |      |

| Associated Registers                    |      |        |      |

| Interrupt Vector                        |      |        | .13  |

| Memory and Stack Maps                   |      |        |      |

| Operation During Code Protect           |      |        |      |

| Organization                            |      |        |      |

| Paging                                  |      |        |      |

| PMADR Register                          |      |        |      |

| PMADRH Register                         |      |        |      |

| Reading FLASH                           |      |        |      |

| Reading, PMADR Register                 |      |        |      |

| Reading, PMADRH Register                |      |        |      |

| Reading, PMCON1 Register                |      |        |      |

| Reading, PMDATA Register                |      |        |      |

| Reading, PMDATH Register                |      |        |      |

| RESET Vector                            |      |        |      |

| Program Verification                    |      |        |      |

| Programming Pin (VPP)                   |      |        |      |

| Programming, Device Instructions        |      |        |      |

| PUSH                                    |      |        |      |

|                                         |      |        |      |

| R                                       |      |        |      |

| R/W bit                                 | .60. | 66.    | 67   |

|                                         |      | ο<br>Ω |      |

| RA0/AN0 Pin          | 8, | 10 |

|----------------------|----|----|

| RA1/AN1 Pin          | 8, | 10 |

| RA2/AN2 Pin          | 8, | 10 |

| RA3/AN3/VREF Pin     | 8, | 10 |

| RA4/T0CKI Pin        |    |    |

| RA5/SS/AN4 Pin       |    |    |

| RAM. See Data Memory | ĺ  |    |

| RB0/INT Pin          | 9, | 11 |

| RB1 Pin              | 9, | 11 |

| RB2 Pin              | 9, | 11 |

| RB3/PGM Pin          | 9, | 11 |

| RB4 Pin              | 9, | 11 |

| RB5 Pin              | 9, | 11 |

| RB6/PGC Pin          | 9, | 11 |

| RB7/PGD Pin          | 9, | 11 |

| RC0/T1OSO/T1CKI Pin  | 9, | 11 |

| RC1/T1OSI/CCP2 Pin   |    |    |

| RC2/CCP1 Pin         |    |    |

| RC3/SCK/SCL Pin      | 9, | 11 |

| RC4/SDI/SDA Pin      | 9, | 11 |

| RC5/SDO Pin          | 9, | 11 |

| RC6/TX/CK Pin        |    |    |

| RC7/RX/DT Pin        | 9, | 11 |

|                      |    |    |

| RCSTA Register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                            |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------|

| CREN bit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                            |

| OERR bit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                            |

| SPEN bit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                            |

| SREN bit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                            |

| RD0/PSP0 Pin                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                            |

| RD1/PSP1 Pin                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                            |

| RD2/PSP2 Pin                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                            |

| RD3/PSP3 Pin                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                            |

| RD4/PSP4 Pin                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                            |

| RD5/PSP5 Pin<br>RD6/PSP6 Pin                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                            |

| RD7/PSP7 Pin                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                            |

| RE0/RD/AN5 Pin                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                            |

| RE1/WR/AN6 Pin                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                            |

| RE2/CS/AN7 Pin                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                            |

| Read-Modify-Write Operations                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                            |

| Receive Overflow Indicator bit (SSPOV)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                            |

| Register File                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                            |

| Registers                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                            |

| ADCON0 (A/D Control 0)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 83                         |

| ADCON0 (A/D Control 0) Register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                            |

| ADCON1 (A/D Control 1)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                            |

| ADCON1 (A/D Control 1) Register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                            |

| ADRES (A/D Result)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                            |

| CCP1CON/CCP2CON (CCP Control) Registers                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | s 54                       |

| Configuration Word Register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                            |

| Initialization Conditions (table)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 96—97                      |

| INTCON (Interrupt Control)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 21                         |

| INTCON (Interrupt Control) Register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 21                         |

| OPTION_REG                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                            |

| OPTION_REG Register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                            |

| PCON (Power Control)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                            |

| PCON (Power Control) Register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                            |

| PIE1 (Peripheral Interrupt Enable 1)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                            |

| PIE1 (Peripheral Interrupt Enable 1) Register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                            |

| PIE2 (Peripheral Interrupt Enable 2)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                            |