#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                   |

|----------------------------|--------------------------------------------------------------------------|

| Core Processor             | PIC                                                                      |

| Core Size                  | 8-Bit                                                                    |

| Speed                      | 20MHz                                                                    |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                                        |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                    |

| Number of I/O              | 22                                                                       |

| Program Memory Size        | 7KB (4K x 14)                                                            |

| Program Memory Type        | FLASH                                                                    |

| EEPROM Size                | -                                                                        |

| RAM Size                   | 192 x 8                                                                  |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 5.5V                                                                |

| Data Converters            | A/D 5x8b                                                                 |

| Oscillator Type            | External                                                                 |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                        |

| Mounting Type              | Surface Mount                                                            |

| Package / Case             | 28-SSOP (0.209", 5.30mm Width)                                           |

| Supplier Device Package    | 28-SSOP                                                                  |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16lf73-i-ss |

|                            |                                                                          |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## TABLE 1-3:PIC16F74 AND PIC16F77 PINOUT DESCRIPTION

| OSC1/CLKI<br>OSC1<br>CLKI<br>OSC2/CLKO<br>OSC2<br>CLKO<br>MCLR/VPP<br>MCLR<br>VPP | 13 | 14<br>15 | 30<br>31 | 1        | ST/CMOS <sup>(4)</sup> | Oscillator crystal or external clock input.<br>Oscillator crystal input or external clock source input.<br>ST buffer when configured in RC mode. Otherwise<br>CMOS.<br>External clock source input. Always associated with pin |

|-----------------------------------------------------------------------------------|----|----------|----------|----------|------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| CLKI<br>OSC2/CLKO<br>OSC2<br>CLKO<br><u>MCLR/VPP</u><br>MCLR                      | 14 | 15       | 31       | I        |                        | Oscillator crystal input or external clock source input.<br>ST buffer when configured in RC mode. Otherwise<br>CMOS.<br>External clock source input. Always associated with pin                                                |

| OSC2/CLKO<br>OSC2<br>CLKO<br>MCLR/VPP<br>MCLR                                     | 14 | 15       | 31       |          |                        | CMOS.<br>External clock source input. Always associated with pin                                                                                                                                                               |

| OSC2/CLKO<br>OSC2<br>CLKO<br>MCLR/VPP<br>MCLR                                     | 14 | 15       | 31       |          |                        | External clock source input. Always associated with pin                                                                                                                                                                        |

| OSC2<br>CLKO<br>MCLR/VPP<br>MCLR                                                  | 14 | 15       | 31       |          |                        |                                                                                                                                                                                                                                |

| OSC2<br>CLKO<br>MCLR/VPP<br>MCLR                                                  | 14 | 15       | 31       | 0        |                        | function OSC1 (see OSC1/CLKI, OSC2/CLKO pins).                                                                                                                                                                                 |

| CLKO<br>MCLR/VPP<br>MCLR                                                          |    |          |          | <u> </u> | I —                    | Oscillator crystal or clock output.                                                                                                                                                                                            |

| MCLR/Vpp<br>MCLR                                                                  |    |          |          | 0        |                        | Oscillator crystal output.                                                                                                                                                                                                     |

| MCLR/Vpp<br>MCLR                                                                  |    |          |          |          |                        | Connects to crystal or resonator in Crystal Oscillator                                                                                                                                                                         |

| MCLR/Vpp<br>MCLR                                                                  |    |          |          |          |                        | mode.                                                                                                                                                                                                                          |

| MCLR                                                                              |    |          |          | 0        |                        | In RC mode, OSC2 pin outputs CLKO, which has 1/4                                                                                                                                                                               |

| MCLR                                                                              |    |          |          |          |                        | the frequency of OSC1 and denotes the instruction                                                                                                                                                                              |

| MCLR                                                                              |    |          |          |          |                        | cycle rate.                                                                                                                                                                                                                    |

|                                                                                   | 1  | 2        | 18       |          | ST                     | Master Clear (input) or programming voltage (output).                                                                                                                                                                          |

| Vpp                                                                               |    |          |          | I        |                        | Master Clear (Reset) input. This pin is an active low                                                                                                                                                                          |

| VPP                                                                               |    |          |          |          |                        | RESET to the device.                                                                                                                                                                                                           |

|                                                                                   |    |          |          | Р        |                        | Programming voltage input.                                                                                                                                                                                                     |

|                                                                                   |    |          |          |          |                        | PORTA is a bi-directional I/O port.                                                                                                                                                                                            |

| RA0/AN0                                                                           | 2  | 3        | 19       |          | TTL                    |                                                                                                                                                                                                                                |

| RA0                                                                               |    |          |          | I/O      |                        | Digital I/O.                                                                                                                                                                                                                   |

| AN0                                                                               |    |          |          | I        |                        | Analog input 0.                                                                                                                                                                                                                |

| RA1/AN1                                                                           | 3  | 4        | 20       |          | TTL                    |                                                                                                                                                                                                                                |

| RA1                                                                               |    |          |          | I/O      |                        | Digital I/O.                                                                                                                                                                                                                   |

| AN1                                                                               |    |          |          | I        |                        | Analog input 1.                                                                                                                                                                                                                |

| RA2/AN2                                                                           | 4  | 5        | 21       |          | TTL                    |                                                                                                                                                                                                                                |

| RA2                                                                               |    |          |          | I/O      |                        | Digital I/O.                                                                                                                                                                                                                   |

| AN2                                                                               |    |          |          | I        |                        | Analog input 2.                                                                                                                                                                                                                |

| RA3/AN3/Vref                                                                      | 5  | 6        | 22       |          | TTL                    |                                                                                                                                                                                                                                |

| RA3                                                                               |    |          |          | I/O      |                        | Digital I/O.                                                                                                                                                                                                                   |

| AN3                                                                               |    |          |          | I        |                        | Analog input 3.                                                                                                                                                                                                                |

| VREF                                                                              |    |          |          | I        |                        | A/D reference voltage input.                                                                                                                                                                                                   |

| RA4/T0CKI                                                                         | 6  | 7        | 23       |          | ST                     |                                                                                                                                                                                                                                |

| RA4                                                                               |    |          |          | I/O      |                        | Digital I/O – Open drain when configured as output.                                                                                                                                                                            |

| TOCKI                                                                             |    |          |          | I        |                        | Timer0 external clock input.                                                                                                                                                                                                   |

| RA5/SS/AN4                                                                        | 7  | 8        | 24       |          | TTL                    |                                                                                                                                                                                                                                |

| RA5                                                                               |    | -        |          | I/O      |                        | Digital I/O.                                                                                                                                                                                                                   |

| SS                                                                                | 1  |          |          | 1        |                        | SPI slave select input.                                                                                                                                                                                                        |

| AN4                                                                               |    |          |          |          | 1                      |                                                                                                                                                                                                                                |

| Legend: I = inpu                                                                  |    | 1        |          |          |                        | Analog input 4.                                                                                                                                                                                                                |

— = Not used TTL = TTL input ST = Schmitt Trigger input

**Note 1:** This buffer is a Schmitt Trigger input when configured as an external interrupt.

2: This buffer is a Schmitt Trigger input when used in Serial Programming mode.

**3:** This buffer is a Schmitt Trigger input when configured as general purpose I/O and a TTL input when used in the Parallel Slave Port mode (for interfacing to a microprocessor bus).

4: This buffer is a Schmitt Trigger input when configured in RC Oscillator mode and a CMOS input otherwise.

# PIC16F7X

| FIGL | JRE | 2-3: |

|------|-----|------|

|      |     |      |

## PIC16F74/73 REGISTER FILE MAP

| ŀ                                                                      | File<br>Address |                                           | File<br>Address |                           | File<br>Address | ļ                 | File<br>Addre |

|------------------------------------------------------------------------|-----------------|-------------------------------------------|-----------------|---------------------------|-----------------|-------------------|---------------|

| Indirect addr.(*)                                                      | 00h             | Indirect addr.(*)                         | 80h             | Indirect addr.(*)         | 100h            | Indirect addr.(*) | 180           |

| TMR0                                                                   | 01h             | OPTION_REG                                | 81h             | TMR0                      | 101h            | OPTION_REG        | 181           |

| PCL                                                                    | 02h             | PCL                                       | 82h             | PCL                       | 102h            | PCL               | 182           |

| STATUS                                                                 | 03h             | STATUS                                    | 83h             | STATUS                    | 103h            | STATUS            | 183           |

| FSR                                                                    | 04h             | FSR                                       | 84h             | FSR                       | 104h            | FSR               | 184           |

| PORTA                                                                  | 05h             | TRISA                                     | 85h             |                           | 105h            |                   | 185           |

| PORTB                                                                  | 06h             | TRISB                                     | 86h             | PORTB                     | 106h            | TRISB             | 186           |

| PORTC                                                                  | 07h             | TRISC                                     | 87h             |                           | 107h            |                   | 187           |

| PORTD <sup>(1)</sup>                                                   | 08h             | TRISD <sup>(1)</sup>                      | 88h             |                           | 108h            |                   | 188           |

| PORTE <sup>(1)</sup>                                                   | 09h             | TRISE <sup>(1)</sup>                      | 89h             |                           | 109h            |                   | 189           |

| PCLATH                                                                 | 0Ah             | PCLATH                                    | 8Ah             | PCLATH                    | 10Ah            | PCLATH            | 18A           |

| INTCON                                                                 | 0Bh             | INTCON                                    | 8Bh             | INTCON                    | 10Bh            | INTCON            | 18E           |

| PIR1                                                                   | 0Ch             | PIE1                                      | 8Ch             | PMDATA                    | 10Ch            | PMCON1            | 180           |

| PIR2                                                                   | 0Dh             | PIE2                                      | 8Dh             | PMADR                     | 10Dh            |                   | 180           |

| TMR1L                                                                  | 0Eh             | PCON                                      | 8Eh             | PMDATH                    | 10Eh            |                   | 18E           |

| TMR1H                                                                  | 0Fh             |                                           | 8Fh             | PMADRH                    | 10Fh            |                   | 18F           |

| T1CON                                                                  | 10h             |                                           | 90h             |                           | 110h            |                   | 190           |

| TMR2                                                                   | 11h             |                                           | 91h             |                           |                 |                   |               |

| T2CON                                                                  | 12h             | PR2                                       | 92h             |                           |                 |                   |               |

| SSPBUF                                                                 | 13h             | SSPADD                                    | 93h             |                           |                 |                   |               |

| SSPCON                                                                 | 14h             | SSPSTAT                                   | 94h             |                           |                 |                   |               |

| CCPR1L                                                                 | 15h             |                                           | 95h             |                           |                 |                   |               |

| CCPR1H                                                                 | 16h             |                                           | 96h             |                           |                 |                   |               |

| CCP1CON                                                                | 17h             |                                           | 97h             |                           |                 |                   |               |

| RCSTA                                                                  | 18h             | TXSTA                                     | 98h             |                           |                 |                   |               |

| TXREG                                                                  | 19h             | SPBRG                                     | 99h             |                           |                 |                   |               |

| RCREG                                                                  | 1Ah             |                                           | 9Ah             |                           |                 |                   |               |

| CCPR2L                                                                 | 1Bh             |                                           | 9Bh             |                           |                 |                   |               |

| CCPR2H                                                                 | 1Ch             |                                           | 9Ch             |                           |                 |                   |               |

| CCP2CON                                                                | 1Dh             |                                           | 9Dh             |                           |                 |                   |               |

| ADRES                                                                  | 1Eh             |                                           | 9Eh             |                           |                 |                   |               |

| ADCON0                                                                 | 1Fh             | ADCON1                                    | 9Fh             |                           | 1001            |                   | 4.4.0         |

|                                                                        | 20h             |                                           | A0h             |                           | 120h            |                   | 1A0           |

|                                                                        |                 |                                           | 7,011           |                           |                 |                   |               |

| General                                                                |                 | General                                   |                 |                           |                 |                   |               |

|                                                                        |                 | Purpose<br>Register                       |                 | accesses                  |                 | accesses          |               |

| -                                                                      |                 | -                                         |                 | 20h-7Fh                   |                 | A0h - FFh         | 4             |

| 96 Bytes                                                               |                 | 96 Bytes                                  |                 |                           | 16Fh<br>170b    |                   | 1EF<br>1FC    |

|                                                                        |                 |                                           |                 |                           | 17011           |                   |               |

| Bank 0                                                                 | 7Fh             | Bank 1                                    | FFh             | Bank 2                    | 17Fh            | Bank 3            | 1FF           |

| Purpose<br>Register<br>96 Bytes<br>Bank 0<br>Unimpleme<br>* Not a phys | ented data      | Purpose<br>Register<br>96 Bytes<br>Bank 1 | s, read as      | 20h-7Fh<br>Bank 2<br>'0'. | 170h            | A0h - FFh         |               |

#### 2.2.2 SPECIAL FUNCTION REGISTERS

The Special Function Registers are registers used by the CPU and peripheral modules for controlling the desired operation of the device. These registers are implemented as static RAM. A list of these registers is given in Table 2-1. The Special Function Registers can be classified into two sets: core (CPU) and peripheral. Those registers associated with the core functions are described in detail in this section. Those related to the operation of the peripheral features are described in detail in the peripheral feature section.

| Address              | Name    | Bit 7                | Bit 6                                                                       | Bit 5         | Bit 4          | Bit 3         | Bit 2         | Bit 1         | Bit 0        | Value on:<br>POR,<br>BOR | Details<br>on page |

|----------------------|---------|----------------------|-----------------------------------------------------------------------------|---------------|----------------|---------------|---------------|---------------|--------------|--------------------------|--------------------|

| Bank 0               | •       |                      |                                                                             |               |                | •             | •             | •             | •            |                          |                    |

| 00h <sup>(4)</sup>   | INDF    | Addressing           | g this locatio                                                              | n uses conte  | nts of FSR to  | address data  | a memory (r   | not a physica | al register) | 0000 0000                | 27, 96             |

| 01h                  | TMR0    | Timer0 Mc            | dule Registe                                                                | er            |                |               |               |               |              | xxxx xxxx                | 45, 96             |

| 02h <sup>(4)</sup>   | PCL     | Program C            | Counter (PC)                                                                | Least Signif  | icant Byte     |               |               |               |              | 0000 0000                | 26, 96             |

| 03h <sup>(4)</sup>   | STATUS  | IRP                  | RP1                                                                         | RP0           | TO             | PD            | Z             | DC            | С            | 0001 1xxx                | 19, 96             |

| 04h <sup>(4)</sup>   | FSR     | Indirect Da          | Indirect Data Memory Address Pointer                                        |               |                |               |               |               |              |                          | 27, 96             |

| 05h                  | PORTA   | _                    | PORTA Data Latch when written: PORTA pins when read                         |               |                |               |               |               |              | 0x 0000                  | 32, 96             |

| 06h                  | PORTB   | PORTB D              | ata Latch wh                                                                | en written: P | ORTB pins w    | hen read      | •             |               |              | xxxx xxxx                | 34, 96             |

| 07h                  | PORTC   | PORTC D              | ata Latch wh                                                                | en written: P | ORTC pins w    | /hen read     |               |               |              | XXXX XXXX                | 35, 96             |

| 08h <b>(5)</b>       | PORTD   | PORTD D              | ata Latch wh                                                                | en written: P | ORTD pins w    | /hen read     |               |               |              | xxxx xxxx                | 36, 96             |

| 09h <b>(5)</b>       | PORTE   | _                    |                                                                             | —             | —              | —             | RE2           | RE1           | RE0          | xxx                      | 39, 96             |

| 0Ah <sup>(1,4)</sup> | PCLATH  | _                    | _                                                                           | _             | Write Buffer   | for the upper | 5 bits of the | Program C     | ounter       | 0 0000                   | 26, 96             |

| 0Bh <sup>(4)</sup>   | INTCON  | GIE                  | PEIE                                                                        | TMR0IE        | INTE           | RBIE          | TMR0IF        | INTF          | RBIF         | 0000 000x                | 21, 96             |

| 0Ch                  | PIR1    | PSPIF <sup>(3)</sup> | ADIF                                                                        | RCIF          | TXIF           | SSPIF         | CCP1IF        | TMR2IF        | TMR1IF       | 0000 0000                | 23, 96             |

| 0Dh                  | PIR2    | _                    | _                                                                           | _             | _              | _             | _             | _             | CCP2IF       | 0                        | 24, 96             |

| 0Eh                  | TMR1L   | Holding Re           | Holding Register for the Least Significant Byte of the 16-bit TMR1 Register |               |                |               |               |               |              |                          |                    |

| 0Fh                  | TMR1H   | Holding Re           | egister for the                                                             | e Most Signif | ficant Byte of | the 16-bit TM | IR1 Registe   | r             |              | xxxx xxxx                | 50, 96             |

| 10h                  | T1CON   | _                    | _                                                                           | T1CKPS1       | T1CKPS0        | T1OSCEN       | T1SYNC        | TMR1CS        | TMR10N       | 00 0000                  | 47, 96             |

| 11h                  | TMR2    | Timer2 Mc            | dule Registe                                                                | er            |                |               |               | -             |              | 0000 0000                | 52, 96             |

| 12h                  | T2CON   | _                    | TOUTPS3                                                                     | TOUTPS2       | TOUTPS         | TOUTPS0       | TMR2ON        | T2CKPS1       | T2CKPS0      | -000 0000                | 52, 96             |

| 13h                  | SSPBUF  | Synchrono            | ous Serial Po                                                               | ort Receive B | uffer/Transmi  | t Register    |               |               |              | xxxx xxxx                | 64, 68, 96         |

| 14h                  | SSPCON  | WCOL                 | SSPOV                                                                       | SSPEN         | CKP            | SSPM3         | SSPM2         | SSPM1         | SSPM0        | 0000 0000                | 61, 96             |

| 15h                  | CCPR1L  | Capture/C            | ompare/PWI                                                                  | M Register1   | (LSB)          |               |               |               |              | xxxx xxxx                | 56, 96             |

| 16h                  | CCPR1H  | Capture/C            | ompare/PWI                                                                  | M Register1   | (MSB)          |               |               |               |              | xxxx xxxx                | 56, 96             |

| 17h                  | CCP1CON | _                    | _                                                                           | CCP1X         | CCP1Y          | CCP1M3        | CCP1M2        | CCP1M1        | CCP1M0       | 00 0000                  | 54, 96             |

| 18h                  | RCSTA   | SPEN                 | RX9                                                                         | SREN          | CREN           | —             | FERR          | OERR          | RX9D         | 0000 -00x                | 70, 96             |

| 19h                  | TXREG   | USART Tr             | ansmit Data                                                                 | Register      |                |               |               |               |              | 0000 0000                | 74, 96             |

| 1Ah                  | RCREG   | USART Re             | eceive Data                                                                 | Register      |                |               |               |               |              | 0000 0000                | 76, 96             |

| 1Bh                  | CCPR2L  | Capture/C            | ompare/PWI                                                                  | M Register2   | (LSB)          |               |               |               |              | xxxx xxxx                | 58, 96             |

| 1Ch                  | CCPR2H  | Capture/C            | ompare/PWI                                                                  | M Register2   | (MSB)          |               |               |               |              | xxxx xxxx                | 58, 96             |

| 1Dh                  | CCP2CON | _                    | _                                                                           | CCP2X         | CCP2Y          | CCP2M3        | CCP2M2        | CCP2M1        | CCP2M0       | 00 0000                  | 54, 96             |

| 1Eh                  | ADRES   | A/D Result           | t Register By                                                               | rte           |                |               |               |               |              | xxxx xxxx                | 88, 96             |

| 1Fh                  | ADCON0  | ADCS1                | ADCS0                                                                       | CHS2          | CHS1           | CHS0          | GO/<br>DONE   | —             | ADON         | 0000 00-0                | 83, 96             |

TABLE 2-1:SPECIAL FUNCTION REGISTER SUMMARY

$\label{eq:legend: Legend: Legend: u = unchanged, q = value depends on condition, - = unimplemented, read as '0', r = reserved. \\ Shaded locations are unimplemented, read as '0'.$

**Note** 1: The upper byte of the program counter is not directly accessible. PCLATH is a holding register for the PC<12:8>, whose contents are transferred to the upper byte of the program counter during branches (CALL or GOTO).

2: Other (non power-up) RESETS include external RESET through MCLR and Watchdog Timer Reset.

3: Bits PSPIE and PSPIF are reserved on the 28-pin devices; always maintain these bits clear.

4: These registers can be addressed from any bank.

5: PORTD, PORTE, TRISD, and TRISE are not physically implemented on the 28-pin devices, read as '0'.

6: This bit always reads as a '1'.

# 2.3 PCL and PCLATH

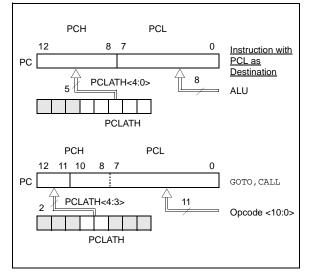

The program counter (PC) is 13 bits wide. The low byte comes from the PCL register, which is a readable and writable register. The upper bits (PC<12:8>) are not readable, but are indirectly writable through the PCLATH register. On any RESET, the upper bits of the PC will be cleared. Figure 2-4 shows the two situations for the loading of the PC. The upper example in the figure shows how the PC is loaded on a write to PCL (PCLATH<4:0>  $\rightarrow$  PCH). The lower example in the figure shows how the PC is loaded during a CALL or GOTO instruction (PCLATH<4:3>  $\rightarrow$  PCH).

#### FIGURE 2-4: LOADING OF PC IN DIFFERENT SITUATIONS

### 2.3.1 COMPUTED GOTO

A computed GOTO is accomplished by adding an offset to the program counter (ADDWF PCL). When doing a table read using a computed GOTO method, care should be exercised if the table location crosses a PCL memory boundary (each 256 byte block). Refer to the Application Note, *"Implementing a Table Read"* (AN556).

### 2.3.2 STACK

The PIC16F7X family has an 8-level deep x 13-bit wide hardware stack. The stack space is not part of either program or data space and the stack pointer is not readable or writable. The PC is PUSHed onto the stack when a CALL instruction is executed, or an interrupt causes a branch. The stack is POPed in the event of a RETURN, RETLW or a RETFIE instruction execution. PCLATH is not affected by a PUSH or POP operation.

The stack operates as a circular buffer. This means that after the stack has been PUSHed eight times, the ninth push overwrites the value that was stored from the first push. The tenth push overwrites the second push (and so on).

- Note 1: There are no status bits to indicate stack overflow or stack underflow conditions.

- 2: There are no instructions/mnemonics called PUSH or POP. These are actions that occur from the execution of the CALL, RETURN, RETLW and RETFIE instructions, or the vectoring to an interrupt address.

## 2.4 Program Memory Paging

PIC16F7X devices are capable of addressing a continuous 8K word block of program memory. The CALL and GOTO instructions provide only 11 bits of address to allow branching within any 2K program memory page. When doing a CALL or GOTO instruction, the upper 2 bits of the address are provided by PCLATH<4:3>. When doing a CALL or GOTO instruction, the user must ensure that the page select bits are programmed so that the desired program memory page is addressed. If a return from a CALL instruction (or interrupt) is executed, the entire 13-bit PC is popped off the stack. Therefore, manipulation of the PCLATH<4:3> bits are not required for the RETURN instructions (which POPs the address from the stack).

| Note: | The contents of the PCLATH are         |  |  |  |  |  |  |  |  |  |

|-------|----------------------------------------|--|--|--|--|--|--|--|--|--|

|       | unchanged after a RETURN or RETFIE     |  |  |  |  |  |  |  |  |  |

|       | instruction is executed. The user must |  |  |  |  |  |  |  |  |  |

|       | setup the PCLATH for any subsequent    |  |  |  |  |  |  |  |  |  |

|       | CALLS <b>or</b> GOTOS.                 |  |  |  |  |  |  |  |  |  |

Example 2-1 shows the calling of a subroutine in page 1 of the program memory. This example assumes that PCLATH is saved and restored by the Interrupt Service Routine (if interrupts are used).

#### EXAMPLE 2-1: CALL OF A SUBROUTINE IN PAGE 1 FROM PAGE 0

|         | ORG  | 0x500    |                                                          |

|---------|------|----------|----------------------------------------------------------|

|         | BCF  | PCLATH,4 |                                                          |

|         | BSF  | PCLATH,3 | ;Select page 1<br>;(800h-FFFh)                           |

|         | CALL | SUB1_P1  | ;Call subroutine in                                      |

|         | :    |          | ;page 1 (800h-FFFh)                                      |

|         | :    |          |                                                          |

|         | ORG  | 0x900    | ;page 1 (800h-FFFh)                                      |

| SUB1_P1 |      |          |                                                          |

|         | :    |          | ;called subroutine                                       |

|         | :    |          | ;page 1 (800h-FFFh)                                      |

|         | :    |          |                                                          |

| RETURN  |      |          | ;return to Call<br>;subroutine in page 0<br>;(000h-7FFh) |

INDIDECT ADDESSING

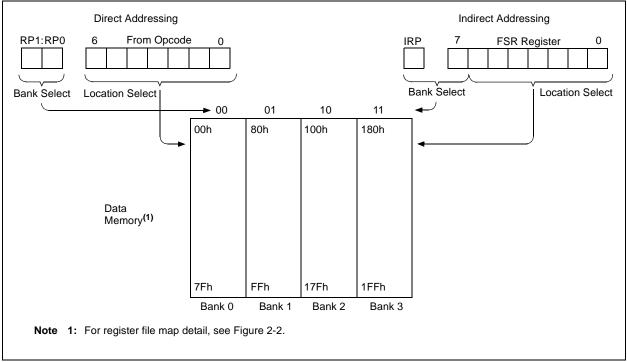

# 2.5 Indirect Addressing, INDF and FSR Registers

The INDF register is not a physical register. Addressing the INDF register will cause indirect addressing.

Indirect addressing is possible by using the INDF register. Any instruction using the INDF register actually accesses the register pointed to by the File Select Register, FSR. Reading the INDF register itself indirectly (FSR = '0') will read 00h. Writing to the INDF register indirectly results in a no operation (although status bits may be affected). An effective 9-bit address is obtained by concatenating the 8-bit FSR register and the IRP bit (STATUS<7>), as shown in Figure 2-5.

A simple program to clear RAM locations 20h-2Fh using indirect addressing is shown in Example 2-2.

|        | PLE 2-2: | INL   | JIRECT ADDRESSING    |

|--------|----------|-------|----------------------|

|        | MOVLW    | 0x20  | ;initialize pointer  |

|        | MOVWF    | FSR   | ;to RAM              |

| NEXT   | CLRF     | INDF  | clear INDF register; |

|        | INCF     | FSR,F | ;inc pointer         |

|        | BTFSS    | FSR,4 | ;all done?           |

|        | GOTO     | NEXT  | ;no clear next       |

| CONTIN | IUE      |       |                      |

| :      |          |       | ;yes continue        |

|        |          |       |                      |

EVAMPLE 2.2.

## FIGURE 2-5: DIRECT/INDIRECT ADDRESSING

# 6.0 TIMER1 MODULE

The Timer1 module is a 16-bit timer/counter consisting of two 8-bit registers (TMR1H and TMR1L), which are readable and writable. The TMR1 Register pair (TMR1H:TMR1L) increments from 0000h to FFFFh and rolls over to 0000h. The TMR1 Interrupt, if enabled, is generated on overflow, which is latched in interrupt flag bit TMR1IF (PIR1<0>). This interrupt can be enabled/disabled by setting/clearing TMR1 interrupt enable bit TMR1IE (PIE1<0>).

Timer1 can operate in one of two modes:

- As a timer

- · As a counter

The operating mode is determined by the clock select bit, TMR1CS (T1CON<1>).

In Timer mode, Timer1 increments every instruction cycle. In Counter mode, it increments on every rising edge of the external clock input.

Timer1 can be enabled/disabled by setting/clearing control bit TMR1ON (T1CON<0>).

Timer1 also has an internal "RESET input". This RESET can be generated by either of the two CCP modules as the special event trigger (see Sections 8.1 and 8.2). Register 6-1 shows the Timer1 Control register.

When the Timer1 oscillator is enabled (T1OSCEN is set), the RC1/T1OSI/CCP2 and RC0/T1OSO/T1CKI pins become inputs. That is, the TRISC<1:0> value is ignored and these pins read as '0'.

Additional information on timer modules is available in the PICmicro<sup>™</sup> Mid-Range MCU Family Reference Manual (DS33023).

### REGISTER 6-1: T1CON: TIMER1 CONTROL REGISTER (ADDRESS 10h)

|         |             |                                                                                             |              |                | •                                                                       | ,          |              |         |  |  |  |  |  |

|---------|-------------|---------------------------------------------------------------------------------------------|--------------|----------------|-------------------------------------------------------------------------|------------|--------------|---------|--|--|--|--|--|

|         | U-0         | U-0                                                                                         | R/W-0        | R/W-0          | R/W-0                                                                   | R/W-0      | R/W-0        | R/W-0   |  |  |  |  |  |

|         | _           | —                                                                                           | T1CKPS1      | T1CKPS0        | T1OSCEN                                                                 | T1SYNC     | TMR1CS       | TMR10N  |  |  |  |  |  |

|         | bit 7       |                                                                                             |              |                |                                                                         |            |              | bit 0   |  |  |  |  |  |

|         |             |                                                                                             |              |                |                                                                         |            |              |         |  |  |  |  |  |

| bit 7-6 | Unimplem    | Unimplemented: Read as '0'                                                                  |              |                |                                                                         |            |              |         |  |  |  |  |  |

| bit 5-4 |             | T1CKPS1:T1CKPS0: Timer1 Input Clock Prescale Select bits                                    |              |                |                                                                         |            |              |         |  |  |  |  |  |

|         |             | 11 = 1:8 Prescale value                                                                     |              |                |                                                                         |            |              |         |  |  |  |  |  |

|         |             | 10 = 1:4 Prescale value<br>11 = 1:2 Prescale value                                          |              |                |                                                                         |            |              |         |  |  |  |  |  |

|         |             | 00 = 1:1 Prescale value                                                                     |              |                |                                                                         |            |              |         |  |  |  |  |  |

| bit 3   | T1OSCEN     | l: Timer1 Os                                                                                | cillator Ena | ble Control b  | oit                                                                     |            |              |         |  |  |  |  |  |

|         | 1 = Oscilla | 1 = Oscillator is enabled                                                                   |              |                |                                                                         |            |              |         |  |  |  |  |  |

|         | 0 = Oscilla | 0 = Oscillator is shut-off (the oscillator inverter is turned off to eliminate power drain) |              |                |                                                                         |            |              |         |  |  |  |  |  |

| bit 2   | T1SYNC:     | Timer1 Exte                                                                                 | rnal Clock I | nput Synchr    | onization Co                                                            | ntrol bit  |              |         |  |  |  |  |  |

|         | TMR1CS :    |                                                                                             |              | I.a. a. l      |                                                                         |            |              |         |  |  |  |  |  |

|         |             | synchronize                                                                                 |              |                |                                                                         |            |              |         |  |  |  |  |  |

|         | TMR1CS :    |                                                                                             |              | Jul            |                                                                         |            |              |         |  |  |  |  |  |

|         |             |                                                                                             | ner1 uses th | e internal clo | ock when TM                                                             | IR1CS = 0. |              |         |  |  |  |  |  |

| bit 1   | TMR1CS:     | Timer1 Cloc                                                                                 | k Source S   | elect bit      |                                                                         |            |              |         |  |  |  |  |  |

|         |             | al clock fron<br>al clock (Fos                                                              | •            | 10SO/T1Cł      | <i (on="" risi<="" td="" the=""><td>ng edge)</td><td></td><td></td></i> | ng edge)   |              |         |  |  |  |  |  |

| bit 0   | TMR10N:     | Timer1 On I                                                                                 | bit          |                |                                                                         |            |              |         |  |  |  |  |  |

|         | 1 = Enable  | es Timer1                                                                                   |              |                |                                                                         |            |              |         |  |  |  |  |  |

|         | 0 = Stops   | Timer1                                                                                      |              |                |                                                                         |            |              |         |  |  |  |  |  |

|         | r           |                                                                                             |              |                |                                                                         |            |              |         |  |  |  |  |  |

|         | Legend:     |                                                                                             |              |                |                                                                         |            |              |         |  |  |  |  |  |

|         | R = Reada   | able bit                                                                                    | W = V        | Nritable bit   | U = Unin                                                                | nplemented | bit, read as | '0'     |  |  |  |  |  |

|         | - n = Value | e at POR res                                                                                | set '1' =    | Bit is set     | '0' = Bit i                                                             | s cleared  | x = Bit is ι | unknown |  |  |  |  |  |

|         |             |                                                                                             |              |                |                                                                         |            |              |         |  |  |  |  |  |

#### 8.5.3 SETUP FOR PWM OPERATION

The following steps should be taken when configuring the CCP module for PWM operation:

- 1. Set the PWM period by writing to the PR2 register.

- 2. Set the PWM duty cycle by writing to the CCPR1L register and CCP1CON<5:4> bits.

- 3. Make the CCP1 pin an output by clearing the TRISC<2> bit.

- 4. Set the TMR2 prescale value and enable Timer2 by writing to T2CON.

- 5. Configure the CCP1 module for PWM operation.

## TABLE 8-4: EXAMPLE PWM FREQUENCIES AND RESOLUTIONS (Fosc = 20 MHz)

| PWM Frequency             | 1.22 kHz | 4.88 kHz | 19.53 kHz | 78.12 kHz | 156.3 kHz | 208.3 kHz |  |

|---------------------------|----------|----------|-----------|-----------|-----------|-----------|--|

| Timer Prescale (1, 4, 16) | 16       | 4        | 1         | 1         | 1         | 1         |  |

| PR2 Value                 | 0xFF     | 0xFF     | 0xFF      | 0x3F      | 0x1F      | 0x17      |  |

| Maximum Resolution (bits) | 10       | 10       | 10        | 8         | 7         | 5.5       |  |

#### TABLE 8-5: REGISTERS ASSOCIATED WITH PWM AND TIMER2

| Address               | Name    | Bit 7                               | Bit 6                         | 6 Bit 5 Bit 4 Bit 3 Bit 2 Bit 1 Bit 0 |           |         |        |         | Value on:<br>POR,<br>BOR |      | Value on<br>all other<br>RESETS |      |      |

|-----------------------|---------|-------------------------------------|-------------------------------|---------------------------------------|-----------|---------|--------|---------|--------------------------|------|---------------------------------|------|------|

| 0Bh,8Bh,<br>10Bh,18Bh | INTCON  | GIE                                 | PEIE                          | TMR0IE                                | INTE      | RBIE    | TMR0IF | INTF    | RBIF                     | 0000 | 000x                            | 0000 | 000u |

| 0Ch                   | PIR1    | PSPIF <sup>(1)</sup>                | ADIF                          | RCIF                                  | TXIF      | SSPIF   | CCP1IF | TMR2IF  | TMR1IF                   | 0000 | 0000                            | 0000 | 0000 |

| 0Dh                   | PIR2    | _                                   | —                             | —                                     |           | _       | —      |         | CCP2IF                   |      | 0                               |      | 0    |

| 8Ch                   | PIE1    | PSPIE <sup>(1)</sup>                | ADIE                          | RCIE                                  | TXIE      | SSPIE   | CCP1IE | TMR2IE  | TMR1IE                   | 0000 | 0000                            | 0000 | 0000 |

| 8Dh                   | PIE2    | —                                   | _                             | _                                     | _         | —       | —      | _       | CCP2IE                   |      | 0                               |      | 0    |

| 87h                   | TRISC   | PORTC D                             | PORTC Data Direction Register |                                       |           |         |        |         |                          |      |                                 | 1111 | 1111 |

| 11h                   | TMR2    | Timer2 M                            | odule Regi                    | ster                                  |           |         |        |         |                          | 0000 | 0000                            | 0000 | 0000 |

| 92h                   | PR2     | Timer2 M                            | odule Peric                   | d Register                            |           |         |        |         |                          | 1111 | 1111                            | 1111 | 1111 |

| 12h                   | T2CON   | _                                   | TOUTPS3                       | TOUTPS2                               | TOUTPS1   | TOUTPS0 | TMR2ON | T2CKPS1 | T2CKPS0                  | -000 | 0000                            | -000 | 0000 |

| 15h                   | CCPR1L  | Capture/C                           | Compare/P                     | VM Registe                            | er1 (LSB) |         |        |         |                          | xxxx | xxxx                            | uuuu | uuuu |

| 16h                   | CCPR1H  | Capture/C                           | Compare/P                     | VM Registe                            | er1 (MSB) |         |        |         |                          | xxxx | xxxx                            | uuuu | uuuu |

| 17h                   | CCP1CON | _                                   | _                             | CCP1X                                 | CCP1Y     | CCP1M3  | CCP1M2 | CCP1M1  | CCP1M0                   | 00   | 0000                            | 00   | 0000 |

| 1Bh                   | CCPR2L  | Capture/Compare/PWM Register2 (LSB) |                               |                                       |           |         |        |         | xxxx                     | xxxx | uuuu                            | uuuu |      |

| 1Ch                   | CCPR2H  | Capture/C                           | Compare/P                     | WM Registe                            | er2 (MSB) |         |        |         |                          | xxxx | xxxx                            | uuuu | uuuu |

| 1Dh                   | CCP2CON | —                                   | —                             | CCP2X                                 | CCP2Y     | CCP2M3  | CCP2M2 | CCP2M1  | CCP2M0                   | 00   | 0000                            | 00   | 0000 |

Legend: x = unknown, u = unchanged, - = unimplemented, read as '0'. Shaded cells are not used by PWM and Timer2.

Note 1: Bits PSPIE and PSPIF are reserved on the PIC16F73/76; always maintain these bits clear.

|              |         | Fosc = 20 M | Hz                          |         | Fosc = 16 M | Hz                          |         | Fosc = 10 MHz |                             |  |

|--------------|---------|-------------|-----------------------------|---------|-------------|-----------------------------|---------|---------------|-----------------------------|--|

| BAUD<br>RATE | BAUD    | %<br>ERROR  | SPBRG<br>VALUE<br>(DECIMAL) | BAUD    | %<br>ERROR  | SPBRG<br>VALUE<br>(DECIMAL) | BAUD    | %<br>ERROR    | SPBRG<br>VALUE<br>(DECIMAL) |  |

| 1200         | 1,221   | 1.73%       | 255                         | 1,202   | 0.16%       | 207                         | 1,202   | 0.16%         | 129                         |  |

| 2400         | 2,404   | 0.16%       | 129                         | 2,404   | 0.16%       | 103                         | 2,404   | 0.16%         | 64                          |  |

| 9600         | 9,470   | -1.36%      | 32                          | 9,615   | 0.16%       | 25                          | 9,766   | 1.73%         | 15                          |  |

| 19,200       | 19,531  | 1.73%       | 15                          | 19,231  | 0.16%       | 12                          | 19,531  | 1.73%         | 7                           |  |

| 38,400       | 39,063  | 1.73%       | 7                           | 35,714  | -6.99%      | 6                           | 39,063  | 1.73%         | 3                           |  |

| 57,600       | 62,500  | 8.51%       | 4                           | 62,500  | 8.51%       | 3                           | 52,083  | -9.58%        | 2                           |  |

| 76,800       | 78,125  | 1.73%       | 3                           | 83,333  | 8.51%       | 2                           | 78,125  | 1.73%         | 1                           |  |

| 96,000       | 104,167 | 8.51%       | 2                           | 83,333  | -13.19%     | 2                           | 78,125  | -18.62%       | 1                           |  |

| 115,200      | 104,167 | -9.58%      | 2                           | 125,000 | 8.51%       | 1                           | 78,125  | -32.18%       | 1                           |  |

| 250,000      | 312,500 | 25.00%      | 0                           | 250,000 | 0.00%       | 0                           | 156,250 | -37.50%       | 0                           |  |

# TABLE 10-3:BAUD RATES FOR ASYNCHRONOUS MODE (BRGH = 0)

|              | Fosc = 4 MHz |            |                             |        | Fosc = 3.6864 | MHz                         | Fosc = 3.579545 MHz |            |                             |  |

|--------------|--------------|------------|-----------------------------|--------|---------------|-----------------------------|---------------------|------------|-----------------------------|--|

| BAUD<br>RATE | BAUD         | %<br>ERROR | SPBRG<br>VALUE<br>(DECIMAL) | BAUD   | %<br>ERROR    | SPBRG<br>VALUE<br>(DECIMAL) | BAUD                | %<br>ERROR | SPBRG<br>VALUE<br>(DECIMAL) |  |

| 300          | 300          | 0.16%      | 207                         | 300    | 0.00%         | 191                         | 301                 | 0.23%      | 185                         |  |

| 1200         | 1,202        | 0.16%      | 51                          | 1,200  | 0.00%         | 47                          | 1,190               | -0.83%     | 46                          |  |

| 2400         | 2,404        | 0.16%      | 25                          | 2,400  | 0.00%         | 23                          | 2,432               | 1.32%      | 22                          |  |

| 9600         | 8,929        | -6.99%     | 6                           | 9,600  | 0.00%         | 5                           | 9,322               | -2.90%     | 5                           |  |

| 19,200       | 20,833       | 8.51%      | 2                           | 19,200 | 0.00%         | 2                           | 18,643              | -2.90%     | 2                           |  |

| 38,400       | 31,250       | -18.62%    | 1                           | 28,800 | -25.00%       | 1                           | 27,965              | -27.17%    | 1                           |  |

| 57,600       | 62,500       | 8.51%      | 0                           | 57,600 | 0.00%         | 0                           | 55,930              | -2.90%     | 0                           |  |

| 76,800       | 62,500       | -18.62%    | 0                           | —      | _             | _                           | _                   | _          | —                           |  |

## TABLE 10-4: BAUD RATES FOR ASYNCHRONOUS MODE (BRGH = 1)

|              | Fosc = 20 MHz |            |                             |         | Fosc = 16 M | Hz                          | Fosc = 10 MHz |            |                             |  |

|--------------|---------------|------------|-----------------------------|---------|-------------|-----------------------------|---------------|------------|-----------------------------|--|

| BAUD<br>RATE | BAUD          | %<br>ERROR | SPBRG<br>VALUE<br>(DECIMAL) | BAUD    | %<br>ERROR  | SPBRG<br>VALUE<br>(DECIMAL) | BAUD          | %<br>ERROR | SPBRG<br>VALUE<br>(DECIMAL) |  |

| 2400         | _             | _          | _                           | —       | _           | _                           | 2,441         | 1.73%      | 255                         |  |

| 9600         | 9,615         | 0.16%      | 129                         | 9,615   | 0.16%       | 103                         | 9,615         | 0.16%      | 64                          |  |

| 19,200       | 19,231        | 0.16%      | 64                          | 19,231  | 0.16%       | 51                          | 18,939        | -1.36%     | 32                          |  |

| 38,400       | 37,879        | -1.36%     | 32                          | 38,462  | 0.16%       | 25                          | 39,063        | 1.73%      | 15                          |  |

| 57,600       | 56,818        | -1.36%     | 21                          | 58,824  | 2.12%       | 16                          | 56,818        | -1.36%     | 10                          |  |

| 76,800       | 78,125        | 1.73%      | 15                          | 76,923  | 0.16%       | 12                          | 78,125        | 1.73%      | 7                           |  |

| 96,000       | 96,154        | 0.16%      | 12                          | 100,000 | 4.17%       | 9                           | 89,286        | -6.99%     | 6                           |  |

| 115,200      | 113,636       | -1.36%     | 10                          | 111,111 | -3.55%      | 8                           | 125,000       | 8.51%      | 4                           |  |

| 250,000      | 250,000       | 0.00%      | 4                           | 250,000 | 0.00%       | 3                           | 208,333       | -16.67%    | 2                           |  |

| 300,000      | 312,500       | 4.17%      | 3                           | 333,333 | 11.11%      | 2                           | 312,500       | 4.17%      | 1                           |  |

| BAUD        | Fosc = 4 MHz |            |                             | F       | osc = 3.6864 | MHz                         | Fosc = 3.579545 MHz |            |                             |  |

|-------------|--------------|------------|-----------------------------|---------|--------------|-----------------------------|---------------------|------------|-----------------------------|--|

| RATE<br>(K) | BAUD         | %<br>ERROR | SPBRG<br>VALUE<br>(DECIMAL) | BAUD    | %<br>ERROR   | SPBRG<br>VALUE<br>(DECIMAL) | BAUD                | %<br>ERROR | SPBRG<br>VALUE<br>(DECIMAL) |  |

| 1200        | 1,202        | 0.16%      | 207                         | 1,200   | 0.00%        | 191                         | 1,203               | 0.23%      | 185                         |  |

| 2400        | 2,404        | 0.16%      | 103                         | 2,400   | 0.00%        | 95                          | 2,406               | 0.23%      | 92                          |  |

| 9600        | 9,615        | 0.16%      | 25                          | 9,600   | 0.00%        | 23                          | 9,727               | 1.32%      | 22                          |  |

| 19,200      | 19,231       | 0.16%      | 12                          | 19,200  | 0.00%        | 11                          | 18,643              | -2.90%     | 11                          |  |

| 38,400      | 35,714       | -6.99%     | 6                           | 38,400  | 0.00%        | 5                           | 37,287              | -2.90%     | 5                           |  |

| 57,600      | 62,500       | 8.51%      | 3                           | 57,600  | 0.00%        | 3                           | 55,930              | -2.90%     | 3                           |  |

| 76,800      | 83,333       | 8.51%      | 2                           | 76,800  | 0.00%        | 2                           | 74,574              | -2.90%     | 2                           |  |

| 96,000      | 83,333       | -13.19%    | 2                           | 115,200 | 20.00%       | 1                           | 111,861             | 16.52%     | 1                           |  |

| 115,200     | 125,000      | 8.51%      | 1                           | 115,200 | 0.00%        | 1                           | 111,861             | -2.90%     | 1                           |  |

| 250,000     | 250,000      | 0.00%      | 0                           | 230,400 | -7.84%       | 0                           | 223,722             | -10.51%    | 0                           |  |

## 10.2 USART Asynchronous Mode

In this mode, the USART uses standard non-return-tozero (NRZ) format (one START bit, eight or nine data bits, and one STOP bit). The most common data format is 8-bits. An on-chip, dedicated, 8-bit baud rate generator can be used to derive standard baud rate frequencies from the oscillator. The USART transmits and receives the LSb first. The USART's transmitter and receiver are functionally independent, but use the same data format and baud rate. The baud rate generator produces a clock, either x16 or x64 of the bit shift rate, depending on bit BRGH (TXSTA<2>). Parity is not supported by the hardware, but can be implemented in software (and stored as the ninth data bit). Asynchronous mode is stopped during SLEEP.

Asynchronous mode is selected by clearing bit SYNC (TXSTA<4>).

The USART Asynchronous module consists of the following important elements:

- · Baud Rate Generator

- Sampling Circuit

- Asynchronous Transmitter

- Asynchronous Receiver

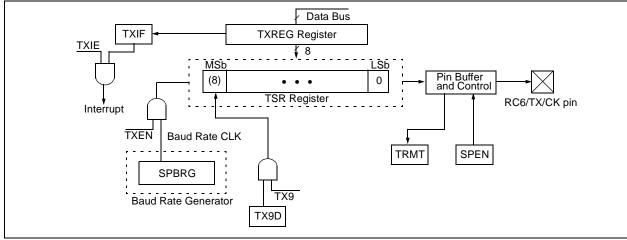

#### 10.2.1 USART ASYNCHRONOUS TRANSMITTER

The USART transmitter block diagram is shown in Figure 10-1. The heart of the transmitter is the transmit (serial) shift register (TSR). The shift register obtains its data from the read/write transmit buffer, TXREG. The TXREG register is loaded with data by firmware. The TSR register is not loaded until the STOP bit has been transmitted from the previous load. As soon as the STOP bit is transmitted, the TSR is loaded with new data from the TXREG register (if available). Once the TXREG register transfers the data to the TSR register, the TXREG register is empty. One instruction cycle later, flag bit TXIF (PIR1<4>) and flag bit TRMT (TXSTA<1>)

are set. The TXIF interrupt can be enabled/disabled by setting/clearing enable bit TXIE (PIE1<4>). Flag bit TXIF will be set, regardless of the state of enable bit TXIE and cannot be cleared in software. It will reset only when new data is loaded into the TXREG register. While flag bit TXIF indicates the status of the TXREG register, another bit TRMT (TXSTA<1>) shows the status of the TSR register. Status bit TRMT is a read only bit, which is set one instruction cycle after the TSR register becomes empty, and is cleared one instruction cycle after the TSR register is loaded. No interrupt logic is tied to this bit, so the user has to poll this bit in order to determine if the TSR register is empty.

| Note 1: | The TSR register is not mapped in data      |

|---------|---------------------------------------------|

|         | memory, so it is not available to the user. |

| 2:      | Flag bit TXIF is set when enable bit TXEN   |

is set. TXIF is cleared by loading TXREG.

Transmission is enabled by setting enable bit TXEN (TXSTA<5>). The actual transmission will not occur until the TXREG register has been loaded with data and the baud rate generator (BRG) has produced a shift clock (Figure 10-2). The transmission can also be started by first loading the TXREG register and then setting enable bit TXEN. Normally, when transmission is first started, the TSR register is empty. At that point, transfer to the TXREG register will result in an immediate transfer to TSR, resulting in an empty TXREG. A back-to-back transfer is thus possible (Figure 10-3). Clearing enable bit TXEN during a transmission will cause the transmission to be aborted and will reset the transmitter. As a result, the RC6/TX/CK pin will revert to hi-impedance.

In order to select 9-bit transmission, transmit bit TX9 (TXSTA<6>) should be set and the ninth bit should be written to TX9D (TXSTA<0>). The ninth bit must be written before writing the 8-bit data to the TXREG register. This is because a data write to the TXREG register can result in an immediate transfer of the data to the TSR register (if the TSR is empty). In such a case, an incorrect ninth data bit may be loaded in the TSR register.

### FIGURE 10-1: USART TRANSMIT BLOCK DIAGRAM

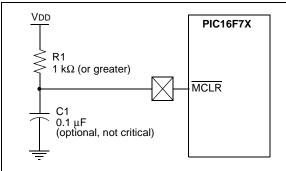

# 12.4 MCLR

PIC16F7X devices have a noise filter in the  $\overline{\text{MCLR}}$ Reset path. The filter will detect and ignore small pulses.

It should be noted that a WDT Reset does not drive MCLR pin low.

The behavior of the ESD protection on the  $\overline{\text{MCLR}}$  pin has been altered from previous devices of this family. Voltages applied to the pin that exceed its specification can result in both  $\overline{\text{MCLR}}$  Resets and excessive current beyond the device specification during the ESD event. For this reason, Microchip recommends that the  $\overline{\text{MCLR}}$ pin no longer be tied directly to VDD. The use of an RC network, as shown in Figure 12-5, is suggested.

## 12.5 Power-on Reset (POR)

A Power-on Reset pulse is generated on-chip when VDD rise is detected (in the range of 1.2V - 1.7V). To take advantage of the POR, tie the MCLR pin to VDD as described in Section 12.4. A maximum rise time for VDD is specified. See the Electrical Specifications for details.

When the device starts normal operation (exits the RESET condition), device operating parameters (voltage, frequency, temperature,...) must be met to ensure operation. If these conditions are not met, the device must be held in RESET until the operating conditions are met. For additional information, refer to Application Note, AN607, "Power-up Trouble Shooting" (DS00607).

## 12.6 Power-up Timer (PWRT)

The Power-up Timer provides a fixed 72 ms nominal time-out on power-up only from the POR. The Power-up Timer operates on an internal RC oscillator. The chip is kept in RESET as long as the PWRT is active. The PWRT's time delay allows VDD to rise to an accept-able level. A configuration bit is provided to enable/ disable the PWRT.

The power-up time delay will vary from chip to chip, due to VDD, temperature and process variation. See DC parameters for details (TPWRT, parameter #33).

## 12.7 Oscillator Start-up Timer (OST)

The Oscillator Start-up Timer (OST) provides 1024 oscillator cycles (from OSC1 input) delay after the PWRT delay is over (if enabled). This helps to ensure that the crystal oscillator or resonator has started and stabilized.

The OST time-out is invoked only for XT, LP and HS modes and only on Power-on Reset, or wake-up from SLEEP.

## 12.8 Brown-out Reset (BOR)

The configuration bit, BODEN, can enable or disable the Brown-out Reset circuit. If VDD falls below VBOR (parameter D005, about 4V) for longer than TBOR (parameter #35, about 100  $\mu$ S), the brown-out situation will reset the device. If VDD falls below VBOR for less than TBOR, a RESET may not occur.