Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                    |

|----------------------------|---------------------------------------------------------------------------|

| Core Processor             | PIC                                                                       |

| Core Size                  | 8-Bit                                                                     |

| Speed                      | 20MHz                                                                     |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                                         |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                     |

| Number of I/O              | 22                                                                        |

| Program Memory Size        | 7KB (4K x 14)                                                             |

| Program Memory Type        | FLASH                                                                     |

| EEPROM Size                | -                                                                         |

| RAM Size                   | 192 x 8                                                                   |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 5.5V                                                                 |

| Data Converters            | A/D 5x8b                                                                  |

| Oscillator Type            | External                                                                  |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                         |

| Mounting Type              | Surface Mount                                                             |

| Package / Case             | 28-SSOP (0.209", 5.30mm Width)                                            |

| Supplier Device Package    | 28-SSOP                                                                   |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16lf73t-i-ss |

|                            |                                                                           |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### Note the following details of the code protection feature on PICmicro<sup>®</sup> MCUs.

- The PICmicro family meets the specifications contained in the Microchip Data Sheet.

- Microchip believes that its family of PICmicro microcontrollers is one of the most secure products of its kind on the market today, when used in the intended manner and under normal conditions.

- There are dishonest and possibly illegal methods used to breach the code protection feature. All of these methods, to our knowledge, require using the PICmicro microcontroller in a manner outside the operating specifications contained in the data sheet. The person doing so may be engaged in theft of intellectual property.

- Microchip is willing to work with the customer who is concerned about the integrity of their code.

- Neither Microchip nor any other semiconductor manufacturer can guarantee the security of their code. Code protection does not mean that we are guaranteeing the product as "unbreakable".

- Code protection is constantly evolving. We at Microchip are committed to continuously improving the code protection features of our product.

If you have any further questions about this matter, please contact the local sales office nearest to you.

Information contained in this publication regarding device applications and the like is intended through suggestion only and may be superseded by updates. It is your responsibility to ensure that your application meets with your specifications. No representation or warranty is given and no liability is assumed by Microchip Technology Incorporated with respect to the accuracy or use of such information, or infringement of patents or other intellectual property rights arising from such use or otherwise. Use of Microchip's products as critical components in life support systems is not authorized except with express written approval by Microchip. No licenses are conveyed, implicitly or otherwise, under any intellectual property rights.

#### Trademarks

The Microchip name and logo, the Microchip logo, FilterLab, KEELOQ, MPLAB, PIC, PICmicro, PICMASTER, PICSTART, PRO MATE, SEEVAL and The Embedded Control Solutions Company are registered trademarks of Microchip Technology Incorporated in the U.S.A. and other countries.

dsPIC, ECONOMONITOR, FanSense, FlexROM, fuzzyLAB, In-Circuit Serial Programming, ICSP, ICEPIC, microID, microPort, Migratable Memory, MPASM, MPLIB, MPLINK, MPSIM, MXDEV, PICC, PICDEM, PICDEM.net, rfPIC, Select Mode and Total Endurance are trademarks of Microchip Technology Incorporated in the U.S.A.

Serialized Quick Term Programming (SQTP) is a service mark of Microchip Technology Incorporated in the U.S.A.

All other trademarks mentioned herein are property of their respective companies.

© 2002, Microchip Technology Incorporated, Printed in the U.S.A., All Rights Reserved.

Microchip received QS-9000 quality system certification for its worldwide headquarters, design and wafer fabrication facilities in Chandler and Tempe, Arizona in July 1999. The Company's quality system processes and procedures are QS-9000 compliant for its PICmicro® 8-bit MCUs, KEEL00® code hopping devices, Serial EEPROMs and microperipheral products. In addition, Microchip's quality system for the design and manufacture of development systems is ISO 9001 certified.

#### 2.2.2.1 STATUS Register

The STATUS register contains the arithmetic status of the ALU, the RESET status and the bank select bits for data memory.

The STATUS register can be the destination for any instruction, as with any other register. If the STATUS register is the destination for an instruction that affects the Z, DC, or C bits, then the write to these three bits is disabled. These bits are set or cleared according to the device logic. Furthermore, the TO and PD bits are not writable, therefore, the result of an instruction with the STATUS register as destination may be different than intended.

For example, CLRF STATUS will clear the upper three bits and set the Z bit. This leaves the STATUS register as  $000u \ u1uu$  (where u = unchanged).

It is recommended, therefore, that only BCF, BSF, SWAPF and MOVWF instructions are used to alter the STATUS register, because these instructions do not affect the Z, C, or DC bits from the STATUS register. For other instructions not affecting any status bits, see the "Instruction Set Summary."

Note 1: The <u>C</u> and <u>DC</u> bits operate as a borrow and digit borrow bit, respectively, in subtraction. See the <u>SUBLW</u> and <u>SUBWF</u> instructions for examples.

## REGISTER 2-1: STATUS REGISTER (ADDRESS 03h, 83h, 103h, 183h)

|         | R/W-0                                                                                                                 | R/W-0                                                                                                                                                                                                                                                   | R/W-0         | R-1            | R-1         | R/W-x        | R/W-x | R/W-x |  |  |  |  |  |

|---------|-----------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------|----------------|-------------|--------------|-------|-------|--|--|--|--|--|

|         | IRP                                                                                                                   | RP1                                                                                                                                                                                                                                                     | RP0           | TO             | PD          | Z            | DC    | С     |  |  |  |  |  |

|         | bit 7                                                                                                                 |                                                                                                                                                                                                                                                         |               |                |             |              |       | bit 0 |  |  |  |  |  |

| bit 7   | 1 = Bank 2                                                                                                            | ter Bank Sele<br>2, 3 (100h - 1F                                                                                                                                                                                                                        | Fh)           | or indirect ac | ldressing)  |              |       |       |  |  |  |  |  |

|         |                                                                                                                       | 0 = Bank 0, 1 (00h - FFh)                                                                                                                                                                                                                               |               |                |             |              |       |       |  |  |  |  |  |

| bit 6-5 |                                                                                                                       | <b>RP1:RP0</b> : Register Bank Select bits (used for direct addressing)                                                                                                                                                                                 |               |                |             |              |       |       |  |  |  |  |  |

|         | 01 = Bank<br>00 = Bank                                                                                                | 10 = Bank 2 (100h - 17Fh)<br>01 = Bank 1 (80h - FFh)<br>00 = Bank 0 (00h - 7Fh)<br>Each bank is 128 bytes<br>TO: Time-out bit                                                                                                                           |               |                |             |              |       |       |  |  |  |  |  |

| bit 4   | TO: Time-c                                                                                                            | out bit                                                                                                                                                                                                                                                 |               |                |             |              |       |       |  |  |  |  |  |

|         | <ul> <li>1 = After power-up, CLRWDT instruction, or SLEEP instruction</li> <li>0 = A WDT time-out occurred</li> </ul> |                                                                                                                                                                                                                                                         |               |                |             |              |       |       |  |  |  |  |  |

| bit 3   | PD: Power                                                                                                             | -down bit                                                                                                                                                                                                                                               |               |                |             |              |       |       |  |  |  |  |  |

|         |                                                                                                                       | ower-up or by<br>cution of the                                                                                                                                                                                                                          |               |                |             |              |       |       |  |  |  |  |  |

| bit 2   | z: Zero bit                                                                                                           |                                                                                                                                                                                                                                                         |               |                |             |              |       |       |  |  |  |  |  |

|         |                                                                                                                       | sult of an arith<br>sult of an arith                                                                                                                                                                                                                    |               |                |             |              |       |       |  |  |  |  |  |

| bit 1   | DC: Digit c                                                                                                           | arry/borrow b                                                                                                                                                                                                                                           | it (addwf, ae | DLW, SUBL      | W, SUBWF    | instructions | 5)    |       |  |  |  |  |  |

|         | •                                                                                                                     | r-out from the<br>ry-out from th                                                                                                                                                                                                                        |               |                |             | d            |       |       |  |  |  |  |  |

| bit 0   | C: Carry/b                                                                                                            | orrow bit (ADI                                                                                                                                                                                                                                          | WF, ADDLW     | , SUBLW, S     | SUBWF instr | uctions)     |       |       |  |  |  |  |  |

|         |                                                                                                                       | -out from the<br>ry-out from th                                                                                                                                                                                                                         |               |                |             |              |       |       |  |  |  |  |  |

|         | Note:                                                                                                                 | <b>Note:</b> For borrow, the polarity is reversed. A subtraction is executed by adding the two's complement of the second operand. For rotate (RRF, RLF) instructions, this bit is loaded with either the high or low order bit of the source register. |               |                |             |              |       |       |  |  |  |  |  |

|         | Legend:                                                                                                               |                                                                                                                                                                                                                                                         |               |                |             |              |       |       |  |  |  |  |  |

| Legend:                                    |                  |                      |                    |

|--------------------------------------------|------------------|----------------------|--------------------|

| R = Readable bit                           | W = Writable bit | U = Unimplemented    | bit, read as '0'   |

| <ul> <li>n = Value at POR reset</li> </ul> | '1' = Bit is set | '0' = Bit is cleared | x = Bit is unknown |

x = Bit is unknown

#### **PCON Register** 2.2.2.8

The Power Control (PCON) register contains flag bits to allow differentiation between a Power-on Reset (POR), a Brown-out Reset (BOR), a Watchdog Reset (WDT) and an external MCLR Reset.

BOR is unknown on POR. It must be set by Note: the user and checked on subsequent RESETS to see if BOR is clear, indicating a brown-out has occurred. The BOR status bit is not predictable if the brown-out circuit is disabled (by clearing the BODEN bit in the configuration word).

#### **REGISTER 2-8:** PCON REGISTER (ADDRESS 8Eh)

- n = Value at POR reset

|         | U-0 U-0                                                                               |             | U-0           | U-0            | U-0         | U-0         | R/W-0         | R/W-1   |  |  |  |  |

|---------|---------------------------------------------------------------------------------------|-------------|---------------|----------------|-------------|-------------|---------------|---------|--|--|--|--|

|         | _                                                                                     | _           | _             |                | —           |             | POR           | BOR     |  |  |  |  |

|         | bit 7                                                                                 |             |               |                |             |             |               | bit 0   |  |  |  |  |

|         |                                                                                       |             |               |                |             |             |               |         |  |  |  |  |

| bit 7-2 | Unimplemented: Read as '0'                                                            |             |               |                |             |             |               |         |  |  |  |  |

| bit 1   | POR: Power-on Reset Status bit                                                        |             |               |                |             |             |               |         |  |  |  |  |

|         | 1 = No Power-on Reset occurred                                                        |             |               |                |             |             |               |         |  |  |  |  |

|         | 0 = A Power-on Reset occurred (must be set in software after a Power-on Reset occurs) |             |               |                |             |             |               |         |  |  |  |  |

| bit 0   | BOR: Brov                                                                             | vn-out Rese | t Status bit  |                |             |             |               |         |  |  |  |  |

|         | 1 = No Bro                                                                            | wn-out Res  | et occurred   |                |             |             |               |         |  |  |  |  |

|         | 0 = A Brow                                                                            | n-out Rese  | t occurred (m | lust be set in | software af | ter a Brown | -out Reset of | occurs) |  |  |  |  |

|         |                                                                                       |             |               |                |             |             |               |         |  |  |  |  |

|         | Legend:                                                                               |             |               |                |             |             |               |         |  |  |  |  |

|         | R = Reada                                                                             | ble bit     | W = W         | ritable bit    | U = Unim    | plemented l | bit, read as  | '0'     |  |  |  |  |

'0' = Bit is cleared

'1' = Bit is set

NOTES:

# PIC16F7X

# REGISTER 4-1: TRISE REGISTER (ADDRESS 89h)

|       |                                                                                                                                                             | •                                                                                                                            |                | ,         |     |       |       |       |  |  |  |  |

|-------|-------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------|----------------|-----------|-----|-------|-------|-------|--|--|--|--|

|       | R-0                                                                                                                                                         | R-0                                                                                                                          | R/W-0          | R/W-0     | U-0 | R/W-1 | R/W-1 | R/W-1 |  |  |  |  |

|       | IBF                                                                                                                                                         | OBF                                                                                                                          | IBOV           | PSPMODE   | —   | Bit2  | Bit1  | Bit0  |  |  |  |  |

|       | bit 7                                                                                                                                                       |                                                                                                                              |                |           |     |       |       | bit 0 |  |  |  |  |

| bit 7 | Parallel S                                                                                                                                                  | ave Port St                                                                                                                  | atus/Contro    | l bits:   |     |       |       |       |  |  |  |  |

|       | Parallel Slave Port Status/Control bits:<br>IBF: Input Buffer Full Status bit                                                                               |                                                                                                                              |                |           |     |       |       |       |  |  |  |  |

|       |                                                                                                                                                             | <ul> <li>1 = A word has been received and is waiting to be read by the CPU</li> <li>0 = No word has been received</li> </ul> |                |           |     |       |       |       |  |  |  |  |

| bit 6 | OBF: Outp                                                                                                                                                   | out Buffer Fu                                                                                                                | ll Status bit  |           |     |       |       |       |  |  |  |  |

|       | <ul> <li>1 = The output buffer still holds a previously written word</li> <li>0 = The output buffer has been read</li> </ul>                                |                                                                                                                              |                |           |     |       |       |       |  |  |  |  |

| bit 5 | IBOV: Inpu                                                                                                                                                  | IBOV: Input Buffer Overflow Detect bit (in Microprocessor mode)                                                              |                |           |     |       |       |       |  |  |  |  |

|       | <ul> <li>1 = A write occurred when a previously input word has not been read<br/>(must be cleared in software)</li> <li>0 = No overflow occurred</li> </ul> |                                                                                                                              |                |           |     |       |       |       |  |  |  |  |

| bit 4 | PSPMODE: Parallel Slave Port Mode Select bit                                                                                                                |                                                                                                                              |                |           |     |       |       |       |  |  |  |  |

|       | 1 = Parallel Slave Port mode                                                                                                                                |                                                                                                                              |                |           |     |       |       |       |  |  |  |  |

|       | 0 = General Purpose I/O mode                                                                                                                                |                                                                                                                              |                |           |     |       |       |       |  |  |  |  |

| bit 3 | Unimplem                                                                                                                                                    | nented: Read                                                                                                                 | d as '0'       |           |     |       |       |       |  |  |  |  |

| bit 2 | PORTE Da                                                                                                                                                    | PORTE Data Direction bits:                                                                                                   |                |           |     |       |       |       |  |  |  |  |

|       | Bit2: Direction Control bit for pin RE2/CS/AN7                                                                                                              |                                                                                                                              |                |           |     |       |       |       |  |  |  |  |

|       | 1 = Input<br>0 = Output                                                                                                                                     | 1 = Input<br>0 = Output                                                                                                      |                |           |     |       |       |       |  |  |  |  |

| bit 1 | Bit1: Direc                                                                                                                                                 | tion Control                                                                                                                 | bit for pin RE | E1/WR/AN6 |     |       |       |       |  |  |  |  |

|       | 1 = Input<br>0 = Output                                                                                                                                     | t                                                                                                                            |                |           |     |       |       |       |  |  |  |  |

| bit 0 | Bit0: Direc                                                                                                                                                 | tion Control                                                                                                                 | bit for pin RE | E0/RD/AN5 |     |       |       |       |  |  |  |  |

|       | 1 = Input<br>0 = Output                                                                                                                                     |                                                                                                                              |                |           |     |       |       |       |  |  |  |  |

| Legend:                  |                  |                      |                    |

|--------------------------|------------------|----------------------|--------------------|

| R = Readable bit         | W = Writable bit | U = Unimplemented    | bit, read as '0'   |

| - n = Value at POR reset | '1' = Bit is set | '0' = Bit is cleared | x = Bit is unknown |

| Name       | Bit# | Buffer Type           | Function                                                                                                                                                                                                                          |

|------------|------|-----------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| RE0/RD/AN5 | bit0 | ST/TTL <sup>(1)</sup> | Input/output port pin or read control input in Parallel Slave Port mode or<br>analog input.<br>For RD (PSP mode):<br>1 = IDLE<br>0 = Read operation. Contents of PORTD register output to PORTD I/O<br>pins (if chip selected).   |

| RE1/WR/AN6 | bit1 | ST/TTL <sup>(1)</sup> | Input/output port pin or write control input in Parallel Slave Port mode<br>or analog input.<br>For WR (PSP mode):<br>1 = IDLE<br>0 = Write operation. Value of PORTD I/O pins latched into PORTD<br>register (if chip selected). |

| RE2/CS/AN7 | bit2 | ST/TTL <sup>(1)</sup> | Input/output port pin or chip select control input in Parallel Slave Port<br>mode or analog input.<br>For CS (PSP mode):<br>1 = Device is not selected<br>0 = Device is selected                                                  |

Legend: ST = Schmitt Trigger input, TTL = TTL input **Note 1:** Input buffers are Schmitt Triggers when in I/O mode and TTL buffers when in Parallel Slave Port mode.

| TABLE 4-10: SUMMARY OF REGISTERS ASSOCIATED WITH PORTE | <b>TABLE 4-10</b> : | SUMMARY OF REGISTERS ASSOCIATED WITH PORTE |

|--------------------------------------------------------|---------------------|--------------------------------------------|

|--------------------------------------------------------|---------------------|--------------------------------------------|

| Addr | Name   | Bit 7 | Bit 6 | Bit 5 | Bit 4   | Bit 3 | Bit 2       | Bit 1       | Bit 0   | Value on:<br>POR,<br>BOR | Value on all<br>other<br>RESETS |

|------|--------|-------|-------|-------|---------|-------|-------------|-------------|---------|--------------------------|---------------------------------|

| 09h  | PORTE  | —     | —     |       | —       |       | RE2         | RE1         | RE0     | xxx                      | uuu                             |

| 89h  | TRISE  | IBF   | OBF   | IBOV  | PSPMODE | _     | PORTE D     | ata Directi | on bits | 0000 -111                | 0000 -111                       |

| 9Fh  | ADCON1 | —     | _     |       | _       | _     | PCFG2 PCFG1 |             | PCFG0   | 000                      | 000                             |

Legend: x = unknown, u = unchanged, - = unimplemented, read as '0'. Shaded cells are not used by PORTE.

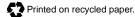

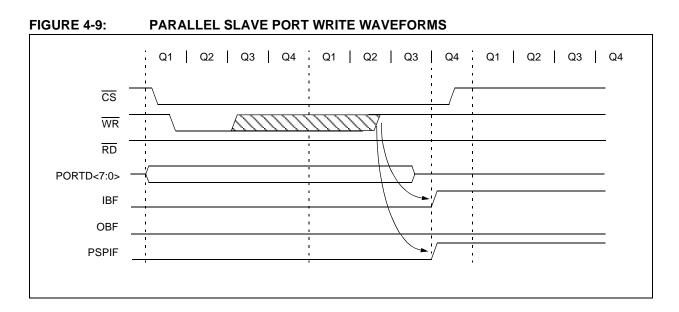

#### FIGURE 4-10: PARALLEL SLAVE PORT READ WAVEFORMS

#### TABLE 4-11: REGISTERS ASSOCIATED WITH PARALLEL SLAVE PORT

| Address | Name   | Bit 7                | Bit 6   | Bit 5      | Bit 4   | Bit 3     | Bit 2 Bit 1 |                           | Bit 0  | Value on:<br>POR,<br>BOR | Value on<br>all other<br>RESETS |

|---------|--------|----------------------|---------|------------|---------|-----------|-------------|---------------------------|--------|--------------------------|---------------------------------|

| 08h     | PORTD  | Port data I          | atch wh | nen writte |         | xxxx xxxx | uuuu uuuu   |                           |        |                          |                                 |

| 09h     | PORTE  | —                    |         | —          |         | —         | RE2 RE1 RE0 |                           | xxx    | uuu                      |                                 |

| 89h     | TRISE  | IBF                  | OBF     | IBOV       | PSPMODE | _         | PORTE D     | PORTE Data Direction Bits |        |                          | 0000 -111                       |

| 0Ch     | PIR1   | PSPIF <sup>(1)</sup> | ADIF    | RCIF       | TXIF    | SSPIF     | CCP1IF      | TMR2IF                    | TMR1IF | 0000 0000                | 0000 0000                       |

| 8Ch     | PIE1   | PSPIE <sup>(1)</sup> | ADIE    | RCIE       | TXIE    | SSPIE     | CCP1IE      | TMR2IE                    | TMR1IE | 0000 0000                | 0000 0000                       |

| 9Fh     | ADCON1 | _                    | _       | _          | _       | _         | PCFG2       | PCFG1                     | PCFG0  | 000                      | 000                             |

Legend: x = unknown, u = unchanged, - = unimplemented, read as '0'. Shaded cells are not used by the Parallel Slave Port.

**Note 1:** Bits PSPIE and PSPIF are reserved on the PIC16F73/76; always maintain these bits clear.

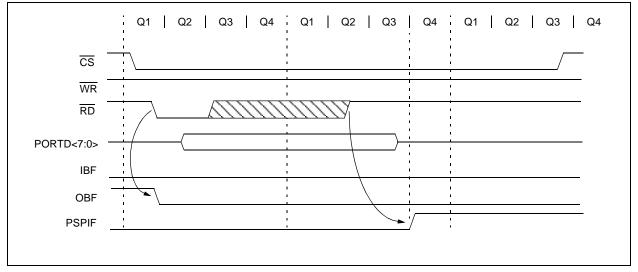

#### FIGURE 9-1: SSP BLOCK DIAGRAM (SPI MODE)

To enable the serial port, SSP enable bit, SSPEN (SSPCON<5>) must be set. To reset or reconfigure SPI mode, clear bit SSPEN, re-initialize the SSPCON register, and then set bit SSPEN. This configures the SDI, SDO, SCK, and SS pins as serial port pins. For the pins to behave as the serial port function, they must have their data direction bits (in the TRISC register) appropriately programmed. That is:

- SDI must have TRISC<4> set

- SDO must have TRISC<5> cleared

- SCK (Master mode) must have TRISC<3> cleared

- SCK (Slave mode) must have TRISC<3> set

- SS must have TRISA<5> set and ADCON must be configured such that RA5 is a digital I/O

Note 1: When the SPI is in Slave mode with SS pin control enabled (SSPCON<3:0> = 0100), the SPI module will reset if the SS pin is set to VDD.

- 2: If the SPI is used in Slave mode with CKE = '1', then the SS pin control must be enabled.

- 3: When the SPI is in Slave mode with  $\overline{SS}$  pin control enabled (SSPCON<3:0> = '0100'), the state of the  $\overline{SS}$  pin can affect the state read back from the TRISC<5> bit. The Peripheral OE signal from the SSP module into PORTC controls the state that is read back from the TRISC<5> bit (see Section 4.3 for information on PORTC). If Read-Modify-Write instructions, such as BSF are performed on the TRISC register while the  $\overline{SS}$  pin is high, this will cause the TRISC<5> bit to be set, thus disabling the SDO output.

| Address               | Name    | Bit 7                | Bit 6       | Bit 5      | Bit 4    | Bit 3      | Bit 2       | Bit 1   | Bit 0  | Value on:<br>POR,<br>BOR | Value on<br>all other<br>RESETS |

|-----------------------|---------|----------------------|-------------|------------|----------|------------|-------------|---------|--------|--------------------------|---------------------------------|

| 0Bh,8Bh.<br>10Bh,18Bh | INTCON  | GIE                  | PEIE        | TMR0IE     | INTE     | RBIE       | TMR0IF      | INTF    | RBIF   | 0000 000x                | 0000 000u                       |

| 0Ch                   | PIR1    | PSPIF <sup>(1)</sup> | ADIF        | RCIF       | TXIF     | SSPIF      | CCP1IF      | TMR2IF  | TMR1IF | 0000 0000                | 0000 0000                       |

| 8Ch                   | PIE1    | PSPIE <sup>(1)</sup> | ADIE        | RCIE       | TXIE     | SSPIE      | CCP1IE      | TMR2IE  | TMR1IE | 0000 0000                | 0000 0000                       |

| 87h                   | TRISC   | PORTC Da             | ta Directio | on Registe | r        |            |             |         |        | 1111 1111                | 1111 1111                       |

| 13h                   | SSPBUF  | Synchronou           | us Serial F | Port Recei | ve Buff  | er/Transm  | it Register |         |        | xxxx xxxx                | uuuu uuuu                       |

| 14h                   | SSPCON  | WCOL                 | SSPOV       | SSPEN      | СКР      | SSPM3      | SSPM2       | SSPM1   | SSPM0  | 0000 0000                | 0000 0000                       |

| 85h                   | TRISA   | —                    | _           | PORTA D    | Data Dii | rection Re | 11 1111     | 11 1111 |        |                          |                                 |

| 94h                   | SSPSTAT | SMP                  | CKE         | D/A        | Р        | S          | R/W         | UA      | BF     | 0000 0000                | 0000 0000                       |

#### TABLE 9-1:REGISTERS ASSOCIATED WITH SPI OPERATION

Legend: x = unknown, u = unchanged, - = unimplemented, read as '0'. Shaded cells are not used by the SSP in SPI mode.

**Note 1:** Bits PSPIE and PSPIF are reserved on the PIC16F73/76; always maintain these bits clear.

|              |         | Fosc = 20 M | Hz                          |         | Fosc = 16 M | Hz                          |         | Fosc = 10 M | Hz                          |

|--------------|---------|-------------|-----------------------------|---------|-------------|-----------------------------|---------|-------------|-----------------------------|

| BAUD<br>RATE | BAUD    | %<br>ERROR  | SPBRG<br>VALUE<br>(DECIMAL) | BAUD    | %<br>ERROR  | SPBRG<br>VALUE<br>(DECIMAL) | BAUD    | %<br>ERROR  | SPBRG<br>VALUE<br>(DECIMAL) |

| 1200         | 1,221   | 1.73%       | 255                         | 1,202   | 0.16%       | 207                         | 1,202   | 0.16%       | 129                         |

| 2400         | 2,404   | 0.16%       | 129                         | 2,404   | 0.16%       | 103                         | 2,404   | 0.16%       | 64                          |

| 9600         | 9,470   | -1.36%      | 32                          | 9,615   | 0.16%       | 25                          | 9,766   | 1.73%       | 15                          |

| 19,200       | 19,531  | 1.73%       | 15                          | 19,231  | 0.16%       | 12                          | 19,531  | 1.73%       | 7                           |

| 38,400       | 39,063  | 1.73%       | 7                           | 35,714  | -6.99%      | 6                           | 39,063  | 1.73%       | 3                           |

| 57,600       | 62,500  | 8.51%       | 4                           | 62,500  | 8.51%       | 3                           | 52,083  | -9.58%      | 2                           |

| 76,800       | 78,125  | 1.73%       | 3                           | 83,333  | 8.51%       | 2                           | 78,125  | 1.73%       | 1                           |

| 96,000       | 104,167 | 8.51%       | 2                           | 83,333  | -13.19%     | 2                           | 78,125  | -18.62%     | 1                           |

| 115,200      | 104,167 | -9.58%      | 2                           | 125,000 | 8.51%       | 1                           | 78,125  | -32.18%     | 1                           |

| 250,000      | 312,500 | 25.00%      | 0                           | 250,000 | 0.00%       | 0                           | 156,250 | -37.50%     | 0                           |

# TABLE 10-3:BAUD RATES FOR ASYNCHRONOUS MODE (BRGH = 0)

|              |        | Fosc = 4 Mł | łz                          |        | Fosc = 3.6864 | MHz                         | Fosc = 3.579545 MHz |            |                             |  |

|--------------|--------|-------------|-----------------------------|--------|---------------|-----------------------------|---------------------|------------|-----------------------------|--|

| BAUD<br>RATE | BAUD   | %<br>ERROR  | SPBRG<br>VALUE<br>(DECIMAL) | BAUD   | %<br>ERROR    | SPBRG<br>VALUE<br>(DECIMAL) | BAUD                | %<br>ERROR | SPBRG<br>VALUE<br>(DECIMAL) |  |

| 300          | 300    | 0.16%       | 207                         | 300    | 0.00%         | 191                         | 301                 | 0.23%      | 185                         |  |

| 1200         | 1,202  | 0.16%       | 51                          | 1,200  | 0.00%         | 47                          | 1,190               | -0.83%     | 46                          |  |

| 2400         | 2,404  | 0.16%       | 25                          | 2,400  | 0.00%         | 23                          | 2,432               | 1.32%      | 22                          |  |

| 9600         | 8,929  | -6.99%      | 6                           | 9,600  | 0.00%         | 5                           | 9,322               | -2.90%     | 5                           |  |

| 19,200       | 20,833 | 8.51%       | 2                           | 19,200 | 0.00%         | 2                           | 18,643              | -2.90%     | 2                           |  |

| 38,400       | 31,250 | -18.62%     | 1                           | 28,800 | -25.00%       | 1                           | 27,965              | -27.17%    | 1                           |  |

| 57,600       | 62,500 | 8.51%       | 0                           | 57,600 | 0.00%         | 0                           | 55,930              | -2.90%     | 0                           |  |

| 76,800       | 62,500 | -18.62%     | 0                           | —      | _             | _                           | _                   | _          | —                           |  |

# TABLE 10-4: BAUD RATES FOR ASYNCHRONOUS MODE (BRGH = 1)

|              |         | Fosc = 20 M | Hz                          |         | Fosc = 16 M | Hz                          |         | Fosc = 10 MI | Hz                          |

|--------------|---------|-------------|-----------------------------|---------|-------------|-----------------------------|---------|--------------|-----------------------------|

| BAUD<br>RATE | BAUD    | %<br>ERROR  | SPBRG<br>VALUE<br>(DECIMAL) | BAUD    | %<br>ERROR  | SPBRG<br>VALUE<br>(DECIMAL) | BAUD    | %<br>ERROR   | SPBRG<br>VALUE<br>(DECIMAL) |

| 2400         | _       | _           | _                           | —       | _           | _                           | 2,441   | 1.73%        | 255                         |

| 9600         | 9,615   | 0.16%       | 129                         | 9,615   | 0.16%       | 103                         | 9,615   | 0.16%        | 64                          |

| 19,200       | 19,231  | 0.16%       | 64                          | 19,231  | 0.16%       | 51                          | 18,939  | -1.36%       | 32                          |

| 38,400       | 37,879  | -1.36%      | 32                          | 38,462  | 0.16%       | 25                          | 39,063  | 1.73%        | 15                          |

| 57,600       | 56,818  | -1.36%      | 21                          | 58,824  | 2.12%       | 16                          | 56,818  | -1.36%       | 10                          |

| 76,800       | 78,125  | 1.73%       | 15                          | 76,923  | 0.16%       | 12                          | 78,125  | 1.73%        | 7                           |

| 96,000       | 96,154  | 0.16%       | 12                          | 100,000 | 4.17%       | 9                           | 89,286  | -6.99%       | 6                           |

| 115,200      | 113,636 | -1.36%      | 10                          | 111,111 | -3.55%      | 8                           | 125,000 | 8.51%        | 4                           |

| 250,000      | 250,000 | 0.00%       | 4                           | 250,000 | 0.00%       | 3                           | 208,333 | -16.67%      | 2                           |

| 300,000      | 312,500 | 4.17%       | 3                           | 333,333 | 11.11%      | 2                           | 312,500 | 4.17%        | 1                           |

| BAUD                |         | Fosc = 4 MH | Iz                          | F       | osc = 3.6864 | MHz                         | Fo      | osc = 3.579545 | MHz                         |

|---------------------|---------|-------------|-----------------------------|---------|--------------|-----------------------------|---------|----------------|-----------------------------|

| BAUD<br>RATE<br>(K) | BAUD    | %<br>ERROR  | SPBRG<br>VALUE<br>(DECIMAL) | BAUD    | %<br>ERROR   | SPBRG<br>VALUE<br>(DECIMAL) | BAUD    | %<br>ERROR     | SPBRG<br>VALUE<br>(DECIMAL) |

| 1200                | 1,202   | 0.16%       | 207                         | 1,200   | 0.00%        | 191                         | 1,203   | 0.23%          | 185                         |

| 2400                | 2,404   | 0.16%       | 103                         | 2,400   | 0.00%        | 95                          | 2,406   | 0.23%          | 92                          |

| 9600                | 9,615   | 0.16%       | 25                          | 9,600   | 0.00%        | 23                          | 9,727   | 1.32%          | 22                          |

| 19,200              | 19,231  | 0.16%       | 12                          | 19,200  | 0.00%        | 11                          | 18,643  | -2.90%         | 11                          |

| 38,400              | 35,714  | -6.99%      | 6                           | 38,400  | 0.00%        | 5                           | 37,287  | -2.90%         | 5                           |

| 57,600              | 62,500  | 8.51%       | 3                           | 57,600  | 0.00%        | 3                           | 55,930  | -2.90%         | 3                           |

| 76,800              | 83,333  | 8.51%       | 2                           | 76,800  | 0.00%        | 2                           | 74,574  | -2.90%         | 2                           |

| 96,000              | 83,333  | -13.19%     | 2                           | 115,200 | 20.00%       | 1                           | 111,861 | 16.52%         | 1                           |

| 115,200             | 125,000 | 8.51%       | 1                           | 115,200 | 0.00%        | 1                           | 111,861 | -2.90%         | 1                           |

| 250,000             | 250,000 | 0.00%       | 0                           | 230,400 | -7.84%       | 0                           | 223,722 | -10.51%        | 0                           |

Steps to follow when setting up an Asynchronous Transmission:

- 1. Initialize the SPBRG register for the appropriate baud rate. If a high speed baud rate is desired, set bit BRGH (Section 10.1).

- 2. Enable the asynchronous serial port by clearing bit SYNC and setting bit SPEN.

- 3. If interrupts are desired, then set enable bit TXIE.

- 4. If 9-bit transmission is desired, then set transmit bit TX9.

- 5. Enable the transmission by setting bit TXEN, which will also set bit TXIF.

- 6. If 9-bit transmission is selected, the ninth bit should be loaded in bit TX9D.

- 7. Load data to the TXREG register (starts transmission).

- 8. If using interrupts, ensure that GIE and PEIE in the INTCON register are set.

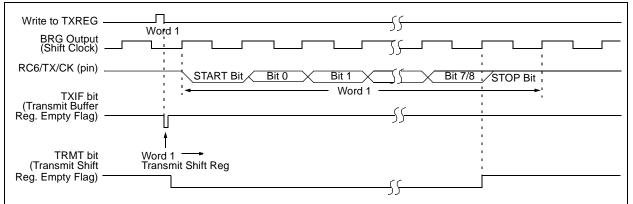

## FIGURE 10-2: ASYNCHRONOUS MASTER TRANSMISSION

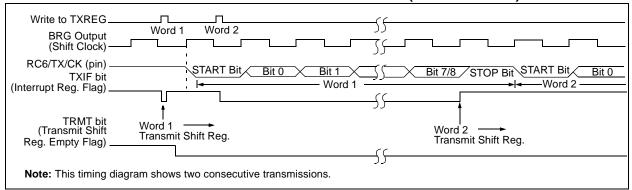

#### FIGURE 10-3: ASYNCHRONOUS MASTER TRANSMISSION (BACK TO BACK)

#### TABLE 10-5: REGISTERS ASSOCIATED WITH ASYNCHRONOUS TRANSMISSION

| Address                | Name                               | Bit 7                | Bit 6     | Bit 5   | Bit 4 | Bit 3 | Bit 2  | Bit 1  | Bit 0  | Value on:<br>POR,<br>BOR | Value on<br>all other<br>RESETS |

|------------------------|------------------------------------|----------------------|-----------|---------|-------|-------|--------|--------|--------|--------------------------|---------------------------------|

| 0Bh, 8Bh,<br>10Bh,18Bh | INTCON                             | GIE                  | PEIE      | TMR0IE  | INTE  | RBIE  | TMR0IF | INTF   | RBIF   | 0000 000x                | 0000 000u                       |

| 0Ch                    | PIR1                               | PSPIF <sup>(1)</sup> | ADIF      | RCIF    | TXIF  | SSPIF | CCP1IF | TMR2IF | TMR1IF | 0000 0000                | 0000 0000                       |

| 18h                    | RCSTA                              | SPEN                 | RX9       | SREN    | CREN  |       | FERR   | OERR   | RX9D   | x00-000x                 | x00- 0000                       |

| 19h                    | TXREG                              | USART Tra            | ansmit Re | egister |       |       |        |        |        | 0000 0000                | 0000 0000                       |

| 8Ch                    | PIE1                               | PSPIE <sup>(1)</sup> | ADIE      | RCIE    | TXIE  | SSPIE | CCP1IE | TMR2IE | TMR1IE | 0000 0000                | 0000 0000                       |

| 98h                    | TXSTA                              | CSRC                 | TX9       | TXEN    | SYNC  |       | BRGH   | TRMT   | TX9D   | 0000 -010                | 0000 -010                       |

| 99h                    | SPBRG Baud Rate Generator Register |                      |           |         |       |       |        |        |        | 0000 0000                | 0000 0000                       |

Legend: x = unknown, - = unimplemented locations read as '0'. Shaded cells are not used for asynchronous transmission. Note 1: Bits PSPIE and PSPIF are reserved on the PIC16F73/76; always maintain these bits clear.

| Address                | Name   | Bit 7                        | Bit 6    | Bit 5   | Bit 4 | Bit 3 | Bit 2  | Bit 1  | Bit 0  | Value on:<br>POR,<br>BOR | Value on<br>all other<br>RESETS |

|------------------------|--------|------------------------------|----------|---------|-------|-------|--------|--------|--------|--------------------------|---------------------------------|

| 0Bh, 8Bh,<br>10Bh,18Bh | INTCON | GIE                          | PEIE     | TMR0IE  | INTE  | RBIE  | TMR0IF | INTF   | RBIF   | 0000 000x                | 0000 000u                       |

| 0Ch                    | PIR1   | PSPIF <sup>(1)</sup>         | ADIF     | RCIF    | TXIF  | SSPIF | CCP1IF | TMR2IF | TMR1IF | 0000 0000                | 0000 0000                       |

| 18h                    | RCSTA  | SPEN                         | RX9      | SREN    | CREN  | ADDEN | FERR   | OERR   | RX9D   | 0000 000x                | 0000 000x                       |

| 19h                    | TXREG  | USART Tr                     | ansmit R | egister |       |       |        |        |        | 0000 0000                | 0000 0000                       |

| 8Ch                    | PIE1   | PSPIE <sup>(1)</sup>         | ADIE     | RCIE    | TXIE  | SSPIE | CCP1IE | TMR2IE | TMR1IE | 0000 0000                | 0000 0000                       |

| 98h                    | TXSTA  | CSRC                         | TX9      | TXEN    | SYNC  | —     | BRGH   | TRMT   | TX9D   | 0000 -010                | 0000 -010                       |

| 99h                    | SPBRG  | Baud Rate Generator Register |          |         |       |       |        |        |        | 0000 0000                | 0000 0000                       |

Legend: x = unknown, - = unimplemented, read as '0'. Shaded cells are not used for synchronous slave transmission.

Note 1: Bits PSPIE and PSPIF are reserved on the PIC16F73/76 devices; always maintain these bits clear.

#### 10.4.2 USART SYNCHRONOUS SLAVE RECEPTION

The operation of the Synchronous Master and Slave modes is identical, except in the case of the SLEEP mode. Bit SREN is a "don't care" in Slave mode.

If receive is enabled by setting bit CREN prior to the SLEEP instruction, then a word may be received during SLEEP. On completely receiving the word, the RSR register will transfer the data to the RCREG register and if enable bit RCIE bit is set, the interrupt generated will wake the chip from SLEEP. If the global interrupt is enabled, the program will branch to the interrupt vector (0004h).

Follow these steps when setting up a Synchronous Slave Reception:

- Enable the synchronous master serial port by setting bits SYNC and SPEN and clearing bit CSRC.

- 2. If interrupts are desired, set enable bit RCIE.

- 3. If 9-bit reception is desired, set bit RX9.

- 4. To enable reception, set enable bit CREN.

- 5. Flag bit RCIF will be set when reception is complete and an interrupt will be generated, if enable bit RCIE was set.

- Read the RCSTA register to get the ninth bit (if enabled) and determine if any error occurred during reception.

- 7. Read the 8-bit received data by reading the RCREG register.

- 8. If any error occurred, clear the error by clearing bit CREN.

- 9. If using interrupts, ensure that GIE and PEIE in the INTCON register are set.

| Address                | Name   | Bit 7                | Bit 6                        | Bit 5   | Bit 4 | Bit 3 | Bit 2  | Bit 1  | Bit 0  | Value on:<br>POR,<br>BOR | Value on<br>all other<br>RESETS |

|------------------------|--------|----------------------|------------------------------|---------|-------|-------|--------|--------|--------|--------------------------|---------------------------------|

| 0Bh, 8Bh,<br>10Bh,18Bh | INTCON | GIE                  | PEIE                         | TMR0IE  | INTE  | RBIE  | TMR0IF | INTF   | RBIF   | 0000 000x                | 0000 000u                       |

| 0Ch                    | PIR1   | PSPIF <sup>(1)</sup> | ADIF                         | RCIF    | TXIF  | SSPIF | CCP1IF | TMR2IF | TMR1IF | 0000 0000                | 0000 0000                       |

| 18h                    | RCSTA  | SPEN                 | RX9                          | SREN    | CREN  | ADDEN | FERR   | OERR   | RX9D   | x000 0000x               | 0000 000x                       |

| 1Ah                    | RCREG  | USART R              | eceive R                     | egister |       |       |        |        |        | 0000 0000                | 0000 0000                       |

| 8Ch                    | PIE1   | PSPIE <sup>(1)</sup> | ADIE                         | RCIE    | TXIE  | SSPIE | CCP1IE | TMR2IE | TMR1IE | 0000 0000                | 0000 0000                       |

| 98h                    | TXSTA  | CSRC                 | TX9                          | TXEN    | SYNC  | —     | BRGH   | TRMT   | TX9D   | 0000 -010                | 0000 -010                       |

| 99h                    | SPBRG  | Baud Rate            | Baud Rate Generator Register |         |       |       |        |        |        | 0000 0000                | 0000 0000                       |

#### TABLE 10-10: REGISTERS ASSOCIATED WITH SYNCHRONOUS SLAVE RECEPTION

Legend: x = unknown, - = unimplemented, read as '0'. Shaded cells are not used for synchronous slave reception. **Note 1:** Bits PSPIE and PSPIF are reserved on the PIC16F73/76 devices, always maintain these bits clear.

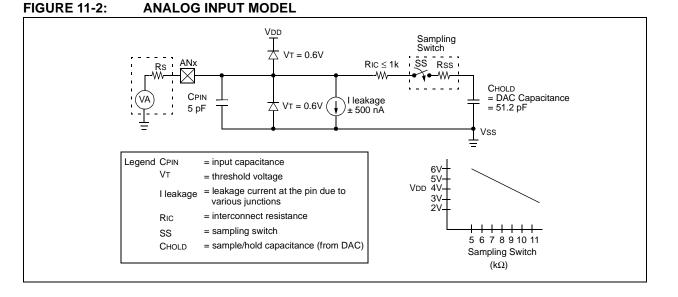

## 11.1 A/D Acquisition Requirements

For the A/D converter to meet its specified accuracy, the charge holding capacitor (CHOLD) must be allowed to fully charge to the input channel voltage level. The analog input model is shown in Figure 11-2. The source impedance (Rs) and the internal sampling switch (Rss) impedance directly affect the time required to charge the capacitor CHOLD. The sampling switch (Rss) impedance varies over the device voltage (VDD), see Figure 11-2. The source impedance affects the offset voltage at the analog input (due to pin leakage current). The maximum recommended impedance for analog sources is 10 k $\Omega$ . After the analog input channel is selected (changed), the acquisition period must pass before the conversion can be started.

To calculate the minimum acquisition time, TACQ, see the PICmicro<sup>TM</sup> Mid-Range MCU Family Reference Manual (DS33023). In general, however, given a maximum source impedance of 10 k $\Omega$  and at a temperature of 100°C, TACQ will be no more than 16 µsec.

## TABLE 11-1: TAD vs. MAXIMUM DEVICE OPERATING FREQUENCIES (STANDARD DEVICES (C))

| AD Cloc                 | k Source (Tad) | Maximum Device Frequency |

|-------------------------|----------------|--------------------------|

| Operation               | ADCS1:ADCS0    | Max.                     |

| 2Tosc                   | 0.0            | 1.25 MHz                 |

| 8Tosc                   | 01             | 5 MHz                    |

| 32Tosc                  | 10             | 20 MHz                   |

| RC <sup>(1, 2, 3)</sup> | 11             | (Note 1)                 |

Note 1: The RC source has a typical TAD time of 4 µs but can vary between 2-6 µs.

2: When the device frequencies are greater than 1 MHz, the RC A/D conversion clock source is only recommended for SLEEP operation.

3: For extended voltage devices (LC), please refer to the Electrical Specifications section.

# 14.13 PICDEM 3 Low Cost PIC16CXXX Demonstration Board

The PICDEM 3 demonstration board is a simple demonstration board that supports the PIC16C923 and PIC16C924 in the PLCC package. It will also support future 44-pin PLCC microcontrollers with an LCD Module. All the necessary hardware and software is included to run the basic demonstration programs. The user can program the sample microcontrollers provided with the PICDEM 3 demonstration board on a PRO MATE II device programmer, or a PICSTART Plus development programmer with an adapter socket, and easily test firmware. The MPLAB ICE in-circuit emulator may also be used with the PICDEM 3 demonstration board to test firmware. A prototype area has been provided to the user for adding hardware and connecting it to the microcontroller socket(s). Some of the features include a RS-232 interface, push button switches, a potentiometer for simulated analog input, a thermistor and separate headers for connection to an external LCD module and a keypad. Also provided on the PICDEM 3 demonstration board is a LCD panel, with 4 commons and 12 segments, that is capable of displaying time, temperature and day of the week. The PICDEM 3 demonstration board provides an additional RS-232 interface and Windows software for showing the demultiplexed LCD signals on a PC. A simple serial interface allows the user to construct a hardware demultiplexer for the LCD signals.

# 14.14 PICDEM 17 Demonstration Board

The PICDEM 17 demonstration board is an evaluation board that demonstrates the capabilities of several Microchip microcontrollers, including PIC17C752, PIC17C756A, PIC17C762 and PIC17C766. All necessary hardware is included to run basic demo programs, which are supplied on a 3.5-inch disk. A programmed sample is included and the user may erase it and program it with the other sample programs using the PRO MATE II device programmer, or the PICSTART Plus development programmer, and easily debug and test the sample code. In addition, the PICDEM 17 demonstration board supports downloading of programs to and executing out of external FLASH memory on board. The PICDEM 17 demonstration board is also usable with the MPLAB ICE in-circuit emulator, or the PICMASTER emulator and all of the sample programs can be run and modified using either emulator. Additionally, a generous prototype area is available for user hardware.

# 14.15 KEELOQ Evaluation and Programming Tools

KEELOQ evaluation and programming tools support Microchip's HCS Secure Data Products. The HCS evaluation kit includes a LCD display to show changing codes, a decoder to decode transmissions and a programming interface to program test transmitters. NOTES:

| Param.<br>No. | Symbol  | Characte               | eristic      | Min        | Max  | Units | Conditions                                  |

|---------------|---------|------------------------|--------------|------------|------|-------|---------------------------------------------|

| 100*          | Тнідн   | Clock high time        | 100 kHz mode | 4.0        |      | μs    | Device must operate at a minimum of 1.5 MHz |

|               |         |                        | 400 kHz mode | 0.6        |      | μs    | Device must operate at a minimum of 10 MHz  |

|               |         |                        | SSP Module   | 1.5Tcy     |      |       |                                             |

| 101*          | TLOW    | Clock low time         | 100 kHz mode | 4.7        |      | μs    | Device must operate at a minimum of 1.5 MHz |

|               |         |                        | 400 kHz mode | 1.3        |      | μs    | Device must operate at a minimum of 10 MHz  |

|               |         |                        | SSP Module   | 1.5Tcy     | _    |       |                                             |

| 102*          | Tr      | SDA and SCL rise       | 100 kHz mode | —          | 1000 | ns    |                                             |

|               |         | time                   | 400 kHz mode | 20 + 0.1Св | 300  | ns    | CB is specified to be from 10 - 400 pF      |

| 103*          | TF      | SDA and SCL fall       | 100 kHz mode | —          | 300  | ns    |                                             |

|               |         | time                   | 400 kHz mode | 20 + 0.1Св | 300  | ns    | CB is specified to be from 10 - 400 pF      |

| 90*           | TSU:STA | START condition        | 100 kHz mode | 4.7        |      | μs    | Only relevant for                           |

|               |         | setup time             | 400 kHz mode | 0.6        |      | μs    | Repeated START condition                    |

| 91*           | THD:STA | START condition        | 100 kHz mode | 4.0        | _    | μs    | After this period the first                 |

|               |         | hold time              | 400 kHz mode | 0.6        | _    | μs    | clock pulse is generated                    |

| 106*          | THD:DAT | Data input hold time   | 100 kHz mode | 0          | —    | ns    |                                             |

|               |         |                        | 400 kHz mode | 0          | 0.9  | μs    |                                             |

| 107*          | TSU:DAT | Data input setup       | 100 kHz mode | 250        | —    | ns    | (Note 2)                                    |

|               |         | time                   | 400 kHz mode | 100        | —    | ns    |                                             |

| 92*           | Tsu:sto | STOP condition         | 100 kHz mode | 4.7        | —    | μs    |                                             |

|               |         | setup time             | 400 kHz mode | 0.6        | _    | μs    |                                             |

| 109*          | ΤΑΑ     | Output valid from      | 100 kHz mode | —          | 3500 | ns    | (Note 1)                                    |

|               |         | clock                  | 400 kHz mode | —          | —    | ns    |                                             |

| 110*          | TBUF    | Bus free time          | 100 kHz mode | 4.7        | _    | μs    | Time the bus must be free                   |

|               |         |                        | 400 kHz mode | 1.3        | —    | μs    | before a new transmission<br>can start      |

|               | Св      | Bus capacitive loading | ng           | -          | 400  | pF    |                                             |

## TABLE 15-9: I<sup>2</sup>C BUS DATA REQUIREMENTS

\* These parameters are characterized but not tested.

**Note 1:** As a transmitter, the device must provide this internal minimum delay time to bridge the undefined region (min. 300 ns) of the falling edge of SCL to avoid unintended generation of START or STOP conditions.

2: A Fast mode (400 kHz) I<sup>2</sup>C bus device can be used in a Standard mode (100 kHz) I<sup>2</sup>C bus system, but the requirement TsU:DAT ≥ 250 ns must then be met. This will automatically be the case if the device does not stretch the LOW period of the SCL signal. If such a device does stretch the LOW period of the SCL signal, it must output the next data bit to the SDA line TR max. + TSU:DAT = 1000 + 250 = 1250 ns (according to the Standard mode I<sup>2</sup>C bus specification), before the SCL line is released.

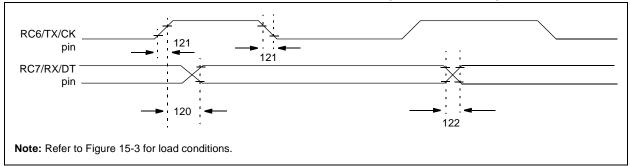

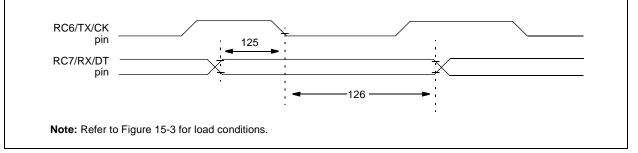

#### TABLE 15-10: USART SYNCHRONOUS TRANSMISSION REQUIREMENTS

| Param<br>No. | Symbol   | Characte                                        | ristic               | Min | Тур† | Max | Units | Conditions |

|--------------|----------|-------------------------------------------------|----------------------|-----|------|-----|-------|------------|

| 120          | TckH2dtV | <u>SYNC XMIT (MASTER &amp;</u><br><u>SLAVE)</u> | Standard( <b>F</b> ) |     | _    | 80  | ns    |            |

|              |          | Clock high to data out valid                    | Extended(LF)         | _   | —    | 100 | ns    |            |

| 121          | Tckrf    | Clock out rise time and fall                    | Standard(F)          | _   | —    | 45  | ns    |            |

|              |          | time (Master mode)                              | Extended(LF)         | —   | —    | 50  | ns    |            |

| 122          | Tdtrf    | Data out rise time and fall                     | Standard(F)          | _   | —    | 45  | ns    |            |

|              |          | time                                            | Extended(LF)         |     | —    | 50  | ns    |            |

† Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

## TABLE 15-11: USART SYNCHRONOUS RECEIVE REQUIREMENTS

| Parameter<br>No. | Symbol   | Characteristic                                                                | Min | Тур† | Max | Units | Conditions |

|------------------|----------|-------------------------------------------------------------------------------|-----|------|-----|-------|------------|

| 125              |          | <u>SYNC RCV (MASTER &amp; SLAVE)</u><br>Data setup before CK↓ (DT setup time) | 15  |      |     | ns    |            |

| 126              | TckL2dtl | Data hold after CK↓ (DT hold time)                                            | 15  |      |     | ns    |            |

† Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

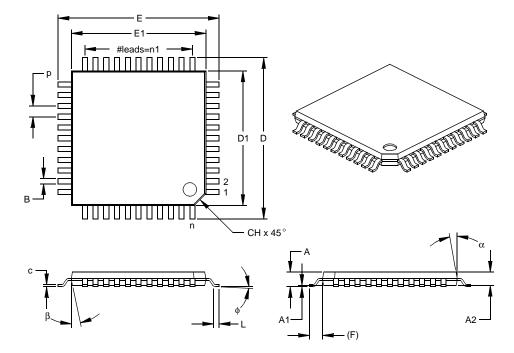

44-Lead Plastic Thin Quad Flatpack (PT) 10x10x1 mm Body, 1.0/0.10 mm Lead Form (TQFP)

|                          | Units    | INCHES |      |      | MILLIMETERS* |       |       |

|--------------------------|----------|--------|------|------|--------------|-------|-------|

| Dimensior                | n Limits | MIN    | NOM  | MAX  | MIN          | NOM   | MAX   |

| Number of Pins           | n        |        | 44   |      |              | 44    |       |

| Pitch                    | р        |        | .031 |      |              | 0.80  |       |

| Pins per Side            | n1       |        | 11   |      |              | 11    |       |

| Overall Height           | А        | .039   | .043 | .047 | 1.00         | 1.10  | 1.20  |

| Molded Package Thickness | A2       | .037   | .039 | .041 | 0.95         | 1.00  | 1.05  |

| Standoff §               | A1       | .002   | .004 | .006 | 0.05         | 0.10  | 0.15  |

| Foot Length              | L        | .018   | .024 | .030 | 0.45         | 0.60  | 0.75  |

| Footprint (Reference)    | (F)      |        | .039 |      | 1.00         |       |       |

| Foot Angle               | φ        | 0      | 3.5  | 7    | 0            | 3.5   | 7     |

| Overall Width            | Е        | .463   | .472 | .482 | 11.75        | 12.00 | 12.25 |

| Overall Length           | D        | .463   | .472 | .482 | 11.75        | 12.00 | 12.25 |

| Molded Package Width     | E1       | .390   | .394 | .398 | 9.90         | 10.00 | 10.10 |

| Molded Package Length    | D1       | .390   | .394 | .398 | 9.90         | 10.00 | 10.10 |

| Lead Thickness           | С        | .004   | .006 | .008 | 0.09         | 0.15  | 0.20  |

| Lead Width               | В        | .012   | .015 | .017 | 0.30         | 0.38  | 0.44  |

| Pin 1 Corner Chamfer     | СН       | .025   | .035 | .045 | 0.64         | 0.89  | 1.14  |

| Mold Draft Angle Top     | α        | 5      | 10   | 15   | 5            | 10    | 15    |

| Mold Draft Angle Bottom  | β        | 5      | 10   | 15   | 5            | 10    | 15    |

\* Controlling Parameter § Significant Characteristic

Notes:

Dimensions D1 and E1 do not include mold flash or protrusions. Mold flash or protrusions shall not exceed .010" (0.254mm) per side. JEDEC Equivalent: MS-026 Drawing No. C04-076

# **ON-LINE SUPPORT**

Microchip provides on-line support on the Microchip World Wide Web (WWW) site.

The web site is used by Microchip as a means to make files and information easily available to customers. To view the site, the user must have access to the Internet and a web browser, such as Netscape or Microsoft Explorer. Files are also available for FTP download from our FTP site.

#### Connecting to the Microchip Internet Web Site

The Microchip web site is available by using your favorite Internet browser to attach to:

#### www.microchip.com

The file transfer site is available by using an FTP service to connect to:

#### ftp://ftp.microchip.com

The web site and file transfer site provide a variety of services. Users may download files for the latest Development Tools, Data Sheets, Application Notes, User's Guides, Articles and Sample Programs. A variety of Microchip specific business information is also available, including listings of Microchip sales offices, distributors and factory representatives. Other data available for consideration is:

- Latest Microchip Press Releases

- Technical Support Section with Frequently Asked

Questions

- Design Tips

- Device Errata

- Job Postings

- Microchip Consultant Program Member Listing

- Links to other useful web sites related to Microchip Products

- Conferences for products, Development Systems, technical information and more

- · Listing of seminars and events

#### Systems Information and Upgrade Hot Line

The Systems Information and Upgrade Line provides system users a listing of the latest versions of all of Microchip's development systems software products. Plus, this line provides information on how customers can receive any currently available upgrade kits.The Hot Line Numbers are:

1-800-755-2345 for U.S. and most of Canada, and

1-480-792-7302 for the rest of the world.

013001

# **READER RESPONSE**

It is our intention to provide you with the best documentation possible to ensure successful use of your Microchip product. If you wish to provide your comments on organization, clarity, subject matter, and ways in which our documentation can better serve you, please FAX your comments to the Technical Publications Manager at (480) 792-4150.

Please list the following information, and use this outline to provide us with your comments about this Data Sheet.

| To:                                             | Technical Publications Manager Tota                                                      | I Pages Sent           |  |  |  |  |  |  |

|-------------------------------------------------|------------------------------------------------------------------------------------------|------------------------|--|--|--|--|--|--|

| RE:                                             | Reader Response                                                                          |                        |  |  |  |  |  |  |

| From                                            | m: Name                                                                                  |                        |  |  |  |  |  |  |

|                                                 | Company                                                                                  |                        |  |  |  |  |  |  |

|                                                 | Address                                                                                  |                        |  |  |  |  |  |  |

|                                                 | City / State / ZIP / Country                                                             |                        |  |  |  |  |  |  |

| <b>.</b>                                        | Telephone:                                                                               | )                      |  |  |  |  |  |  |

| Application (optional):                         |                                                                                          |                        |  |  |  |  |  |  |

| Would                                           | uld you like a reply?YN                                                                  |                        |  |  |  |  |  |  |

| Device: PIC16F7X Literature Number: DS30325B    |                                                                                          |                        |  |  |  |  |  |  |

| Ques                                            | estions:                                                                                 |                        |  |  |  |  |  |  |

| 1. What are the best features of this document? |                                                                                          |                        |  |  |  |  |  |  |

|                                                 |                                                                                          |                        |  |  |  |  |  |  |

| _                                               |                                                                                          |                        |  |  |  |  |  |  |

| 2. H                                            | How does this document meet your hardware and software developm                          | ent needs?             |  |  |  |  |  |  |

| _                                               |                                                                                          |                        |  |  |  |  |  |  |

| 3. D                                            | 3. Do you find the organization of this data sheet easy to follow? If not, why?          |                        |  |  |  |  |  |  |

| _                                               |                                                                                          |                        |  |  |  |  |  |  |

| 4. W                                            | . What additions to the data sheet do you think would enhance the structure and subject? |                        |  |  |  |  |  |  |

| _                                               |                                                                                          |                        |  |  |  |  |  |  |

| 5. W                                            | What deletions from the data sheet could be made without affecting the                   | ne overall usefulness? |  |  |  |  |  |  |

| _                                               |                                                                                          |                        |  |  |  |  |  |  |

| 6. Is                                           | . Is there any incorrect or misleading information (what and where)?                     |                        |  |  |  |  |  |  |

| _                                               |                                                                                          |                        |  |  |  |  |  |  |