Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Obsolete                                                                 |

|----------------------------|--------------------------------------------------------------------------|

| Core Processor             | PIC                                                                      |

| Core Size                  | 8-Bit                                                                    |

| Speed                      | 20MHz                                                                    |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                                        |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                    |

| Number of I/O              | 33                                                                       |

| Program Memory Size        | 7KB (4K x 14)                                                            |

| Program Memory Type        | FLASH                                                                    |

| EEPROM Size                | -                                                                        |

| RAM Size                   | 192 x 8                                                                  |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 5.5V                                                                |

| Data Converters            | A/D 8x8b                                                                 |

| Oscillator Type            | External                                                                 |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                        |

| Mounting Type              | Surface Mount                                                            |

| Package / Case             | 44-VQFN Exposed Pad                                                      |

| Supplier Device Package    | 44-QFN (8x8)                                                             |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16lf74-i-ml |

|                            |                                                                          |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

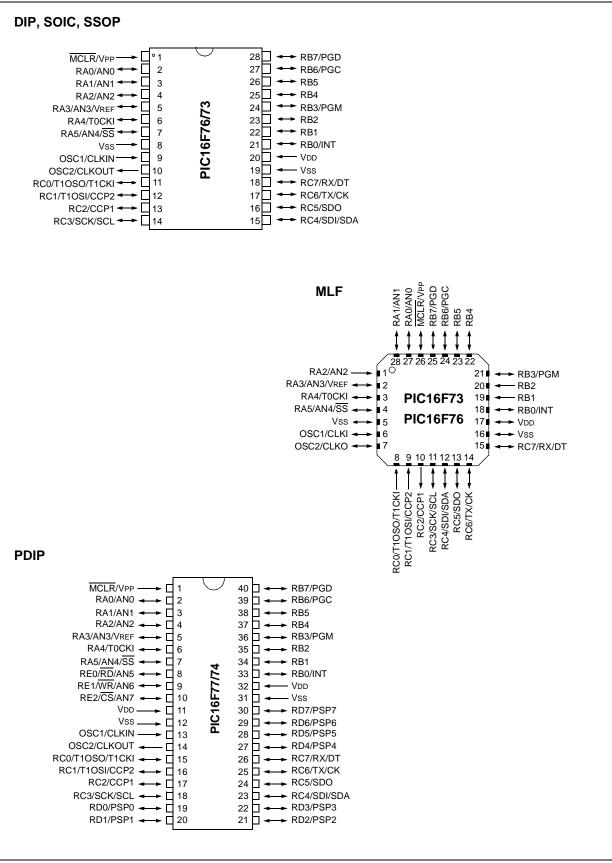

## **Pin Diagrams**

#### 3.0 **READING PROGRAM MEMORY**

The FLASH Program Memory is readable during normal operation over the entire VDD range. It is indirectly addressed through Special Function Registers (SFR). Up to 14-bit numbers can be stored in memory for use as calibration parameters, serial numbers, packed 7-bit ASCII, etc. Executing a program memory location containing data that forms an invalid instruction results in a NOP.

There are five SFRs used to read the program and memory. These registers are:

- PMCON1

- PMDATA

- PMDATH

- PMADR

- PMADRH

The program memory allows word reads. Program memory access allows for checksum calculation and reading calibration tables.

When interfacing to the program memory block, the PMDATH:PMDATA registers form a two-byte word, which holds the 14-bit data for reads. The PMADRH:PMADR registers form a two-byte word, which holds the 13-bit address of the FLASH location being accessed. These devices can have up to 8K words of program FLASH, with an address range from Oh to 3FFFh. The unused upper bits in both the PMDATH and PMADRH registers are not implemented and read as "0's".

#### 3.1 **PMADR**

The address registers can address up to a maximum of 8K words of program FLASH.

When selecting a program address value, the MSByte of the address is written to the PMADRH register and the LSByte is written to the PMADR register. The upper MSbits of PMADRH must always be clear.

#### 3.2 PMCON1 Register

PMCON1 is the control register for memory accesses.

The control bit RD initiates read operations. This bit cannot be cleared, only set, in software. It is cleared in hardware at the completion of the read operation.

#### **REGISTER 3-1:** PMCON1 REGISTER (ADDRESS 18Ch)

|         | R-1                       | U-0         | U-0          | U-0           | U-x        | U-0          | U-0            | R/S-0       |

|---------|---------------------------|-------------|--------------|---------------|------------|--------------|----------------|-------------|

|         | reserved                  | _           | —            | _             | _          | —            | —              | RD          |

|         | bit 7                     |             |              |               |            |              |                | bit 0       |

|         |                           |             |              |               |            |              |                |             |

| bit 7   | Reserved:                 | Read as '1  | ,            |               |            |              |                |             |

| bit 6-1 | Unimplem                  | ented: Rea  | d as '0'     |               |            |              |                |             |

| bit 0   | RD: Read                  | Control bit |              |               |            |              |                |             |

|         | 1 = Initiates<br>in softw |             | ead, RD is c | leared in har | dware. The | RD bit can c | only be set (n | ot cleared) |

|         | 0 = FLASH                 | l read comp | leted        |               |            |              |                |             |

|         | _                         |             |              |               |            |              |                |             |

|         | Legend:                   |             |              |               |            |              |                |             |

| Legend:                  |                  |                      |                    |

|--------------------------|------------------|----------------------|--------------------|

| R = Readable bit         | W = Writable bit | U = Unimplemented    | bit, read as '0'   |

| - n = Value at POR reset | '1' = Bit is set | '0' = Bit is cleared | x = Bit is unknown |

## 3.3 Reading the FLASH Program Memory

A program memory location may be read by writing two bytes of the address to the PMADR and PMADRH registers and then setting control bit RD (PMCON1<0>). Once the read control bit is set, the microcontroller will use the next two instruction cycles to read the data. The data is available in the PMDATA and PMDATH registers after the second NOP instruction. Therefore, it can be read as two bytes in the following instructions. The PMDATA and PMDATH registers will hold this value until the next read operation.

# 3.4 Operation During Code Protect

FLASH program memory has its own code protect mechanism. External Read and Write operations by programmers are disabled if this mechanism is enabled.

The microcontroller can read and execute instructions out of the internal FLASH program memory, regardless of the state of the code protect configuration bits.

|                      | BSF               | STATUS, RP1 | ;                                                                                          |

|----------------------|-------------------|-------------|--------------------------------------------------------------------------------------------|

|                      | BCF               | STATUS, RP0 | ; Bank 2                                                                                   |

|                      | MOVF              | ADDRH, W    | ;                                                                                          |

|                      | MOVWF             | PMADRH      | ; MSByte of Program Address to read                                                        |

|                      | MOVF              | ADDRL, W    | ;                                                                                          |

|                      | MOVWF             | PMADR       | ; LSByte of Program Address to read                                                        |

|                      | BSF               | STATUS, RP0 | ; Bank 3 Required                                                                          |

| Required<br>Sequence | BSF<br>NOP<br>NOP | PMCON1, RD  | ; EEPROM Read Sequence<br>; memory is read in the next two cycles after BSF PMCON1,RD<br>; |

|                      | BCF               | STATUS, RPO | ; Bank 2                                                                                   |

|                      | MOVF              | PMDATA, W   | ; W = LSByte of Program PMDATA                                                             |

|                      | MOVF              | PMDATH, W   | ; W = MSByte of Program PMDATA                                                             |

#### EXAMPLE 3-1: FLASH PROGRAM READ

## TABLE 3-1: REGISTERS ASSOCIATED WITH PROGRAM FLASH

| Address | Name   | Bit 7     | Bit 6       | Bit 5    | Bit 4      | Bit 3      | Bit 2     | Bit 1     | Bit 0 | Value on:<br>POR,<br>BOR | Value on<br>all other<br>RESETS |

|---------|--------|-----------|-------------|----------|------------|------------|-----------|-----------|-------|--------------------------|---------------------------------|

| 10Dh    | PMADR  | Address F | Register Lo | ow Byte  |            |            |           |           |       | xxxx xxxx                | uuuu uuuu                       |

| 10Fh    | PMADRH | _         | —           | _        | Address I  | Register H | igh Byte  |           |       | xxxx xxxx                | uuuu uuuu                       |

| 10Ch    | PMDATA | Data Reg  | ister Low I | Byte     |            |            |           |           |       | xxxx xxxx                | uuuu uuuu                       |

| 10Eh    | PMDATH | _         | _           | Data Reg | ister High | Byte       | xxxx xxxx | uuuu uuuu |       |                          |                                 |

| 18Ch    | PMCON1 | _(1)      | —           | _        | _          | —          | _         | —         | RD    | 10                       | 10                              |

Legend: x = unknown, u = unchanged, r = reserved, - = unimplemented read as '0'. Shaded cells are not used during FLASH access. **Note 1:** This bit always reads as a '1'.

# 4.0 I/O PORTS

Some pins for these I/O ports are multiplexed with an alternate function for the peripheral features on the device. In general, when a peripheral is enabled, that pin may not be used as a general purpose I/O pin.

Additional information on I/O ports may be found in the PICmicro<sup>™</sup> Mid-Range Reference Manual, (DS33023).

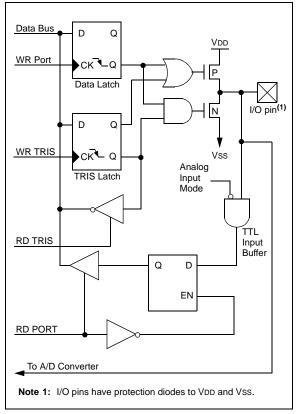

# 4.1 PORTA and the TRISA Register

PORTA is a 6-bit wide, bi-directional port. The corresponding data direction register is TRISA. Setting a TRISA bit (= '1') will make the corresponding PORTA pin an input (i.e., put the corresponding output driver in a Hi-Impedance mode). Clearing a TRISA bit (= '0') will make the corresponding PORTA pin an output (i.e., put the contents of the output latch on the selected pin).

Reading the PORTA register reads the status of the pins, whereas writing to it will write to the port latch. All write operations are read-modify-write operations. Therefore, a write to a port implies that the port pins are read, the value is modified and then written to the port data latch.

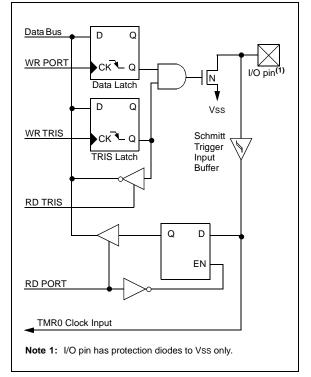

Pin RA4 is multiplexed with the Timer0 module clock input to become the RA4/T0CKI pin. The RA4/T0CKI pin is a Schmitt Trigger input and an open drain output. All other PORTA pins have TTL input levels and full CMOS output drivers.

Other PORTA pins are multiplexed with analog inputs and analog VREF input. The operation of each pin is selected by clearing/setting the control bits in the ADCON1 register (A/D Control Register1).

**Note:** On a Power-on Reset, these pins are configured as analog inputs and read as '0'.

The TRISA register controls the direction of the RA pins, even when they are being used as analog inputs. The user must ensure the bits in the TRISA register are maintained set, when using them as analog inputs.

| BCF<br>BCF<br>CLRF                      | STATUS,<br>STATUS,<br>PORTA                |     | ;<br>; Bank0<br>; Initialize PORTA by<br>; clearing output<br>: data latches | Y |

|-----------------------------------------|--------------------------------------------|-----|------------------------------------------------------------------------------|---|

| BSF<br>MOVLW<br>MOVWF<br>MOVLW<br>MOVWF | STATUS,<br>0x06<br>ADCON1<br>0xCF<br>TRISA | RPO | ,                                                                            |   |

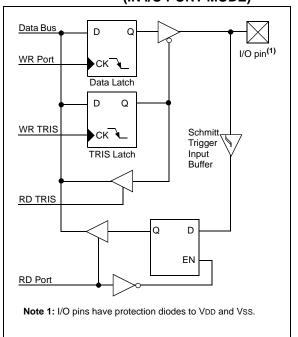

## FIGURE 4-1:

#### BLOCK DIAGRAM OF RA3:RA0 AND RA5 PINS

FIGURE 4-2:

#### BLOCK DIAGRAM OF RA4/T0CKI PIN

## 4.5 PORTE and TRISE Register

This section is not applicable to the PIC16F73 or PIC16F76.

PORTE has three pins, RE0/RD/AN5, RE1/WR/AN6 and RE2/CS/AN7, which are individually configureable as inputs or outputs. These pins have Schmitt Trigger input buffers.

I/O PORTE becomes control inputs for the microprocessor port when bit PSPMODE (TRISE<4>) is set. In this mode, the user must make sure that the TRISE<2:0> bits are set (pins are configured as digital inputs). Ensure ADCON1 is configured for digital I/O. In this mode, the input buffers are TTL.

Register 4-1 shows the TRISE register, which also controls the parallel slave port operation.

PORTE pins are multiplexed with analog inputs. When selected as an analog input, these pins will read as '0's.

TRISE controls the direction of the RE pins, even when they are being used as analog inputs. The user must make sure to keep the pins configured as inputs when using them as analog inputs.

**Note:** On a Power-on Reset, these pins are configured as analog inputs and read as '0'.

#### FIGURE 4-7: PORTE BLOCK DIAGRAM (IN I/O PORT MODE)

| REGISTER 7-1: | T2CON: TIMER2 CONTROL REGISTER (ADDRESS 12h) |                              |             |               |               |             |                |          |  |  |  |  |

|---------------|----------------------------------------------|------------------------------|-------------|---------------|---------------|-------------|----------------|----------|--|--|--|--|

|               | U-0                                          | R/W-0                        | R/W-0       | R/W-0         | R/W-0         | R/W-0       | R/W-0          | R/W-0    |  |  |  |  |

|               | _                                            | TOUTPS3                      | TOUTPS2     | TOUTPS1       | TOUTPS0       | TMR2ON      | T2CKPS1        | T2CKPS0  |  |  |  |  |

|               | bit 7                                        |                              |             |               |               |             |                | bit 0    |  |  |  |  |

| bit 7         | Unimplo                                      | mented: Rea                  | nd as '0'   |               |               |             |                |          |  |  |  |  |

|               | -                                            |                              |             |               | 0.1           |             |                |          |  |  |  |  |

| bit 6-3       |                                              |                              | Timer2 Out  | put Postscale | e Select Dits |             |                |          |  |  |  |  |

|               |                                              | :1 Postscale<br>:2 Postscale |             |               |               |             |                |          |  |  |  |  |

|               |                                              | :3 Postscale                 |             |               |               |             |                |          |  |  |  |  |

|               | •                                            | .01000000                    |             |               |               |             |                |          |  |  |  |  |

|               | •                                            |                              |             |               |               |             |                |          |  |  |  |  |

|               | •                                            |                              |             |               |               |             |                |          |  |  |  |  |

|               | 1111 <b>= 1</b>                              | :16 Postscale                | Э           |               |               |             |                |          |  |  |  |  |

| bit 2         | TMR2ON                                       | I: Timer2 On                 | bit         |               |               |             |                |          |  |  |  |  |

|               | 1 = Timei                                    |                              |             |               |               |             |                |          |  |  |  |  |

|               | 0 = Timei                                    |                              |             |               |               |             |                |          |  |  |  |  |

| bit 1-0       | T2CKPS                                       | 1:T2CKPS0:                   | Timer2 Cloc | k Prescale S  | elect bits    |             |                |          |  |  |  |  |

|               |                                              | scaler is 1                  |             |               |               |             |                |          |  |  |  |  |

|               |                                              | scaler is 4                  |             |               |               |             |                |          |  |  |  |  |

|               | 1x = Pres                                    | scaler is 16                 |             |               |               |             |                |          |  |  |  |  |

|               | Legend:                                      |                              |             |               |               |             |                |          |  |  |  |  |

|               | R = Reada                                    | ahle hit                     | M - M       | /ritable bit  | II – Unim     | olemented I | oit, read as ' | 0'       |  |  |  |  |

|               | 1. – 1.caua                                  |                              | vv — v      |               | 0 - 01111     | siomonicui  | 51, 1000 05    | <b>°</b> |  |  |  |  |

# TABLE 7-1: REGISTERS ASSOCIATED WITH TIMER2 AS A TIMER/COUNTER

- n = Value at POR reset

| Address                | Name   | Bit 7                | Bit 6        | Bit 5   | Bit 4   | Bit 3   | Bit 2  | Bit 1   | Bit 0   | Value<br>PC<br>BC | R,   |      | e on<br>other<br>iETS |

|------------------------|--------|----------------------|--------------|---------|---------|---------|--------|---------|---------|-------------------|------|------|-----------------------|

| 0Bh,8Bh,<br>10Bh, 18Bh | INTCON | GIE                  | PEIE         | TMR0IE  | INTE    | RBIE    | TMR0IF | INTF    | RBIF    | 0000              | 000x | 0000 | 000u                  |

| 0Ch                    | PIR1   | PSPIF <sup>(1)</sup> | ADIF         | RCIF    | TXIF    | SSPIF   | CCP1IF | TMR2IF  | TMR1IF  | 0000              | 0000 | 0000 | 0000                  |

| 8Ch                    | PIE1   | PSPIE <sup>(1)</sup> | ADIE         | RCIE    | TXIE    | SSPIE   | CCP1IE | TMR2IE  | TMR1IE  | 0000              | 0000 | 0000 | 0000                  |

| 11h                    | TMR2   | Timer2 M             | odule Regis  | ster    |         |         |        |         |         | 0000              | 0000 | 0000 | 0000                  |

| 12h                    | T2CON  |                      | TOUTPS3      | TOUTPS2 | TOUTPS1 | TOUTPS0 | TMR2ON | T2CKPS1 | T2CKPS0 | -000              | 0000 | -000 | 0000                  |

| 92h                    | PR2    | Timer2 Pe            | eriod Regist | ter     |         |         |        |         |         | 1111              | 1111 | 1111 | 1111                  |

'1' = Bit is set

'0' = Bit is cleared

Legend: x = unknown, u = unchanged, - = unimplemented, read as '0'. Shaded cells are not used by the Timer2 module.

Note 1: Bits PSPIE and PSPIF are reserved on the PIC16F73/76; always maintain these bits clear.

x = Bit is unknown

# 8.0 CAPTURE/COMPARE/PWM MODULES

Each Capture/Compare/PWM (CCP) module contains a 16-bit register which can operate as a:

- 16-bit Capture register

- 16-bit Compare register

- PWM Master/Slave Duty Cycle register

Both the CCP1 and CCP2 modules are identical in operation, with the exception being the operation of the special event trigger. Table 8-1 and Table 8-2 show the resources and interactions of the CCP module(s). In the following sections, the operation of a CCP module is described with respect to CCP1. CCP2 operates the same as CCP1, except where noted.

## 8.1 CCP1 Module

Capture/Compare/PWM Register1 (CCPR1) is comprised of two 8-bit registers: CCPR1L (low byte) and CCPR1H (high byte). The CCP1CON register controls the operation of CCP1. The special event trigger is generated by a compare match and will clear both TMR1H and TMR1L registers.

# 8.2 CCP2 Module

Capture/Compare/PWM Register1 (CCPR1) is comprised of two 8-bit registers: CCPR1L (low byte) and CCPR1H (high byte). The CCP2CON register controls the operation of CCP2. The special event trigger is generated by a compare match; it will clear both TMR1H and TMR1L registers, and start an A/D conversion (if the A/D module is enabled).

Additional information on CCP modules is available in the PICmicro<sup>™</sup> Mid-Range MCU Family Reference Manual (DS33023) and in Application Note AN594, "Using the CCP Modules" (DS00594).

#### TABLE 8-1: CCP MODE - TIMER RESOURCES REQUIRED

| CCP Mode | Timer Resource |

|----------|----------------|

| Capture  | Timer1         |

| Compare  | Timer1         |

| PWM      | Timer2         |

## TABLE 8-2:INTERACTION OF TWO CCP MODULES

| CCPx Mode | CCPy Mode | Interaction                                                                                           |

|-----------|-----------|-------------------------------------------------------------------------------------------------------|

| Capture   | Capture   | Same TMR1 time-base.                                                                                  |

| Capture   | Compare   | Same TMR1 time-base.                                                                                  |

| Compare   | Compare   | Same TMR1 time-base.                                                                                  |

| PWM       | PWM       | The PWMs will have the same frequency and update rate (TMR2 interrupt). The rising edges are aligned. |

| PWM       | Capture   | None.                                                                                                 |

| PWM       | Compare   | None.                                                                                                 |

# 9.0 SYNCHRONOUS SERIAL PORT (SSP) MODULE

## 9.1 SSP Module Overview

The Synchronous Serial Port (SSP) module is a serial interface useful for communicating with other peripheral or microcontroller devices. These peripheral devices may be Serial EEPROMs, shift registers, display drivers, A/D converters, etc. The SSP module can operate in one of two modes:

- Serial Peripheral Interface (SPI)

- Inter-Integrated Circuit (I<sup>2</sup>C)

An overview of I<sup>2</sup>C operations and additional information on the SSP module can be found in the PICmicro<sup>™</sup> Mid-Range MCU Family Reference Manual (DS33023).

Refer to Application Note AN578, "Use of the SSP Module in the I<sup>2</sup>C Multi-Master Environment" (DS00578).

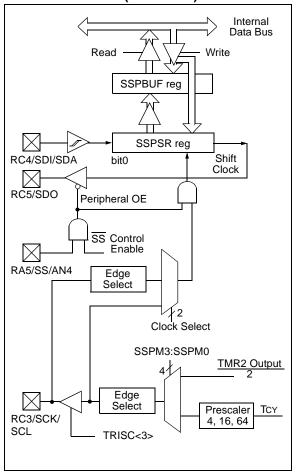

## 9.2 SPI Mode

This section contains register definitions and operational characteristics of the SPI module. Additional information on the SPI module can be found in the PICmicro<sup>™</sup> Mid-Range MCU Family Reference Manual (DS33023A).

SPI mode allows 8 bits of data to be synchronously transmitted and received simultaneously. To accomplish communication, typically three pins are used:

- Serial Data Out (SDO) RC5/SDO

- Serial Data In (SDI) RC4/SDI/SDA

- Serial Clock (SCK) RC3/SCK/SCL

Additionally, a fourth pin may be used when in a Slave mode of operation:

Slave Select (SS) RA5/SS/AN4

When initializing the SPI, several options need to be specified. This is done by programming the appropriate control bits in the SSPCON register (SSPCON<5:0>) and SSPSTAT<7:6>. These control bits allow the following to be specified:

- Master mode (SCK is the clock output)

- Slave mode (SCK is the clock input)

- Clock Polarity (IDLE state of SCK)

- Clock edge (output data on rising/falling edge of SCK)

- Clock Rate (Master mode only)

- Slave Select mode (Slave mode only)

|           | R/W-0                                                                                                                                                                                                     | R/W-0                                                                                                                                                                                                                                                                                                                                                                                                                                                          | R/W-0          | R/W-0                                              | R/W-0        | R/W-0                                 | R/W-0         | R/W-0  |  |  |  |  |  |

|-----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------|----------------------------------------------------|--------------|---------------------------------------|---------------|--------|--|--|--|--|--|

|           | WCOL                                                                                                                                                                                                      | SSPOV                                                                                                                                                                                                                                                                                                                                                                                                                                                          | SSPEN          | CKP                                                | SSPM3        | SSPM2                                 | SSPM1         | SSPM0  |  |  |  |  |  |

|           | bit 7                                                                                                                                                                                                     | 331 0 1                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                | UN                                                 | 30F 1013     |                                       | 301 101       | bit 0  |  |  |  |  |  |

| 1 : 1 - 7 |                                                                                                                                                                                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                |                                                    |              |                                       |               |        |  |  |  |  |  |

| bit 7     | <ul> <li>WCOL: Write Collision Detect bit</li> <li>1 = The SSPBUF register is written while it is still transmitting the previous word (must be cleared in software)</li> <li>0 = No collision</li> </ul> |                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                |                                                    |              |                                       |               |        |  |  |  |  |  |

| bit 6     | SSPOV: F                                                                                                                                                                                                  | Receive Ove                                                                                                                                                                                                                                                                                                                                                                                                                                                    | rflow Indicate | or bit                                             |              |                                       |               |        |  |  |  |  |  |

|           | In SPI mo                                                                                                                                                                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                |                                                    |              |                                       |               |        |  |  |  |  |  |

|           | of ove<br>must<br>Maste<br>initiate<br>0 = No ov                                                                                                                                                          | <ul> <li>1 = A new byte is received while the SSPBUF register is still holding the previous data. In case of overflow, the data in SSPSR is lost. Overflow can only occur in Slave mode. The user must read the SSPBUF, even if only transmitting data, to avoid setting overflow. In Master mode, the overflow bit is not set since each new reception (and transmission) is initiated by writing to the SSPBUF register.</li> <li>0 = No overflow</li> </ul> |                |                                                    |              |                                       |               |        |  |  |  |  |  |

|           | 1 = A byte<br>is a "c                                                                                                                                                                                     | <ul> <li>In I<sup>2</sup>C mode:</li> <li>1 = A byte is received while the SSPBUF register is still holding the previous byte. SSPOV is a "don't care" in Transmit mode. SSPOV must be cleared in software in either mode.</li> <li>0 = No overflow</li> </ul>                                                                                                                                                                                                 |                |                                                    |              |                                       |               |        |  |  |  |  |  |

| bit 5     | <b>SSPEN</b> : S                                                                                                                                                                                          | Svnchronous                                                                                                                                                                                                                                                                                                                                                                                                                                                    | Serial Port I  | Enable bit                                         |              |                                       |               |        |  |  |  |  |  |

|           | In SPI mode:<br>1 = Enables serial port and configures SCK, SDO, and SDI as serial port pins<br>0 = Disables serial port and configures these pins as I/O port pins<br>In $I^2C$ mode:                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                |                                                    |              |                                       |               |        |  |  |  |  |  |

|           | <ul> <li>1 = Enables the serial port and configures the SDA and SCL pins as serial port pins</li> <li>0 = Disables serial port and configures these pins as I/O port pins</li> </ul>                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                |                                                    |              |                                       |               |        |  |  |  |  |  |

|           | In both mo                                                                                                                                                                                                | odes, when a                                                                                                                                                                                                                                                                                                                                                                                                                                                   | enabled, the   | se pins must b                                     | e properly o | configured a                          | as input or o | utput. |  |  |  |  |  |

| bit 4     | CKP: Clor                                                                                                                                                                                                 | ck Polarity S                                                                                                                                                                                                                                                                                                                                                                                                                                                  | elect bit      |                                                    |              |                                       |               |        |  |  |  |  |  |

|           | In SPI mode:<br>1 = IDLE state for clock is a high level (Microwire <sup>®</sup> default)<br>0 = IDLE state for clock is a low level (Microwire <sup>®</sup> alternate)                                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                |                                                    |              |                                       |               |        |  |  |  |  |  |

|           | In I <sup>2</sup> C mode:<br>SCK release control<br>1 = Enable clock                                                                                                                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                |                                                    |              |                                       |               |        |  |  |  |  |  |

|           |                                                                                                                                                                                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                | lock stretch)  | . (Used to ens                                     | ure data se  | tup time.)                            |               |        |  |  |  |  |  |

| bit 3-0   |                                                                                                                                                                                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                | -              | rial Port Mode                                     |              | , , , , , , , , , , , , , , , , , , , |               |        |  |  |  |  |  |

|           | 0000 = SPI Master mode, clock = Fosc/4<br>0001 = SPI Master mode, clock = Fosc/16<br>0010 = SPI Master mode, clock = Fosc/64<br>0011 = SPI Master mode, clock = TMR2 output/2                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                |                                                    |              |                                       |               |        |  |  |  |  |  |

|           | 0101 = SF<br>$0110 = I^{2}(0111 = I^{2})$                                                                                                                                                                 | 0100 = SPI Slave mode, clock = SCK pin. $\overline{SS}$ pin control enabled.<br>0101 = SPI Slave mode, clock = SCK pin. $\overline{SS}$ pin control disabled. $\overline{SS}$ can be used as I/O pin.<br>0110 = I <sup>2</sup> C Slave mode, 7-bit address<br>0111 = I <sup>2</sup> C Slave mode, 10-bit address                                                                                                                                               |                |                                                    |              |                                       |               |        |  |  |  |  |  |

|           | $1110 = I^{2}$                                                                                                                                                                                            | C Slave mod                                                                                                                                                                                                                                                                                                                                                                                                                                                    | de, 7-bit addr | laster mode (s<br>ress with STAF<br>dress with STA | RT and STC   |                                       |               |        |  |  |  |  |  |

|           | Legend:                                                                                                                                                                                                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                |                                                    |              |                                       |               |        |  |  |  |  |  |

|           | R = Reada                                                                                                                                                                                                 | able bit                                                                                                                                                                                                                                                                                                                                                                                                                                                       | VV = V         | Nritable bit                                       | U = Unim     | plemented                             | bit, read as  | '0'    |  |  |  |  |  |

| Legend:                  |                  |                      |                    |

|--------------------------|------------------|----------------------|--------------------|

| R = Readable bit         | W = Writable bit | U = Unimplemented    | bit, read as '0'   |

| - n = Value at POR reset | '1' = Bit is set | '0' = Bit is cleared | x = Bit is unknown |

#### FIGURE 9-1: SSP BLOCK DIAGRAM (SPI MODE)

To enable the serial port, SSP enable bit, SSPEN (SSPCON<5>) must be set. To reset or reconfigure SPI mode, clear bit SSPEN, re-initialize the SSPCON register, and then set bit SSPEN. This configures the SDI, SDO, SCK, and SS pins as serial port pins. For the pins to behave as the serial port function, they must have their data direction bits (in the TRISC register) appropriately programmed. That is:

- SDI must have TRISC<4> set

- SDO must have TRISC<5> cleared

- SCK (Master mode) must have TRISC<3> cleared

- SCK (Slave mode) must have TRISC<3> set

- SS must have TRISA<5> set and ADCON must be configured such that RA5 is a digital I/O

Note 1: When the SPI is in Slave mode with SS pin control enabled (SSPCON<3:0> = 0100), the SPI module will reset if the SS pin is set to VDD.

- 2: If the SPI is used in Slave mode with CKE = '1', then the SS pin control must be enabled.

- 3: When the SPI is in Slave mode with  $\overline{SS}$  pin control enabled (SSPCON<3:0> = '0100'), the state of the  $\overline{SS}$  pin can affect the state read back from the TRISC<5> bit. The Peripheral OE signal from the SSP module into PORTC controls the state that is read back from the TRISC<5> bit (see Section 4.3 for information on PORTC). If Read-Modify-Write instructions, such as BSF are performed on the TRISC register while the  $\overline{SS}$  pin is high, this will cause the TRISC<5> bit to be set, thus disabling the SDO output.

# 10.2 USART Asynchronous Mode

In this mode, the USART uses standard non-return-tozero (NRZ) format (one START bit, eight or nine data bits, and one STOP bit). The most common data format is 8-bits. An on-chip, dedicated, 8-bit baud rate generator can be used to derive standard baud rate frequencies from the oscillator. The USART transmits and receives the LSb first. The USART's transmitter and receiver are functionally independent, but use the same data format and baud rate. The baud rate generator produces a clock, either x16 or x64 of the bit shift rate, depending on bit BRGH (TXSTA<2>). Parity is not supported by the hardware, but can be implemented in software (and stored as the ninth data bit). Asynchronous mode is stopped during SLEEP.

Asynchronous mode is selected by clearing bit SYNC (TXSTA<4>).

The USART Asynchronous module consists of the following important elements:

- · Baud Rate Generator

- Sampling Circuit

- Asynchronous Transmitter

- Asynchronous Receiver

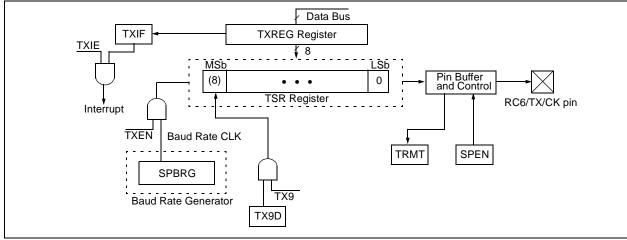

#### 10.2.1 USART ASYNCHRONOUS TRANSMITTER

The USART transmitter block diagram is shown in Figure 10-1. The heart of the transmitter is the transmit (serial) shift register (TSR). The shift register obtains its data from the read/write transmit buffer, TXREG. The TXREG register is loaded with data by firmware. The TSR register is not loaded until the STOP bit has been transmitted from the previous load. As soon as the STOP bit is transmitted, the TSR is loaded with new data from the TXREG register (if available). Once the TXREG register transfers the data to the TSR register, the TXREG register is empty. One instruction cycle later, flag bit TXIF (PIR1<4>) and flag bit TRMT (TXSTA<1>)

are set. The TXIF interrupt can be enabled/disabled by setting/clearing enable bit TXIE (PIE1<4>). Flag bit TXIF will be set, regardless of the state of enable bit TXIE and cannot be cleared in software. It will reset only when new data is loaded into the TXREG register. While flag bit TXIF indicates the status of the TXREG register, another bit TRMT (TXSTA<1>) shows the status of the TSR register. Status bit TRMT is a read only bit, which is set one instruction cycle after the TSR register becomes empty, and is cleared one instruction cycle after the TSR register is loaded. No interrupt logic is tied to this bit, so the user has to poll this bit in order to determine if the TSR register is empty.

| Note 1: | The TSR register is not mapped in data      |

|---------|---------------------------------------------|

|         | memory, so it is not available to the user. |

| 2:      | Flag bit TXIF is set when enable bit TXEN   |

is set. TXIF is cleared by loading TXREG.

Transmission is enabled by setting enable bit TXEN (TXSTA<5>). The actual transmission will not occur until the TXREG register has been loaded with data and the baud rate generator (BRG) has produced a shift clock (Figure 10-2). The transmission can also be started by first loading the TXREG register and then setting enable bit TXEN. Normally, when transmission is first started, the TSR register is empty. At that point, transfer to the TXREG register will result in an immediate transfer to TSR, resulting in an empty TXREG. A back-to-back transfer is thus possible (Figure 10-3). Clearing enable bit TXEN during a transmission will cause the transmission to be aborted and will reset the transmitter. As a result, the RC6/TX/CK pin will revert to hi-impedance.

In order to select 9-bit transmission, transmit bit TX9 (TXSTA<6>) should be set and the ninth bit should be written to TX9D (TXSTA<0>). The ninth bit must be written before writing the 8-bit data to the TXREG register. This is because a data write to the TXREG register can result in an immediate transfer of the data to the TSR register (if the TSR is empty). In such a case, an incorrect ninth data bit may be loaded in the TSR register.

## FIGURE 10-1: USART TRANSMIT BLOCK DIAGRAM

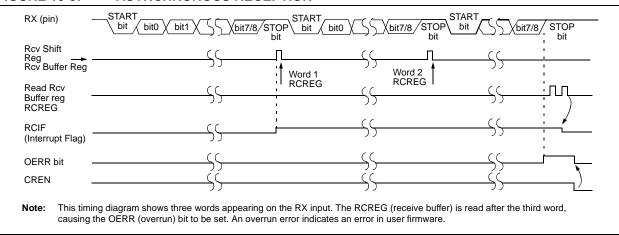

#### FIGURE 10-5: ASYNCHRONOUS RECEPTION

Steps to follow when setting up an Asynchronous Reception:

- 1. Initialize the SPBRG register for the appropriate baud rate. If a high speed baud rate is desired, set bit BRGH (Section 10.1).

- 2. Enable the asynchronous serial port by clearing bit SYNC and setting bit SPEN.

- 3. If interrupts are desired, then set enable bit RCIE.

- 4. If 9-bit reception is desired, then set bit RX9.

- 5. Enable the reception by setting bit CREN.

- 6. Flag bit RCIF will be set when reception is complete and an interrupt will be generated if enable bit RCIE is set.

- 7. Read the RCSTA register to get the ninth bit (if enabled) and determine if any error occurred during reception.

- 8. Read the 8-bit received data by reading the RCREG register.

- 9. If any error occurred, clear the error by clearing enable bit CREN.

- 10. If using interrupts, ensure that GIE and PEIE in the INTCON register are set.

| Address                | Name   | Bit 7                | Bit 6     | Bit 5       | Bit 4 | Bit 3 | Bit 2  | Bit 1  | Bit 0  | Value on:<br>POR,<br>BOR | Value on<br>all other<br>RESETS |

|------------------------|--------|----------------------|-----------|-------------|-------|-------|--------|--------|--------|--------------------------|---------------------------------|

| 0Bh, 8Bh,<br>10Bh,18Bh | INTCON | GIE                  | PEIE      | TMR0IE      | INTE  | RBIE  | TMR0IF | INTF   | RBIF   | 0000 000x                | 0000 000u                       |

| 0Ch                    | PIR1   | PSPIF <sup>(1)</sup> | ADIF      | RCIF        | TXIF  | SSPIF | CCP1IF | TMR2IF | TMR1IF | 0000 0000                | 0000 0000                       |

| 18h                    | RCSTA  | SPEN                 | RX9       | SREN        | CREN  |       | FERR   | OERR   | RX9D   | 0000 -00x                | 0000 -00x                       |

| 1Ah                    | RCREG  | USART R              | eceive Re | gister      |       |       |        |        |        | 0000 0000                | 0000 0000                       |

| 8Ch                    | PIE1   | PSPIE <sup>(1)</sup> | ADIE      | RCIE        | TXIE  | SSPIE | CCP1IE | TMR2IE | TMR1IE | 0000 0000                | 0000 0000                       |

| 98h                    | TXSTA  | CSRC                 | TX9       | TXEN        | SYNC  |       | BRGH   | TRMT   | TX9D   | 0000 -010                | 0000 -010                       |

| 99h                    | SPBRG  | Baud Rate            | Generato  | or Register |       |       |        |        |        | 0000 0000                | 0000 0000                       |

## TABLE 10-6: REGISTERS ASSOCIATED WITH ASYNCHRONOUS RECEPTION

Legend: x = unknown, - = unimplemented locations read as '0'. Shaded cells are not used for asynchronous reception. Note 1: Bits PSPIE and PSPIF are reserved on the PIC16F73/76 devices; always maintain these bits clear.

| Address                | Name   | Bit 7                | Bit 6     | Bit 5      | Bit 4 | Bit 3 | Bit 2  | Bit 1  | Bit 0  | Value on:<br>POR, BOR | Value on<br>all other<br>RESETS |

|------------------------|--------|----------------------|-----------|------------|-------|-------|--------|--------|--------|-----------------------|---------------------------------|

| 0Bh, 8Bh,<br>10Bh,18Bh | INTCON | GIE                  | PEIE      | TMR0IE     | INTE  | RBIE  | TMR0IF | INTF   | RBIF   | 0000 000x             | 0000 000u                       |

| 0Ch                    | PIR1   | PSPIF <sup>(1)</sup> | ADIF      | RCIF       | TXIF  | SSPIF | CCP1IF | TMR2IF | TMR1IF | 0000 0000             | 0000 0000                       |

| 18h                    | RCSTA  | SPEN                 | RX9       | SREN       | CREN  | _     | FERR   | OERR   | RX9D   | 0000 -00x             | 0000 -00x                       |

| 1Ah                    | RCREG  | USART Re             | eceive Re | gister     |       |       |        |        |        | 0000 0000             | 0000 0000                       |

| 8Ch                    | PIE1   | PSPIE <sup>(1)</sup> | ADIE      | RCIE       | TXIE  | SSPIE | CCP1IE | TMR2IE | TMR1IE | 0000 0000             | 0000 0000                       |

| 98h                    | TXSTA  | CSRC                 | TX9       | TXEN       | SYNC  | _     | BRGH   | TRMT   | TX9D   | 0000 -010             | 0000 -010                       |

| 99h                    | SPBRG  | Baud Rate            | Generat   | or Registe | r     |       | •      | •      |        | 0000 0000             | 0000 0000                       |

Legend: x = unknown, - = unimplemented, read as '0'. Shaded cells are not used for synchronous master reception. **Note** 1: Bits PSPIE and PSPIF are reserved on the PIC16F73/76 devices; always maintain these bits clear.

## 10.4 USART Synchronous Slave Mode

Synchronous Slave mode differs from the Master mode, in that the shift clock is supplied externally at the RC6/TX/CK pin (instead of being supplied internally in Master mode). This allows the device to transfer or receive data while in SLEEP mode. Slave mode is entered by clearing bit CSRC (TXSTA<7>).

#### 10.4.1 USART SYNCHRONOUS SLAVE TRANSMIT

The operation of the Synchronous Master and Slave modes are identical except in the case of the SLEEP mode.

If two words are written to the TXREG and then the SLEEP instruction is executed, the following will occur:

- a) The first word will immediately transfer to the TSR register and transmit when the master device drives the CK line.

- b) The second word will remain in TXREG register.

- c) Flag bit TXIF will not be set.

- d) When the first word has been shifted out of TSR, the TXREG register will transfer the second word to the TSR and flag bit TXIF will now be set.

- e) If enable bit TXIE is set, the interrupt will wake the chip from SLEEP and if the global interrupt is enabled, the program will branch to the interrupt vector (0004h).

Follow these steps when setting up a Synchronous Slave Transmission:

- 1. Enable the synchronous slave serial port by setting bits SYNC and SPEN and clearing bit CSRC.

- 2. Clear bits CREN and SREN.

- 3. If interrupts are desired, then set enable bit TXIE.

- 4. If 9-bit transmission is desired, then set bit TX9.

- 5. Enable the transmission by setting enable bit TXEN.

- 6. If 9-bit transmission is selected, the ninth bit should be loaded in bit TX9D.

- 7. Start transmission by loading data to the TXREG register.

- 8. If using interrupts, ensure that GIE and PEIE in the INTCON register are set.

# 12.0 SPECIAL FEATURES OF THE CPU

These devices have a host of features intended to maximize system reliability, minimize cost through elimination of external components, provide power saving operating modes and offer code protection. These are:

- Oscillator Selection

- RESET

- Power-on Reset (POR)

- Power-up Timer (PWRT)

- Oscillator Start-up Timer (OST)

- Brown-out Reset (BOR)

- Interrupts

- Watchdog Timer (WDT)

- SLEEP

- Code Protection

- ID Locations

- In-Circuit Serial Programming

These devices have a Watchdog Timer, which can be enabled or disabled, using a configuration bit. It runs off its own RC oscillator for added reliability.

There are two timers that offer necessary delays on power-up. One is the Oscillator Start-up Timer (OST), intended to keep the chip in RESET until the crystal oscillator is stable. The other is the Power-up Timer (PWRT), which provides a fixed delay of 72 ms (nominal) on power-up only. It is designed to keep the part in RESET while the power supply stabilizes, and is enabled or disabled, using a configuration bit. With these two timers on-chip, most applications need no external RESET circuitry. SLEEP mode is designed to offer a very low current power-down mode. The user can wake-up from SLEEP through external RESET, Watchdog Timer Wake-up, or through an interrupt.

Several oscillator options are also made available to allow the part to fit the application. The RC oscillator option saves system cost while the LP crystal option saves power. Configuration bits are used to select the desired oscillator mode.

Additional information on special features is available in the PICmicro<sup>™</sup> Mid-Range Reference Manual (DS33023).

# 12.1 Configuration Bits

The configuration bits can be programmed (read as '0'), or left unprogrammed (read as '1'), to select various device configurations. These bits are mapped in program memory location 2007h.

The user will note that address 2007h is beyond the user program memory space, which can be accessed only during programming.

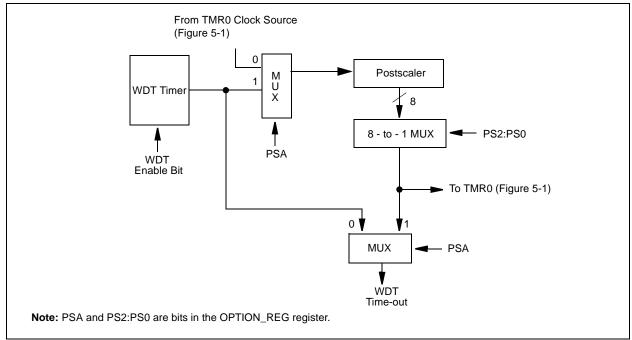

# 12.13 Watchdog Timer (WDT)

The Watchdog Timer is a free running on-chip RC oscillator, which does not require any external components. This RC oscillator is separate from the RC oscillator of the OSC1/CLKIN pin. That means that the WDT will run, even if the clock on the OSC1/CLKIN and OSC2/ CLKOUT pins of the device has been stopped, for example, by execution of a SLEEP instruction.

During normal operation, a WDT time-out generates a device RESET (Watchdog Timer Reset). If the device is in SLEEP mode, a WDT time-out causes the device to wake-up and continue with normal operation (Watchdog Timer Wake-up). The  $\overline{\text{TO}}$  bit in the STATUS register will be cleared upon a Watchdog Timer time-out.

The WDT can be permanently disabled by clearing configuration bit, WDTE (Section 12.1).

WDT time-out period values may be found in the Electrical Specifications section under parameter #31. Values for the WDT prescaler (actually a postscaler, but shared with the Timer0 prescaler) may be assigned using the OPTION\_REG register.

- Note 1: The CLRWDT and SLEEP instructions clear the WDT and the postscaler, if assigned to the WDT, and prevent it from timing out and generating a device RESET condition.

- 2: When a CLRWDT instruction is executed and the prescaler is assigned to the WDT, the prescaler count will be cleared, but the prescaler assignment is not changed.

## FIGURE 12-11: WATCHDOG TIMER BLOCK DIAGRAM

## TABLE 12-7: SUMMARY OF WATCHDOG TIMER REGISTERS

| Address  | Name         | Bit 7 | Bit 6                | Bit 5 | Bit 4 | Bit 3                | Bit 2 | Bit 1 | Bit 0 |

|----------|--------------|-------|----------------------|-------|-------|----------------------|-------|-------|-------|

| 2007h    | Config. bits | (1)   | BODEN <sup>(1)</sup> | _     | CP0   | PWRTE <sup>(1)</sup> | WDTE  | FOSC1 | FOSC0 |

| 81h,181h | OPTION_REG   | RBPU  | INTEDG               | TOCS  | TOSE  | PSA                  | PS2   | PS1   | PS0   |

Legend: Shaded cells are not used by the Watchdog Timer.

Note 1: See Register 12-1 for operation of these bits.

| ; Q1  Q2  Q3  Q4<br>OSC1 /<br>CLKOUT <sup>(4)</sup> \ | ; Q1  Q2  Q3  Q4; Q1 <br>//_//_/_/_/                                                                                                           |                   | Q1  Q2  Q3  Q4<br>  | ; Q1  Q2  Q3  Q4;<br>////_//_// | Q1  Q2  Q3  Q4; (<br>/////<br>/ | 21  Q2  Q3  Q4;<br>\_/\_/\_/ |

|-------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------|-------------------|---------------------|---------------------------------|---------------------------------|------------------------------|

| ·                                                     | λ/ λ<br>ι ι                                                                                                                                    | 1031.1            | /                   | ۱۸/ ۱۸<br>۱ ۱                   | / i\                            | /                            |

| INT pin                                               | <u>ı ı</u>                                                                                                                                     | <u> </u>          |                     | <u> </u>                        | <u> </u>                        | <u> </u>                     |

| INTF Flag<br>(INTCON<1>)                              | ı ı<br>+                                                                                                                                       |                   |                     | Interrupt Latency<br>(Note 2)   |                                 |                              |

| GIE bit<br>(INTCON<7>)                                |                                                                                                                                                | <b>b</b>          |                     |                                 | i                               |                              |

| INSTRUCTION FLOW                                      |                                                                                                                                                |                   |                     | 1 I<br>1 I                      | 1<br>1                          | 1                            |

| PC X PC                                               | Х РС+1 Х                                                                                                                                       | PC+2              | PC+2                | <u>X PC + 2 X</u>               | 0004h X                         | 0005h                        |

| Instruction Fetched Inst(PC) = SLEE                   | P Inst(PC + 1)                                                                                                                                 | 1<br>1<br>1       | Inst(PC + 2)        | 1 1<br>1 1<br>1 1               | Inst(0004h)                     | Inst(0005h)                  |

| Instruction<br>Executed { Inst(PC - 1)                | SLEEP                                                                                                                                          | 1<br> <br>        | Inst(PC + 1)        | Dummy cycle                     | Dummy cycle                     | Inst(0004h)                  |

| 3: GIE = '1' assumed. In<br>If GIE = '0', execution   | tor mode assumed.<br>Irawing not to scale) This de<br>n this case after wake- up, t<br>n will continue in-line.<br>able in these osc modes, bu | the processor jur | mps to the interrup | ot routine.                     |                                 |                              |

#### FIGURE 12-12: WAKE-UP FROM SLEEP THROUGH INTERRUPT

12.15 Program Verification/Code Protection

If the code protection bit(s) have not been programmed, the on-chip program memory can be read out for verification purposes.

## 12.16 ID Locations

Four memory locations (2000h - 2003h) are designated as ID locations, where the user can store checksum or other code identification numbers. These locations are not accessible during normal execution, but are readable and writable during program/verify. It is recommended that only the 4 Least Significant bits of the ID location are used.

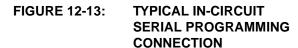

## 12.17 In-Circuit Serial Programming

PIC16F7X microcontrollers can be serially programmed while in the end application circuit. This is simply done, with two lines for clock and data and three other lines for power, ground, and the programming voltage (see Figure 12-13 for an example). This allows customers to manufacture boards with unprogrammed devices, and then program the microcontroller just before shipping the product. This also allows the most recent firmware or a custom firmware to be programmed. For general information of serial programming, please refer to the In-Circuit Serial Programming (ICSP<sup>™</sup>) Guide (DS30277). For specific details on programming commands and operations for the PIC16F7X devices, please refer to the latest version of the PIC16F7X FLASH Program Memory Programming Specification (DS30324).

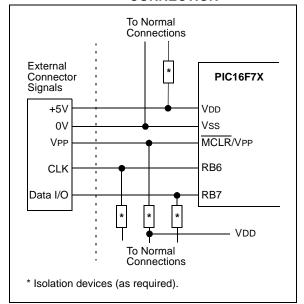

#### **FIGURE 15-9:** CAPTURE/COMPARE/PWM TIMINGS (CCP1 AND CCP2)

#### TABLE 15-5: CAPTURE/COMPARE/PWM REQUIREMENTS (CCP1 AND CCP2)

| Param<br>No. | Symbol |                  | Characteristic   |                      | Min                   | Тур†        | Max | Units | Conditions                        |    |  |

|--------------|--------|------------------|------------------|----------------------|-----------------------|-------------|-----|-------|-----------------------------------|----|--|

| 50*          | TccL   | CCP1 and CCP2    | No Prescaler     |                      | 0.5Tcy + 20           |             |     | ns    |                                   |    |  |

|              |        | input low time   |                  | Standard(F)          | 10                    | —           |     | ns    |                                   |    |  |

|              |        |                  | With Prescaler   | Extended(LF)         | 20                    | —           |     | ns    |                                   |    |  |

| 51*          | ТссН   | CCP1 and CCP2    | No Prescaler     |                      | 0.5Tcy + 20           | —           |     | ns    |                                   |    |  |

|              |        | input high time  |                  |                      |                       | Standard(F) | 10  | —     |                                   | ns |  |

|              |        |                  | With Prescaler   | Extended(LF)         | 20                    | —           |     | ns    |                                   |    |  |

| 52*          | TccP   | CCP1 and CCP2 in | nput period      |                      | <u>3Tcy + 40</u><br>N | -           | _   | ns    | N = prescale<br>value (1,4 or 16) |    |  |

| 53*          | TccR   | CCP1 and CCP2 of | output rise time | Standard(F)          | —                     | 10          | 25  | ns    |                                   |    |  |

|              |        |                  |                  | Extended(LF)         | —                     | 25          | 50  | ns    |                                   |    |  |

| 54*          | TccF   | CCP1 and CCP2 of | output fall time | Standard( <b>F</b> ) | —                     | 10          | 25  | ns    |                                   |    |  |

|              |        |                  |                  | Extended(LF)         | —                     | 25          | 45  | ns    |                                   |    |  |

These parameters are characterized but not tested.

† Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

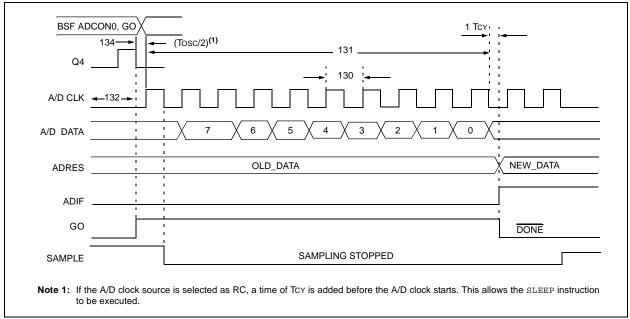

## TABLE 15-13: A/D CONVERSION REQUIREMENTS

| Param<br>No. | Sym  | Characteristic                                       |           | Min | Тур†   | Max | Units | Conditions                                                                                                                                                                                                                       |

|--------------|------|------------------------------------------------------|-----------|-----|--------|-----|-------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 130          | Tad  | A/D clock period                                     | PIC16F7X  | 1.6 | _      | _   | μs    | Tosc based, VREF $\geq 3.0V$                                                                                                                                                                                                     |

|              |      |                                                      | PIC16LF7X | 2.0 | _      | _   | μs    | Tosc based, $2.0V \le VREF \le 5.5V$                                                                                                                                                                                             |

|              |      |                                                      | PIC16F7X  | 2.0 | 4.0    | 6.0 | μs    | A/D RC mode                                                                                                                                                                                                                      |

|              |      |                                                      | PIC16LF7X | 3.0 | 6.0    | 9.0 | μs    | A/D RC mode                                                                                                                                                                                                                      |

| 131          | Тслу | Conversion time (not in<br>S/H time) <b>(Note 1)</b> | cluding   | 9   |        | 9   | Tad   |                                                                                                                                                                                                                                  |

| 132          | TACQ | Acquisition time                                     |           | 5*  | _      |     | μs    | The minimum time is the<br>amplifier settling time. This<br>may be used if the "new" input<br>voltage has not changed by<br>more than 1 LSb (i.e.,<br>20.0 mV @ 5.12V) from the<br>last sampled voltage (as<br>stated on CHOLD). |

| 134          | TGO  | Q4 to A/D clock start                                |           |     | Tosc/2 |     |       | If the A/D clock source is selected as RC, a time of TCY is added before the A/D clock starts. This allows the SLEEP instruction to be executed.                                                                                 |

\* These parameters are characterized but not tested.

† Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

**Note 1:** ADRES register may be read on the following TCY cycle.

2: See Section 11.1 for minimum conditions.

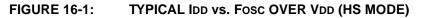

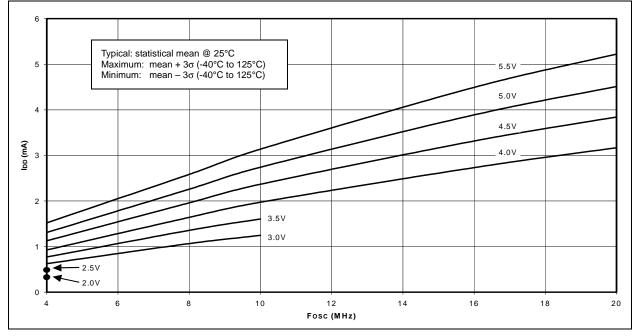

# 16.0 DC AND AC CHARACTERISTICS GRAPHS AND TABLES

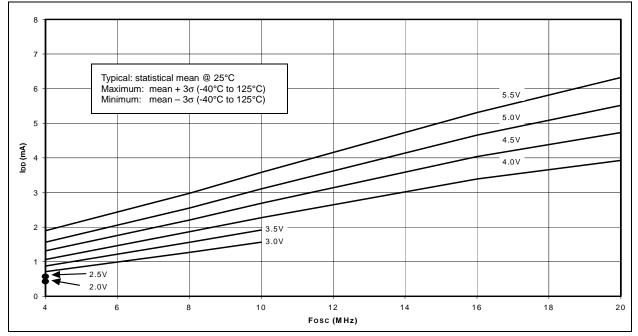

**Note:** The graphs and tables provided following this note are a statistical summary based on a limited number of samples and are provided for informational purposes only. The performance characteristics listed herein are not tested or guaranteed. In some graphs or tables, the data presented may be outside the specified operating range (e.g., outside specified power supply range) and therefore, outside the warranted range.

"Typical" represents the mean of the distribution at 25°C. "Maximum" or "minimum" represents (mean +  $3\sigma$ ) or (mean -  $3\sigma$ ) respectively, where  $\sigma$  is a standard deviation, over the whole temperature range.

| PORTE Register                          |      |        | . 37 |

|-----------------------------------------|------|--------|------|

| Postscaler, WDT                         |      |        |      |

| Assignment (PSA bit)                    |      |        |      |

| Rate Select (PS2:PS0 bits)              |      |        | . 20 |

| Power-down Mode. See SLEEP              |      |        |      |

| Power-on Reset (POR)89,                 |      |        |      |

| Oscillator Start-up Timer (OST)         |      | 89,    | 94   |

| POR Status (POR bit)                    |      |        | .25  |

| Power Control (PCON) Register           |      |        | . 95 |

| Power-down (PD bit)                     |      |        | .93  |

| Power-up Timer (PWRT)                   |      | 89,    | 94   |

| Time-out (TO bit)                       |      |        |      |

| PR2 Register                            |      |        | .51  |

| Prescaler, Timer0                       |      |        |      |

| Assignment (PSA bit)                    |      |        | .20  |

| Rate Select (PS2:PS0 bits)              |      |        |      |

| PRO MATE II Universal Device Programmer |      |        |      |

| Program Counter                         |      |        |      |

| RESET Conditions                        |      |        | . 95 |

| Program Memory                          |      |        |      |

| Associated Registers                    |      |        |      |

| Interrupt Vector                        |      |        | .13  |

| Memory and Stack Maps                   |      |        |      |

| Operation During Code Protect           |      |        |      |

| Organization                            |      |        |      |

| Paging                                  |      |        |      |

| PMADR Register                          |      |        |      |

| PMADRH Register                         |      |        |      |

| Reading FLASH                           |      |        |      |

| Reading, PMADR Register                 |      |        |      |

| Reading, PMADRH Register                |      |        |      |

| Reading, PMCON1 Register                |      |        |      |

| Reading, PMDATA Register                |      |        |      |

| Reading, PMDATH Register                |      |        |      |

| RESET Vector                            |      |        |      |

| Program Verification                    |      |        |      |

| Programming Pin (VPP)                   |      |        |      |

| Programming, Device Instructions        |      |        |      |

| PUSH                                    |      |        |      |

|                                         |      |        |      |

| R                                       |      |        |      |

| R/W bit                                 | .60. | 66.    | 67   |

|                                         |      | ο<br>Ω |      |

| RA0/AN0 Pin          | 8, | 10 |

|----------------------|----|----|

| RA1/AN1 Pin          | 8, | 10 |

| RA2/AN2 Pin          | 8, | 10 |

| RA3/AN3/VREF Pin     | 8, | 10 |

| RA4/T0CKI Pin        |    |    |

| RA5/SS/AN4 Pin       |    |    |

| RAM. See Data Memory | ĺ  |    |