Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                  |

|----------------------------|-------------------------------------------------------------------------|

| Core Processor             | PIC                                                                     |

| Core Size                  | 8-Bit                                                                   |

| Speed                      | 20MHz                                                                   |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                                       |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                   |

| Number of I/O              | 33                                                                      |

| Program Memory Size        | 7KB (4K x 14)                                                           |

| Program Memory Type        | FLASH                                                                   |

| EEPROM Size                |                                                                         |

| RAM Size                   | 192 x 8                                                                 |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 5.5V                                                               |

| Data Converters            | A/D 8x8b                                                                |

| Oscillator Type            | External                                                                |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                       |

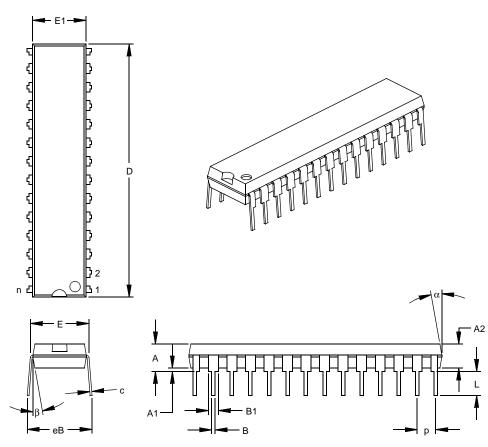

| Mounting Type              | Through Hole                                                            |

| Package / Case             | 40-DIP (0.600", 15.24mm)                                                |

| Supplier Device Package    | 40-PDIP                                                                 |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16lf74-i-p |

|                            |                                                                         |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| Pin Name          | DIP<br>Pin# | PLCC<br>Pin# | QFP<br>Pin# | I/O/P<br>Type | Buffer<br>Type        | Description                                                   |

|-------------------|-------------|--------------|-------------|---------------|-----------------------|---------------------------------------------------------------|

|                   |             |              |             |               |                       | PORTD is a bi-directional I/O port or parallel slave port     |

|                   |             |              |             |               |                       | when interfacing to a microprocessor bus.                     |

| RD0/PSP0          | 19          | 21           | 38          |               | ST/TTL <sup>(3)</sup> |                                                               |

| RD0               |             |              |             | I/O           |                       | Digital I/O.                                                  |

| PSP0              |             |              | 00          | I/O           | ot (3)                | Parallel Slave Port data.                                     |

| RD1/PSP1<br>RD1   | 20          | 22           | 39          | і<br>І/О      | ST/TTL <sup>(3)</sup> | Digital I/O.                                                  |

| PSP1              |             |              |             | 1/O           |                       | Parallel Slave Port data.                                     |

| RD2/PSP2          | 21          | 23           | 40          | 1, C          | ST/TTL <sup>(3)</sup> |                                                               |

| RD2               | 21          | 20           | 40          | ı/O           | OI/TIE                | Digital I/O.                                                  |

| PSP2              |             |              |             | I/O           |                       | Parallel Slave Port data.                                     |

| RD3/PSP3          | 22          | 24           | 41          |               | ST/TTL <sup>(3)</sup> |                                                               |

| RD3               |             |              |             | I/O           |                       | Digital I/O.                                                  |

| PSP3              |             |              |             | I/O           |                       | Parallel Slave Port data.                                     |

| RD4/PSP4          | 27          | 30           | 2           |               | ST/TTL <sup>(3)</sup> |                                                               |

| RD4               |             |              |             | I/O           |                       | Digital I/O.                                                  |

| PSP4              |             |              |             | I/O           |                       | Parallel Slave Port data.                                     |

| RD5/PSP5          | 28          | 31           | 3           |               | ST/TTL <sup>(3)</sup> |                                                               |

| RD5               |             |              |             | I/O           |                       | Digital I/O.                                                  |

| PSP5              |             |              |             | I/O           | · · · · · · (2)       | Parallel Slave Port data.                                     |

| RD6/PSP6          | 29          | 32           | 4           |               | ST/TTL <sup>(3)</sup> | District I/O                                                  |

| RD6<br>PSP6       |             |              |             | I/O<br>I/O    |                       | Digital I/O.<br>Parallel Slave Port data.                     |

| RD7/PSP7          | 30          | 33           | 5           | 1/0           | ST/TTL <sup>(3)</sup> | Faraller Slave Folt data.                                     |

| RD7/PSP7          | 30          | - 33         | Э           | I/O           | 51/11L*/              | Digital I/O.                                                  |

| PSP7              |             |              |             | 1/O           |                       | Parallel Slave Port data.                                     |

| -                 |             |              |             |               |                       | PORTE is a bi-directional I/O port.                           |

| RE0/RD/AN5        | 8           | 9            | 25          |               | ST/TTL <sup>(3)</sup> |                                                               |

| RE0               | -           | -            |             | I/O           |                       | Digital I/O.                                                  |

| RD                |             |              |             | I             |                       | Read control for parallel slave port .                        |

| AN5               |             |              |             | I             |                       | Analog input 5.                                               |

| RE1/WR/AN6        | 9           | 10           | 26          |               | ST/TTL <sup>(3)</sup> |                                                               |

| RE1               |             |              |             | I/O           |                       | Digital I/O.                                                  |

| WR                |             |              |             | 1             |                       | Write control for parallel slave port .                       |

| AN6               |             |              |             | I             | o <i></i> (3)         | Analog input 6.                                               |

| RE2/CS/AN7        | 10          | 11           | 27          |               | ST/TTL <sup>(3)</sup> |                                                               |

| RE2<br>CS         |             |              |             | I/O<br>I      |                       | Digital I/O.<br>Chip select control for parallel slave port . |

| AN7               |             |              |             | 1             |                       | Analog input 7.                                               |

| Vss               | 12,31       | 13,34        | 6,29        | P             | _                     | Ground reference for logic and I/O pins.                      |

| VDD               | 11,32       | 12,35        | 7,28        | Р             | _                     | Positive supply for logic and I/O pins.                       |

| NC                | · -         | 1,17,2       | 12,13,      |               | _                     | These pins are not internally connected. These pins should    |

|                   |             | 8, 40        | 33, 34      |               |                       | be left unconnected.                                          |

| Legend: I = input |             | O = 0        |             | I/C           | ) = input/outpu       | ut P = power                                                  |

#### **TABLE 1-3:** PIC16F74 AND PIC16F77 PINOUT DESCRIPTION (CONTINUED)

**Note 1:** This buffer is a Schmitt Trigger input when configured as an external interrupt.

2: This buffer is a Schmitt Trigger input when used in Serial Programming mode.

3: This buffer is a Schmitt Trigger input when configured as general purpose I/O and a TTL input when used in the Parallel Slave Port mode (for interfacing to a microprocessor bus).

4: This buffer is a Schmitt Trigger input when configured in RC Oscillator mode and a CMOS input otherwise.

### 2.2.2.5 PIR1 Register

The PIR1 register contains the individual flag bits for the peripheral interrupts.

| Note: | Interrupt flag bits are set when an interrupt  |

|-------|------------------------------------------------|

|       | condition occurs, regardless of the state of   |

|       | its corresponding enable bit or the global     |

|       | enable bit, GIE (INTCON<7>). User soft-        |

|       | ware should ensure the appropriate interrupt   |

|       | bits are clear prior to enabling an interrupt. |

### REGISTER 2-5: PIR1 REGISTER (ADDRESS 0Ch)

| R/W-0                | R/W-0 | R-0  | R-0  | R/W-0 | R/W-0  | R/W-0  | R/W-0  |

|----------------------|-------|------|------|-------|--------|--------|--------|

| PSPIF <sup>(1)</sup> | ADIF  | RCIF | TXIF | SSPIF | CCP1IF | TMR2IF | TMR1IF |

| bit 7                |       |      |      |       |        |        | bit 0  |

| bit 7 | <b>PSPIF<sup>(1)</sup>:</b> Parallel Slave Port Read/Write Interrupt Flag bit<br>1 = A read or a write operation has taken place (must be cleared in software)<br>0 = No read or write has occurred                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |

|-------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| bit 6 | ADIF: A/D Converter Interrupt Flag bit<br>1 = An A/D conversion is completed (must be cleared in software)<br>0 = The A/D conversion is not complete                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |

| bit 5 | RCIF: USART Receive Interrupt Flag bit<br>1 = The USART receive buffer is full<br>0 = The USART receive buffer is empty                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |

| bit 4 | <b>TXIF</b> : USART Transmit Interrupt Flag bit<br>1 = The USART transmit buffer is empty<br>0 = The USART transmit buffer is full                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |

| bit 3 | <ul> <li>SSPIF: Synchronous Serial Port (SSP) Interrupt Flag</li> <li>1 = The SSP interrupt condition has occurred, and must be cleared in software before returning from the Interrupt Service Routine. The conditions that will set this bit are:</li> <li><u>SPI</u> <ul> <li>A transmission/reception has taken place.</li> <li><u>I<sup>2</sup>C Slave</u></li> <li>A transmission/reception has taken place.</li> <li><u>I<sup>2</sup>C Master</u></li> <li>A transmission/reception has taken place.</li> <li>The initiated START condition was completed by the SSP module.</li> <li>The initiated Restart condition was completed by the SSP module.</li> <li>The initiated Restart condition was completed by the SSP module.</li> <li>A START condition occurred while the SSP module was IDLE (multi-master system).</li> <li>A STOP condition has occurred</li> </ul> </li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |

| bit 2 | CCP1IF: CCP1 Interrupt Flag bit<br><u>Capture mode:</u><br>1 = A TMR1 register capture occurred (must be cleared in software)<br>0 = No TMR1 register capture occurred<br><u>Compare mode:</u><br>1 = A TMR1 register compare match occurred (must be cleared in software)<br>0 = No TMR1 register compare match occurred<br><u>PWM mode:</u><br>Unused in this mode                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |

| bit 1 | <b>TMR2IF</b> : TMR2 to PR2 Match Interrupt Flag bit<br>1 = TMR2 to PR2 match occurred (must be cleared in software)<br>0 = No TMR2 to PR2 match occurred                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |

| bit 0 | <ul> <li>TMR1IF: TMR1 Overflow Interrupt Flag bit</li> <li>1 = TMR1 register overflowed (must be cleared in software)</li> <li>0 = TMR1 register did not overflow</li> <li>Note 1: PSPIF is reserved on 28-pin devices; always maintain this bit clear.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |

|       | Legend.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |

|       | <ul> <li>No read or write has occurred</li> <li>DiF: A/D Converter Interrupt Flag bit</li> <li>An A/D Conversion is completed (must be cleared in software)</li> <li>The A/D conversion is not complete</li> <li>DiF: A/D conversion is not complete</li> <li>DiF: USART Receive Interrupt Flag bit</li> <li>The USART receive buffer is full</li> <li>The USART receive buffer is empty</li> <li>UF: USART transmit buffer is empty</li> <li>The USART transmit buffer is enclassion/reception has cocurred, and must be cleared in software before returning from the Interrupt Service Routine. The conditions that will set this bit are: SPI</li> <li>A transmission/reception has taken place.</li> <li><u>I<sup>C</sup>C Master</u></li> <li>A transmission/reception has taken place.</li> <li><u>I<sup>C</sup>C Master</u></li> <li>A transmission/reception has taken place.</li> <li>The initiated Restart condition was completed by the SSP module.</li> <li>The initiated Restart condition was completed by the SSP module.</li> <li>The initiated Restart condition was completed by the SSP module.</li> <li>A START condition occurred while the SSP module was IDLE (multi-master system).</li> <li>A STOP condition occurred while the SSP module was IDLE (multi-master system).</li> <li>A SSP interrupt Condition has occurred</li> <li>CPIIF: CCP1 Interrupt Flag bit <u>splute mode</u>:</li> <li>A TMR1 register capture occurred (must be cleared in software)</li> <li>No TMR1 register compare match occurred (must be cleared in software)</li> <li>No TMR1 register compare match occurred (must be cleared in software)</li> <li>No TMR1 register compare match occurred (must be cleared in software)</li> <li>No TMR1 register occurred Multis be cleared in software)</li> <li>No TMR2 to PR2 match occu</li></ul> |  |

|       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |

'1' = Bit is set

'0' = Bit is cleared

- n = Value at POR reset

x = Bit is unknown

# 4.0 I/O PORTS

Some pins for these I/O ports are multiplexed with an alternate function for the peripheral features on the device. In general, when a peripheral is enabled, that pin may not be used as a general purpose I/O pin.

Additional information on I/O ports may be found in the PICmicro<sup>™</sup> Mid-Range Reference Manual, (DS33023).

## 4.1 PORTA and the TRISA Register

PORTA is a 6-bit wide, bi-directional port. The corresponding data direction register is TRISA. Setting a TRISA bit (= '1') will make the corresponding PORTA pin an input (i.e., put the corresponding output driver in a Hi-Impedance mode). Clearing a TRISA bit (= '0') will make the corresponding PORTA pin an output (i.e., put the contents of the output latch on the selected pin).

Reading the PORTA register reads the status of the pins, whereas writing to it will write to the port latch. All write operations are read-modify-write operations. Therefore, a write to a port implies that the port pins are read, the value is modified and then written to the port data latch.

Pin RA4 is multiplexed with the Timer0 module clock input to become the RA4/T0CKI pin. The RA4/T0CKI pin is a Schmitt Trigger input and an open drain output. All other PORTA pins have TTL input levels and full CMOS output drivers.

Other PORTA pins are multiplexed with analog inputs and analog VREF input. The operation of each pin is selected by clearing/setting the control bits in the ADCON1 register (A/D Control Register1).

**Note:** On a Power-on Reset, these pins are configured as analog inputs and read as '0'.

The TRISA register controls the direction of the RA pins, even when they are being used as analog inputs. The user must ensure the bits in the TRISA register are maintained set, when using them as analog inputs.

| BCF<br>BCF<br>CLRF                      | STATUS,<br>STATUS,<br>PORTA                |     | ;<br>; Bank0<br>; Initialize PORTA by<br>; clearing output<br>: data latches | Y |

|-----------------------------------------|--------------------------------------------|-----|------------------------------------------------------------------------------|---|

| BSF<br>MOVLW<br>MOVWF<br>MOVLW<br>MOVWF | STATUS,<br>0x06<br>ADCON1<br>0xCF<br>TRISA | RPO | ,                                                                            |   |

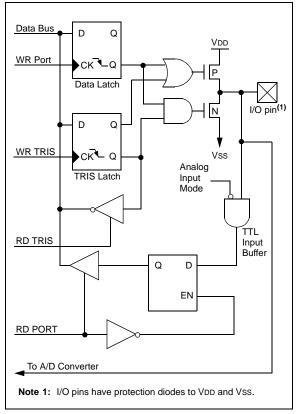

## FIGURE 4-1:

#### BLOCK DIAGRAM OF RA3:RA0 AND RA5 PINS

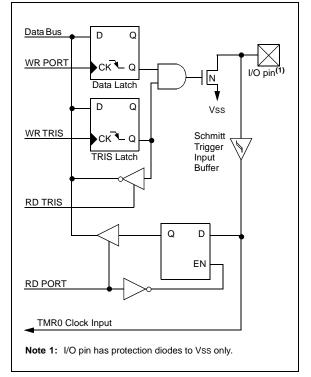

FIGURE 4-2:

### BLOCK DIAGRAM OF RA4/T0CKI PIN

#### 5.2 Using Timer0 with an External Clock

When no prescaler is used, the external clock input is the same as the prescaler output. The synchronization of T0CKI, with the internal phase clocks, is accomplished by sampling the prescaler output on the Q2 and Q4 cycles of the internal phase clocks. Therefore, it is necessary for T0CKI to be high for at least 2Tosc (and a small RC delay of 20 ns) and low for at least 2Tosc (and a small RC delay of 20 ns). Refer to the electrical specification of the desired device.

| REGISTER 5-1: | <b>OPTION_REG REGISTER</b> |

|---------------|----------------------------|

|---------------|----------------------------|

|         | R/W-1                                                                                                            | R/W-1                                         | R/W-1        | R/W-1        | R/W-1     | R/W-1      | R/W-1        | R/W-1   |  |  |  |  |

|---------|------------------------------------------------------------------------------------------------------------------|-----------------------------------------------|--------------|--------------|-----------|------------|--------------|---------|--|--|--|--|

|         | RBPU                                                                                                             | INTEDG                                        | TOCS         | T0SE         | PSA       | PS2        | PS1          | PS0     |  |  |  |  |

|         | bit 7                                                                                                            |                                               |              |              |           |            |              | bit 0   |  |  |  |  |

|         |                                                                                                                  |                                               |              |              |           |            |              |         |  |  |  |  |

| bit 7   | <b>RBPU</b> : PORTB Pull-up Enable bit (see Section 2.2.2.2)                                                     |                                               |              |              |           |            |              |         |  |  |  |  |

| bit 6   | INTEDG: Interrupt Edge Select bit (see Section 2.2.2.2)                                                          |                                               |              |              |           |            |              |         |  |  |  |  |

| bit 5   | T0CS: TMR0 Clock Source Select bit                                                                               |                                               |              |              |           |            |              |         |  |  |  |  |

|         |                                                                                                                  | tion on T0Ck<br>al instruction                |              | (CLKOUT)     |           |            |              |         |  |  |  |  |

| bit 4   | TOSE: TM                                                                                                         | R0 Source E                                   | Edge Select  | bit          |           |            |              |         |  |  |  |  |

|         | 1 = Incren                                                                                                       | nent on high-                                 | to-low trans | ition on TOC | KI pin    |            |              |         |  |  |  |  |

|         | 0 = Incren                                                                                                       | nent on low-t                                 | o-high trans | ition on TOC | KI pin    |            |              |         |  |  |  |  |

| bit 3   | PSA: Pres                                                                                                        | PSA: Prescaler Assignment bit                 |              |              |           |            |              |         |  |  |  |  |

|         | <ul> <li>1 = Prescaler is assigned to the WDT</li> <li>0 = Prescaler is assigned to the Timer0 module</li> </ul> |                                               |              |              |           |            |              |         |  |  |  |  |

| bit 2-0 | PS2:PS0:                                                                                                         | Prescaler R                                   | ate Select b | its          |           |            |              |         |  |  |  |  |

|         | Bit Value                                                                                                        | TMR0 Rate                                     | WDT Rate     |              |           |            |              |         |  |  |  |  |

|         | 000                                                                                                              | 1:2                                           | 1:1          |              |           |            |              |         |  |  |  |  |

|         | 001                                                                                                              | 1:4<br>1:8                                    | 1:2<br>1:4   |              |           |            |              |         |  |  |  |  |

|         | 010<br>011                                                                                                       | 1:16                                          | 1:4          |              |           |            |              |         |  |  |  |  |

|         | 100                                                                                                              | 1:32                                          | 1:16         |              |           |            |              |         |  |  |  |  |

|         | 101                                                                                                              | 1:64                                          | 1:32         |              |           |            |              |         |  |  |  |  |

|         | 110                                                                                                              | 1:128                                         | 1:64         |              |           |            |              |         |  |  |  |  |

|         | 111                                                                                                              | 1 : 256                                       | 1 : 128      |              |           |            |              |         |  |  |  |  |

|         | Legend:                                                                                                          |                                               |              |              |           |            |              |         |  |  |  |  |

|         | R = Reada                                                                                                        | able bit                                      | W = V        | Vritable bit | U = Unii  | mplemented | bit, read as | '0'     |  |  |  |  |

|         | - n = Value                                                                                                      | e at POR res                                  | et '1' = B   | Bit is set   | '0' = Bit | is cleared | x = Bit is ι | unknown |  |  |  |  |

|         |                                                                                                                  |                                               |              |              |           |            |              |         |  |  |  |  |

|         |                                                                                                                  | To avoid ar                                   |              |              |           |            |              |         |  |  |  |  |

|         |                                                                                                                  | Example 5-1<br>caler assigni<br>even if the W | ment betwee  | en Timer0 a  |           |            |              |         |  |  |  |  |

# 9.3 SSP I<sup>2</sup>C Operation

The SSP module in  $l^2C$  mode, fully implements all slave functions, except general call support, and provides interrupts on START and STOP bits in hardware to facilitate firmware implementations of the master functions. The SSP module implements the standard mode specifications as well as 7-bit and 10-bit addressing.

Two pins are used for data transfer. These are the RC3/ SCK/SCL pin, which is the clock (SCL), and the RC4/ SDI/SDA pin, which is the data (SDA). The user must configure these pins as inputs or outputs through the TRISC<4:3> bits.

The SSP module functions are enabled by setting SSP enable bit SSPEN (SSPCON<5>).

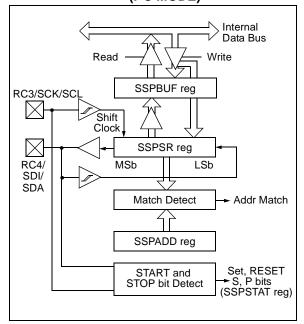

FIGURE 9-5: SSP BLOCK DIAGRAM (I<sup>2</sup>C MODE)

The SSP module has five registers for  $\mathsf{I}^2\mathsf{C}$  operation. These are the:

- SSP Control Register (SSPCON)

- SSP Status Register (SSPSTAT)

- Serial Receive/Transmit Buffer (SSPBUF)

- SSP Shift Register (SSPSR) Not directly accessible

- SSP Address Register (SSPADD)

The SSPCON register allows control of the  $I^2C$  operation. Four mode selection bits (SSPCON<3:0>) allow one of the following  $I^2C$  modes to be selected:

- I<sup>2</sup>C Slave mode (7-bit address)

- I<sup>2</sup>C Slave mode (10-bit address)

- I<sup>2</sup>C Slave mode (7-bit address), with START and STOP bit interrupts enabled to support Firmware Master mode

- I<sup>2</sup>C Slave mode (10-bit address), with START and STOP bit interrupts enabled to support Firmware Master mode

- I<sup>2</sup>C START and STOP bit interrupts enabled to support Firmware Master mode, Slave is IDLE

Selection of any  $I^2C$  mode with the SSPEN bit set, forces the SCL and SDA pins to be open drain, provided these pins are programmed to inputs by setting the appropriate TRISC bits. Pull-up resistors must be provided externally to the SCL and SDA pins for proper operation of the  $I^2C$  module.

Additional information on SSP I<sup>2</sup>C operation can be found in the PICmicro<sup>™</sup> Mid-Range MCU Family Reference Manual (DS33023A).

### 9.3.1 SLAVE MODE

In Slave mode, the SCL and SDA pins must be configured as inputs (TRISC<4:3> set). The SSP module will override the input state with the output data when required (slave-transmitter).

When an address is matched, or the data transfer after an address match is received, the hardware automatically will generate the Acknowledge ( $\overline{ACK}$ ) pulse, and then load the SSPBUF register with the received value currently in the SSPSR register.

There are certain conditions that will cause the SSP module not to give this ACK pulse. They include (either or both):

- a) The buffer full bit BF (SSPSTAT<0>) was set before the transfer was received.

- b) The overflow bit SSPOV (SSPCON<6>) was set before the transfer was received.

In this case, the SSPSR register value is not loaded into the SSPBUF, but bit SSPIF (PIR1<3>) is set. Table 9-2 shows what happens when a data transfer byte is received, given the status of bits BF and SSPOV. The shaded cells show the condition where user software did not properly clear the overflow condition. Flag bit BF is cleared by reading the SSPBUF register, while bit SSPOV is cleared through software.

The SCL clock input must have a minimum high and low for proper operation. The high and low times of the  $I^2C$  specification, as well as the requirements of the SSP module, are shown in timing parameter #100 and parameter #101.

| FIGURE 9-6: I <sup>2</sup> C WAVEFO                                                                                                                                                                                                                                                      | DRMS FOR RECEPTION (7-BIT ADDRESS)                                           |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------|

| Receiving Address $R\overline{W}$<br>SDA $\overline{\sqrt{1}}$ $\overline{A7} \overline{A6} \overline{A5} \overline{A4} \overline{A3} \overline{A2} \overline{A1}$<br>SCL $\frac{1}{1} S^{1} \sqrt{1} \sqrt{2} \sqrt{3} \sqrt{4} \sqrt{5} \sqrt{6} \sqrt{7} \sqrt{8}$<br>SSPIF (PIR1<3>) | =0 Receiving Data ACK Receiving Data ACK |

| BF (SSPSTAT<0>)                                                                                                                                                                                                                                                                          | SSPBUF register is read                                                      |

| SSPOV (SSPCON<6>)                                                                                                                                                                                                                                                                        | Bit SSPOV is set because the SSPBUF register is still full.                  |

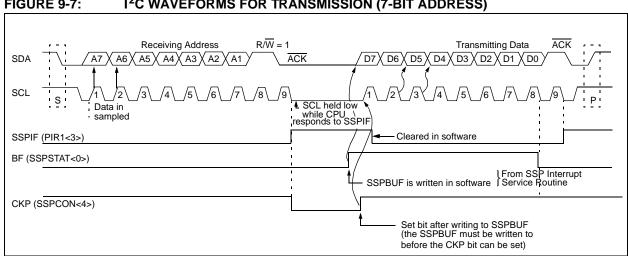

#### 9.3.1.3 Transmission

When the R/W bit of the incoming address byte is set and an address match occurs, the R/W bit of the SSPSTAT register is set. The received address is loaded into the SSPBUF register. The ACK pulse will be sent on the ninth bit, and pin RC3/SCK/SCL is held low. The transmit data must be loaded into the SSPBUF register, which also loads the SSPSR register. Then, pin RC3/SCK/SCL should be enabled by setting bit CKP (SSPCON<4>). The master must monitor the SCL pin prior to asserting another clock pulse. The slave devices may be holding off the master by stretching the clock. The eight data bits are shifted out on the falling edge of the SCL input. This ensures that the SDA signal is valid during the SCL high time (Figure 9-7).

An SSP interrupt is generated for each data transfer byte. Flag bit SSPIF must be cleared in software, and the SSPSTAT register is used to determine the status of the byte. Flag bit SSPIF is set on the falling edge of the ninth clock pulse.

As a slave-transmitter, the ACK pulse from the masterreceiver is latched on the rising edge of the ninth SCL input pulse. If the SDA line was high (not ACK), then the data transfer is complete. When the  $\overline{ACK}$  is latched by the slave, the slave logic is reset (resets SSPSTAT register) and the slave then monitors for another occurrence of the START bit. If the SDA line was low (ACK), the transmit data must be loaded into the SSPBUF reqister, which also loads the SSPSR register. Then pin RC3/SCK/SCL should be enabled by setting bit CKP.

#### I<sup>2</sup>C WAVEFORMS FOR TRANSMISSION (7-BIT ADDRESS) FIGURE 9-7:

| Address                | Name   | Bit 7                | Bit 6                  | Bit 5      | Bit 4 | Bit 3 | Bit 2  | Bit 1  | Bit 0  | Value on:<br>POR, BOR | Value on<br>all other<br>RESETS |

|------------------------|--------|----------------------|------------------------|------------|-------|-------|--------|--------|--------|-----------------------|---------------------------------|

| 0Bh, 8Bh,<br>10Bh,18Bh | INTCON | GIE                  | PEIE                   | TMR0IE     | INTE  | RBIE  | TMR0IF | INTF   | RBIF   | 0000 000x             | 0000 000u                       |

| 0Ch                    | PIR1   | PSPIF <sup>(1)</sup> | ADIF                   | RCIF       | TXIF  | SSPIF | CCP1IF | TMR2IF | TMR1IF | 0000 0000             | 0000 0000                       |

| 18h                    | RCSTA  | SPEN                 | RX9                    | SREN       | CREN  | _     | FERR   | OERR   | RX9D   | 0000 -00x             | 0000 -00x                       |

| 1Ah                    | RCREG  | USART Re             | USART Receive Register |            |       |       |        |        |        |                       | 0000 0000                       |

| 8Ch                    | PIE1   | PSPIE <sup>(1)</sup> | ADIE                   | RCIE       | TXIE  | SSPIE | CCP1IE | TMR2IE | TMR1IE | 0000 0000             | 0000 0000                       |

| 98h                    | TXSTA  | CSRC                 | TX9                    | TXEN       | SYNC  | _     | BRGH   | TRMT   | TX9D   | 0000 -010             | 0000 -010                       |

| 99h                    | SPBRG  | Baud Rate            | Generat                | or Registe | r     |       | •      | •      |        | 0000 0000             | 0000 0000                       |

Legend: x = unknown, - = unimplemented, read as '0'. Shaded cells are not used for synchronous master reception. **Note** 1: Bits PSPIE and PSPIF are reserved on the PIC16F73/76 devices; always maintain these bits clear.

## 10.4 USART Synchronous Slave Mode

Synchronous Slave mode differs from the Master mode, in that the shift clock is supplied externally at the RC6/TX/CK pin (instead of being supplied internally in Master mode). This allows the device to transfer or receive data while in SLEEP mode. Slave mode is entered by clearing bit CSRC (TXSTA<7>).

### 10.4.1 USART SYNCHRONOUS SLAVE TRANSMIT

The operation of the Synchronous Master and Slave modes are identical except in the case of the SLEEP mode.

If two words are written to the TXREG and then the SLEEP instruction is executed, the following will occur:

- a) The first word will immediately transfer to the TSR register and transmit when the master device drives the CK line.

- b) The second word will remain in TXREG register.

- c) Flag bit TXIF will not be set.

- d) When the first word has been shifted out of TSR, the TXREG register will transfer the second word to the TSR and flag bit TXIF will now be set.

- e) If enable bit TXIE is set, the interrupt will wake the chip from SLEEP and if the global interrupt is enabled, the program will branch to the interrupt vector (0004h).

Follow these steps when setting up a Synchronous Slave Transmission:

- 1. Enable the synchronous slave serial port by setting bits SYNC and SPEN and clearing bit CSRC.

- 2. Clear bits CREN and SREN.

- 3. If interrupts are desired, then set enable bit TXIE.

- 4. If 9-bit transmission is desired, then set bit TX9.

- 5. Enable the transmission by setting enable bit TXEN.

- 6. If 9-bit transmission is selected, the ninth bit should be loaded in bit TX9D.

- 7. Start transmission by loading data to the TXREG register.

- 8. If using interrupts, ensure that GIE and PEIE in the INTCON register are set.

| Address                | Name   | Bit 7                | Bit 6                        | Bit 5   | Bit 4 | Bit 3 | Bit 2  | Bit 1  | Bit 0  | Value on:<br>POR,<br>BOR | Value on<br>all other<br>RESETS |

|------------------------|--------|----------------------|------------------------------|---------|-------|-------|--------|--------|--------|--------------------------|---------------------------------|

| 0Bh, 8Bh,<br>10Bh,18Bh | INTCON | GIE                  | PEIE                         | TMR0IE  | INTE  | RBIE  | TMR0IF | INTF   | RBIF   | 0000 000x                | 0000 000u                       |

| 0Ch                    | PIR1   | PSPIF <sup>(1)</sup> | ADIF                         | RCIF    | TXIF  | SSPIF | CCP1IF | TMR2IF | TMR1IF | 0000 0000                | 0000 0000                       |

| 18h                    | RCSTA  | SPEN                 | RX9                          | SREN    | CREN  | ADDEN | FERR   | OERR   | RX9D   | 0000 000x                | 0000 000x                       |

| 19h                    | TXREG  | USART Tr             | ansmit R                     | egister |       |       |        |        |        | 0000 0000                | 0000 0000                       |

| 8Ch                    | PIE1   | PSPIE <sup>(1)</sup> | ADIE                         | RCIE    | TXIE  | SSPIE | CCP1IE | TMR2IE | TMR1IE | 0000 0000                | 0000 0000                       |

| 98h                    | TXSTA  | CSRC                 | TX9                          | TXEN    | SYNC  | —     | BRGH   | TRMT   | TX9D   | 0000 -010                | 0000 -010                       |

| 99h                    | SPBRG  | Baud Rate            | Baud Rate Generator Register |         |       |       |        |        |        |                          | 0000 0000                       |

Legend: x = unknown, - = unimplemented, read as '0'. Shaded cells are not used for synchronous slave transmission.

Note 1: Bits PSPIE and PSPIF are reserved on the PIC16F73/76 devices; always maintain these bits clear.

### 10.4.2 USART SYNCHRONOUS SLAVE RECEPTION

The operation of the Synchronous Master and Slave modes is identical, except in the case of the SLEEP mode. Bit SREN is a "don't care" in Slave mode.

If receive is enabled by setting bit CREN prior to the SLEEP instruction, then a word may be received during SLEEP. On completely receiving the word, the RSR register will transfer the data to the RCREG register and if enable bit RCIE bit is set, the interrupt generated will wake the chip from SLEEP. If the global interrupt is enabled, the program will branch to the interrupt vector (0004h).

Follow these steps when setting up a Synchronous Slave Reception:

- Enable the synchronous master serial port by setting bits SYNC and SPEN and clearing bit CSRC.

- 2. If interrupts are desired, set enable bit RCIE.

- 3. If 9-bit reception is desired, set bit RX9.

- 4. To enable reception, set enable bit CREN.

- 5. Flag bit RCIF will be set when reception is complete and an interrupt will be generated, if enable bit RCIE was set.

- Read the RCSTA register to get the ninth bit (if enabled) and determine if any error occurred during reception.

- 7. Read the 8-bit received data by reading the RCREG register.

- 8. If any error occurred, clear the error by clearing bit CREN.

- 9. If using interrupts, ensure that GIE and PEIE in the INTCON register are set.

| Address                | Name   | Bit 7                | Bit 6    | Bit 5        | Bit 4 | Bit 3 | Bit 2  | Bit 1  | Bit 0  | Value on:<br>POR,<br>BOR | Value on<br>all other<br>RESETS |

|------------------------|--------|----------------------|----------|--------------|-------|-------|--------|--------|--------|--------------------------|---------------------------------|

| 0Bh, 8Bh,<br>10Bh,18Bh | INTCON | GIE                  | PEIE     | TMR0IE       | INTE  | RBIE  | TMR0IF | INTF   | RBIF   | 0000 000x                | 0000 000u                       |

| 0Ch                    | PIR1   | PSPIF <sup>(1)</sup> | ADIF     | RCIF         | TXIF  | SSPIF | CCP1IF | TMR2IF | TMR1IF | 0000 0000                | 0000 0000                       |

| 18h                    | RCSTA  | SPEN                 | RX9      | SREN         | CREN  | ADDEN | FERR   | OERR   | RX9D   | 0000 000x                | 0000 000x                       |

| 1Ah                    | RCREG  | USART R              | eceive R | egister      |       |       |        |        |        | 0000 0000                | 0000 0000                       |

| 8Ch                    | PIE1   | PSPIE <sup>(1)</sup> | ADIE     | RCIE         | TXIE  | SSPIE | CCP1IE | TMR2IE | TMR1IE | 0000 0000                | 0000 0000                       |

| 98h                    | TXSTA  | CSRC                 | TX9      | TXEN         | SYNC  | _     | BRGH   | TRMT   | TX9D   | 0000 -010                | 0000 -010                       |

| 99h                    | SPBRG  | Baud Rate            | e Genera | ator Registe | er    |       |        |        |        | 0000 0000                | 0000 0000                       |

### TABLE 10-10: REGISTERS ASSOCIATED WITH SYNCHRONOUS SLAVE RECEPTION

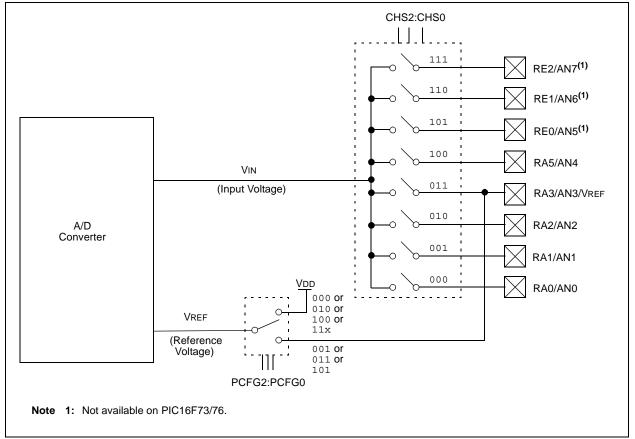

Legend: x = unknown, - = unimplemented, read as '0'. Shaded cells are not used for synchronous slave reception. Note 1: Bits PSPIE and PSPIF are reserved on the PIC16F73/76 devices, always maintain these bits clear. The following steps should be followed for doing an  $\ensuremath{\mathsf{A}}\xspace/\ensuremath{\mathsf{D}}\xspace$  conversion:

- 1. Configure the A/D module:

- Configure analog pins, voltage reference, and digital I/O (ADCON1)

- Select A/D conversion clock (ADCON0)

- Turn on A/D module (ADCON0)

- 2. Configure the A/D interrupt (if desired):

- Clear ADIF bit

- Set ADIE bit

- Set PEIE bit

- Set GIE bit

- 3. Select an A/D input channel (ADCON0).

- 4. Wait for at least an appropriate acquisition period.

- 5. Start conversion:Set GO/DONE bit (ADCON0)

- 6. Wait for the A/D conversion to complete, by either:

- Polling for the GO/DONE bit to be cleared (interrupts disabled)

OR

- Waiting for the A/D interrupt

- 7. Read A/D result register (ADRES), and clear bit ADIF if required.

- 8. For next conversion, go to step 3 or step 4, as required.

### FIGURE 11-1: A/D BLOCK DIAGRAM

### 11.1 A/D Acquisition Requirements

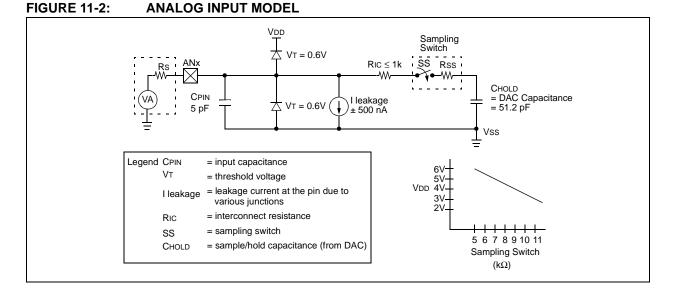

For the A/D converter to meet its specified accuracy, the charge holding capacitor (CHOLD) must be allowed to fully charge to the input channel voltage level. The analog input model is shown in Figure 11-2. The source impedance (Rs) and the internal sampling switch (Rss) impedance directly affect the time required to charge the capacitor CHOLD. The sampling switch (Rss) impedance varies over the device voltage (VDD), see Figure 11-2. The source impedance affects the offset voltage at the analog input (due to pin leakage current). The maximum recommended impedance for analog sources is 10 k $\Omega$ . After the analog input channel is selected (changed), the acquisition period must pass before the conversion can be started.

To calculate the minimum acquisition time, TACQ, see the PICmicro<sup>TM</sup> Mid-Range MCU Family Reference Manual (DS33023). In general, however, given a maximum source impedance of 10 k $\Omega$  and at a temperature of 100°C, TACQ will be no more than 16 µsec.

### TABLE 11-1: TAD vs. MAXIMUM DEVICE OPERATING FREQUENCIES (STANDARD DEVICES (C))

| AD Cloc                 | Maximum Device Frequency |          |

|-------------------------|--------------------------|----------|

| Operation               | ADCS1:ADCS0              | Max.     |

| 2Tosc                   | 0.0                      | 1.25 MHz |

| 8Tosc                   | 01                       | 5 MHz    |

| 32Tosc                  | 10                       | 20 MHz   |

| RC <sup>(1, 2, 3)</sup> | 11                       | (Note 1) |

Note 1: The RC source has a typical TAD time of 4 µs but can vary between 2-6 µs.

2: When the device frequencies are greater than 1 MHz, the RC A/D conversion clock source is only recommended for SLEEP operation.

3: For extended voltage devices (LC), please refer to the Electrical Specifications section.

### TABLE 12-2: CAPACITOR SELECTION FOR CRYSTAL OSCILLATOR (FOR DESIGN GUIDANCE ONLY)

| Osc Type | Crystal<br>Freq | Typical Capacitor Values<br>Tested: |       |  |  |  |

|----------|-----------------|-------------------------------------|-------|--|--|--|

|          | ITEG            | C1                                  | C2    |  |  |  |

| LP       | 32 kHz          | 33 pF                               | 33 pF |  |  |  |

|          | 200 kHz         | 15 pF                               | 15 pF |  |  |  |

| XT       | 200 kHz         | 56 pF                               | 56 pF |  |  |  |

|          | 1 MHz           | 15 pF                               | 15 pF |  |  |  |

|          | 4 MHz           | 15 pF                               | 15 pF |  |  |  |

| HS       | 4 MHz           | 15 pF                               | 15 pF |  |  |  |

|          | 8 MHz           | 15 pF                               | 15 pF |  |  |  |

|          | 20 MHz          | 15 pF                               | 15 pF |  |  |  |

#### Capacitor values are for design guidance only.

These capacitors were tested with the crystals listed below for basic start-up and operation. These values were not optimized.

Different capacitor values may be required to produce acceptable oscillator operation. The user should test the performance of the oscillator over the expected VDD and temperature range for the application.

See the notes following this table for additional information.

|         | Crystals Used:         |  |  |  |  |  |  |  |  |

|---------|------------------------|--|--|--|--|--|--|--|--|

| 32 kHz  | Epson C-001R32.768K-A  |  |  |  |  |  |  |  |  |

| 200 kHz | STD XTL 200.000KHz     |  |  |  |  |  |  |  |  |

| 1 MHz   | ECS ECS-10-13-1        |  |  |  |  |  |  |  |  |

| 4 MHz   | ECS ECS-40-20-1        |  |  |  |  |  |  |  |  |

| 8 MHz   | EPSON CA-301 8.000M-C  |  |  |  |  |  |  |  |  |

| 20 MHz  | EPSON CA-301 20.000M-C |  |  |  |  |  |  |  |  |

- **Note 1:** Higher capacitance increases the stability of oscillator, but also increases the start-up time.

- 2: Since each resonator/crystal has its own characteristics, the user should consult the resonator/crystal manufacturer for appropriate values of external components.

- 3: Rs may be required in HS mode, as well as XT mode, to avoid overdriving crystals with low drive level specification.

- **4:** Always verify oscillator performance over the VDD and temperature range that is expected for the application.

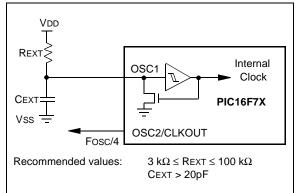

### 12.2.3 RC OSCILLATOR

For timing insensitive applications, the "RC" device option offers additional cost savings. The RC oscillator frequency is a function of the supply voltage, the resistor (REXT) and capacitor (CEXT) values, and the operating temperature. In addition to this, the oscillator frequency will vary from unit to unit due to normal process parameter variation. Furthermore, the difference in lead frame capacitance between package types will also affect the oscillation frequency, especially for low CEXT values. The user also needs to take into account variation due to tolerance of external R and C components used. Figure 12-3 shows how the R/C combination is connected to the PIC16F7X.

### FIGURE 12-3: RC OSCILLATOR MODE

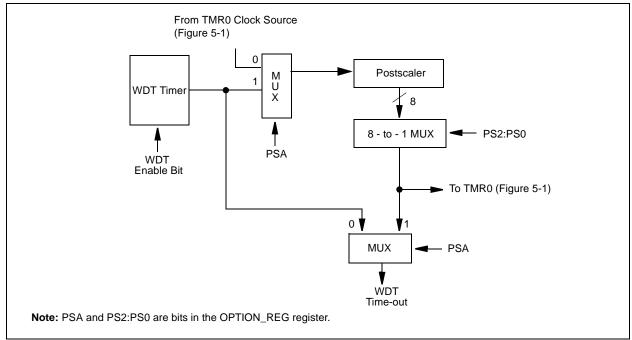

## 12.13 Watchdog Timer (WDT)

The Watchdog Timer is a free running on-chip RC oscillator, which does not require any external components. This RC oscillator is separate from the RC oscillator of the OSC1/CLKIN pin. That means that the WDT will run, even if the clock on the OSC1/CLKIN and OSC2/ CLKOUT pins of the device has been stopped, for example, by execution of a SLEEP instruction.

During normal operation, a WDT time-out generates a device RESET (Watchdog Timer Reset). If the device is in SLEEP mode, a WDT time-out causes the device to wake-up and continue with normal operation (Watchdog Timer Wake-up). The  $\overline{\text{TO}}$  bit in the STATUS register will be cleared upon a Watchdog Timer time-out.

The WDT can be permanently disabled by clearing configuration bit, WDTE (Section 12.1).

WDT time-out period values may be found in the Electrical Specifications section under parameter #31. Values for the WDT prescaler (actually a postscaler, but shared with the Timer0 prescaler) may be assigned using the OPTION\_REG register.

- Note 1: The CLRWDT and SLEEP instructions clear the WDT and the postscaler, if assigned to the WDT, and prevent it from timing out and generating a device RESET condition.

- 2: When a CLRWDT instruction is executed and the prescaler is assigned to the WDT, the prescaler count will be cleared, but the prescaler assignment is not changed.

### FIGURE 12-11: WATCHDOG TIMER BLOCK DIAGRAM

### TABLE 12-7: SUMMARY OF WATCHDOG TIMER REGISTERS

| Address  | Name         | Bit 7 | Bit 6                | Bit 5 | Bit 4 | Bit 3                | Bit 2 | Bit 1 | Bit 0 |

|----------|--------------|-------|----------------------|-------|-------|----------------------|-------|-------|-------|

| 2007h    | Config. bits | (1)   | BODEN <sup>(1)</sup> | _     | CP0   | PWRTE <sup>(1)</sup> | WDTE  | FOSC1 | FOSC0 |

| 81h,181h | OPTION_REG   | RBPU  | INTEDG               | TOCS  | TOSE  | PSA                  | PS2   | PS1   | PS0   |

Legend: Shaded cells are not used by the Watchdog Timer.

Note 1: See Register 12-1 for operation of these bits.

# **15.0 ELECTRICAL CHARACTERISTICS**

### Absolute Maximum Ratings †

| Ambient temperature under bias                                                                                                                                         | 55 to +125°C                          |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------|

| Storage temperature                                                                                                                                                    |                                       |

| Voltage on any pin with respect to Vss (except VDD, MCLR. and RA4)                                                                                                     |                                       |

| Voltage on VDD with respect to Vss                                                                                                                                     |                                       |

| Voltage on MCLR with respect to Vss (Note 2)                                                                                                                           |                                       |

| Voltage on RA4 with respect to Vss                                                                                                                                     |                                       |

| Total power dissipation (Note 1)                                                                                                                                       |                                       |

| Maximum current out of Vss pin                                                                                                                                         |                                       |

| Maximum current into VDD pin                                                                                                                                           |                                       |

| Input clamp current, Iк (Vi < 0 or Vi > VDD)                                                                                                                           |                                       |

| Output clamp current, loк (Vo < 0 or Vo > Voo)                                                                                                                         |                                       |

| Maximum output current sunk by any I/O pin                                                                                                                             |                                       |

| Maximum output current sourced by any I/O pin                                                                                                                          |                                       |

| Maximum current sunk by PORTA, PORTB, and PORTE (combined) (Note 3)                                                                                                    | 200 mA                                |

| Maximum current sourced by PORTA, PORTB, and PORTE (combined) (Note 3)                                                                                                 |                                       |

| Maximum current sunk by PORTC and PORTD (combined) (Note 3)                                                                                                            | 200 mA                                |

| Maximum current sourced by PORTC and PORTD (combined) (Note 3)                                                                                                         |                                       |

| <b>Note 1:</b> Power dissipation is calculated as follows: Pdis = VDD x {IDD - $\sum$ IOH} + $\sum$ {(VDD - V                                                          | $√$ ОН) x IOH} + $\Sigma$ (VOI x IOL) |

| <ol> <li>Voltage spikes at the MCLR pin may cause latchup. A series resistor of greater the to pull MCLR to VDD, rather than tying the pin directly to VDD.</li> </ol> | nan 1 k $\Omega$ should be used       |

3: PORTD and PORTE are not implemented on the PIC16F73/76 devices.

† NOTICE: Stresses above those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress rating only and functional operation of the device at those or any other conditions above those indicated in the operation listings of this specification is not implied. Exposure to maximum rating conditions for extended periods may affect device reliability.

## 15.1 DC Characteristics: PIC16F73/74/76/77 (Industrial, Extended) PIC16LF73/74/76/77 (Industrial) (Continued)

|                                             |               |                                     | Standard Operating Conditions (unless otherwise stated)<br>Operating temperature $-40^{\circ}C \le TA \le +85^{\circ}C$ for industrial |                                                                                                                                                                                                |          |          |                                                                                                                                     |  |  |  |

|---------------------------------------------|---------------|-------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|----------|-------------------------------------------------------------------------------------------------------------------------------------|--|--|--|