Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                                           |

|----------------------------|---------------------------------------------------------------------------|

| Product Status             | Obsolete                                                                  |

| Core Processor             | PIC                                                                       |

| Core Size                  | 8-Bit                                                                     |

| Speed                      | 20MHz                                                                     |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                                         |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                     |

| Number of I/O              | 33                                                                        |

| Program Memory Size        | 7KB (4K x 14)                                                             |

| Program Memory Type        | FLASH                                                                     |

| EEPROM Size                | -                                                                         |

| RAM Size                   | 192 x 8                                                                   |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 5.5V                                                                 |

| Data Converters            | A/D 8x8b                                                                  |

| Oscillator Type            | External                                                                  |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                         |

| Mounting Type              | Surface Mount                                                             |

| Package / Case             | 44-TQFP                                                                   |

| Supplier Device Package    | 44-TQFP (10x10)                                                           |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16lf74t-i-pt |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

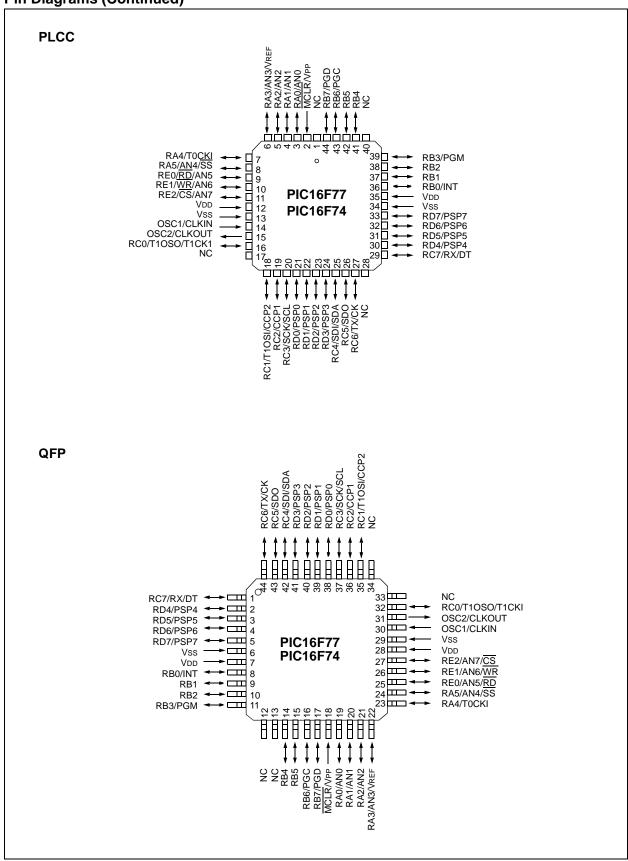

## Pin Diagrams (Continued)

TABLE 1-2: PIC16F73 AND PIC16F76 PINOUT DESCRIPTION (CONTINUED)

| Pin Name              | DIP<br>SSOP<br>SOIC<br>Pin# | MLF<br>Pin# | I/O/P<br>Type | Buffer<br>Type        | Description                                                                                                           |

|-----------------------|-----------------------------|-------------|---------------|-----------------------|-----------------------------------------------------------------------------------------------------------------------|

|                       |                             |             |               |                       | PORTB is a bi-directional I/O port. PORTB can be software                                                             |

|                       |                             |             |               | (0-(1)                | programmed for internal weak pull-up on all inputs.                                                                   |

| RB0/INT               | 21                          | 18          | I/O           | TTL/ST <sup>(1)</sup> | Digital I/O                                                                                                           |

| RB0<br>INT            |                             |             | I/O           |                       | Digital I/O. External interrupt.                                                                                      |

| RB1                   | 22                          | 19          | I/O           | TTL                   | Digital I/O.                                                                                                          |

| RB2                   | 23                          | 20          | I/O           | TTL                   | Digital I/O.                                                                                                          |

| RB3/PGM               | 24                          | 21          | 1/0           | TTL                   | Digital 1/O.                                                                                                          |

| RB3                   | 24                          | 21          | I/O           | '''                   | Digital I/O.                                                                                                          |

| PGM                   |                             |             | I/O           |                       | Low voltage ICSP programming enable pin.                                                                              |

| RB4                   | 25                          | 22          | I/O           | TTL                   | Digital I/O.                                                                                                          |

| RB5                   | 26                          | 23          | I/O           | TTL                   | Digital I/O.                                                                                                          |

| RB6/PGC               | 27                          | 24          |               | TTL/ST <sup>(2)</sup> | - 19 5.                                                                                                               |

| RB6                   |                             |             | I/O           | ,                     | Digital I/O.                                                                                                          |

| PGC                   |                             |             | I/O           |                       | In-Circuit Debugger and ICSP programming clock.                                                                       |

| RB7/PGD               | 28                          | 25          |               | TTL/ST <sup>(2)</sup> |                                                                                                                       |

| RB7                   |                             |             | I/O           |                       | Digital I/O.                                                                                                          |

| PGD                   |                             |             | I/O           |                       | In-Circuit Debugger and ICSP programming data.                                                                        |

|                       |                             |             |               |                       | PORTC is a bi-directional I/O port.                                                                                   |

| RC0/T1OSO/T1CKI       | 11                          | 8           |               | ST                    |                                                                                                                       |

| RC0                   |                             |             | I/O           |                       | Digital I/O.                                                                                                          |

| T1OSO<br>T1CKI        |                             |             | 0             |                       | Timer1 oscillator output.                                                                                             |

|                       | 40                          | 0           | '             | СТ                    | Timer1 external clock input.                                                                                          |

| RC1/T1OSI/CCP2<br>RC1 | 12                          | 9           | I/O           | ST                    | Digital I/O.                                                                                                          |

| T1OSI                 |                             |             | ı,O           |                       | Timer1 oscillator input.                                                                                              |

| CCP2                  |                             |             | I/O           |                       | Capture2 input, Compare2 output, PWM2 output.                                                                         |

| RC2/CCP1              | 13                          | 10          |               | ST                    |                                                                                                                       |

| RC2                   |                             |             | I/O           |                       | Digital I/O.                                                                                                          |

| CCP1                  |                             |             | I/O           |                       | Capture1 input/Compare1 output/PWM1 output.                                                                           |

| RC3/SCK/SCL           | 14                          | 11          |               | ST                    |                                                                                                                       |

| RC3                   |                             |             | I/O           |                       | Digital I/O.                                                                                                          |

| SCK<br>SCL            |                             |             | I/O<br>I/O    |                       | Synchronous serial clock input/output for SPI mode.  Synchronous serial clock input/output for I <sup>2</sup> C mode. |

| RC4/SDI/SDA           | 15                          | 12          | 1/0           | ST                    | Synchronous serial clock inpulvoutput for 1 C mode.                                                                   |

| RC4/3DI/3DA<br>RC4    | 15                          | 12          | I/O           | 31                    | Digital I/O.                                                                                                          |

| SDI                   |                             |             | ı, C          |                       | SPI data in.                                                                                                          |

| SDA                   |                             |             | I/O           |                       | I <sup>2</sup> C data I/O.                                                                                            |

| RC5/SDO               | 16                          | 13          |               | ST                    |                                                                                                                       |

| RC5                   |                             |             | I/O           |                       | Digital I/O.                                                                                                          |

| SDO                   |                             |             | 0             |                       | SPI data out.                                                                                                         |

| RC6/TX/CK             | 17                          | 14          |               | ST                    |                                                                                                                       |

| RC6                   |                             |             | 1/0           |                       | Digital I/O.                                                                                                          |

| TX<br>CK              |                             |             | 0<br>I/O      |                       | USART asynchronous transmit. USART 1 synchronous clock.                                                               |

| RC7/RX/DT             | 18                          | 15          | 1,0           | ST                    | CONTRI I Synonionous clock.                                                                                           |

| RC7/RX/DT<br>RC7      | 10                          | 10          | I/O           | 31                    | Digital I/O.                                                                                                          |

| RX                    |                             |             | ı, O          |                       | USART asynchronous receive.                                                                                           |

| DT                    |                             |             | I/O           |                       | USART synchronous data.                                                                                               |

| Vss                   | 8, 19                       | 5, 16       | Р             | _                     | Ground reference for logic and I/O pins.                                                                              |

|                       |                             |             |               |                       |                                                                                                                       |

Legend: I = input

O = output

I/O = input/output

P = power

— = Not used

t used TTL = TTL input

ST = Schmitt Trigger input

Note 1: This buffer is a Schmitt Trigger input when configured as the external interrupt.

2: This buffer is a Schmitt Trigger input when used in Serial Programming mode.

3: This buffer is a Schmitt Trigger input when configured in RC Oscillator mode and a CMOS input otherwise.

TABLE 1-3: PIC16F74 AND PIC16F77 PINOUT DESCRIPTION (CONTINUED)

| Pin Name          | DIP<br>Pin# | PLCC<br>Pin# | QFP<br>Pin# | I/O/P<br>Type | Buffer<br>Type        | Description                                                                                                          |

|-------------------|-------------|--------------|-------------|---------------|-----------------------|----------------------------------------------------------------------------------------------------------------------|

|                   |             |              |             |               |                       | PORTB is a bi-directional I/O port. PORTB can be software programmed for internal weak pull-up on all inputs.        |

| RB0/INT           | 33          | 36           | 8           |               | TTL/ST <sup>(1)</sup> |                                                                                                                      |

| RB0<br>INT        |             |              |             | I/O<br>I      |                       | Digital I/O. External interrupt.                                                                                     |

| RB1               | 34          | 37           | 9           | I/O           | TTL                   | Digital I/O.                                                                                                         |

| RB2               | 35          | 38           | 10          | I/O           | TTL                   | Digital I/O.                                                                                                         |

| RB3/PGM           | 36          | 39           | 11          |               | TTL                   |                                                                                                                      |

| RB3               |             |              |             | I/O           |                       | Digital I/O.                                                                                                         |

| PGM               |             |              |             | I/O           |                       | Low voltage ICSP programming enable pin.                                                                             |

| RB4               | 37          | 41           | 14          | I/O           | TTL                   | Digital I/O.                                                                                                         |

| RB5               | 38          | 42           | 15          | I/O           | TTL                   | Digital I/O.                                                                                                         |

| RB6/PGC           | 39          | 43           | 16          |               | TTL/ST <sup>(2)</sup> |                                                                                                                      |

| RB6               |             |              |             | I/O           |                       | Digital I/O.                                                                                                         |

| PGC               |             |              |             | I/O           | 4-1                   | In-Circuit Debugger and ICSP programming clock.                                                                      |

| RB7/PGD           | 40          | 44           | 17          |               | TTL/ST <sup>(2)</sup> |                                                                                                                      |

| RB7               |             |              |             | I/O           |                       | Digital I/O.                                                                                                         |

| PGD               |             |              |             | I/O           |                       | In-Circuit Debugger and ICSP programming data.                                                                       |

|                   |             |              |             |               |                       | PORTC is a bi-directional I/O port.                                                                                  |

| RC0/T1OSO/T1CKI   | 15          | 16           | 32          |               | ST                    | 5: :: 11/0                                                                                                           |

| RC0<br>T1OSO      |             |              |             | I/O<br>O      |                       | Digital I/O.                                                                                                         |

| T1CKI             |             |              |             | ı             |                       | Timer1 oscillator output. Timer1 external clock input.                                                               |

| RC1/T1OSI/CCP2    | 16          | 18           | 35          | '             | ST                    | Time i external desix input.                                                                                         |

| RC1               | 10          | '0           | 33          | I/O           | 01                    | Digital I/O.                                                                                                         |

| T1OSI             |             |              |             | I             |                       | Timer1 oscillator input.                                                                                             |

| CCP2              |             |              |             | I/O           |                       | Capture2 input, Compare2 output, PWM2 output.                                                                        |

| RC2/CCP1          | 17          | 19           | 36          |               | ST                    |                                                                                                                      |

| RC2               |             |              |             | I/O           |                       | Digital I/O.                                                                                                         |

| CCP1              |             |              |             | I/O           |                       | Capture1 input/Compare1 output/PWM1 output                                                                           |

| RC3/SCK/SCL       | 18          | 20           | 37          |               | ST                    | 51.1.110                                                                                                             |

| RC3<br>SCK        |             |              |             | I/O<br>I/O    |                       | Digital I/O                                                                                                          |

| SCL               |             |              |             | 1/0           |                       | Synchronous serial clock input/output for SPI mode. Synchronous serial clock input/output for I <sup>2</sup> C mode. |

| RC4/SDI/SDA       | 23          | 25           | 42          | 1/0           | ST                    | Cyricinolous schal clock inputoutput for 1 o mode.                                                                   |

| RC4               | 23          | 20           | 42          | I/O           | 31                    | Digital I/O.                                                                                                         |

| SDI               |             |              |             | ı, ü          |                       | SPI data in.                                                                                                         |

| SDA               |             |              |             | I/O           |                       | I <sup>2</sup> C data I/O.                                                                                           |

| RC5/SDO           | 24          | 26           | 43          |               | ST                    |                                                                                                                      |

| RC5               |             |              |             | I/O           |                       | Digital I/O.                                                                                                         |

| SDO               |             |              |             | 0             |                       | SPI data out.                                                                                                        |

| RC6/TX/CK         | 25          | 27           | 44          |               | ST                    |                                                                                                                      |

| RC6               |             |              |             | I/O           |                       | Digital I/O.                                                                                                         |

| TX<br>CK          |             |              |             | O<br>I/O      |                       | USART asynchronous transmit.                                                                                         |

|                   | 20          | 20           |             | 1/0           | C.T.                  | USART 1 synchronous clock.                                                                                           |

| RC7/RX/DT<br>RC7  | 26          | 29           | 1           | I/O           | ST                    | Digital I/O.                                                                                                         |

| RX<br>RX          |             |              |             | 1,0           |                       | USART asynchronous receive.                                                                                          |

| DT                |             |              |             | I/O           |                       | USART synchronous data.                                                                                              |

| Legend: L = input |             | 0 - 0        | L           |               | ) – innut/outni       | 1                                                                                                                    |

Legend: I = input O

O = output TTL = TTL input I/O = input/output

P = power

ST = Schmitt Trigger input

Note 1: This buffer is a Schmitt Trigger input when configured as an external interrupt.

<sup>2:</sup> This buffer is a Schmitt Trigger input when used in Serial Programming mode.

<sup>3:</sup> This buffer is a Schmitt Trigger input when configured as general purpose I/O and a TTL input when used in the Parallel Slave Port mode (for interfacing to a microprocessor bus).

<sup>4:</sup> This buffer is a Schmitt Trigger input when configured in RC Oscillator mode and a CMOS input otherwise.

# 3.3 Reading the FLASH Program Memory

A program memory location may be read by writing two bytes of the address to the PMADR and PMADRH registers and then setting control bit RD (PMCON1<0>). Once the read control bit is set, the microcontroller will use the next two instruction cycles to read the data. The data is available in the PMDATA and PMDATH registers after the second NOP instruction. Therefore, it can be read as two bytes in the following instructions. The PMDATA and PMDATH registers will hold this value until the next read operation.

## 3.4 Operation During Code Protect

FLASH program memory has its own code protect mechanism. External Read and Write operations by programmers are disabled if this mechanism is enabled.

The microcontroller can read and execute instructions out of the internal FLASH program memory, regardless of the state of the code protect configuration bits.

## **EXAMPLE 3-1: FLASH PROGRAM READ**

```

STATUS, RP1

; Bank 2

BCF

STATUS, RPO

MOVF

ADDRH, W

MOVWF

PMADRH

; MSByte of Program Address to read

MOVF

ADDRL, W

;

MOVWF

PMADR

; LSByte of Program Address to read

BSF

STATUS, RPO ; Bank 3 Required

Required

BSF

PMCON1, RD

; EEPROM Read Sequence

; memory is read in the next two cycles after BSF PMCON1,RD

Sequence

NOP

NOP

BCF

STATUS, RPO

; Bank 2

; W = LSByte of Program PMDATA

MOVF

PMDATA, W

MOVF

PMDATH, W

; W = MSByte of Program PMDATA

```

## TABLE 3-1: REGISTERS ASSOCIATED WITH PROGRAM FLASH

| Address | Name   | Bit 7     | Bit 6       | Bit 5    | Bit 4      | Bit 3     | Bit 2     | Bit 1 | Bit 0 | Value on:<br>POR,<br>BOR | Value on<br>all other<br>RESETS |

|---------|--------|-----------|-------------|----------|------------|-----------|-----------|-------|-------|--------------------------|---------------------------------|

| 10Dh    | PMADR  | Address F | Register Lo | ow Byte  |            |           |           |       |       | xxxx xxxx                | uuuu uuuu                       |

| 10Fh    | PMADRH | _         | _           | _        | Address F  | xxxx xxxx | uuuu uuuu |       |       |                          |                                 |

| 10Ch    | PMDATA | Data Reg  | ister Low I | Byte     |            |           |           |       |       | xxxx xxxx                | uuuu uuuu                       |

| 10Eh    | PMDATH | _         | _           | Data Reg | ister High | xxxx xxxx | uuuu uuuu |       |       |                          |                                 |

| 18Ch    | PMCON1 | (1)       | _           | _        | _          | _         | _         | _     | RD    | 10                       | 10                              |

Legend: x = unknown, u = unchanged, r = reserved, - = unimplemented read as '0'. Shaded cells are not used during FLASH access. **Note 1:** This bit always reads as a '1'.

## PIC16F7X

TABLE 4-3: PORTB FUNCTIONS

| Name    | Bit# | Buffer                | Function                                                                                                            |

|---------|------|-----------------------|---------------------------------------------------------------------------------------------------------------------|

| RB0/INT | bit0 | TTL/ST <sup>(1)</sup> | Input/output pin or external interrupt input. Internal software programmable weak pull-up.                          |

| RB1     | bit1 | TTL                   | Input/output pin. Internal software programmable weak pull-up.                                                      |

| RB2     | bit2 | TTL                   | Input/output pin. Internal software programmable weak pull-up.                                                      |

| RB3     | bit3 | TTL                   | Input/output pin. Internal software programmable weak pull-up.                                                      |

| RB4     | bit4 | TTL                   | Input/output pin (with interrupt-on-change). Internal software programmable weak pull-up.                           |

| RB5     | bit5 | TTL                   | Input/output pin (with interrupt-on-change). Internal software programmable weak pull-up.                           |

| RB6     | bit6 | TTL/ST <sup>(2)</sup> | Input/output pin (with interrupt-on-change). Internal software programmable weak pull-up. Serial programming clock. |

| RB7     | bit7 | TTL/ST <sup>(2)</sup> | Input/output pin (with interrupt-on-change). Internal software programmable weak pull-up. Serial programming data.  |

Legend: TTL = TTL input, ST = Schmitt Trigger input

Note 1: This buffer is a Schmitt Trigger input when configured as the external interrupt.

2: This buffer is a Schmitt Trigger input when used in Serial Programming mode.

TABLE 4-4: SUMMARY OF REGISTERS ASSOCIATED WITH PORTB

| Address   | Name       | Bit 7   | Bit 6          | Bit 5     | Bit 4     | Bit 3 | Bit 2 | Bit 1 | Bit 0 | Value on:<br>POR,<br>BOR | Value on<br>all other<br>RESETS |

|-----------|------------|---------|----------------|-----------|-----------|-------|-------|-------|-------|--------------------------|---------------------------------|

| 06h, 106h | PORTB      | RB7     | RB6            | RB5       | RB4       | RB3   | RB2   | RB1   | RB0   | xxxx xxxx                | uuuu uuuu                       |

| 86h, 186h | TRISB      | PORTB I | Data Direction | 1111 1111 | 1111 1111 |       |       |       |       |                          |                                 |

| 81h, 181h | OPTION_REG | RBPU    | INTEDG         | T0CS      | TOSE      | PSA   | PS2   | PS1   | PS0   | 1111 1111                | 1111 1111                       |

Legend: x = unknown, u = unchanged. Shaded cells are not used by PORTB.

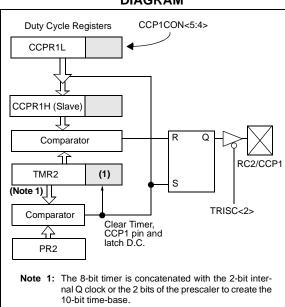

## 8.5 PWM Mode (PWM)

In Pulse Width Modulation mode, the CCPx pin produces up to a 10-bit resolution PWM output. Since the CCP1 pin is multiplexed with the PORTC data latch, the TRISC<2> bit must be cleared to make the CCP1 pin an output.

Note: Clearing the CCP1CON register will force the CCP1 PWM output latch to the default low level. This is not the PORTC I/O data latch.

Figure 8-3 shows a simplified block diagram of the CCP module in PWM mode.

For a step-by-step procedure on how to set up the CCP module for PWM operation, see Section 8.5.3.

## FIGURE 8-3: SIMPLIFIED PWM BLOCK DIAGRAM

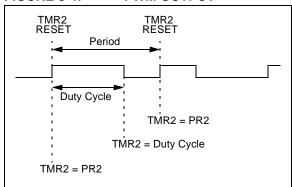

A PWM output (Figure 8-4) has a time-base (period) and a time that the output stays high (duty cycle). The frequency of the PWM is the inverse of the period (1/period).

FIGURE 8-4: PWM OUTPUT

#### 8.5.1 PWM PERIOD

The PWM period is specified by writing to the PR2 register. The PWM period can be calculated using the following formula:

PWM period =

$$[(PR2) + 1] \cdot 4 \cdot TOSC \cdot (TMR2 \text{ prescale value})$$

PWM frequency is defined as 1 / [PWM period].

When TMR2 is equal to PR2, the following three events occur on the next increment cycle:

- · TMR2 is cleared

- The CCP1 pin is set (exception: if PWM duty cycle = 0%, the CCP1 pin will not be set)

- The PWM duty cycle is latched from CCPR1L into CCPR1H

Note: The Timer2 postscaler (see Section 8.3) is not used in the determination of the PWM frequency. The postscaler could be used to have a servo update rate at a different frequency than the PWM output.

#### 8.5.2 PWM DUTY CYCLE

The PWM duty cycle is specified by writing to the CCPR1L register and to the CCP1CON<5:4> bits. Up to 10-bit resolution is available. The CCPR1L contains the eight MSbs and the CCP1CON<5:4> contains the two LSbs. This 10-bit value is represented by CCPR1L:CCP1CON<5:4>. The following equation is used to calculate the PWM duty cycle in time:

CCPR1L and CCP1CON<5:4> can be written to at any time, but the duty cycle value is not latched into CCPR1H until after a match between PR2 and TMR2 occurs (i.e., the period is complete). In PWM mode, CCPR1H is a read only register.

The CCPR1H register and a 2-bit internal latch are used to double buffer the PWM duty cycle. This double buffering is essential for glitchless PWM operation.

When the CCPR1H and 2-bit latch match TMR2, concatenated with an internal 2-bit Q clock or 2 bits of the TMR2 prescaler, the CCP1 pin is cleared.

The maximum PWM resolution (bits) for a given PWM frequency is given by the formula:

Resolution

$$=$$

$\frac{\log(\frac{FOSC}{FPWM})}{\log(2)}$  bits

**Note:** If the PWM duty cycle value is longer than the PWM period, the CCP1 pin will not be cleared.

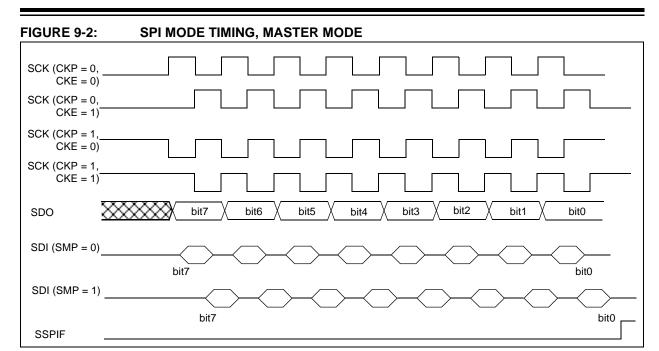

## REGISTER 9-1: SSPSTAT: SYNC SERIAL PORT STATUS REGISTER (ADDRESS 94h)

| R/W-0 | R/W-0 | R-0              | R-0 | R-0 | R-0 | R-0 | R-0 |

|-------|-------|------------------|-----|-----|-----|-----|-----|

| SMP   | CKE   | $D/\overline{A}$ | Р   | S   | R/W | UA  | BF  |

|       |       |                  |     |     |     |     |     |

bit 7 bit 0

bit 7 SMP: SPI Data Input Sample Phase bit

#### SPI Master mode:

- 1 = Input data sampled at end of data output time

- 0 = Input data sampled at middle of data output time (Microwire®)

## SPI Slave mode:

SMP must be cleared when SPI is used in Slave mode

#### I<sup>2</sup>C mode:

This bit must be maintained clear

bit 6 **CKE**: SPI Clock Edge Select bit (Figure 9-2, Figure 9-3, and Figure 9-4)

### SPI mode, CKP = 0:

- 1 = Data transmitted on rising edge of SCK (Microwire<sup>®</sup> alternate)

- 0 = Data transmitted on falling edge of SCK

#### SPI mode, CKP = 1:

- 1 = Data transmitted on falling edge of SCK (Microwire<sup>®</sup> default)

- 0 = Data transmitted on rising edge of SCK

#### I<sup>2</sup>C mode:

This bit must be maintained clear

- bit 5 **D/A**: Data/Address bit (I<sup>2</sup>C mode only)

- 1 = Indicates that the last byte received or transmitted was data

- 0 = Indicates that the last byte received or transmitted was address

- bit 4 **P**: STOP bit (I<sup>2</sup>C mode only)

This bit is cleared when the SSP module is disabled, or when the START bit is detected last. SSPEN is cleared.

- 1 = Indicates that a STOP bit has been detected last (this bit is '0' on RESET)

- 0 = STOP bit was not detected last

- bit 3 **S**: START bit (I<sup>2</sup>C mode only)

This bit is cleared when the SSP module is disabled, or when the STOP bit is detected last. SSPEN is cleared.

- 1 = Indicates that a START bit has been detected last (this bit is '0' on RESET)

- 0 = START bit was not detected last

- bit 2 **R/W**: Read/Write bit Information (I<sup>2</sup>C mode only)

This bit holds the R/W bit information following the last address match. This bit is only valid from the address match to the next START bit, STOP bit, or ACK bit.

- 1 = Read

- 0 = Write

- bit 1 **UA**: Update Address bit (10-bit I<sup>2</sup>C mode only)

- 1 = Indicates that the user needs to update the address in the SSPADD register

- 0 = Address does not need to be updated

- bit 0 **BF**: Buffer Full Status bit

## Receive (SPI and I<sup>2</sup>C modes):

- 1 = Receive complete, SSPBUF is full

- 0 = Receive not complete, SSPBUF is empty

#### Transmit (I<sup>2</sup>C mode only):

- 1 = Transmit in progress, SSPBUF is full

- 0 = Transmit complete, SSPBUF is empty

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0' - n = Value at POR reset '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

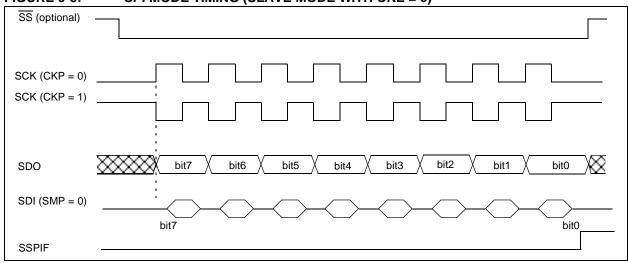

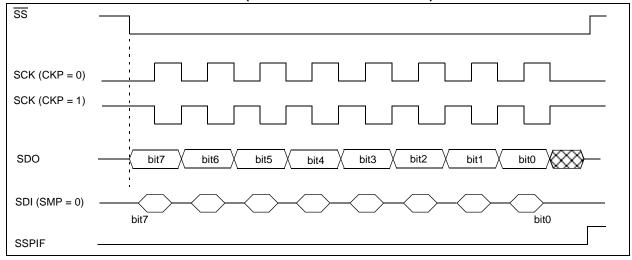

## FIGURE 9-4: SPI MODE TIMING (SLAVE MODE WITH CKE = 1)

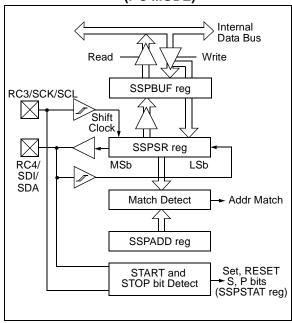

## 9.3 SSP I<sup>2</sup>C Operation

The SSP module in I<sup>2</sup>C mode, fully implements all slave functions, except general call support, and provides interrupts on START and STOP bits in hardware to facilitate firmware implementations of the master functions. The SSP module implements the standard mode specifications as well as 7-bit and 10-bit addressing.

Two pins are used for data transfer. These are the RC3/SCK/SCL pin, which is the clock (SCL), and the RC4/SDI/SDA pin, which is the data (SDA). The user must configure these pins as inputs or outputs through the TRISC<4:3> bits.

The SSP module functions are enabled by setting SSP enable bit SSPEN (SSPCON<5>).

FIGURE 9-5: SSP BLOCK DIAGRAM (1<sup>2</sup>C MODE)

The SSP module has five registers for I<sup>2</sup>C operation. These are the:

- SSP Control Register (SSPCON)

- SSP Status Register (SSPSTAT)

- Serial Receive/Transmit Buffer (SSPBUF)

- · SSP Shift Register (SSPSR) Not directly accessible

- SSP Address Register (SSPADD)

The SSPCON register allows control of the I<sup>2</sup>C operation. Four mode selection bits (SSPCON<3:0>) allow one of the following I<sup>2</sup>C modes to be selected:

- I<sup>2</sup>C Slave mode (7-bit address)

- I<sup>2</sup>C Slave mode (10-bit address)

- I<sup>2</sup>C Slave mode (7-bit address), with START and STOP bit interrupts enabled to support Firmware Master mode

- I<sup>2</sup>C Slave mode (10-bit address), with START and STOP bit interrupts enabled to support Firmware Master mode

- I<sup>2</sup>C START and STOP bit interrupts enabled to support Firmware Master mode, Slave is IDLE

Selection of any I<sup>2</sup>C mode with the SSPEN bit set, forces the SCL and SDA pins to be open drain, provided these pins are programmed to inputs by setting the appropriate TRISC bits. Pull-up resistors must be provided externally to the SCL and SDA pins for proper operation of the I<sup>2</sup>C module.

Additional information on SSP I<sup>2</sup>C operation can be found in the PICmicro™ Mid-Range MCU Family Reference Manual (DS33023A).

#### 9.3.1 SLAVE MODE

In Slave mode, the SCL and SDA pins must be configured as inputs (TRISC<4:3> set). The SSP module will override the input state with the output data when required (slave-transmitter).

When an address is matched, or the data transfer after an address match is received, the hardware automatically will generate the Acknowledge (ACK) pulse, and then load the SSPBUF register with the received value currently in the SSPSR register.

There are certain conditions that will cause the SSP module not to give this  $\overline{ACK}$  pulse. They include (either or both):

- The buffer full bit BF (SSPSTAT<0>) was set before the transfer was received.

- b) The overflow bit SSPOV (SSPCON<6>) was set before the transfer was received.

In this case, the SSPSR register value is not loaded into the SSPBUF, but bit SSPIF (PIR1<3>) is set. Table 9-2 shows what happens when a data transfer byte is received, given the status of bits BF and SSPOV. The shaded cells show the condition where user software did not properly clear the overflow condition. Flag bit BF is cleared by reading the SSPBUF register, while bit SSPOV is cleared through software.

The SCL clock input must have a minimum high and low for proper operation. The high and low times of the  $I^2C$  specification, as well as the requirements of the SSP module, are shown in timing parameter #100 and parameter #101.

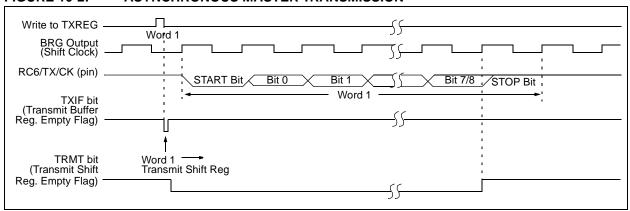

Steps to follow when setting up an Asynchronous Transmission:

- 1. Initialize the SPBRG register for the appropriate baud rate. If a high speed baud rate is desired, set bit BRGH (Section 10.1).

- Enable the asynchronous serial port by clearing bit SYNC and setting bit SPEN.

- 3. If interrupts are desired, then set enable bit TXIE.

- If 9-bit transmission is desired, then set transmit bit TX9.

- Enable the transmission by setting bit TXEN, which will also set bit TXIF.

- If 9-bit transmission is selected, the ninth bit should be loaded in bit TX9D.

- 7. Load data to the TXREG register (starts transmission).

- If using interrupts, ensure that GIE and PEIE in the INTCON register are set.

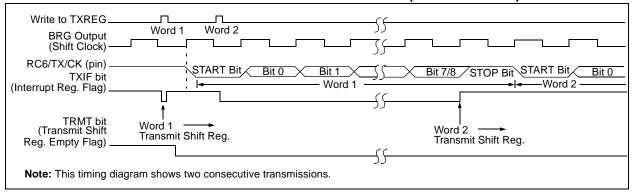

## FIGURE 10-2: ASYNCHRONOUS MASTER TRANSMISSION

## FIGURE 10-3: ASYNCHRONOUS MASTER TRANSMISSION (BACK TO BACK)

## TABLE 10-5: REGISTERS ASSOCIATED WITH ASYNCHRONOUS TRANSMISSION

| Address                | Name   | Bit 7                | Bit 6     | Bit 5   | Bit 4 | Bit 3   | Bit 2  | Bit 1  | Bit 0  | Value or<br>POR,<br>BOR | - , |         | POR, |  | on<br>er<br>ГS |

|------------------------|--------|----------------------|-----------|---------|-------|---------|--------|--------|--------|-------------------------|-----|---------|------|--|----------------|

| 0Bh, 8Bh,<br>10Bh,18Bh | INTCON | GIE                  | PEIE      | TMR0IE  | INTE  | RBIE    | TMR0IF | INTF   | RBIF   | 0000 00                 | Эx  | 0000 00 | 00u  |  |                |

| 0Ch                    | PIR1   | PSPIF <sup>(1)</sup> | ADIF      | RCIF    | TXIF  | SSPIF   | CCP1IF | TMR2IF | TMR1IF | 0000 00                 | 00  | 0000 00 | 000  |  |                |

| 18h                    | RCSTA  | SPEN                 | RX9       | SREN    | CREN  | _       | FERR   | OERR   | RX9D   | 0000 -0                 | Οx  | 0000 -0 | 00x  |  |                |

| 19h                    | TXREG  | USART Tra            | ansmit Re | egister |       |         |        |        |        | 0000 00                 | 0.0 | 0000 00 | 000  |  |                |

| 8Ch                    | PIE1   | PSPIE <sup>(1)</sup> | ADIE      | RCIE    | TXIE  | SSPIE   | CCP1IE | TMR2IE | TMR1IE | 0000 00                 | 0.0 | 0000 00 | 000  |  |                |

| 98h                    | TXSTA  | CSRC                 | TX9       | TXEN    | SYNC  | _       | BRGH   | TRMT   | TX9D   | 0000 -0                 | 10  | 0000 -0 | 010  |  |                |

| 99h                    | SPBRG  | Baud Rate            | Generate  | 0000 00 | 00    | 0000 00 | 000    |        |        |                         |     |         |      |  |                |

Legend: x = unknown, - = unimplemented locations read as '0'. Shaded cells are not used for asynchronous transmission.

Note 1: Bits PSPIE and PSPIF are reserved on the PIC16F73/76; always maintain these bits clear.

## 10.2.2 USART ASYNCHRONOUS RECEIVER

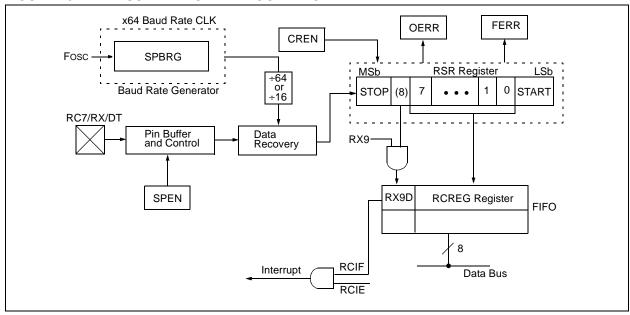

The receiver block diagram is shown in Figure 10-4. The data is received on the RC7/RX/DT pin and drives the data recovery block. The data recovery block is actually a high speed shifter operating at x16 times the baud rate, whereas the main receive serial shifter operates at the bit rate, or at Fosc.

Once Asynchronous mode is selected, reception is enabled by setting bit CREN (RCSTA<4>).

The heart of the receiver is the receive (serial) shift register (RSR). After sampling the STOP bit, the received data in the RSR is transferred to the RCREG register (if it is empty). If the transfer is complete, flag bit RCIF (PIR1<5>) is set. The actual interrupt can be enabled/disabled by setting/clearing enable bit RCIE (PIE1<5>). Flag bit RCIF is a read only bit which is cleared by the hardware. It is cleared when the RCREG register has been read and is empty. The RCREG is a double buffered register (i.e., it is a two deep FIFO). It

is possible for two bytes of data to be received and transferred to the RCREG FIFO and a third byte to begin shifting to the RSR register. On the detection of the STOP bit of the third byte, if the RCREG register is still full, the overrun error bit OERR (RCSTA<1>) will be set. The word in the RSR will be lost. The RCREG register can be read twice to retrieve the two bytes in the FIFO. Overrun bit OERR has to be cleared in software. This is done by resetting the receive logic (CREN is cleared and then set). If bit OERR is set, transfers from the RSR register to the RCREG register are inhibited and no further data will be received, therefore, it is essential to clear error bit OERR if it is set. Framing error bit FERR (RCSTA<2>) is set if a STOP bit is detected as clear. Bit FERR and the 9th receive bit are buffered the same way as the receive data. Reading the RCREG will load bits RX9D and FERR with new values, therefore, it is essential for the user to read the RCSTA register before reading RCREG register, in order not to lose the old FERR and RX9D information.

FIGURE 10-4: USART RECEIVE BLOCK DIAGRAM

# PIC16F7X

NOTES:

| CALL             | Call Subroutine                                                                                                                                                                                             | CLRWDT           | Clear Watchdog Timer                                                                                                                           |

|------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [label] CALL k                                                                                                                                                                                              | Syntax:          | [label] CLRWDT                                                                                                                                 |

| Operands:        | $0 \leq k \leq 2047$                                                                                                                                                                                        | Operands:        | None                                                                                                                                           |

| Operation:       | (PC)+ 1 $\rightarrow$ TOS,<br>k $\rightarrow$ PC<10:0>,<br>(PCLATH<4:3>) $\rightarrow$ PC<12:11>                                                                                                            | Operation:       | 00h → WDT<br>0 → WDT prescaler,<br>1 → $\overline{TO}$                                                                                         |

| Status Affected: | None                                                                                                                                                                                                        |                  | 1 → PD<br>————————————————————————————————————                                                                                                 |

| Description:     | Call Subroutine. First, return                                                                                                                                                                              | Status Affected: | TO, PD                                                                                                                                         |

|                  | address (PC+1) is pushed onto<br>the stack. The eleven-bit immedi-<br>ate address is loaded into PC bits<br><10:0>. The upper bits of the PC<br>are loaded from PCLATH. CALL is<br>a two-cycle instruction. | Description:     | CLRWDT instruction resets the Watchdog Timer. It also resets the prescaler of the WDT. Status bits TO and PD are set.                          |

| CLRF             | Clear f                                                                                                                                                                                                     | COMF             | Complement f                                                                                                                                   |

| Syntax:          | [label] CLRF f                                                                                                                                                                                              | Syntax:          | [ label ] COMF f,d                                                                                                                             |

| Operands:        | $0 \le f \le 127$                                                                                                                                                                                           | Operands:        | 0 ≤ f ≤ 127                                                                                                                                    |

| Operation:       | $00h \rightarrow (f)$                                                                                                                                                                                       |                  | $d \in [0,1]$                                                                                                                                  |

|                  | $1 \rightarrow Z$                                                                                                                                                                                           | Operation:       | $(\bar{f}) \rightarrow (destination)$                                                                                                          |

| Status Affected: | Z                                                                                                                                                                                                           | Status Affected: | Z                                                                                                                                              |

| Description:     | The contents of register 'f' are cleared and the Z bit is set.                                                                                                                                              | Description:     | The contents of register 'f' are complemented. If 'd' is 0, the result is stored in W. If 'd' is 1, the result is stored back in register 'f'. |

| CLRW             | Clear W                                                                                                                                                                                                     | DECF             | Decrement f                                                                                                                                    |

| Syntax:          | [ label ] CLRW                                                                                                                                                                                              | Syntax:          | [ label ] DECF f,d                                                                                                                             |

| Operands:        | None                                                                                                                                                                                                        | Operands:        | $0 \le f \le 127$                                                                                                                              |

| Operation:       | $00h \rightarrow (W)$                                                                                                                                                                                       |                  | d ∈ [0,1]                                                                                                                                      |

|                  | $1 \rightarrow Z$                                                                                                                                                                                           | Operation:       | (f) - 1 $\rightarrow$ (destination)                                                                                                            |

| Status Affected: | Z                                                                                                                                                                                                           | Status Affected: | Z                                                                                                                                              |

| Description:     | W register is cleared. Zero bit (Z) is set.                                                                                                                                                                 | Description:     | Decrement register 'f'. If 'd' is 0, the result is stored in the W register. If 'd' is 1, the result is                                        |

stored back in register 'f'.

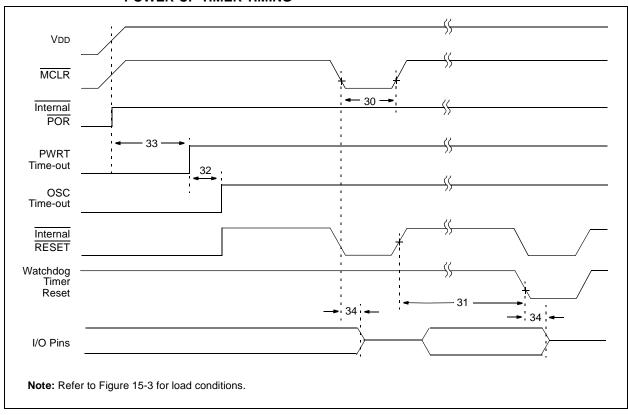

FIGURE 15-6: RESET, WATCHDOG TIMER, OSCILLATOR START-UP TIMER AND POWER-UP TIMER TIMING

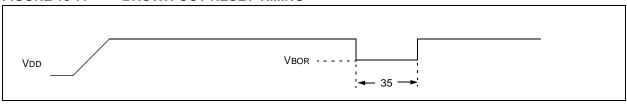

FIGURE 15-7: BROWN-OUT RESET TIMING

TABLE 15-3: RESET, WATCHDOG TIMER, OSCILLATOR START-UP TIMER, POWER-UP TIMER, AND BROWN-OUT RESET REQUIREMENTS

| Parameter<br>No. | Sym   | Characteristic                                         | Min | Typ†      | Max | Units | Conditions                                        |

|------------------|-------|--------------------------------------------------------|-----|-----------|-----|-------|---------------------------------------------------|

| 30               | TmcL  | MCLR Pulse Width (low)                                 | 2   | _         | _   | μs    | VDD = 5V, -40°C to +85°C                          |

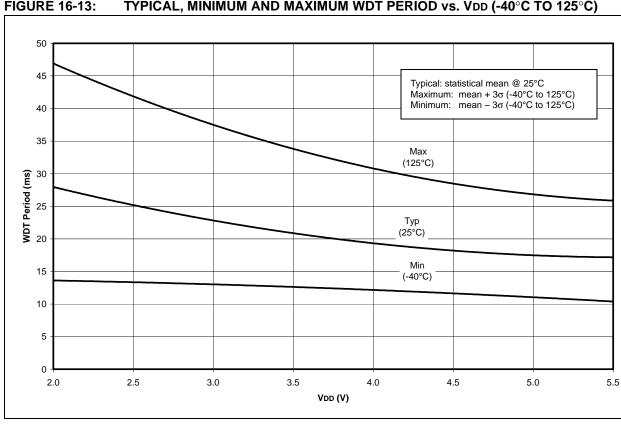

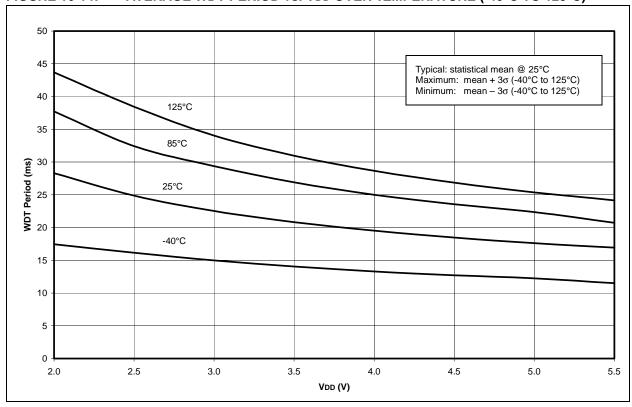

| 31*              | TWDT  | Watchdog Timer Time-out Period (No Prescaler)          | 7   | 18        | 33  | ms    | VDD = 5V, -40°C to +85°C                          |

| 32               | Tost  | Oscillation Start-up Timer Period                      | _   | 1024 Tosc | _   | _     | Tosc = OSC1 period                                |

| 33*              | TPWRT | Power-up Timer Period                                  | 28  | 72        | 132 | ms    | $VDD = 5V, -40^{\circ}C \text{ to } +85^{\circ}C$ |

| 34               | Tıoz  | I/O Hi-Impedance from MCLR Low or Watchdog Timer Reset | _   | _         | 2.1 | μs    |                                                   |

| 35               | TBOR  | Brown-out Reset Pulse Width                            | 100 | _         | _   | μs    | VDD ≤ VBOR (D005)                                 |

<sup>\*</sup> These parameters are characterized but not tested.

<sup>†</sup> Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

FIGURE 16-13: TYPICAL, MINIMUM AND MAXIMUM WDT PERIOD vs. VDD (-40°C TO 125°C)

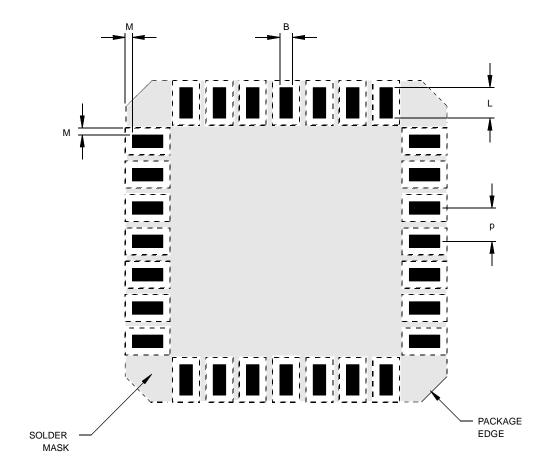

## 28-Lead Plastic Micro Leadframe Package (MF) 6x6 mm Body (MLF) (Continued)

|                    | Uni              | its |      | INCHES   |      | MILLIMETERS* |      |      |  |

|--------------------|------------------|-----|------|----------|------|--------------|------|------|--|

|                    | Dimension Limits | 3   | MIN  | NOM      | MAX  | MIN          | NOM  | MAX  |  |

| Pitch              | р                | )   |      | .026 BSC |      | 0.65 BSC     |      |      |  |

| Pad Width          | В                | 3   | .009 | .011     | .014 | 0.23         | 0.28 | 0.35 |  |

| Pad Length         | L                |     | .020 | .024     | .030 | 0.50         | 0.60 | 0.75 |  |

| Pad to Solder Mask | M                | 1   | .005 |          | .006 | 0.13         |      | 0.15 |  |

<sup>\*</sup>Controlling Parameter

Drawing No. C04-2114

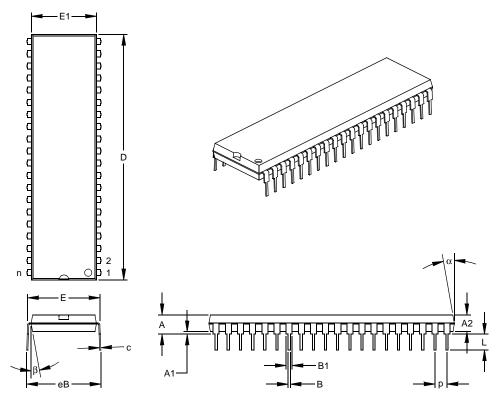

## 40-Lead Plastic Dual In-line (P) - 600 mil (PDIP)

|                            | Units    |       | INCHES* |       | MILLIMETERS |       |       |  |

|----------------------------|----------|-------|---------|-------|-------------|-------|-------|--|

| Dimensio                   | n Limits | MIN   | NOM     | MAX   | MIN         | NOM   | MAX   |  |

| Number of Pins             | n        |       | 40      |       |             | 40    |       |  |

| Pitch                      | р        |       | .100    |       |             | 2.54  |       |  |

| Top to Seating Plane       | Α        | .160  | .175    | .190  | 4.06        | 4.45  | 4.83  |  |

| Molded Package Thickness   | A2       | .140  | .150    | .160  | 3.56        | 3.81  | 4.06  |  |

| Base to Seating Plane      | A1       | .015  |         |       | 0.38        |       |       |  |

| Shoulder to Shoulder Width | Е        | .595  | .600    | .625  | 15.11       | 15.24 | 15.88 |  |

| Molded Package Width       | E1       | .530  | .545    | .560  | 13.46       | 13.84 | 14.22 |  |

| Overall Length             | D        | 2.045 | 2.058   | 2.065 | 51.94       | 52.26 | 52.45 |  |

| Tip to Seating Plane       | L        | .120  | .130    | .135  | 3.05        | 3.30  | 3.43  |  |

| Lead Thickness             | С        | .008  | .012    | .015  | 0.20        | 0.29  | 0.38  |  |

| Upper Lead Width           | B1       | .030  | .050    | .070  | 0.76        | 1.27  | 1.78  |  |

| Lower Lead Width           | В        | .014  | .018    | .022  | 0.36        | 0.46  | 0.56  |  |

| Overall Row Spacing §      | eВ       | .620  | .650    | .680  | 15.75       | 16.51 | 17.27 |  |

| Mold Draft Angle Top       | α        | 5     | 10      | 15    | 5           | 10    | 15    |  |

| Mold Draft Angle Bottom    | β        | 5     | 10      | 15    | 5           | 10    | 15    |  |

Dimensions D and E1 do not include mold flash or protrusions. Mold flash or protrusions shall not exceed

.010" (0.254mm) per side.

JEDEC Equivalent: MO-011 Drawing No. C04-016

<sup>\*</sup> Controlling Parameter § Significant Characteristic

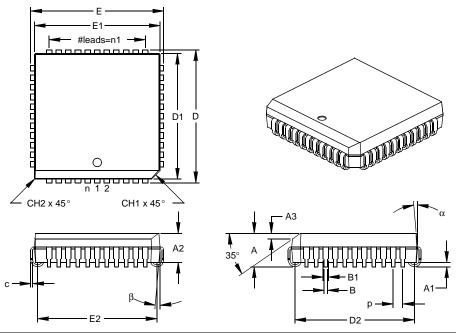

## 44-Lead Plastic Leaded Chip Carrier (L) – Square (PLCC)

|                          | Units  | INCHES* |      | MILLIMETERS |       |       |       |

|--------------------------|--------|---------|------|-------------|-------|-------|-------|

| Dimension                | Limits | MIN     | NOM  | MAX         | MIN   | NOM   | MAX   |

| Number of Pins           | n      |         | 44   |             |       | 44    |       |

| Pitch                    | р      |         | .050 |             |       | 1.27  |       |

| Pins per Side            | n1     |         | 11   |             |       | 11    |       |

| Overall Height           | Α      | .165    | .173 | .180        | 4.19  | 4.39  | 4.57  |

| Molded Package Thickness | A2     | .145    | .153 | .160        | 3.68  | 3.87  | 4.06  |

| Standoff §               | A1     | .020    | .028 | .035        | 0.51  | 0.71  | 0.89  |

| Side 1 Chamfer Height    | A3     | .024    | .029 | .034        | 0.61  | 0.74  | 0.86  |

| Corner Chamfer 1         | CH1    | .040    | .045 | .050        | 1.02  | 1.14  | 1.27  |

| Corner Chamfer (others)  | CH2    | .000    | .005 | .010        | 0.00  | 0.13  | 0.25  |

| Overall Width            | Е      | .685    | .690 | .695        | 17.40 | 17.53 | 17.65 |

| Overall Length           | D      | .685    | .690 | .695        | 17.40 | 17.53 | 17.65 |

| Molded Package Width     | E1     | .650    | .653 | .656        | 16.51 | 16.59 | 16.66 |

| Molded Package Length    | D1     | .650    | .653 | .656        | 16.51 | 16.59 | 16.66 |

| Footprint Width          | E2     | .590    | .620 | .630        | 14.99 | 15.75 | 16.00 |

| Footprint Length         | D2     | .590    | .620 | .630        | 14.99 | 15.75 | 16.00 |

| Lead Thickness           | С      | .008    | .011 | .013        | 0.20  | 0.27  | 0.33  |

| Upper Lead Width         | B1     | .026    | .029 | .032        | 0.66  | 0.74  | 0.81  |

| Lower Lead Width         | В      | .013    | .020 | .021        | 0.33  | 0.51  | 0.53  |

| Mold Draft Angle Top     | α      | 0       | 5    | 10          | 0     | 5     | 10    |

| Mold Draft Angle Bottom  | β      | 0       | 5    | 10          | 0     | 5     | 10    |

Dimensions D and E1 do not include mold flash or protrusions. Mold flash or protrusions shall not exceed

.010" (0.254mm) per side.

JEDEC Equivalent: MO-047

Drawing No. C04-048

<sup>\*</sup> Controlling Parameter § Significant Characteristic

# PIC16F7X

| USART Synchronous Transmission      |     |

|-------------------------------------|-----|

| (Through TXEN)                      |     |

| Wake-up from SLEEP via Interrupt    | 103 |

| Watchdog Timer                      |     |

| Timing Parameter Symbology          | 125 |

| Timing Requirements                 |     |

| Capture/Compare/PWM (CCP1 and CCP2) | 130 |

| CLKOUT and I/O                      | 127 |

| External Clock                      | 126 |

| I <sup>2</sup> C Bus Data           | 136 |

| I2C Bus START/STOP Bits             | 135 |

| Parallel Slave Port                 | 131 |

| RESET, Watchdog Timer, Oscillator   |     |

| Start-up Timer, Power-up Timer      |     |

| and Brown-out Reset                 | 128 |

| SPI Mode                            | 134 |

| Timer0 and Timer1 External Clock    | 129 |

| USART Synchronous Receive           |     |

| USART Synchronous Transmission      |     |

| TMR1CS bit                          |     |

| TMR1ON bit                          |     |

| TMR2ON bit                          | 52  |

| TOUTPS<3:0> bits                    | 52  |

| TRISA Register                      |     |

| TRISB Register                      |     |

| TRISC Register                      |     |

| TRISD Register                      |     |

| TRISE Register                      |     |

| IBF Bit                             |     |

| IBOV Bit                            |     |

| PSPMODE bit                         |     |

| TXSTA Register                      | , - |

| SYNC bit                            | 69  |

| TRMT bit                            |     |

| TX9 bit                             |     |

| TX9D bit                            |     |

| TXEN bit                            |     |

|                                     |     |

| U                                   |     |

| UA                                  | 60  |

| Universal Synchronous Asynchronous  |     |

| Receiver Transmitter. See USART     |     |

| Update Address bit, UA              | 60  |

| USART                               |     |

| Asynchronous Mode                   |     |

| Asynchronous Receiver               |     |

| Asynchronous Reception              |     |

| Associated Registers                |     |

| Asynchronous Transmission           |     |

| Associated Registers                | 74  |

| Asynchronous Transmitter            |     |

|                                     |     |

| Baud Rate Generator (BRG)                   | 71      |

|---------------------------------------------|---------|

| Baud Rate Formula                           | 71      |

| Baud Rates, Asynchronous Mode               |         |

| (BRGH = 0)                                  | 72      |

| Baud Rates, Asynchronous Mode               |         |

| (BRGH = 1)                                  | 72      |

| Sampling                                    |         |

| Mode Select (SYNC Bit)                      | 60      |

| Overrun Error (OERR Bit)                    |         |

| RC6/TX/CK Pin                               |         |

| RC7/RX/DT Pin                               |         |

| Serial Port Enable (SPEN Bit)               |         |

| Single Receive Enable (SREN Bit)            |         |

|                                             |         |

| Synchronous Master Mode                     |         |

| Synchronous Master Reception                |         |

| Associated Registers                        |         |

| Synchronous Master Transmission             |         |

| Associated Registers                        |         |

| Synchronous Slave Mode                      |         |

| Synchronous Slave Reception                 |         |

| Associated Registers                        | 81      |

| Synchronous Slave Transmission              |         |

| Associated Registers                        | 81      |

| Transmit Data, 9th Bit (TX9D)               | 69      |

| Transmit Enable (TXEN bit)                  |         |

| Transmit Enable, Nine-bit (TX9 bit)         | 69      |

| Transmit Shift Register Status (TRMT bit) . | 69      |

| · · · · · ·                                 |         |

| W                                           |         |

| Wake-up from SLEEP                          | 89, 102 |

| Interrupts                                  |         |

| MCLR Reset                                  |         |

| WDT Reset                                   |         |

| Wake-up Using Interrupts                    |         |

| Watchdog Timer (WDT)                        |         |

| Associated Registers                        |         |

| Enable (WDTE Bit)                           |         |

| Postscaler. See Postscaler, WDT             | 101     |

| Programming Considerations                  | 101     |

| RC Oscillator                               |         |

|                                             |         |

| Time-out Period                             |         |

| WDT Reset, Normal Operation                 |         |

| WDT Reset, SLEEP                            |         |

| WCOL bit                                    |         |

| Write Collision Detect bit (WCOL)           |         |

| WWW, On-Line Support                        |         |

|                                             |         |

## **ON-LINE SUPPORT**

Microchip provides on-line support on the Microchip World Wide Web (WWW) site.

The web site is used by Microchip as a means to make files and information easily available to customers. To view the site, the user must have access to the Internet and a web browser, such as Netscape or Microsoft Explorer. Files are also available for FTP download from our FTP site.

## Connecting to the Microchip Internet Web Site

The Microchip web site is available by using your favorite Internet browser to attach to:

#### www.microchip.com

The file transfer site is available by using an FTP service to connect to:

## ftp://ftp.microchip.com

The web site and file transfer site provide a variety of services. Users may download files for the latest Development Tools, Data Sheets, Application Notes, User's Guides, Articles and Sample Programs. A variety of Microchip specific business information is also available, including listings of Microchip sales offices, distributors and factory representatives. Other data available for consideration is:

- · Latest Microchip Press Releases

- Technical Support Section with Frequently Asked Questions

- Design Tips

- · Device Errata

- · Job Postings

- · Microchip Consultant Program Member Listing

- Links to other useful web sites related to Microchip Products

- Conferences for products, Development Systems, technical information and more

- · Listing of seminars and events

## Systems Information and Upgrade Hot Line

The Systems Information and Upgrade Line provides system users a listing of the latest versions of all of Microchip's development systems software products. Plus, this line provides information on how customers can receive any currently available upgrade kits. The Hot Line Numbers are:

1-800-755-2345 for U.S. and most of Canada, and 1-480-792-7302 for the rest of the world.

013001