Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

### Details

| Details                    |                                                                          |

|----------------------------|--------------------------------------------------------------------------|

| Product Status             | Active                                                                   |

| Core Processor             | PIC                                                                      |

| Core Size                  | 8-Bit                                                                    |

| Speed                      | 20MHz                                                                    |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                                        |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                    |

| Number of I/O              | 22                                                                       |

| Program Memory Size        | 14KB (8K x 14)                                                           |

| Program Memory Type        | FLASH                                                                    |

| EEPROM Size                | -                                                                        |

| RAM Size                   | 368 × 8                                                                  |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 5.5V                                                                |

| Data Converters            | A/D 5x8b                                                                 |

| Oscillator Type            | External                                                                 |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                        |

| Mounting Type              | Surface Mount                                                            |

| Package / Case             | 28-SOIC (0.295", 7.50mm Width)                                           |

| Supplier Device Package    | 28-SOIC                                                                  |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16lf76-i-so |

|                            |                                                                          |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### Note the following details of the code protection feature on PICmicro<sup>®</sup> MCUs.

- The PICmicro family meets the specifications contained in the Microchip Data Sheet.

- Microchip believes that its family of PICmicro microcontrollers is one of the most secure products of its kind on the market today, when used in the intended manner and under normal conditions.

- There are dishonest and possibly illegal methods used to breach the code protection feature. All of these methods, to our knowledge, require using the PICmicro microcontroller in a manner outside the operating specifications contained in the data sheet. The person doing so may be engaged in theft of intellectual property.

- Microchip is willing to work with the customer who is concerned about the integrity of their code.

- Neither Microchip nor any other semiconductor manufacturer can guarantee the security of their code. Code protection does not mean that we are guaranteeing the product as "unbreakable".

- Code protection is constantly evolving. We at Microchip are committed to continuously improving the code protection features of our product.

If you have any further questions about this matter, please contact the local sales office nearest to you.

Information contained in this publication regarding device applications and the like is intended through suggestion only and may be superseded by updates. It is your responsibility to ensure that your application meets with your specifications. No representation or warranty is given and no liability is assumed by Microchip Technology Incorporated with respect to the accuracy or use of such information, or infringement of patents or other intellectual property rights arising from such use or otherwise. Use of Microchip's products as critical components in life support systems is not authorized except with express written approval by Microchip. No licenses are conveyed, implicitly or otherwise, under any intellectual property rights.

#### Trademarks

The Microchip name and logo, the Microchip logo, FilterLab, KEELOQ, MPLAB, PIC, PICmicro, PICMASTER, PICSTART, PRO MATE, SEEVAL and The Embedded Control Solutions Company are registered trademarks of Microchip Technology Incorporated in the U.S.A. and other countries.

dsPIC, ECONOMONITOR, FanSense, FlexROM, fuzzyLAB, In-Circuit Serial Programming, ICSP, ICEPIC, microID, microPort, Migratable Memory, MPASM, MPLIB, MPLINK, MPSIM, MXDEV, PICC, PICDEM, PICDEM.net, rfPIC, Select Mode and Total Endurance are trademarks of Microchip Technology Incorporated in the U.S.A.

Serialized Quick Term Programming (SQTP) is a service mark of Microchip Technology Incorporated in the U.S.A.

All other trademarks mentioned herein are property of their respective companies.

© 2002, Microchip Technology Incorporated, Printed in the U.S.A., All Rights Reserved.

Microchip received QS-9000 quality system certification for its worldwide headquarters, design and wafer fabrication facilities in Chandler and Tempe, Arizona in July 1999. The Company's quality system processes and procedures are QS-9000 compliant for its PICmicro® 8-bit MCUs, KEEL00® code hopping devices, Serial EEPROMs and microperipheral products. In addition, Microchip's quality system for the design and manufacture of development systems is ISO 9001 certified.

## 3.3 Reading the FLASH Program Memory

A program memory location may be read by writing two bytes of the address to the PMADR and PMADRH registers and then setting control bit RD (PMCON1<0>). Once the read control bit is set, the microcontroller will use the next two instruction cycles to read the data. The data is available in the PMDATA and PMDATH registers after the second NOP instruction. Therefore, it can be read as two bytes in the following instructions. The PMDATA and PMDATH registers will hold this value until the next read operation.

# 3.4 Operation During Code Protect

FLASH program memory has its own code protect mechanism. External Read and Write operations by programmers are disabled if this mechanism is enabled.

The microcontroller can read and execute instructions out of the internal FLASH program memory, regardless of the state of the code protect configuration bits.

|                      | BSF               | STATUS, RP1 | ;                                                                                          |

|----------------------|-------------------|-------------|--------------------------------------------------------------------------------------------|

|                      | BCF               | STATUS, RP0 | ; Bank 2                                                                                   |

|                      | MOVF              | ADDRH, W    | ;                                                                                          |

|                      | MOVWF             | PMADRH      | ; MSByte of Program Address to read                                                        |

|                      | MOVF              | ADDRL, W    | ;                                                                                          |

|                      | MOVWF             | PMADR       | ; LSByte of Program Address to read                                                        |

|                      | BSF               | STATUS, RP0 | ; Bank 3 Required                                                                          |

| Required<br>Sequence | BSF<br>NOP<br>NOP | PMCON1, RD  | ; EEPROM Read Sequence<br>; memory is read in the next two cycles after BSF PMCON1,RD<br>; |

|                      | BCF               | STATUS, RPO | ; Bank 2                                                                                   |

|                      | MOVF              | PMDATA, W   | ; W = LSByte of Program PMDATA                                                             |

|                      | MOVF              | PMDATH, W   | ; W = MSByte of Program PMDATA                                                             |

### EXAMPLE 3-1: FLASH PROGRAM READ

## TABLE 3-1: REGISTERS ASSOCIATED WITH PROGRAM FLASH

| Address | Name   | Bit 7                       | Bit 6                     | Bit 5                      | Bit 4 | Bit 3 | Bit 2 | Bit 1     | Bit 0     | Value on:<br>POR,<br>BOR | Value on<br>all other<br>RESETS |

|---------|--------|-----------------------------|---------------------------|----------------------------|-------|-------|-------|-----------|-----------|--------------------------|---------------------------------|

| 10Dh    | PMADR  | Address F                   | Address Register Low Byte |                            |       |       |       |           |           | xxxx xxxx                | uuuu uuuu                       |

| 10Fh    | PMADRH | _                           | —                         | Address Register High Byte |       |       |       |           |           | xxxx xxxx                | uuuu uuuu                       |

| 10Ch    | PMDATA | Data Reg                    | Data Register Low Byte    |                            |       |       |       |           |           | xxxx xxxx                | uuuu uuuu                       |

| 10Eh    | PMDATH | — — Data Register High Byte |                           |                            |       |       |       | xxxx xxxx | uuuu uuuu |                          |                                 |

| 18Ch    | PMCON1 | _(1)                        | —                         | _                          | _     | —     | _     | —         | RD        | 10                       | 10                              |

Legend: x = unknown, u = unchanged, r = reserved, - = unimplemented read as '0'. Shaded cells are not used during FLASH access. **Note 1:** This bit always reads as a '1'.

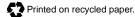

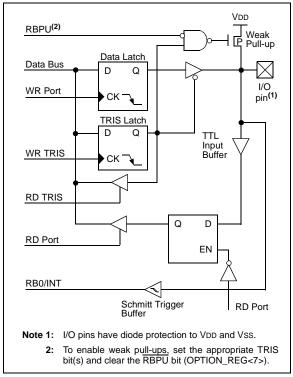

# 4.2 PORTB and the TRISB Register

PORTB is an 8-bit wide, bi-directional port. The corresponding data direction register is TRISB. Setting a TRISB bit (= '1') will make the corresponding PORTB pin an input (i.e., put the corresponding output driver in a Hi-Impedance mode). Clearing a TRISB bit (= '0') will make the corresponding PORTB pin an output (i.e., put the contents of the output latch on the selected pin).

Each of the PORTB pins has a weak internal pull-up. A single control bit can turn on all the pull-ups. This is performed by clearing bit RBPU (OPTION\_REG<7>). The weak pull-up is automatically turned off when the port pin is configured as an output. The pull-ups are disabled on a Power-on Reset.

Four of the PORTB pins (RB7:RB4) have an interrupt-on-change feature. Only pins configured as inputs can cause this interrupt to occur (i.e., any RB7:RB4 pin configured as an output is excluded from the interrupt-on-change comparison). The input pins (of RB7:RB4) are compared with the old value latched on the last read of PORTB. The "mismatch" outputs of RB7:RB4 are ORed together to generate the RB Port Change Interrupt with flag bit RBIF (INTCON<0>). This interrupt can wake the device from SLEEP. The user, in the Interrupt Service Routine, can clear the interrupt in the following manner:

- a) Any read or write of PORTB. This will end the mismatch condition.

- b) Clear flag bit RBIF.

A mismatch condition will continue to set flag bit RBIF. Reading PORTB will end the mismatch condition and allow flag bit RBIF to be cleared.

The interrupt-on-change feature is recommended for wake-up on key depression operation and operations where PORTB is only used for the interrupt-on-change feature. Polling of PORTB is not recommended while using the interrupt-on-change feature.

This interrupt on mismatch feature, together with software configureable pull-ups on these four pins, allow easy interface to a keypad and make it possible for wake-up on key depression. Refer to the Embedded Control Handbook, "Implementing Wake-up on Key Stroke" (AN552).

RB0/INT is an external interrupt input pin and is configured using the INTEDG bit (OPTION\_REG<6>).

RB0/INT is discussed in detail in Section 12.11.1.

### FIGURE 4-4: BLOCK DIAGRAM OF RB7:RB4 PINS

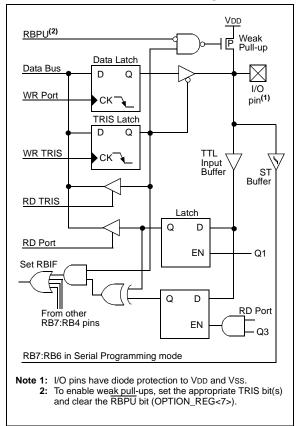

# 4.4 **PORTD and TRISD Registers**

This section is not applicable to the PIC16F73 or PIC16F76.

PORTD is an 8-bit port with Schmitt Trigger input buffers. Each pin is individually configureable as an input or output.

PORTD can be configured as an 8-bit wide microprocessor port (parallel slave port) by setting control bit PSPMODE (TRISE<4>). In this mode, the input buffers are TTL.

### FIGURE 4-6: PORTD BLOCK DIAGRAM (IN I/O PORT MODE)

| Name     | Bit# | Buffer Type           | Function                                          |

|----------|------|-----------------------|---------------------------------------------------|

| RD0/PSP0 | bit0 | ST/TTL <sup>(1)</sup> | Input/output port pin or parallel slave port bit0 |

| RD1/PSP1 | bit1 | ST/TTL <sup>(1)</sup> | Input/output port pin or parallel slave port bit1 |

| RD2/PSP2 | bit2 | ST/TTL <sup>(1)</sup> | Input/output port pin or parallel slave port bit2 |

| RD3/PSP3 | bit3 | ST/TTL <sup>(1)</sup> | Input/output port pin or parallel slave port bit3 |

| RD4/PSP4 | bit4 | ST/TTL <sup>(1)</sup> | Input/output port pin or parallel slave port bit4 |

| RD5/PSP5 | bit5 | ST/TTL <sup>(1)</sup> | Input/output port pin or parallel slave port bit5 |

| RD6/PSP6 | bit6 | ST/TTL <sup>(1)</sup> | Input/output port pin or parallel slave port bit6 |

| RD7/PSP7 | bit7 | ST/TTL <sup>(1)</sup> | Input/output port pin or parallel slave port bit7 |

## TABLE 4-7:PORTD FUNCTIONS

Legend: ST = Schmitt Trigger input, TTL = TTL input

Note 1: Input buffers are Schmitt Triggers when in I/O mode and TTL buffers when in Parallel Slave Port mode.

| Address | Name  | Bit 7 | Bit 6                         | Bit 5 | Bit 4   | Bit 3                                    | Bit 2 | Bit 1 | Bit 0 | Value on:<br>POR,<br>BOR | Value on<br>all other<br>RESETS |

|---------|-------|-------|-------------------------------|-------|---------|------------------------------------------|-------|-------|-------|--------------------------|---------------------------------|

| 08h     | PORTD | RD7   | RD6                           | RD5   | RD4     | RD3                                      | RD2   | RD1   | RD0   | xxxx xxxx                | uuuu uuuu                       |

| 88h     | TRISD | PORT  | PORTD Data Direction Register |       |         |                                          |       |       |       | 1111 1111                | 1111 1111                       |

| 89h     | TRISE | IBF   | OBF                           | IBOV  | PSPMODE | PORTE Data Direction bits 0000 -111 0000 |       |       |       | 0000 -111                |                                 |

Legend: x = unknown, u = unchanged, - = unimplemented read as '0'. Shaded cells are not used by PORTD.

| Name       | Bit# | Buffer Type           | Function                                                                                                                                                                                                                          |

|------------|------|-----------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| RE0/RD/AN5 | bit0 | ST/TTL <sup>(1)</sup> | Input/output port pin or read control input in Parallel Slave Port mode or<br>analog input.<br>For RD (PSP mode):<br>1 = IDLE<br>0 = Read operation. Contents of PORTD register output to PORTD I/O<br>pins (if chip selected).   |

| RE1/WR/AN6 | bit1 | ST/TTL <sup>(1)</sup> | Input/output port pin or write control input in Parallel Slave Port mode<br>or analog input.<br>For WR (PSP mode):<br>1 = IDLE<br>0 = Write operation. Value of PORTD I/O pins latched into PORTD<br>register (if chip selected). |

| RE2/CS/AN7 | bit2 | ST/TTL <sup>(1)</sup> | Input/output port pin or chip select control input in Parallel Slave Port<br>mode or analog input.<br>For CS (PSP mode):<br>1 = Device is not selected<br>0 = Device is selected                                                  |

Legend: ST = Schmitt Trigger input, TTL = TTL input **Note 1:** Input buffers are Schmitt Triggers when in I/O mode and TTL buffers when in Parallel Slave Port mode.

| TABLE 4-10: SUMMARY OF REGISTERS ASSOCIATED WITH PORTE | <b>TABLE 4-10</b> : | SUMMARY OF REGISTERS ASSOCIATED WITH PORTE |

|--------------------------------------------------------|---------------------|--------------------------------------------|

|--------------------------------------------------------|---------------------|--------------------------------------------|

| Addr | Name   | Bit 7 | Bit 6 | Bit 5 | Bit 4   | Bit 3 | Bit 2                     | Bit 1 | Bit 0     | Value on:<br>POR,<br>BOR | Value on all<br>other<br>RESETS |

|------|--------|-------|-------|-------|---------|-------|---------------------------|-------|-----------|--------------------------|---------------------------------|

| 09h  | PORTE  | —     | —     |       | —       | _     | RE2                       | RE1   | RE0       | xxx                      | uuu                             |

| 89h  | TRISE  | IBF   | OBF   | IBOV  | PSPMODE | _     | PORTE Data Direction bits |       | 0000 -111 | 0000 -111                |                                 |

| 9Fh  | ADCON1 | —     | _     |       | _       | _     | PCFG2                     | PCFG1 | PCFG0     | 000                      | 000                             |

Legend: x = unknown, u = unchanged, - = unimplemented, read as '0'. Shaded cells are not used by PORTE.

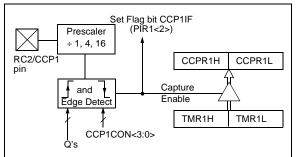

# 8.3 Capture Mode

In Capture mode, CCPR1H:CCPR1L captures the 16-bit value of the TMR1 register when an event occurs on pin RC2/CCP1. An event is defined as one of the following and is configured by CCPxCON<3:0>:

- · Every falling edge

- · Every rising edge

- Every 4th rising edge

- Every 16th rising edge

An event is selected by control bits CCP1M3:CCP1M0 (CCP1CON<3:0>). When a capture is made, the interrupt request flag bit CCP1IF (PIR1<2>) is set. The interrupt flag must be cleared in software. If another capture occurs before the value in register CCPR1 is read, the old captured value is overwritten by the new captured value.

## 8.3.1 CCP PIN CONFIGURATION

In Capture mode, the RC2/CCP1 pin should be configured as an input by setting the TRISC<2> bit.

**Note:** If the RC2/CCP1 pin is configured as an output, a write to the port can cause a capture condition.

### FIGURE 8-1: CAPTURE MODE OPERATION BLOCK DIAGRAM

## 8.3.2 TIMER1 MODE SELECTION

Timer1 must be running in Timer mode or Synchronized Counter mode for the CCP module to use the capture feature. In Asynchronous Counter mode, the capture operation may not work.

## 8.3.3 SOFTWARE INTERRUPT

When the Capture mode is changed, a false capture interrupt may be generated. The user should keep bit CCP1IE (PIE1<2>) clear to avoid false interrupts and should clear the flag bit CCP1IF following any such change in operating mode.

## 8.3.4 CCP PRESCALER

There are four prescaler settings, specified by bits CCP1M3:CCP1M0. Whenever the CCP module is turned off, or the CCP module is not in Capture mode, the prescaler counter is cleared. Any RESET will clear the prescaler counter.

Switching from one capture prescaler to another may generate an interrupt. Also, the prescaler counter will not be cleared, therefore, the first capture may be from a non-zero prescaler. Example 8-1 shows the recommended method for switching between capture prescalers. This example also clears the prescaler counter and will not generate the "false" interrupt.

### EXAMPLE 8-1: CHANGING BETWEEN CAPTURE PRESCALERS

| CCP1CON     | ;Turn CCP module off    |

|-------------|-------------------------|

| NEW_CAPT_PS | ;Load the W reg with    |

|             | ;the new prescaler      |

|             | ;move value and CCP ON  |

| CCP1CON     | ;Load CCP1CON with this |

|             | ;value                  |

|             | NEW_CAPT_PS             |

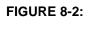

# 8.4 Compare Mode

In Compare mode, the 16-bit CCPR1 register value is constantly compared against the TMR1 register pair value. When a match occurs, the RC2/CCP1 pin is:

- Driven high

- Driven low

- Remains unchanged

The action on the pin is based on the value of control bits CCP1M3:CCP1M0 (CCP1CON<3:0>). At the same time, interrupt flag bit CCP1IF is set.

### COMPARE MODE OPERATION BLOCK DIAGRAM

Special Event Trigger will:

- clear TMR1H and TMR1L registers

- NOT set interrupt flag bit TMR1F (PIR1<0>)

- (for CCP2 only) set the GO/DONE bit (ADCON0<2>)

## 9.3.1.1 Addressing

Once the SSP module has been enabled, it waits for a START condition to occur. Following the START condition, the 8-bits are shifted into the SSPSR register. All incoming bits are sampled with the rising edge of the clock (SCL) line. The value of register SSPSR<7:1> is compared to the value of the SSPADD register. The address is compared on the falling edge of the eighth clock (SCL) pulse. If the addresses match, and the BF and SSPOV bits are clear, the following events occur:

- a) The SSPSR register value is loaded into the SSPBUF register.

- b) The buffer full bit, BF is set.

- c) An ACK pulse is generated.

- d) SSP interrupt flag bit, SSPIF (PIR1<3>) is set (interrupt is generated if enabled) - on the falling edge of the ninth SCL pulse.

In 10-bit Address mode, two address bytes need to be received by the slave (Figure 9-7). The five Most Significant bits (MSbs) of the first address byte specify if this is a 10-bit address. Bit R/W (SSPSTAT<2>) must specify a write so the slave device will receive the second address byte. For a 10-bit address, the first byte would equal '1111 0 A9 A8 0', where A9 and A8 are the two MSbs of the address. The sequence of events for 10-bit address is as follows, with steps 7 - 9 for slave-transmitter:

- 1. Receive first (high) byte of address (bits SSPIF, BF, and bit UA (SSPSTAT<1>) are set).

- Update the SSPADD register with second (low) byte of address (clears bit UA and releases the SCL line).

- 3. Read the SSPBUF register (clears bit BF) and clear flag bit SSPIF.

- 4. Receive second (low) byte of address (bits SSPIF, BF, and UA are set).

- 5. Update the SSPADD register with the first (high) byte of address, if match releases SCL line, this will clear bit UA.

- 6. Read the SSPBUF register (clears bit BF) and clear flag bit SSPIF.

- 7. Receive Repeated START condition.

- 8. Receive first (high) byte of address (bits SSPIF and BF are set).

- 9. Read the SSPBUF register (clears bit BF) and clear flag bit SSPIF.

|    | its as Data<br>s Received | $SSPSR \to SSPBUF$ | Generate ACK<br>Pulse | Set bit SSPIF<br>(SSP Interrupt occurs |  |

|----|---------------------------|--------------------|-----------------------|----------------------------------------|--|

| BF | SSPOV                     |                    | Fuise                 | if enabled)                            |  |

| 0  | 0                         | Yes                | Yes                   | Yes                                    |  |

| 1  | 0                         | No                 | No                    | Yes                                    |  |

| 1  | 1                         | No                 | No                    | Yes                                    |  |

| 0  | 1                         | No                 | No                    | Yes                                    |  |

# TABLE 9-2: DATA TRANSFER RECEIVED BYTE ACTIONS

**Note:** Shaded cells show the conditions where the user software did not properly clear the overflow condition.

### 9.3.1.2 Reception

When the R/W bit of the address byte is clear and an address match occurs, the R/W bit of the SSPSTAT register is cleared. The received address is loaded into the SSPBUF register.

When the address byte overflow condition exists, then no Acknowledge (ACK) pulse is given. An overflow condition is defined as either bit BF (SSPSTAT<0>) is set, or bit SSPOV (SSPCON<6>) is set. This is an error condition due to the user's firmware. An SSP interrupt is generated for each data transfer byte. Flag bit SSPIF (PIR1<3>) must be cleared in software. The SSPSTAT register is used to determine the status of the byte.

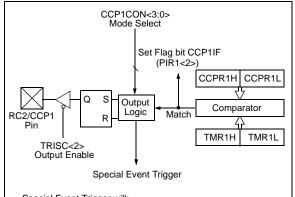

### 10.3.2 USART SYNCHRONOUS MASTER RECEPTION

Once synchronous mode is selected, reception is enabled by setting either enable bit SREN (RCSTA<5>), or enable bit CREN (RCSTA<4>). Data is sampled on the RC7/RX/DT pin on the falling edge of the clock. If enable bit SREN is set, then only a single word is received. If enable bit CREN is set, the reception is continuous until CREN is cleared. If both bits are set, CREN takes precedence. After clocking the last bit, the received data in the Receive Shift Register (RSR) is transferred to the RCREG register (if it is empty). When the transfer is complete, interrupt flag bit RCIF (PIR1<5>) is set. The actual interrupt can be enabled/ disabled by setting/clearing enable bit RCIE (PIE1<5>). Flag bit RCIF is a read only bit, which is reset by the hardware. In this case, it is reset when the RCREG register has been read and is empty. The RCREG is a double buffered register (i.e., it is a two deep FIFO). It is possible for two bytes of data to be received and transferred to the RCREG FIFO and a third byte to begin shifting into the RSR register. On the clocking of the last bit of the third byte, if the RCREG register is still full, then overrun error bit OERR (RCSTA<1>) is set. The word in the RSR will be lost. The RCREG register can be read twice to retrieve the two bytes in the FIFO. Bit OERR has to be cleared in software (by clearing bit CREN). If bit OERR is set, transfers from the RSR to the RCREG are inhibited, so it is essential to clear bit OERR if it is set. The ninth receive bit is buffered the same way as the

receive data. Reading the RCREG register will load bit RX9D with a new value, therefore, it is essential for the user to read the RCSTA register before reading RCREG, in order not to lose the old RX9D information.

Steps to follow when setting up a Synchronous Master Reception:

- 1. Initialize the SPBRG register for the appropriate baud rate (Section 10.1).

- 2. Enable the synchronous master serial port by setting bits SYNC, SPEN and CSRC.

- 3. Ensure bits CREN and SREN are clear.

- 4. If interrupts are desired, then set enable bit RCIE.

- 5. If 9-bit reception is desired, then set bit RX9.

- 6. If a single reception is required, set bit SREN. For continuous reception set bit CREN.

- Interrupt flag bit RCIF will be set when reception is complete and an interrupt will be generated if enable bit RCIE was set.

- 8. Read the RCSTA register to get the ninth bit (if enabled) and determine if any error occurred during reception.

- 9. Read the 8-bit received data by reading the RCREG register.

- 10. If any error occurred, clear the error by clearing bit CREN.

- 11. If using interrupts, ensure that GIE and PEIE in the INTCON register are set.

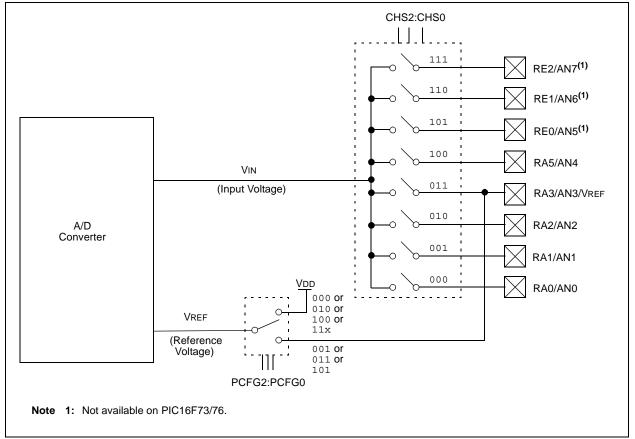

The following steps should be followed for doing an  $\ensuremath{\mathsf{A}}\xspace/\ensuremath{\mathsf{D}}\xspace$  conversion:

- 1. Configure the A/D module:

- Configure analog pins, voltage reference, and digital I/O (ADCON1)

- Select A/D conversion clock (ADCON0)

- Turn on A/D module (ADCON0)

- 2. Configure the A/D interrupt (if desired):

- Clear ADIF bit

- Set ADIE bit

- Set PEIE bit

- Set GIE bit

- 3. Select an A/D input channel (ADCON0).

- 4. Wait for at least an appropriate acquisition period.

- 5. Start conversion:Set GO/DONE bit (ADCON0)

- 6. Wait for the A/D conversion to complete, by either:

- Polling for the GO/DONE bit to be cleared (interrupts disabled)

OR

- Waiting for the A/D interrupt

- 7. Read A/D result register (ADRES), and clear bit ADIF if required.

- 8. For next conversion, go to step 3 or step 4, as required.

## FIGURE 11-1: A/D BLOCK DIAGRAM

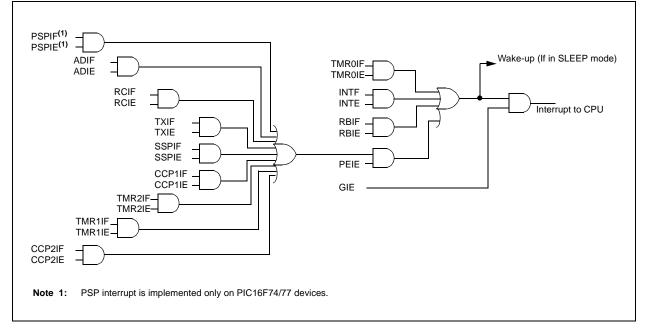

# 12.11 Interrupts

The PIC16F7X family has up to 12 sources of interrupt. The interrupt control register (INTCON) records individual interrupt requests in flag bits. It also has individual and global interrupt enable bits.

| Note: | Individual interrupt flag bits are set, regard- |

|-------|-------------------------------------------------|

|       | less of the status of their corresponding       |

|       | mask bit or the GIE bit.                        |

A global interrupt enable bit, GIE (INTCON<7>) enables (if set) all unmasked interrupts, or disables (if cleared) all interrupts. When bit GIE is enabled and an interrupt's flag bit and mask bit are set, the interrupt will vector immediately. Individual interrupts can be disabled through their corresponding enable bits in various registers. Individual interrupt bits are set, regardless of the status of the GIE bit. The GIE bit is cleared on RESET.

The "return from interrupt" instruction, RETFIE, exits the interrupt routine, as well as sets the GIE bit, which re-enables interrupts.

The RB0/INT pin interrupt, the RB port change interrupt and the TMR0 overflow interrupt flags are contained in the INTCON register.

The peripheral interrupt flags are contained in the Special Function Registers, PIR1 and PIR2. The corresponding interrupt enable bits are contained in Special Function Registers, PIE1 and PIE2, and the peripheral interrupt enable bit is contained in Special Function Register, INTCON.

When an interrupt is responded to, the GIE bit is cleared to disable any further interrupt, the return address is pushed onto the stack and the PC is loaded with 0004h. Once in the Interrupt Service Routine, the source(s) of the interrupt can be determined by polling the interrupt flag bits. The interrupt flag bit(s) must be cleared in software before re-enabling interrupts to avoid recursive interrupts.

For external interrupt events, such as the INT pin or PORTB change interrupt, the interrupt latency will be three or four instruction cycles. The exact latency depends when the interrupt event occurs, relative to the current Q cycle. The latency is the same for one or two-cycle instructions. Individual interrupt flag bits are set, regardless of the status of their corresponding mask bit, PEIE bit, or the GIE bit.

## FIGURE 12-10: INTERRUPT LOGIC

# PIC16F7X

| MOVF             | Move f                                                                                                                                                                                                                                                                            |  |  |  |  |  |

|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| Syntax:          | [ <i>label</i> ] MOVF f,d                                                                                                                                                                                                                                                         |  |  |  |  |  |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ d \in \ [0,1] \end{array}$                                                                                                                                                                                                                 |  |  |  |  |  |

| Operation:       | (f) $\rightarrow$ (destination)                                                                                                                                                                                                                                                   |  |  |  |  |  |

| Status Affected: | Z                                                                                                                                                                                                                                                                                 |  |  |  |  |  |

| Description:     | The contents of register f are<br>moved to a destination dependant<br>upon the status of d. If $d = 0$ ,<br>destination is W register. If $d = 1$ ,<br>the destination is file register f itself.<br>d = 1 is useful to test a file register,<br>since status flag Z is affected. |  |  |  |  |  |

| NOP              | No Operation  |  |  |  |  |

|------------------|---------------|--|--|--|--|

| Syntax:          | [label] NOP   |  |  |  |  |

| Operands:        | None          |  |  |  |  |

| Operation:       | No operation  |  |  |  |  |

| Status Affected: | None          |  |  |  |  |

| Description:     | No operation. |  |  |  |  |

| MOVLW            | Move Literal to W                                                                          |  |  |  |  |  |

|------------------|--------------------------------------------------------------------------------------------|--|--|--|--|--|

| Syntax:          | [ <i>label</i> ] MOVLW k                                                                   |  |  |  |  |  |

| Operands:        | $0 \le k \le 255$                                                                          |  |  |  |  |  |

| Operation:       | $k \rightarrow (W)$                                                                        |  |  |  |  |  |

| Status Affected: | None                                                                                       |  |  |  |  |  |

| Description:     | The eight-bit literal 'k' is loaded into W register. The don't cares will assemble as 0's. |  |  |  |  |  |

| RETFIE           | Return from Interrupt                                   |

|------------------|---------------------------------------------------------|

| Syntax:          | [label] RETFIE                                          |

| Operands:        | None                                                    |

| Operation:       | $\begin{array}{l} TOS \to PC, \\ 1 \to GIE \end{array}$ |

| Status Affected: | None                                                    |

| MOVWF            | Move W to f                                   |  |  |  |  |  |

|------------------|-----------------------------------------------|--|--|--|--|--|

| Syntax:          | [ label ] MOVWF f                             |  |  |  |  |  |

| Operands:        | $0 \le f \le 127$                             |  |  |  |  |  |

| Operation:       | $(W) \rightarrow (f)$                         |  |  |  |  |  |

| Status Affected: | None                                          |  |  |  |  |  |

| Description:     | Move data from W register to<br>register 'f'. |  |  |  |  |  |

| RETLW            | Return with Literal in W                                                                                                                                                            |  |  |  |  |  |

|------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| Syntax:          | [ <i>label</i> ] RETLW k                                                                                                                                                            |  |  |  |  |  |

| Operands:        | $0 \le k \le 255$                                                                                                                                                                   |  |  |  |  |  |

| Operation:       | $k \rightarrow (W);$<br>TOS $\rightarrow PC$                                                                                                                                        |  |  |  |  |  |

| Status Affected: | None                                                                                                                                                                                |  |  |  |  |  |

| Description:     | The W register is loaded with the<br>eight-bit literal 'k'. The program<br>counter is loaded from the top of<br>the stack (the return address).<br>This is a two-cycle instruction. |  |  |  |  |  |

# 14.4 MPLINK Object Linker/ MPLIB Object Librarian

The MPLINK object linker combines relocatable objects created by the MPASM assembler and the MPLAB C17 and MPLAB C18 C compilers. It can also link relocatable objects from pre-compiled libraries, using directives from a linker script.

The MPLIB object librarian is a librarian for precompiled code to be used with the MPLINK object linker. When a routine from a library is called from another source file, only the modules that contain that routine will be linked in with the application. This allows large libraries to be used efficiently in many different applications. The MPLIB object librarian manages the creation and modification of library files.

The MPLINK object linker features include:

- Integration with MPASM assembler and MPLAB C17 and MPLAB C18 C compilers.

- Allows all memory areas to be defined as sections to provide link-time flexibility.

The MPLIB object librarian features include:

- Easier linking because single libraries can be included instead of many smaller files.

- Helps keep code maintainable by grouping related modules together.

- Allows libraries to be created and modules to be added, listed, replaced, deleted or extracted.

# 14.5 MPLAB SIM Software Simulator

The MPLAB SIM software simulator allows code development in a PC-hosted environment by simulating the PICmicro series microcontrollers on an instruction level. On any given instruction, the data areas can be examined or modified and stimuli can be applied from a file, or user-defined key press, to any of the pins. The execution can be performed in single step, execute until break, or trace mode.

The MPLAB SIM simulator fully supports symbolic debugging using the MPLAB C17 and the MPLAB C18 C compilers and the MPASM assembler. The software simulator offers the flexibility to develop and debug code outside of the laboratory environment, making it an excellent multiproject software development tool.

# 14.6 MPLAB ICE High Performance Universal In-Circuit Emulator with MPLAB IDE

The MPLAB ICE universal in-circuit emulator is intended to provide the product development engineer with a complete microcontroller design tool set for PICmicro microcontrollers (MCUs). Software control of the MPLAB ICE in-circuit emulator is provided by the MPLAB Integrated Development Environment (IDE), which allows editing, building, downloading and source debugging from a single environment.

The MPLAB ICE 2000 is a full-featured emulator system with enhanced trace, trigger and data monitoring features. Interchangeable processor modules allow the system to be easily reconfigured for emulation of different processors. The universal architecture of the MPLAB ICE in-circuit emulator allows expansion to support new PICmicro microcontrollers.

The MPLAB ICE in-circuit emulator system has been designed as a real-time emulation system, with advanced features that are generally found on more expensive development tools. The PC platform and Microsoft<sup>®</sup> Windows environment were chosen to best make these features available to you, the end user.

# 14.7 ICEPIC In-Circuit Emulator

The ICEPIC low cost, in-circuit emulator is a solution for the Microchip Technology PIC16C5X, PIC16C6X, PIC16C7X and PIC16CXXX families of 8-bit One-Time-Programmable (OTP) microcontrollers. The modular system can support different subsets of PIC16C5X or PIC16CXXX products through the use of interchangeable personality modules, or daughter boards. The emulator is capable of emulating without target application circuitry being present.

# 15.1 DC Characteristics: PIC16F73/74/76/77 (Industrial, Extended) PIC16LF73/74/76/77 (Industrial) (Continued)

| PIC16LF73/74/76/77<br>(Industrial) |               |                                     | Standard Operating Conditions (unless otherwise stated)<br>Operating temperature $-40^{\circ}C \le TA \le +85^{\circ}C$ for industrial |             |                                                                                                                                                                             |          |                                                                                                                                     |  |

|------------------------------------|---------------|-------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------|-------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|-------------------------------------------------------------------------------------------------------------------------------------|--|

|                                    |               |                                     |                                                                                                                                        |             | Depending Conditions (unless otherwise stated)<br>temperature $-40^{\circ}C \le TA \le +85^{\circ}C$ for industrial<br>$-40^{\circ}C \le TA \le +125^{\circ}C$ for extended |          |                                                                                                                                     |  |

| Param<br>No.                       | Sym           | Characteristic                      | Min Typ† Max Units Conditions                                                                                                          |             |                                                                                                                                                                             |          |                                                                                                                                     |  |

|                                    | Idd           | Supply Current (Notes 2, 5          | <b>i</b> )                                                                                                                             |             |                                                                                                                                                                             |          |                                                                                                                                     |  |

| D010                               |               | PIC16LF7X                           | —                                                                                                                                      | 0.4         | 2.0                                                                                                                                                                         | mA       | XT, RC osc configuration<br>Fosc = 4 MHz, VDD = 3.0V (Note 4)                                                                       |  |

| D010A                              |               |                                     | —                                                                                                                                      | 20          | 48                                                                                                                                                                          | μA       | LP osc configuration<br>FOSC = 32 kHz, VDD = 3.0V, WDT disabled                                                                     |  |

| D010                               |               | PIC16F7X                            | -                                                                                                                                      | 0.9         | 4                                                                                                                                                                           | mA       | XT, RC osc configuration<br>Fosc = 4 MHz, VDD = 5.5V (Note 4)                                                                       |  |

| D013                               |               |                                     | —                                                                                                                                      | 5.2         | 15                                                                                                                                                                          | mA       | HS osc configuration<br>Fosc = 20 MHz, VDD = 5.5V                                                                                   |  |

| D015*                              | ∆Ibor         | Brown-out<br>Reset Current (Note 6) | _                                                                                                                                      | 25          | 200                                                                                                                                                                         | μA       | BOR enabled, VDD = 5.0V                                                                                                             |  |

| D020                               | IPD           | Power-down Current (Note            | es 3, 5)                                                                                                                               |             |                                                                                                                                                                             |          |                                                                                                                                     |  |

| D021                               |               | PIC16LF7X                           |                                                                                                                                        | 2.0<br>0.1  | 30<br>5                                                                                                                                                                     | μΑ<br>μΑ | VDD = $3.0V$ , WDT enabled, $-40^{\circ}C$ to $+85^{\circ}C$<br>VDD = $3.0V$ , WDT disabled, $-40^{\circ}C$ to $+85^{\circ}C$       |  |

| D020<br>D021                       |               | PIC16F7X                            | _                                                                                                                                      | 5.0<br>0.1  | 42<br>19                                                                                                                                                                    | μΑ<br>μΑ | $VDD = 4.0V$ , $WDT$ enabled, $-40^{\circ}C$ to $+85^{\circ}C$<br>$VDD = 4.0V$ , $WDT$ disabled, $-40^{\circ}C$ to $+85^{\circ}C$   |  |

| D021A                              |               |                                     | _                                                                                                                                      | 10.5<br>1.5 | 57<br>42                                                                                                                                                                    | μΑ<br>μΑ | $VDD = 4.0V$ , $WDT$ enabled, $-40^{\circ}C$ to $+125^{\circ}C$<br>$VDD = 4.0V$ , $WDT$ disabled, $-40^{\circ}C$ to $+125^{\circ}C$ |  |

| D023*                              | $\Delta$ Ibor | Brown-out<br>Reset Current (Note 6) | $- 25  200  \mu A  BOR \text{ enabled}, \text{ VDD} = 5.0 \text{ V}$                                                                   |             |                                                                                                                                                                             |          |                                                                                                                                     |  |

Legend: Shading of rows is to assist in readability of of the table.

\* These parameters are characterized but not tested.

† Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

**Note 1:** This is the limit to which VDD can be lowered without losing RAM data.

2: The supply current is mainly a function of the operating voltage and frequency. Other factors, such as I/O pin loading and switching rate, oscillator type, internal code execution pattern and temperature also have an impact on the current consumption.

The test conditions for all IDD measurements in active operation mode are:

- OSC1 = external square wave, from-rail to-rail; all I/O pins tri-stated, pulled to VDD MCLR = VDD; WDT enabled/disabled as specified.

- **3:** The power-down current in SLEEP mode does not depend on the oscillator type. Power-down current is measured with the part in SLEEP mode, with all I/O pins in hi-impedance state and tied to VDD and Vss.

- 4: For RC osc configuration, current through REXT is not included. The current through the resistor can be estimated by the formula Ir = VDD/2REXT (mA) with REXT in kOhm.

- **5:** Timer1 oscillator (when enabled) adds approximately 20 μA to the specification. This value is from characterization and is for design guidance only. This is not tested.

- 6: The ∆ current is the additional current consumed when this peripheral is enabled. This current should be added to the base IDD or IPD measurement.

- 7: When BOR is enabled, the device will operate correctly until the VBOR voltage trip point is reached.

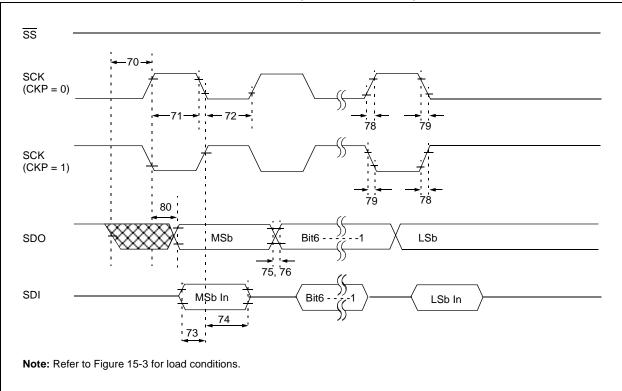

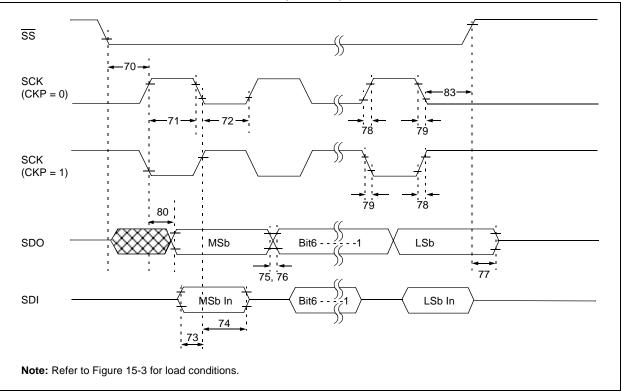

## FIGURE 15-11: SPI MASTER MODE TIMING (CKE = 0, SMP = 0)

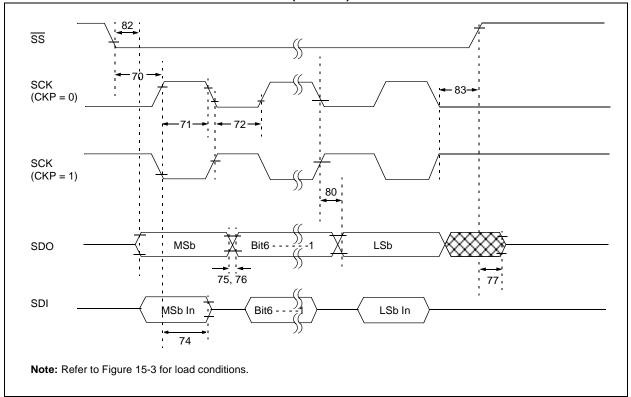

# FIGURE 15-12: SPI MASTER MODE TIMING (CKE = 1, SMP = 1)

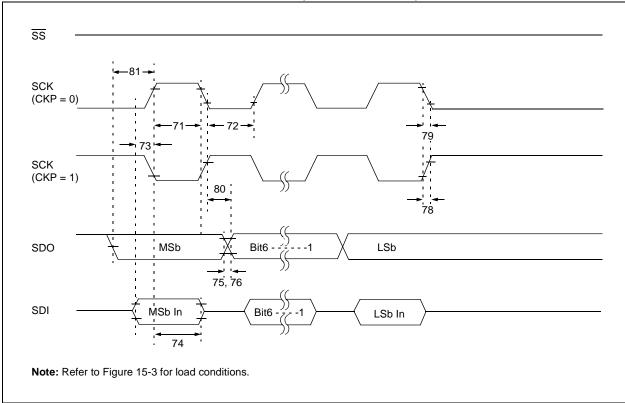

# FIGURE 15-14: SPI SLAVE MODE TIMING (CKE = 1)

# TABLE 15-12: A/D CONVERTER CHARACTERISTICS: PIC16F7X (INDUSTRIAL, EXTENDED) PIC16LF7X (INDUSTRIAL)

| Param<br>No. | Sym  | Characteristic                                    |           | Min        | Тур†       | Max        | Units    | Conditions                                                                                                             |

|--------------|------|---------------------------------------------------|-----------|------------|------------|------------|----------|------------------------------------------------------------------------------------------------------------------------|

| A01          | Nr   | Resolution                                        | PIC16F7X  |            | _          | 8 bits     | bit      | $\begin{array}{l} \text{VREF} = \text{VDD} = 5.12\text{V},\\ \text{VSS} \leq \text{VAIN} \leq \text{VREF} \end{array}$ |

|              |      |                                                   | PIC16LF7X | —          | _          | 8 bits     | bit      | VREF = VDD = 2.2V                                                                                                      |

| A02          | Eabs | Total absolute er                                 | ror       | —          | —          | < ±1       | LSb      | VREF = VDD = 5.12V,<br>VSS ≤ VAIN ≤ VREF                                                                               |

| A03          | EIL  | Integral linearity                                | error     | —          | —          | < ±1       | LSb      | VREF = VDD = 5.12V,<br>$VSS \le VAIN \le VREF$                                                                         |

| A04          | Edl  | Differential linearity error                      |           | —          | —          | < ±1       | LSb      | VREF = VDD = 5.12V,<br>$VSS \le VAIN \le VREF$                                                                         |

| A05          | Efs  | Full scale error                                  |           | —          | —          | < ±1       | LSb      | VREF = VDD = 5.12V,<br>$VSS \le VAIN \le VREF$                                                                         |

| A06          | EOFF | Offset error                                      |           | —          | —          | < ±1       | LSb      | VREF = VDD = 5.12V,<br>$VSS \le VAIN \le VREF$                                                                         |

| A10          | —    | Monotonicity (Note 3)                             |           | —          | guaranteed | —          |          | $VSS \le VAIN \le VREF$                                                                                                |

| A20          | Vref | Reference voltage                                 |           | 2.5<br>2.2 |            | 5.5<br>5.5 | V<br>V   | -40°C to +125°C<br>0°C to +125°C                                                                                       |

| A25          | VAIN | Analog input vol                                  | tage      | Vss - 0.3  |            | Vref + 0.3 | V        |                                                                                                                        |

| A30          | ZAIN | Recommended impedance of<br>analog voltage source |           | —          | _          | 10.0       | kΩ       |                                                                                                                        |

| A40          | IAD  | A/D conversion                                    | PIC16F7X  | _          | 180        | _          | μΑ       | Average current                                                                                                        |

|              |      | current (VDD)                                     | PIC16LF7X |            | 90         | —          | μA       | consumption when A/D is on <b>(Note 1)</b> .                                                                           |

| A50          | IREF | VREF input current (Note 2)                       |           | N/A<br>—   |            | ±5<br>500  | μΑ<br>μΑ | During VAIN acquisition.<br>During A/D Conversion<br>cycle.                                                            |

\* These parameters are characterized but not tested.

† Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

**Note 1:** When A/D is off, it will not consume any current other than minor leakage current. The power-down current spec includes any such leakage from the A/D module.

2: VREF current is from the RA3 pin or the VDD pin, whichever is selected as a reference input.

**3:** The A/D conversion result never decreases with an increase in the input voltage and has no missing codes.

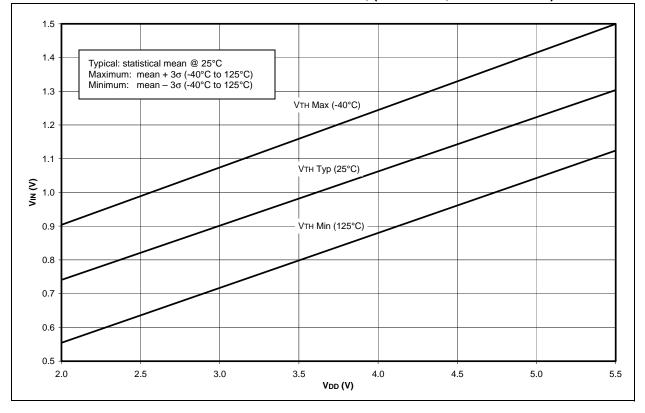

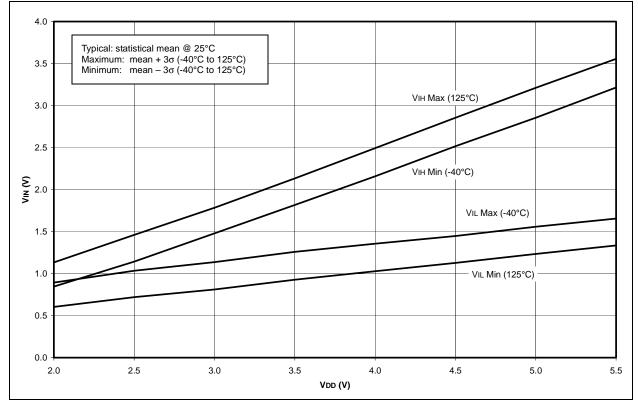

### FIGURE 16-19: MINIMUM AND MAXIMUM VIN vs. VDD, (TTL INPUT, -40°C TO 125°C)

# 17.0 PACKAGING INFORMATION

# 17.1 Package Marking Information

### 28-Lead SOIC

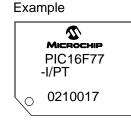

Example

# Example

## 28-Lead SSOP

28-Lead MLF

# Example

# Example

| Legend | I: XXX<br>Y<br>YY<br>WW<br>NNN | Customer specific information*<br>Year code (last digit of calendar year)<br>Year code (last 2 digits of calendar year)<br>Week code (week of January 1 is week '01')<br>Alphanumeric traceability code |

|--------|--------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Note:  | be carried                     | nt the full Microchip part number cannot be marked on one line, it will<br>over to the next line thus limiting the number of available characters<br>her specific information.                          |

\* Standard PICmicro device marking consists of Microchip part number, year code, week code, and traceability code. For PICmicro device marking beyond this, certain price adders apply. Please check with your Microchip Sales Office. For QTP devices, any special marking adders are included in QTP price.

# Package Marking Information (Cont'd)

## 44-Lead TQFP

Example

Ο

PIC16F77-I/P

0210017

## 44-Lead PLCC

Example

# PIC16F7X

| Code Protection                      | 103   |

|--------------------------------------|-------|

| Computed GOTO                        | 26    |

| Configuration Bits                   | 89    |

| Continuous Receive Enable (CREN Bit) | 70    |

| Conversion Considerations            | . 162 |

|                                      | -     |

# D

| D/A bit                        | 60  |

|--------------------------------|-----|

| Data Memory                    |     |

| Bank Select (RP1:RP0 bits)     |     |

| General Purpose Registers      |     |

| Register File Map, PIC16F74/73 |     |

| Register File Map, PIC16F77/76 | 14  |

| Special Function Registers     |     |

| Data/Address bit (D/A)         | 60  |

| DC and AC Characteristics      |     |

| Graphs and Tables              |     |

| DC Characteristics             | 121 |

| Development Support            | 113 |

| Device Differences             |     |

| Device Overview                | 5   |

| Features                       | 5   |

| Direct Addressing              | 27  |

|                                |     |

# Е

| Electrical Characteristics                                | Э |

|-----------------------------------------------------------|---|

| Errata                                                    | 4 |

| External Clock Input (RA4/T0CKI). See Timer0              |   |

| External Interrupt Input (RB0/INT). See Interrupt Sources |   |

|                                                           |   |

#

| FSR Register                         | 27  |

|--------------------------------------|-----|

| I                                    |     |

| I/O Ports                            | 31  |

| I <sup>2</sup> C Mode                |     |

| Addressing                           | 66  |

| Associated Registers                 |     |

| Master Mode                          |     |

| Mode Selection                       |     |

| Multi-Master Mode                    |     |

| Operation                            |     |

| Reception                            |     |

| Slave Mode                           |     |

| SCL and SDA pins                     | 65  |

| Transmission                         |     |

| ICEPIC In-Circuit Emulator           |     |

| ID Locations                         |     |

| In-Circuit Serial Programming (ICSP) |     |

| INDF Register                        |     |

| Indirect Addressing                  |     |

| FSR Register                         |     |

| Instruction Format                   |     |

| Instruction Set                      | 105 |

| ADDLW                                | 107 |

| ADDWF                                | 107 |

| ANDLW                                | 107 |

| ANDWF                                | 107 |

| BCF                                  | 107 |

| BSF                                  | 107 |

| BTFSC                                | 107 |

| BTFSS                                | 107 |

| CALL                                 | 108 |

| CLRF                                 | 108 |

| CLRW                                 | 108 |

|                                      |     |

| COMF                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| DECF                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| DECFSZ                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| INCF                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| INCFSZ                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| IORLW 109                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| IORWF                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| MOVF                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| MOVLW                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| NOVWF                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| RETFIE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| RETLW                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |