#### Welcome to E-XFL.COM

### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

### Details

| Details                    |                                                                          |

|----------------------------|--------------------------------------------------------------------------|

| Product Status             | Active                                                                   |

| Core Processor             | PIC                                                                      |

| Core Size                  | 8-Bit                                                                    |

| Speed                      | 20MHz                                                                    |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                                        |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                    |

| Number of I/O              | 22                                                                       |

| Program Memory Size        | 14KB (8K x 14)                                                           |

| Program Memory Type        | FLASH                                                                    |

| EEPROM Size                | -                                                                        |

| RAM Size                   | 368 x 8                                                                  |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 5.5V                                                                |

| Data Converters            | A/D 5x8b                                                                 |

| Oscillator Type            | External                                                                 |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                        |

| Mounting Type              | Through Hole                                                             |

| Package / Case             | 28-DIP (0.300", 7.62mm)                                                  |

| Supplier Device Package    | 28-SPDIP                                                                 |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16lf76-i-sp |

|                            |                                                                          |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

### TABLE 1-3:PIC16F74 AND PIC16F77 PINOUT DESCRIPTION

| OSC1/CLKI<br>OSC1<br>CLKI<br>OSC2/CLKO<br>OSC2<br>CLKO<br>MCLR/VPP<br>MCLR<br>VPP | 13 | 14<br>15 | 30<br>31 | 1        | ST/CMOS <sup>(4)</sup> | Oscillator crystal or external clock input.<br>Oscillator crystal input or external clock source input.<br>ST buffer when configured in RC mode. Otherwise<br>CMOS.<br>External clock source input. Always associated with pin |

|-----------------------------------------------------------------------------------|----|----------|----------|----------|------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| CLKI<br>OSC2/CLKO<br>OSC2<br>CLKO<br><u>MCLR/VPP</u><br>MCLR                      | 14 | 15       | 31       | I        |                        | Oscillator crystal input or external clock source input.<br>ST buffer when configured in RC mode. Otherwise<br>CMOS.<br>External clock source input. Always associated with pin                                                |

| OSC2/CLKO<br>OSC2<br>CLKO<br>MCLR/VPP<br>MCLR                                     | 14 | 15       | 31       |          |                        | CMOS.<br>External clock source input. Always associated with pin                                                                                                                                                               |

| OSC2/CLKO<br>OSC2<br>CLKO<br>MCLR/VPP<br>MCLR                                     | 14 | 15       | 31       |          |                        | External clock source input. Always associated with pin                                                                                                                                                                        |

| OSC2<br>CLKO<br>MCLR/VPP<br>MCLR                                                  | 14 | 15       | 31       |          |                        |                                                                                                                                                                                                                                |

| OSC2<br>CLKO<br>MCLR/VPP<br>MCLR                                                  | 14 | 15       | 31       | 0        |                        | function OSC1 (see OSC1/CLKI, OSC2/CLKO pins).                                                                                                                                                                                 |

| CLKO<br>MCLR/VPP<br>MCLR                                                          |    |          |          | <u> </u> | I —                    | Oscillator crystal or clock output.                                                                                                                                                                                            |

| MCLR/Vpp<br>MCLR                                                                  |    |          |          | 0        |                        | Oscillator crystal output.                                                                                                                                                                                                     |

| MCLR/Vpp<br>MCLR                                                                  |    |          |          |          |                        | Connects to crystal or resonator in Crystal Oscillator                                                                                                                                                                         |

| MCLR/Vpp<br>MCLR                                                                  |    |          |          |          |                        | mode.                                                                                                                                                                                                                          |

| MCLR                                                                              |    |          |          | 0        |                        | In RC mode, OSC2 pin outputs CLKO, which has 1/4                                                                                                                                                                               |

| MCLR                                                                              |    |          |          |          |                        | the frequency of OSC1 and denotes the instruction                                                                                                                                                                              |

| MCLR                                                                              |    |          |          |          |                        | cycle rate.                                                                                                                                                                                                                    |

|                                                                                   | 1  | 2        | 18       |          | ST                     | Master Clear (input) or programming voltage (output).                                                                                                                                                                          |

| Vpp                                                                               |    |          |          | I        |                        | Master Clear (Reset) input. This pin is an active low                                                                                                                                                                          |

| VPP                                                                               |    |          |          |          |                        | RESET to the device.                                                                                                                                                                                                           |

|                                                                                   |    |          |          | Р        |                        | Programming voltage input.                                                                                                                                                                                                     |

|                                                                                   |    |          |          |          |                        | PORTA is a bi-directional I/O port.                                                                                                                                                                                            |

| RA0/AN0                                                                           | 2  | 3        | 19       |          | TTL                    |                                                                                                                                                                                                                                |

| RA0                                                                               |    |          |          | I/O      |                        | Digital I/O.                                                                                                                                                                                                                   |

| AN0                                                                               |    |          |          | I        |                        | Analog input 0.                                                                                                                                                                                                                |

| RA1/AN1                                                                           | 3  | 4        | 20       |          | TTL                    |                                                                                                                                                                                                                                |

| RA1                                                                               |    |          |          | I/O      |                        | Digital I/O.                                                                                                                                                                                                                   |

| AN1                                                                               |    |          |          | I        |                        | Analog input 1.                                                                                                                                                                                                                |

| RA2/AN2                                                                           | 4  | 5        | 21       |          | TTL                    |                                                                                                                                                                                                                                |

| RA2                                                                               |    |          |          | I/O      |                        | Digital I/O.                                                                                                                                                                                                                   |

| AN2                                                                               |    |          |          | I        |                        | Analog input 2.                                                                                                                                                                                                                |

| RA3/AN3/Vref                                                                      | 5  | 6        | 22       |          | TTL                    |                                                                                                                                                                                                                                |

| RA3                                                                               |    |          |          | I/O      |                        | Digital I/O.                                                                                                                                                                                                                   |

| AN3                                                                               |    |          |          | I        |                        | Analog input 3.                                                                                                                                                                                                                |

| VREF                                                                              |    |          |          | I        |                        | A/D reference voltage input.                                                                                                                                                                                                   |

| RA4/T0CKI                                                                         | 6  | 7        | 23       |          | ST                     |                                                                                                                                                                                                                                |

| RA4                                                                               |    |          |          | I/O      |                        | Digital I/O – Open drain when configured as output.                                                                                                                                                                            |

| TOCKI                                                                             |    |          |          | I        |                        | Timer0 external clock input.                                                                                                                                                                                                   |

| RA5/SS/AN4                                                                        | 7  | 8        | 24       |          | TTL                    |                                                                                                                                                                                                                                |

| RA5                                                                               |    | -        |          | I/O      |                        | Digital I/O.                                                                                                                                                                                                                   |

| SS                                                                                | 1  |          |          | 1        |                        | SPI slave select input.                                                                                                                                                                                                        |

| AN4                                                                               |    |          |          |          | 1                      |                                                                                                                                                                                                                                |

| Legend: I = inpu                                                                  |    | 1        |          |          |                        | Analog input 4.                                                                                                                                                                                                                |

— = Not used TTL = TTL input ST = Schmitt Trigger input

**Note 1:** This buffer is a Schmitt Trigger input when configured as an external interrupt.

2: This buffer is a Schmitt Trigger input when used in Serial Programming mode.

**3:** This buffer is a Schmitt Trigger input when configured as general purpose I/O and a TTL input when used in the Parallel Slave Port mode (for interfacing to a microprocessor bus).

4: This buffer is a Schmitt Trigger input when configured in RC Oscillator mode and a CMOS input otherwise.

### 2.2.2.4 PIE1 Register

The PIE1 register contains the individual enable bits for the peripheral interrupts.

Note: Bit PEIE (INTCON<6>) must be set to enable any peripheral interrupt.

## REGISTER 2-4: PIE1 REGISTER (ADDRESS 8Ch)

|              |                        | •                             |               | •             |             |        |        |        |

|--------------|------------------------|-------------------------------|---------------|---------------|-------------|--------|--------|--------|

|              | R/W-0                  | R/W-0                         | R/W-0         | R/W-0         | R/W-0       | R/W-0  | R/W-0  | R/W-0  |

|              | PSPIE <sup>(1)</sup>   | ADIE                          | RCIE          | TXIE          | SSPIE       | CCP1IE | TMR2IE | TMR1IE |

|              | bit 7                  |                               |               |               |             |        |        | bit 0  |

|              |                        |                               |               |               |             |        |        |        |

| bit 7        | PSPIE <sup>(1)</sup> : | Parallel Slav                 | e Port Read   | d/Write Inter | rupt Enable | bit    |        |        |

|              | 1 = Enable             | es the PSP r                  | ead/write int | terrupt       |             |        |        |        |

|              | 0 = Disabl             | es the PSP                    | read/write in | terrupt       |             |        |        |        |

| bit 6        | ADIE: A/D              | Converter I                   | nterrupt Ena  | able bit      |             |        |        |        |

|              |                        | es the A/D co                 |               |               |             |        |        |        |

|              | 0 = Disabl             | es the A/D c                  | onverter inte | errupt        |             |        |        |        |

| bit 5        |                        | ART Receive                   | •             |               |             |        |        |        |

|              |                        | es the USAR                   |               |               |             |        |        |        |

|              |                        | es the USAF                   |               |               |             |        |        |        |

| bit 4        |                        | RT Transmi                    | -             |               |             |        |        |        |

|              |                        | es the USAR                   |               |               |             |        |        |        |

| <b>h</b> # 0 |                        | es the USAF                   |               |               | hla h:+     |        |        |        |

| bit 3        | •                      | nchronous S                   |               | iterrupt Ena  | DIE DIT     |        |        |        |

|              |                        | es the SSP in<br>es the SSP i |               |               |             |        |        |        |

| bit 2        |                        | CP1 Interru                   |               | i+            |             |        |        |        |

|              |                        | es the CCP1                   | •             | it i          |             |        |        |        |

|              |                        | es the CCP                    | •             |               |             |        |        |        |

| bit 1        |                        | MR2 to PR                     |               | rrupt Enable  | e bit       |        |        |        |

|              |                        | es the TMR2                   |               | •             |             |        |        |        |

|              |                        | es the TMR2                   |               |               |             |        |        |        |

| bit 0        | TMR1IE: T              | MR1 Overfl                    | ow Interrupt  | Enable bit    |             |        |        |        |

|              |                        | es the TMR1                   |               |               |             |        |        |        |

|              |                        | es the TMR'                   |               | •             |             |        |        |        |

|              |                        |                               |               |               |             |        |        |        |

Note 1: PSPIE is reserved on 28-pin devices; always maintain this bit clear.

| Legend:                  |                  |                      |                    |

|--------------------------|------------------|----------------------|--------------------|

| R = Readable bit         | W = Writable bit | U = Unimplemented    | bit, read as '0'   |

| - n = Value at POR reset | '1' = Bit is set | '0' = Bit is cleared | x = Bit is unknown |

# 4.0 I/O PORTS

Some pins for these I/O ports are multiplexed with an alternate function for the peripheral features on the device. In general, when a peripheral is enabled, that pin may not be used as a general purpose I/O pin.

Additional information on I/O ports may be found in the PICmicro<sup>™</sup> Mid-Range Reference Manual, (DS33023).

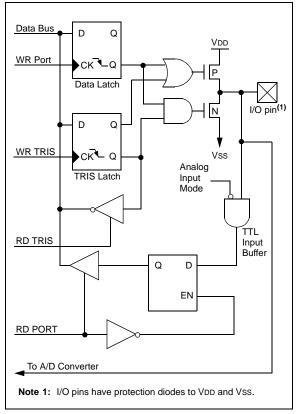

## 4.1 PORTA and the TRISA Register

PORTA is a 6-bit wide, bi-directional port. The corresponding data direction register is TRISA. Setting a TRISA bit (= '1') will make the corresponding PORTA pin an input (i.e., put the corresponding output driver in a Hi-Impedance mode). Clearing a TRISA bit (= '0') will make the corresponding PORTA pin an output (i.e., put the contents of the output latch on the selected pin).

Reading the PORTA register reads the status of the pins, whereas writing to it will write to the port latch. All write operations are read-modify-write operations. Therefore, a write to a port implies that the port pins are read, the value is modified and then written to the port data latch.

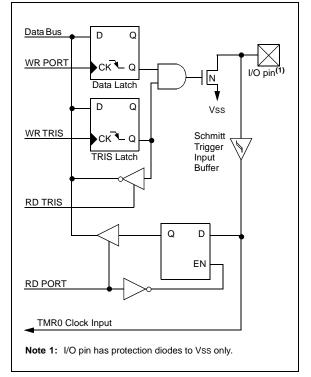

Pin RA4 is multiplexed with the Timer0 module clock input to become the RA4/T0CKI pin. The RA4/T0CKI pin is a Schmitt Trigger input and an open drain output. All other PORTA pins have TTL input levels and full CMOS output drivers.

Other PORTA pins are multiplexed with analog inputs and analog VREF input. The operation of each pin is selected by clearing/setting the control bits in the ADCON1 register (A/D Control Register1).

**Note:** On a Power-on Reset, these pins are configured as analog inputs and read as '0'.

The TRISA register controls the direction of the RA pins, even when they are being used as analog inputs. The user must ensure the bits in the TRISA register are maintained set, when using them as analog inputs.

| BCF<br>BCF<br>CLRF                      | STATUS,<br>STATUS,<br>PORTA                |     | ;<br>; Bank0<br>; Initialize PORTA by<br>; clearing output<br>: data latches | Y |

|-----------------------------------------|--------------------------------------------|-----|------------------------------------------------------------------------------|---|

| BSF<br>MOVLW<br>MOVWF<br>MOVLW<br>MOVWF | STATUS,<br>0x06<br>ADCON1<br>0xCF<br>TRISA | RPO | ,                                                                            |   |

### FIGURE 4-1:

### BLOCK DIAGRAM OF RA3:RA0 AND RA5 PINS

FIGURE 4-2:

### BLOCK DIAGRAM OF RA4/T0CKI PIN

# REGISTER 4-1: TRISE REGISTER (ADDRESS 89h)

|       |                         | •                                              |                                | ,                     |             |         |       |       |

|-------|-------------------------|------------------------------------------------|--------------------------------|-----------------------|-------------|---------|-------|-------|

|       | R-0                     | R-0                                            | R/W-0                          | R/W-0                 | U-0         | R/W-1   | R/W-1 | R/W-1 |

|       | IBF                     | OBF                                            | IBOV                           | PSPMODE               | —           | Bit2    | Bit1  | Bit0  |

|       | bit 7                   |                                                |                                |                       |             |         |       | bit 0 |

| bit 7 | Parallel S              | ave Port St                                    | atus/Contro                    | l bits:               |             |         |       |       |

|       |                         | Buffer Full S                                  |                                | <u></u>               |             |         |       |       |

|       |                         | l has been re<br>rd has been                   |                                | is waiting to be      | read by the | e CPU   |       |       |

| bit 6 | OBF: Outp               | out Buffer Fu                                  | ll Status bit                  |                       |             |         |       |       |

|       |                         | •                                              | till holds a pi<br>as been rea | reviously writte<br>d | n word      |         |       |       |

| bit 5 | IBOV: Inpu              | ut Buffer Ove                                  | erflow Detect                  | bit (in Micropro      | ocessor mo  | de)     |       |       |

|       | (must l                 | e occurred w<br>be cleared in<br>erflow occurr | software)                      | usly input word       | has not be  | en read |       |       |

| bit 4 | PSPMODE                 | E: Parallel SI                                 | ave Port Mo                    | de Select bit         |             |         |       |       |

|       | 1 = Paralle             | el Slave Port                                  | mode                           |                       |             |         |       |       |

|       | 0 = Genera              | al Purpose I/                                  | O mode                         |                       |             |         |       |       |

| bit 3 | Unimplem                | nented: Read                                   | d as '0'                       |                       |             |         |       |       |

| bit 2 | PORTE Da                | ata Directio                                   | n bits:                        |                       |             |         |       |       |

|       | Bit2: Direc             | tion Control                                   | bit for pin RE                 | E2/CS/AN7             |             |         |       |       |

|       | 1 = Input<br>0 = Output | t                                              |                                |                       |             |         |       |       |

| bit 1 | Bit1: Direc             | tion Control                                   | bit for pin RE                 | E1/WR/AN6             |             |         |       |       |

|       | 1 = Input<br>0 = Output | t                                              |                                |                       |             |         |       |       |

| bit 0 | Bit0: Direc             | tion Control                                   | bit for pin RE                 | E0/RD/AN5             |             |         |       |       |

|       | 1 = Input<br>0 = Output |                                                |                                |                       |             |         |       |       |

| Legend:                  |                  |                      |                    |

|--------------------------|------------------|----------------------|--------------------|

| R = Readable bit         | W = Writable bit | U = Unimplemented    | bit, read as '0'   |

| - n = Value at POR reset | '1' = Bit is set | '0' = Bit is cleared | x = Bit is unknown |

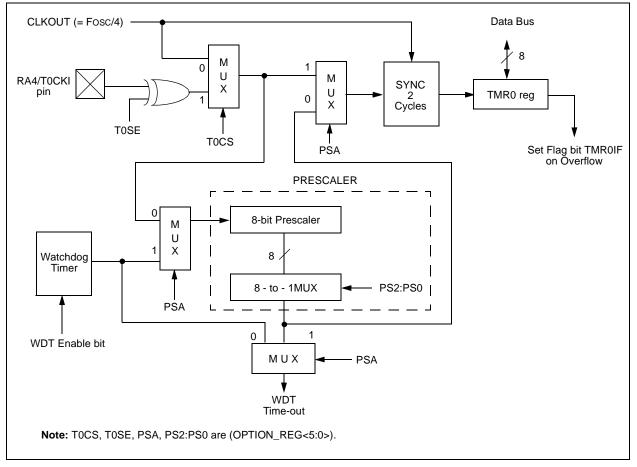

# 5.0 TIMER0 MODULE

The Timer0 module timer/counter has the following features:

- 8-bit timer/counter

- Readable and writable

- 8-bit software programmable prescaler

- · Internal or external clock select

- Interrupt on overflow from FFh to 00h

- Edge select for external clock

Additional information on the Timer0 module is available in the PICmicro<sup>™</sup> Mid-Range MCU Family Reference Manual (DS33023).

Figure 5-1 is a block diagram of the Timer0 module and the prescaler shared with the WDT.

Timer0 operation is controlled through the OPTION\_REG register (Register 5-1 on the following page). Timer mode is selected by clearing bit TOCS (OPTION\_REG<5>). In Timer mode, the Timer0 module will increment every instruction cycle (without prescaler). If the TMR0 register is written, the increment is inhibited for the following two instruction cycles. The user can work around this by writing an adjusted value to the TMR0 register.

Counter mode is selected by setting bit T0CS (OPTION\_REG<5>). In Counter mode, Timer0 will increment, either on every rising or falling edge of pin RA4/T0CKI. The incrementing edge is determined by the Timer0 Source Edge Select bit T0SE (OPTION\_REG<4>). Clearing bit T0SE selects the rising edge. Restrictions on the external clock input are discussed in detail in Section 5.2.

The prescaler is mutually exclusively shared between the Timer0 module and the Watchdog Timer. The prescaler is not readable or writable. Section 5.3 details the operation of the prescaler.

### 5.1 Timer0 Interrupt

The TMR0 interrupt is generated when the TMR0 register overflows from FFh to 00h. This overflow sets bit TMR0IF (INTCON<2>). The interrupt can be masked by clearing bit TMR0IE (INTCON<5>). Bit TMR0IF must be cleared in software by the Timer0 module Interrupt Service Routine, before re-enabling this interrupt. The TMR0 interrupt cannot awaken the processor from SLEEP, since the timer is shut-off during SLEEP.

NOTES:

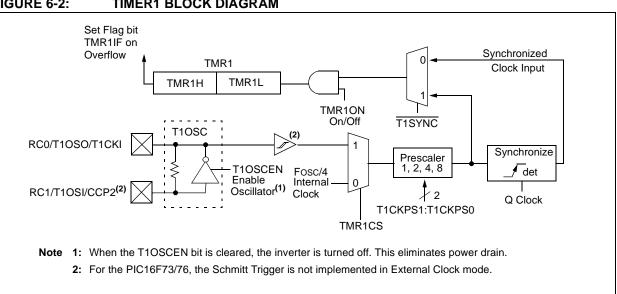

#### 6.1 **Timer1 Operation in Timer Mode**

Timer mode is selected by clearing the TMR1CS (T1CON<1>) bit. In this mode, the input clock to the timer is Fosc/4. The synchronize control bit T1SYNC (T1CON<2>) has no effect, since the internal clock is always in sync.

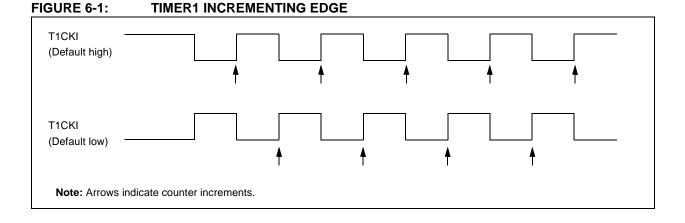

#### 6.2 **Timer1 Counter Operation**

Timer1 may operate in Asynchronous or Synchronous mode, depending on the setting of the TMR1CS bit.

When Timer1 is being incremented via an external source, increments occur on a rising edge. After Timer1 is enabled in Counter mode, the module must first have a falling edge before the counter begins to increment.

#### 6.3 **Timer1 Operation in Synchronized Counter Mode**

Counter mode is selected by setting bit TMR1CS. In this mode, the timer increments on every rising edge of clock input on pin RC1/T1OSI/CCP2, when bit T1OSCEN is set, or on pin RC0/T1OSO/T1CKI, when bit T1OSCEN is cleared.

If TISYNC is cleared, then the external clock input is synchronized with internal phase clocks. The synchronization is done after the prescaler stage. The prescaler stage is an asynchronous ripple counter.

In this configuration, during SLEEP mode, Timer1 will not increment even if the external clock is present, since the synchronization circuit is shut-off. The prescaler, however, will continue to increment.

#### FIGURE 6-2: TIMER1 BLOCK DIAGRAM

| REGISTER 7-1: | T2CON:          | TIMER2 C                                             |             | EGISTER (    | ADDRESS    | 12h)        |                |          |  |

|---------------|-----------------|------------------------------------------------------|-------------|--------------|------------|-------------|----------------|----------|--|

|               | U-0             | R/W-0                                                | R/W-0       | R/W-0        | R/W-0      | R/W-0       | R/W-0          | R/W-0    |  |

|               | _               | TOUTPS3                                              | TOUTPS2     | TOUTPS1      | TOUTPS0    | TMR2ON      | T2CKPS1        | T2CKPS0  |  |

|               | bit 7           |                                                      |             |              |            |             |                | bit 0    |  |

| bit 7         | Unimplo         | montod: Por                                          | nd as '0'   |              |            |             |                |          |  |

|               | -               | Unimplemented: Read as '0'                           |             |              |            |             |                |          |  |

| bit 6-3       |                 | TOUTPS3:TOUTPS0: Timer2 Output Postscale Select bits |             |              |            |             |                |          |  |

|               |                 | :1 Postscale<br>:2 Postscale                         |             |              |            |             |                |          |  |

|               |                 | :3 Postscale                                         |             |              |            |             |                |          |  |

|               | •               | .01000000                                            |             |              |            |             |                |          |  |

|               | •               |                                                      |             |              |            |             |                |          |  |

|               | •               |                                                      |             |              |            |             |                |          |  |

|               | 1111 <b>= 1</b> | :16 Postscale                                        | Э           |              |            |             |                |          |  |

| bit 2         | TMR2ON          | I: Timer2 On                                         | bit         |              |            |             |                |          |  |

|               | 1 = Timei       |                                                      |             |              |            |             |                |          |  |

|               | 0 = Timei       |                                                      |             |              |            |             |                |          |  |

| bit 1-0       | T2CKPS          | 1:T2CKPS0:                                           | Timer2 Cloc | k Prescale S | elect bits |             |                |          |  |

|               |                 | scaler is 1                                          |             |              |            |             |                |          |  |

|               |                 | scaler is 4                                          |             |              |            |             |                |          |  |

|               | 1x = Pres       | scaler is 16                                         |             |              |            |             |                |          |  |

|               | Legend:         |                                                      |             |              |            |             |                |          |  |

|               | R = Reada       | ahle hit                                             | M - M       | /ritable bit | II – Unim  | olemented I | oit, read as ' | 0'       |  |

|               | 1. – 1.caua     |                                                      | vv — v      |              | 0 - 01111  | siomonicui  | 51, 1000 05    | <b>°</b> |  |

## TABLE 7-1: REGISTERS ASSOCIATED WITH TIMER2 AS A TIMER/COUNTER

- n = Value at POR reset

| Address                | Name   | Bit 7                | Bit 6                 | Bit 5   | Bit 4   | Bit 3   | Bit 2  | Bit 1   | Bit 0   | Value<br>PC<br>BC | R,   |      | e on<br>other<br>iETS |

|------------------------|--------|----------------------|-----------------------|---------|---------|---------|--------|---------|---------|-------------------|------|------|-----------------------|

| 0Bh,8Bh,<br>10Bh, 18Bh | INTCON | GIE                  | PEIE                  | TMR0IE  | INTE    | RBIE    | TMR0IF | INTF    | RBIF    | 0000              | 000x | 0000 | 000u                  |

| 0Ch                    | PIR1   | PSPIF <sup>(1)</sup> | ADIF                  | RCIF    | TXIF    | SSPIF   | CCP1IF | TMR2IF  | TMR1IF  | 0000              | 0000 | 0000 | 0000                  |

| 8Ch                    | PIE1   | PSPIE <sup>(1)</sup> | ADIE                  | RCIE    | TXIE    | SSPIE   | CCP1IE | TMR2IE  | TMR1IE  | 0000              | 0000 | 0000 | 0000                  |

| 11h                    | TMR2   | Timer2 M             | ïmer2 Module Register |         |         |         |        |         |         | 0000              | 0000 | 0000 | 0000                  |

| 12h                    | T2CON  |                      | TOUTPS3               | TOUTPS2 | TOUTPS1 | TOUTPS0 | TMR2ON | T2CKPS1 | T2CKPS0 | -000              | 0000 | -000 | 0000                  |

| 92h                    | PR2    | Timer2 Pe            | ïmer2 Period Register |         |         |         |        |         |         | 1111              | 1111 | 1111 | 1111                  |

'1' = Bit is set

'0' = Bit is cleared

Legend: x = unknown, u = unchanged, - = unimplemented, read as '0'. Shaded cells are not used by the Timer2 module.

Note 1: Bits PSPIE and PSPIF are reserved on the PIC16F73/76; always maintain these bits clear.

x = Bit is unknown

# REGISTER 8-1: CCP1CON REGISTER/CCP2CON REGISTER (ADDRESS: 17h/1Dh)

| bit 7-6                                                                                          | U-0<br>—                                                                                                                                                                                     | U-0            | R/W-0<br>CCPxX | R/W-0        | R/W-0       | R/W-0  | R/W-0  | R/W-0  |  |  |  |

|--------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------|----------------|--------------|-------------|--------|--------|--------|--|--|--|

| bit 7-6                                                                                          | —<br>bit 7                                                                                                                                                                                   | _              | CCDvV          |              |             |        |        |        |  |  |  |

| Dit 7-6                                                                                          | bit 7                                                                                                                                                                                        |                | COFXA          | CCPxY        | CCPxM3      | CCPxM2 | CCPxM1 | CCPxM0 |  |  |  |

| bit 5-4 ()<br>()<br>()<br>()<br>()<br>()<br>()<br>()<br>()<br>()<br>()<br>()<br>()<br>(          |                                                                                                                                                                                              |                |                |              |             |        |        | bit 0  |  |  |  |

| ()<br>()<br>()<br>()<br>()<br>()<br>()<br>()<br>()<br>()<br>()<br>()<br>()<br>(                  | Unimplem                                                                                                                                                                                     | ented: Rea     | ad as '0'      |              |             |        |        |        |  |  |  |

| 1<br>1<br>1<br>2<br>2<br>2<br>2<br>1<br>2<br>1<br>2<br>1<br>1<br>1<br>1<br>1<br>1<br>1<br>1<br>1 | CCPxX:CC                                                                                                                                                                                     | PxY: PWN       | l Least Signi  | ficant bits  |             |        |        |        |  |  |  |

| bit 3-0                                                                                          | <u>Capture mode:</u><br>Unused<br><u>Compare mode:</u><br>Unused                                                                                                                             |                |                |              |             |        |        |        |  |  |  |

| -<br>bit 3-0                                                                                     |                                                                                                                                                                                              |                |                |              |             |        |        |        |  |  |  |

| bit 3-0                                                                                          | PWM mode                                                                                                                                                                                     | <del>)</del> : |                |              |             |        |        |        |  |  |  |

|                                                                                                  | These bits are the two LSbs of the PWM duty cycle. The eight MSbs are found in CCPR                                                                                                          |                |                |              |             |        |        |        |  |  |  |

| ,                                                                                                | t 3-0 CCPxM3:CCPxM0: CCPx Mode Select bits                                                                                                                                                   |                |                |              |             |        |        |        |  |  |  |

|                                                                                                  | 0000 <b>= Ca</b>                                                                                                                                                                             | oture/Comp     | oare/PWM di    | sabled (rese | ets CCPx mo | odule) |        |        |  |  |  |

|                                                                                                  |                                                                                                                                                                                              |                | , every fallin |              |             |        |        |        |  |  |  |

| (                                                                                                | 0101 <b>= Ca</b>                                                                                                                                                                             | pture mode     | , every rising | g edge       |             |        |        |        |  |  |  |

| (                                                                                                | 0110 <b>= Ca</b>                                                                                                                                                                             | pture mode     | , every 4th r  | ising edge   |             |        |        |        |  |  |  |

|                                                                                                  | 0111 = Capture mode, every 16th rising edge                                                                                                                                                  |                |                |              |             |        |        |        |  |  |  |

|                                                                                                  | 1000 = Compare mode, set output on match (CCPxIF bit is set)                                                                                                                                 |                |                |              |             |        |        |        |  |  |  |

|                                                                                                  | 1001 = Compare mode, clear output on match (CCPxIF bit is set)                                                                                                                               |                |                |              |             |        |        |        |  |  |  |

| -                                                                                                | 1010 = Compare mode, generate software interrupt on match (CCPxIF bit is set, CCPx pin is unaffected)                                                                                        |                |                |              |             |        |        |        |  |  |  |

| :                                                                                                | 1011 = Compare mode, trigger special event (CCPxIF bit is set, CCPx pin is unaffected);<br>CCP1 clears Timer1; CCP2 clears Timer1 and starts an A/D conversion (if A/D module<br>is enabled) |                |                |              |             |        |        |        |  |  |  |

| :                                                                                                | 11xx = PW                                                                                                                                                                                    | /M mode        |                |              |             |        |        |        |  |  |  |

|                                                                                                  |                                                                                                                                                                                              |                |                |              |             |        |        |        |  |  |  |

|                                                                                                  | Legend:                                                                                                                                                                                      |                |                |              |             |        |        |        |  |  |  |

| Legend:                  |                  |                      |                    |

|--------------------------|------------------|----------------------|--------------------|

| R = Readable bit         | W = Writable bit | U = Unimplemented    | l bit, read as '0' |

| - n = Value at POR reset | '1' = Bit is set | '0' = Bit is cleared | x = Bit is unknown |

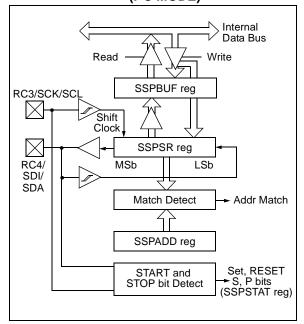

# 9.3 SSP I<sup>2</sup>C Operation

The SSP module in  $l^2C$  mode, fully implements all slave functions, except general call support, and provides interrupts on START and STOP bits in hardware to facilitate firmware implementations of the master functions. The SSP module implements the standard mode specifications as well as 7-bit and 10-bit addressing.

Two pins are used for data transfer. These are the RC3/ SCK/SCL pin, which is the clock (SCL), and the RC4/ SDI/SDA pin, which is the data (SDA). The user must configure these pins as inputs or outputs through the TRISC<4:3> bits.

The SSP module functions are enabled by setting SSP enable bit SSPEN (SSPCON<5>).

FIGURE 9-5: SSP BLOCK DIAGRAM (I<sup>2</sup>C MODE)

The SSP module has five registers for  $\mathsf{I}^2\mathsf{C}$  operation. These are the:

- SSP Control Register (SSPCON)

- SSP Status Register (SSPSTAT)

- Serial Receive/Transmit Buffer (SSPBUF)

- SSP Shift Register (SSPSR) Not directly accessible

- SSP Address Register (SSPADD)

The SSPCON register allows control of the  $I^2C$  operation. Four mode selection bits (SSPCON<3:0>) allow one of the following  $I^2C$  modes to be selected:

- I<sup>2</sup>C Slave mode (7-bit address)

- I<sup>2</sup>C Slave mode (10-bit address)

- I<sup>2</sup>C Slave mode (7-bit address), with START and STOP bit interrupts enabled to support Firmware Master mode

- I<sup>2</sup>C Slave mode (10-bit address), with START and STOP bit interrupts enabled to support Firmware Master mode

- I<sup>2</sup>C START and STOP bit interrupts enabled to support Firmware Master mode, Slave is IDLE

Selection of any  $I^2C$  mode with the SSPEN bit set, forces the SCL and SDA pins to be open drain, provided these pins are programmed to inputs by setting the appropriate TRISC bits. Pull-up resistors must be provided externally to the SCL and SDA pins for proper operation of the  $I^2C$  module.

Additional information on SSP I<sup>2</sup>C operation can be found in the PICmicro<sup>™</sup> Mid-Range MCU Family Reference Manual (DS33023A).

### 9.3.1 SLAVE MODE

In Slave mode, the SCL and SDA pins must be configured as inputs (TRISC<4:3> set). The SSP module will override the input state with the output data when required (slave-transmitter).

When an address is matched, or the data transfer after an address match is received, the hardware automatically will generate the Acknowledge ( $\overline{ACK}$ ) pulse, and then load the SSPBUF register with the received value currently in the SSPSR register.

There are certain conditions that will cause the SSP module not to give this ACK pulse. They include (either or both):

- a) The buffer full bit BF (SSPSTAT<0>) was set before the transfer was received.

- b) The overflow bit SSPOV (SSPCON<6>) was set before the transfer was received.

In this case, the SSPSR register value is not loaded into the SSPBUF, but bit SSPIF (PIR1<3>) is set. Table 9-2 shows what happens when a data transfer byte is received, given the status of bits BF and SSPOV. The shaded cells show the condition where user software did not properly clear the overflow condition. Flag bit BF is cleared by reading the SSPBUF register, while bit SSPOV is cleared through software.

The SCL clock input must have a minimum high and low for proper operation. The high and low times of the  $I^2C$  specification, as well as the requirements of the SSP module, are shown in timing parameter #100 and parameter #101.

| MOVF             | Move f                                                                                                                                                                                                                                                                            |

|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [ <i>label</i> ] MOVF f,d                                                                                                                                                                                                                                                         |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ d \in \ [0,1] \end{array}$                                                                                                                                                                                                                 |

| Operation:       | (f) $\rightarrow$ (destination)                                                                                                                                                                                                                                                   |

| Status Affected: | Z                                                                                                                                                                                                                                                                                 |

| Description:     | The contents of register f are<br>moved to a destination dependant<br>upon the status of d. If $d = 0$ ,<br>destination is W register. If $d = 1$ ,<br>the destination is file register f itself.<br>d = 1 is useful to test a file register,<br>since status flag Z is affected. |

| NOP              | No Operation  |

|------------------|---------------|

| Syntax:          | [label] NOP   |

| Operands:        | None          |

| Operation:       | No operation  |

| Status Affected: | None          |

| Description:     | No operation. |

| MOVLW            | Move Literal to W                                                                          |  |  |  |  |

|------------------|--------------------------------------------------------------------------------------------|--|--|--|--|

| Syntax:          | [ <i>label</i> ] MOVLW k                                                                   |  |  |  |  |

| Operands:        | $0 \le k \le 255$                                                                          |  |  |  |  |

| Operation:       | $k \rightarrow (W)$                                                                        |  |  |  |  |

| Status Affected: | None                                                                                       |  |  |  |  |

| Description:     | The eight-bit literal 'k' is loaded into W register. The don't cares will assemble as 0's. |  |  |  |  |

| RETFIE           | Return from Interrupt                                   |  |  |  |  |

|------------------|---------------------------------------------------------|--|--|--|--|

| Syntax:          | [label] RETFIE                                          |  |  |  |  |

| Operands:        | None                                                    |  |  |  |  |

| Operation:       | $\begin{array}{l} TOS \to PC, \\ 1 \to GIE \end{array}$ |  |  |  |  |

| Status Affected: | None                                                    |  |  |  |  |

| MOVWF            | Move W to f                                   |  |  |  |  |

|------------------|-----------------------------------------------|--|--|--|--|

| Syntax:          | [ label ] MOVWF f                             |  |  |  |  |

| Operands:        | $0 \le f \le 127$                             |  |  |  |  |

| Operation:       | $(W) \rightarrow (f)$                         |  |  |  |  |

| Status Affected: | None                                          |  |  |  |  |

| Description:     | Move data from W register to<br>register 'f'. |  |  |  |  |

| RETLW            | Return with Literal in W                                                                                                                                                            |  |  |  |  |  |

|------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| Syntax:          | [ <i>label</i> ] RETLW k                                                                                                                                                            |  |  |  |  |  |

| Operands:        | $0 \le k \le 255$                                                                                                                                                                   |  |  |  |  |  |

| Operation:       | $k \rightarrow (W);$<br>TOS $\rightarrow PC$                                                                                                                                        |  |  |  |  |  |

| Status Affected: | None                                                                                                                                                                                |  |  |  |  |  |

| Description:     | The W register is loaded with the<br>eight-bit literal 'k'. The program<br>counter is loaded from the top of<br>the stack (the return address).<br>This is a two-cycle instruction. |  |  |  |  |  |

# **15.0 ELECTRICAL CHARACTERISTICS**

### Absolute Maximum Ratings †

| Ambient temperature under bias                                                                                                                                         | 55 to +125°C                          |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------|

| Storage temperature                                                                                                                                                    |                                       |

| Voltage on any pin with respect to Vss (except VDD, MCLR. and RA4)                                                                                                     |                                       |

| Voltage on VDD with respect to Vss                                                                                                                                     |                                       |

| Voltage on MCLR with respect to Vss (Note 2)                                                                                                                           |                                       |

| Voltage on RA4 with respect to Vss                                                                                                                                     |                                       |

| Total power dissipation (Note 1)                                                                                                                                       |                                       |

| Maximum current out of Vss pin                                                                                                                                         |                                       |

| Maximum current into VDD pin                                                                                                                                           |                                       |

| Input clamp current, Iк (Vi < 0 or Vi > VDD)                                                                                                                           |                                       |

| Output clamp current, loк (Vo < 0 or Vo > Voo)                                                                                                                         |                                       |

| Maximum output current sunk by any I/O pin                                                                                                                             |                                       |

| Maximum output current sourced by any I/O pin                                                                                                                          |                                       |

| Maximum current sunk by PORTA, PORTB, and PORTE (combined) (Note 3)                                                                                                    | 200 mA                                |

| Maximum current sourced by PORTA, PORTB, and PORTE (combined) (Note 3)                                                                                                 |                                       |

| Maximum current sunk by PORTC and PORTD (combined) (Note 3)                                                                                                            | 200 mA                                |

| Maximum current sourced by PORTC and PORTD (combined) (Note 3)                                                                                                         |                                       |

| <b>Note 1:</b> Power dissipation is calculated as follows: Pdis = VDD x {IDD - $\sum$ IOH} + $\sum$ {(VDD - V                                                          | $√$ ОН) x IOH} + $\Sigma$ (VOI x IOL) |

| <ol> <li>Voltage spikes at the MCLR pin may cause latchup. A series resistor of greater the to pull MCLR to VDD, rather than tying the pin directly to VDD.</li> </ol> | nan 1 k $\Omega$ should be used       |

3: PORTD and PORTE are not implemented on the PIC16F73/76 devices.

† NOTICE: Stresses above those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress rating only and functional operation of the device at those or any other conditions above those indicated in the operation listings of this specification is not implied. Exposure to maximum rating conditions for extended periods may affect device reliability.

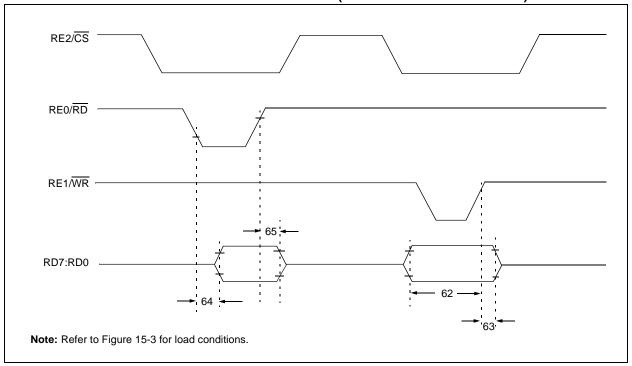

### TABLE 15-6: PARALLEL SLAVE PORT REQUIREMENTS (PIC16F74/77 DEVICES ONLY)

| Parameter<br>No. | Symbol   | Characteristic                                                            |                                               |          | Тур† | Max      | Units    | Conditions          |

|------------------|----------|---------------------------------------------------------------------------|-----------------------------------------------|----------|------|----------|----------|---------------------|

| 62               | TdtV2wrH | Data in valid before WR↑ or CS1                                           | `(setup time)                                 | 20<br>25 | _    | _        | ns<br>ns | Extended range only |

| 63*              | TwrH2dtl | ₩R↑ or CS↑ to data in invalid<br>(hold time)                              | Standard( <b>F</b> )<br>Extended( <b>LF</b> ) | 20<br>35 |      |          | ns<br>ns |                     |

| 64               | TrdL2dtV | $\overline{RD}\downarrow$ and $\overline{CS}\downarrow$ to data out valid |                                               |          |      | 80<br>90 | ns<br>ns | Extended range only |

| 65               | TrdH2dtl | $\overline{RD}$ or $\overline{CS}$ to data out invalid                    |                                               | 10       | —    | 30       | ns       |                     |

\* These parameters are characterized but not tested.

† Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

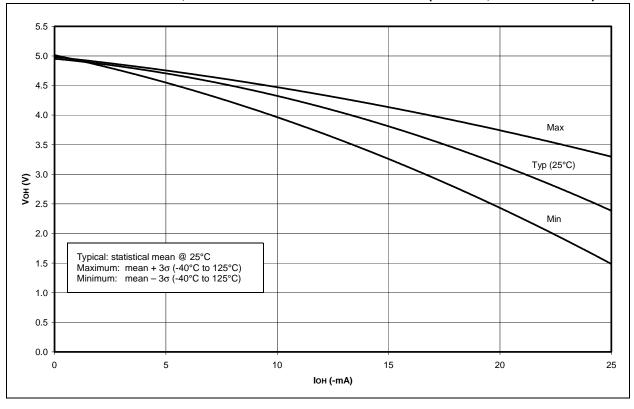

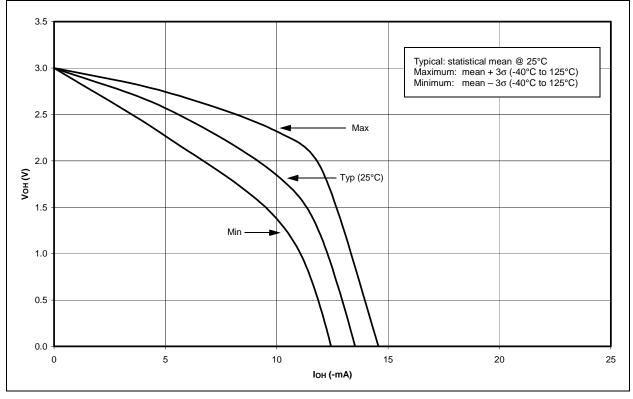

FIGURE 16-15: TYPICAL, MINIMUM AND MAXIMUM VOH vs. IOH (VDD = 5V, -40°C TO 125°C)

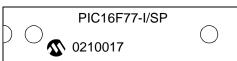

# 17.0 PACKAGING INFORMATION

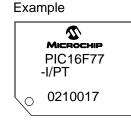

## 17.1 Package Marking Information

### 28-Lead SOIC

Example

### Example

### 28-Lead SSOP

28-Lead MLF

### Example

### Example

| Legend | I: XXX<br>Y<br>YY<br>WW<br>NNN | Customer specific information*<br>Year code (last digit of calendar year)<br>Year code (last 2 digits of calendar year)<br>Week code (week of January 1 is week '01')<br>Alphanumeric traceability code |

|--------|--------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Note:  | be carried                     | nt the full Microchip part number cannot be marked on one line, it will<br>over to the next line thus limiting the number of available characters<br>her specific information.                          |

\* Standard PICmicro device marking consists of Microchip part number, year code, week code, and traceability code. For PICmicro device marking beyond this, certain price adders apply. Please check with your Microchip Sales Office. For QTP devices, any special marking adders are included in QTP price.

# Package Marking Information (Cont'd)

### 44-Lead TQFP

Example

Ο

PIC16F77-I/P

0210017

### 44-Lead PLCC

Example

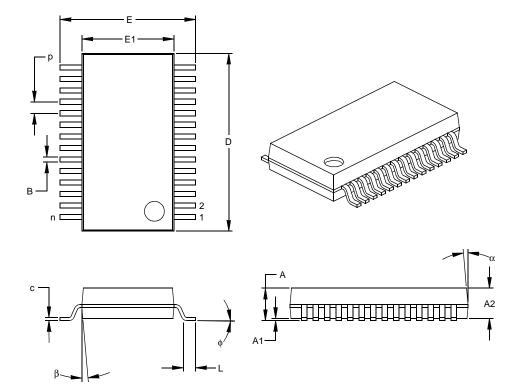

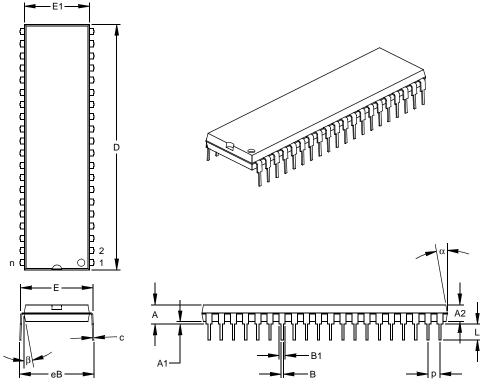

# 28-Lead Plastic Shrink Small Outline (SS) – 209 mil, 5.30 mm (SSOP)

| Units    |                                                                                                                                                                       | INCHES                                                                                                                                                                                                                                                                                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | N                                                      | <b>IILLIMETERS</b>                                     | S*                                                     |

|----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------|--------------------------------------------------------|--------------------------------------------------------|

| n Limits | MIN                                                                                                                                                                   | NOM                                                                                                                                                                                                                                                                                                                          | MAX                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | MIN                                                    | NOM                                                    | MAX                                                    |

| n        |                                                                                                                                                                       | 28                                                                                                                                                                                                                                                                                                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                        | 28                                                     |                                                        |

| р        |                                                                                                                                                                       | .026                                                                                                                                                                                                                                                                                                                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                        | 0.65                                                   |                                                        |

| А        | .068                                                                                                                                                                  | .073                                                                                                                                                                                                                                                                                                                         | .078                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 1.73                                                   | 1.85                                                   | 1.98                                                   |

| A2       | .064                                                                                                                                                                  | .068                                                                                                                                                                                                                                                                                                                         | .072                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 1.63                                                   | 1.73                                                   | 1.83                                                   |

| A1       | .002                                                                                                                                                                  | .006                                                                                                                                                                                                                                                                                                                         | .010                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 0.05                                                   | 0.15                                                   | 0.25                                                   |

| Е        | .299                                                                                                                                                                  | .309                                                                                                                                                                                                                                                                                                                         | .319                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 7.59                                                   | 7.85                                                   | 8.10                                                   |