Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                    |

|----------------------------|---------------------------------------------------------------------------|

| Core Processor             | PIC                                                                       |

| Core Size                  | 8-Bit                                                                     |

| Speed                      | 20MHz                                                                     |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                                         |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                     |

| Number of I/O              | 22                                                                        |

| Program Memory Size        | 14KB (8K x 14)                                                            |

| Program Memory Type        | FLASH                                                                     |

| EEPROM Size                | -                                                                         |

| RAM Size                   | 368 x 8                                                                   |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 5.5V                                                                 |

| Data Converters            | A/D 5x8b                                                                  |

| Oscillator Type            | External                                                                  |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                         |

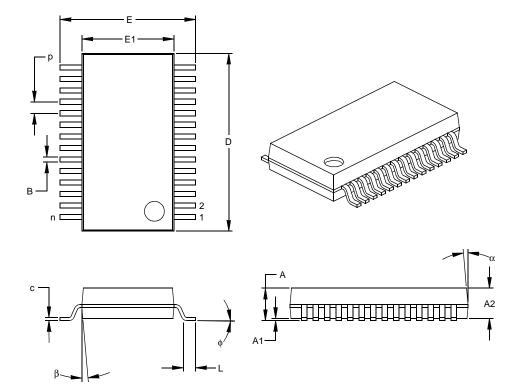

| Mounting Type              | Surface Mount                                                             |

| Package / Case             | 28-SSOP (0.209", 5.30mm Width)                                            |

| Supplier Device Package    | 28-SSOP                                                                   |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16lf76t-i-ss |

|                            |                                                                           |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

PIC16F7X

# 28/40-Pin 8-Bit CMOS FLASH Microcontrollers

### **Devices Included in this Data Sheet:**

- PIC16F73PIC16F74

- PIC16F76PIC16F77

### **High Performance RISC CPU:**

- High performance RISC CPU

- Only 35 single word instructions to learn

- All single cycle instructions except for program branches which are two-cycle

- Operating speed: DC 20 MHz clock input DC - 200 ns instruction cycle

- Up to 8K x 14 words of FLASH Program Memory, Up to 368 x 8 bytes of Data Memory (RAM)

- Pinout compatible to the PIC16C73B/74B/76/77

- Pinout compatible to the PIC16F873/874/876/877

- Interrupt capability (up to 12 sources)

- Eight level deep hardware stack

- Direct, Indirect and Relative Addressing modes

- Processor read access to program memory

### **Special Microcontroller Features:**

- Power-on Reset (POR)

- Power-up Timer (PWRT) and Oscillator Start-up Timer (OST)

- Watchdog Timer (WDT) with its own on-chip RC oscillator for reliable operation

- Programmable code protection

- Power saving SLEEP mode

- Selectable oscillator options

- In-Circuit Serial Programming<sup>™</sup> (ICSP<sup>™</sup>) via two pins

### **Peripheral Features:**

- Timer0: 8-bit timer/counter with 8-bit prescaler

- Timer1: 16-bit timer/counter with prescaler, can be incremented during SLEEP via external crystal/clock

- Timer2: 8-bit timer/counter with 8-bit period register, prescaler and postscaler

- Two Capture, Compare, PWM modules

- Capture is 16-bit, max. resolution is 12.5 ns

- Compare is 16-bit, max. resolution is 200 ns

PWM max. resolution is 10-bit

- 8-bit, up to 8-channel Analog-to-Digital converter

- Synchronous Serial Port (SSP) with SPI™ (Master mode) and I<sup>2</sup>C<sup>™</sup> (Slave)

- Universal Synchronous Asynchronous Receiver Transmitter (USART/SCI)

- Parallel Slave Port (PSP), 8-bits wide with external RD, WR and CS controls (40/44-pin only)

- Brown-out detection circuitry for Brown-out Reset (BOR)

### **CMOS Technology:**

- Low power, high speed CMOS FLASH technology

- Fully static design

- Wide operating voltage range: 2.0V to 5.5V

- High Sink/Source Current: 25 mA

- Industrial temperature range

- Low power consumption:

- < 2 mA typical @ 5V, 4 MHz

- 20 μA typical @ 3V, 32 kHz

- < 1 µA typical standby current

|          | Program Memory Data             |                 | Q   | 8-bit      | CCD | SS           | P               |                             | Timers |          |  |

|----------|---------------------------------|-----------------|-----|------------|-----|--------------|-----------------|-----------------------------|--------|----------|--|

| Device   | (# Single Word<br>Instructions) | SRAM<br>(Bytes) | I/O | Interrunts |     | CCP<br>(PWM) | SPI<br>(Master) | l <sup>2</sup> C<br>(Slave) | USART  | 8/16-bit |  |

| PIC16F73 | 4096                            | 192             | 22  | 11         | 5   | 2            | Yes             | Yes                         | Yes    | 2 / 1    |  |

| PIC16F74 | 4096                            | 192             | 33  | 12         | 8   | 2            | Yes             | Yes                         | Yes    | 2/1      |  |

| PIC16F76 | 8192                            | 368             | 22  | 11         | 5   | 2            | Yes             | Yes                         | Yes    | 2 / 1    |  |

| PIC16F77 | 8192                            | 368             | 33  | 12         | 8   | 2            | Yes             | Yes                         | Yes    | 2 / 1    |  |

### **Table of Contents**

| 1.0   | Device Overview                                                 | 5 |

|-------|-----------------------------------------------------------------|---|

| 2.0   | Device Overview                                                 | 3 |

| 3.0   | Reading Program Memory                                          | 9 |

| 4.0   | I/O Ports                                                       |   |

| 5.0   | Timer0 Module                                                   | 3 |

| 6.0   | Timer1 Module                                                   | 7 |

| 7.0   | Timer2 Module                                                   | 1 |

| 8.0   | Capture/Compare/PWM Modules                                     | 3 |

| 9.0   | Synchronous Serial Port (SSP) Module                            | 9 |

| 10.0  | Universal Synchronous Asynchronous Receiver Transmitter (USART) |   |

| 11.0  | Analog-to-Digital Converter (A/D) Module                        |   |

| 12.0  | Special Features of the CPU                                     | 9 |

| 13.0  | Instruction Set Summary 109                                     | 5 |

| 14.0  | Development Support                                             |   |

| 15.0  | Electrical Characteristics                                      | 9 |

| 16.0  | DC and AC Characteristics Graphs and Tables                     | 1 |

| 17.0  | Packaging Information 15                                        | 1 |

| Apper | ndix A: Revision History                                        | 1 |

|       | ndix B: Device Differences                                      |   |

| Apper | ndix C: Conversion Considerations                               | 2 |

| Index |                                                                 | 3 |

| On-Li | ne Support                                                      | 9 |

|       | er Response                                                     |   |

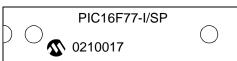

| PIC16 | F7X Product Identification System                               | 1 |

# TO OUR VALUED CUSTOMERS

It is our intention to provide our valued customers with the best documentation possible to ensure successful use of your Microchip products. To this end, we will continue to improve our publications to better suit your needs. Our publications will be refined and enhanced as new volumes and updates are introduced.

If you have any questions or comments regarding this publication, please contact the Marketing Communications Department via E-mail at **docerrors@mail.microchip.com** or fax the **Reader Response Form** in the back of this data sheet to (480) 792-4150. We welcome your feedback.

### Most Current Data Sheet

To obtain the most up-to-date version of this data sheet, please register at our Worldwide Web site at:

http://www.microchip.com

You can determine the version of a data sheet by examining its literature number found on the bottom outside corner of any page. The last character of the literature number is the version number, (e.g., DS30000A is version A of document DS30000).

### Errata

An errata sheet, describing minor operational differences from the data sheet and recommended workarounds, may exist for current devices. As device/documentation issues become known to us, we will publish an errata sheet. The errata will specify the revision of silicon and revision of document to which it applies.

To determine if an errata sheet exists for a particular device, please check with one of the following:

- Microchip's Worldwide Web site; http://www.microchip.com

- Your local Microchip sales office (see last page)

- The Microchip Corporate Literature Center; U.S. FAX: (480) 792-7277

When contacting a sales office or the literature center, please specify which device, revision of silicon and data sheet (include literature number) you are using.

### **Customer Notification System**

Register on our web site at www.microchip.com/cn to receive the most current information on all of our products.

#### 1.0 **DEVICE OVERVIEW**

This document contains device specific information about the following devices:

- PIC16F73

- PIC16F74

- PIC16F76

- PIC16F77

PIC16F73/76 devices are available only in 28-pin packages, while PIC16F74/77 devices are available in 40-pin and 44-pin packages. All devices in the PIC16F7X family share common architecture, with the following differences:

- The PIC16F73 and PIC16F76 have one-half of the total on-chip memory of the PIC16F74 and **PIC16F77**

- The 28-pin devices have 3 I/O ports, while the 40/44-pin devices have 5

- · The 28-pin devices have 11 interrupts, while the 40/44-pin devices have 12

- The 28-pin devices have 5 A/D input channels, while the 40/44-pin devices have 8

- The Parallel Slave Port is implemented only on the 40/44-pin devices

PIC16F7X DEVICE FEATURES **PIC16F74 PIC16F76 Key Features PIC16F73 PIC16F77 Operating Frequency** DC - 20 MHz DC - 20 MHz DC - 20 MHz DC - 20 MHz **RESETS** (and Delays) POR, BOR POR. BOR POR. BOR POR, BOR (PWRT, OST) (PWRT, OST) (PWRT, OST) (PWRT, OST) FLASH Program Memory 4K 4K 8K 8K (14-bit words) Data Memory (bytes) 368 192 192 368 Interrupts 11 12 11 12 I/O Ports Ports A,B,C Ports A,B,C Ports A,B,C,D,E Ports A,B,C,D,E Timers 3 3 3 3 Capture/Compare/PWM Modules 2 2 2 2 SSP, USART Serial Communications SSP, USART SSP. USART SSP, USART **Parallel Communications** PSP PSP 8-bit Analog-to-Digital Module **5 Input Channels** 8 Input Channels 5 Input Channels 8 Input Channels Instruction Set **35 Instructions 35 Instructions** 35 Instructions **35 Instructions** Packaging 28-pin DIP 40-pin PDIP 28-pin DIP 40-pin PDIP 28-pin SOIC 44-pin PLCC 28-pin SOIC 44-pin PLCC 28-pin SSOP 44-pin TQFP 28-pin SSOP 44-pin TQFP 28-pin MLF 28-pin MLF

### **TABLE 1-1:**

The available features are summarized in Table 1-1. Block diagrams of the PIC16F73/76 and PIC16F74/77 devices are provided in Figure 1-1 and Figure 1-2, respectively. The pinouts for these device families are listed in Table 1-2 and Table 1-3.

Additional information may be found in the PICmicro™ Mid-Range Reference Manual (DS33023), which may be obtained from your local Microchip Sales Representative or downloaded from the Microchip website. The Reference Manual should be considered a complementary document to this data sheet, and is highly recommended reading for a better understanding of the device architecture and operation of the peripheral modules.

### TABLE 1-3:PIC16F74 AND PIC16F77 PINOUT DESCRIPTION

| OSC1/CLKI<br>OSC1<br>CLKI<br>OSC2/CLKO<br>OSC2<br>CLKO<br>MCLR/VPP<br>MCLR<br>VPP | 13 | 14<br>15 | 30<br>31 | 1        | ST/CMOS <sup>(4)</sup> | Oscillator crystal or external clock input.<br>Oscillator crystal input or external clock source input.<br>ST buffer when configured in RC mode. Otherwise<br>CMOS.<br>External clock source input. Always associated with pin |

|-----------------------------------------------------------------------------------|----|----------|----------|----------|------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| CLKI<br>OSC2/CLKO<br>OSC2<br>CLKO<br><u>MCLR/VPP</u><br>MCLR                      | 14 | 15       | 31       | I        |                        | Oscillator crystal input or external clock source input.<br>ST buffer when configured in RC mode. Otherwise<br>CMOS.<br>External clock source input. Always associated with pin                                                |

| OSC2/CLKO<br>OSC2<br>CLKO<br>MCLR/VPP<br>MCLR                                     | 14 | 15       | 31       |          |                        | CMOS.<br>External clock source input. Always associated with pin                                                                                                                                                               |

| OSC2/CLKO<br>OSC2<br>CLKO<br>MCLR/VPP<br>MCLR                                     | 14 | 15       | 31       |          |                        | External clock source input. Always associated with pin                                                                                                                                                                        |

| OSC2<br>CLKO<br>MCLR/VPP<br>MCLR                                                  | 14 | 15       | 31       |          |                        |                                                                                                                                                                                                                                |

| OSC2<br>CLKO<br>MCLR/VPP<br>MCLR                                                  | 14 | 15       | 31       | 0        |                        | function OSC1 (see OSC1/CLKI, OSC2/CLKO pins).                                                                                                                                                                                 |

| CLKO<br>MCLR/VPP<br>MCLR                                                          |    |          |          | <u> </u> | I —                    | Oscillator crystal or clock output.                                                                                                                                                                                            |

| MCLR/Vpp<br>MCLR                                                                  |    |          |          | 0        |                        | Oscillator crystal output.                                                                                                                                                                                                     |

| MCLR/Vpp<br>MCLR                                                                  |    |          |          |          |                        | Connects to crystal or resonator in Crystal Oscillator                                                                                                                                                                         |

| MCLR/Vpp<br>MCLR                                                                  |    |          |          |          |                        | mode.                                                                                                                                                                                                                          |

| MCLR                                                                              |    |          |          | 0        |                        | In RC mode, OSC2 pin outputs CLKO, which has 1/4                                                                                                                                                                               |

| MCLR                                                                              |    |          |          |          |                        | the frequency of OSC1 and denotes the instruction                                                                                                                                                                              |

| MCLR                                                                              |    |          |          |          |                        | cycle rate.                                                                                                                                                                                                                    |

|                                                                                   | 1  | 2        | 18       |          | ST                     | Master Clear (input) or programming voltage (output).                                                                                                                                                                          |

| Vpp                                                                               |    |          |          | I        |                        | Master Clear (Reset) input. This pin is an active low                                                                                                                                                                          |

| VPP                                                                               |    |          |          |          |                        | RESET to the device.                                                                                                                                                                                                           |

|                                                                                   |    |          |          | Р        |                        | Programming voltage input.                                                                                                                                                                                                     |

|                                                                                   |    |          |          |          |                        | PORTA is a bi-directional I/O port.                                                                                                                                                                                            |

| RA0/AN0                                                                           | 2  | 3        | 19       |          | TTL                    |                                                                                                                                                                                                                                |

| RA0                                                                               |    |          |          | I/O      |                        | Digital I/O.                                                                                                                                                                                                                   |

| AN0                                                                               |    |          |          | I        |                        | Analog input 0.                                                                                                                                                                                                                |

| RA1/AN1                                                                           | 3  | 4        | 20       |          | TTL                    |                                                                                                                                                                                                                                |

| RA1                                                                               |    |          |          | I/O      |                        | Digital I/O.                                                                                                                                                                                                                   |

| AN1                                                                               |    |          |          | I        |                        | Analog input 1.                                                                                                                                                                                                                |

| RA2/AN2                                                                           | 4  | 5        | 21       |          | TTL                    |                                                                                                                                                                                                                                |

| RA2                                                                               |    |          |          | I/O      |                        | Digital I/O.                                                                                                                                                                                                                   |

| AN2                                                                               |    |          |          | I        |                        | Analog input 2.                                                                                                                                                                                                                |

| RA3/AN3/Vref                                                                      | 5  | 6        | 22       |          | TTL                    |                                                                                                                                                                                                                                |

| RA3                                                                               |    |          |          | I/O      |                        | Digital I/O.                                                                                                                                                                                                                   |

| AN3                                                                               |    |          |          | I        |                        | Analog input 3.                                                                                                                                                                                                                |

| VREF                                                                              |    |          |          | I        |                        | A/D reference voltage input.                                                                                                                                                                                                   |

| RA4/T0CKI                                                                         | 6  | 7        | 23       |          | ST                     |                                                                                                                                                                                                                                |

| RA4                                                                               |    |          |          | I/O      |                        | Digital I/O – Open drain when configured as output.                                                                                                                                                                            |

| TOCKI                                                                             |    |          |          | I        |                        | Timer0 external clock input.                                                                                                                                                                                                   |

| RA5/SS/AN4                                                                        | 7  | 8        | 24       |          | TTL                    |                                                                                                                                                                                                                                |

| RA5                                                                               |    | -        |          | I/O      |                        | Digital I/O.                                                                                                                                                                                                                   |

| SS                                                                                | 1  |          |          | 1        |                        | SPI slave select input.                                                                                                                                                                                                        |

| AN4                                                                               |    |          |          |          | 1                      |                                                                                                                                                                                                                                |

| Legend: I = inpu                                                                  |    | 1        |          |          |                        | Analog input 4.                                                                                                                                                                                                                |

— = Not used TTL = TTL input ST = Schmitt Trigger input

**Note 1:** This buffer is a Schmitt Trigger input when configured as an external interrupt.

2: This buffer is a Schmitt Trigger input when used in Serial Programming mode.

**3:** This buffer is a Schmitt Trigger input when configured as general purpose I/O and a TTL input when used in the Parallel Slave Port mode (for interfacing to a microprocessor bus).

4: This buffer is a Schmitt Trigger input when configured in RC Oscillator mode and a CMOS input otherwise.

| Pin Name          | DIP<br>Pin# | PLCC<br>Pin# | QFP<br>Pin# | I/O/P<br>Type | Buffer<br>Type        | Description                                                   |

|-------------------|-------------|--------------|-------------|---------------|-----------------------|---------------------------------------------------------------|

|                   |             |              |             |               |                       | PORTD is a bi-directional I/O port or parallel slave port     |

|                   |             |              |             |               |                       | when interfacing to a microprocessor bus.                     |

| RD0/PSP0          | 19          | 21           | 38          |               | ST/TTL <sup>(3)</sup> |                                                               |

| RD0               |             |              |             | I/O           |                       | Digital I/O.                                                  |

| PSP0              |             |              | 00          | I/O           | ot (3)                | Parallel Slave Port data.                                     |

| RD1/PSP1<br>RD1   | 20          | 22           | 39          | і<br>І/О      | ST/TTL <sup>(3)</sup> | Digital I/O.                                                  |

| PSP1              |             |              |             | 1/O           |                       | Parallel Slave Port data.                                     |

| RD2/PSP2          | 21          | 23           | 40          | 1, C          | ST/TTL <sup>(3)</sup> |                                                               |

| RD2               | 21          | 20           | 40          | ı/O           | OI/TIE                | Digital I/O.                                                  |

| PSP2              |             |              |             | I/O           |                       | Parallel Slave Port data.                                     |

| RD3/PSP3          | 22          | 24           | 41          |               | ST/TTL <sup>(3)</sup> |                                                               |

| RD3               |             |              |             | I/O           |                       | Digital I/O.                                                  |

| PSP3              |             |              |             | I/O           |                       | Parallel Slave Port data.                                     |

| RD4/PSP4          | 27          | 30           | 2           |               | ST/TTL <sup>(3)</sup> |                                                               |

| RD4               |             |              |             | I/O           |                       | Digital I/O.                                                  |

| PSP4              |             |              |             | I/O           |                       | Parallel Slave Port data.                                     |

| RD5/PSP5          | 28          | 31           | 3           |               | ST/TTL <sup>(3)</sup> |                                                               |

| RD5               |             |              |             | I/O           |                       | Digital I/O.                                                  |

| PSP5              |             |              |             | I/O           | · · · · · · (2)       | Parallel Slave Port data.                                     |

| RD6/PSP6          | 29          | 32           | 4           |               | ST/TTL <sup>(3)</sup> | District I/O                                                  |

| RD6<br>PSP6       |             |              |             | I/O<br>I/O    |                       | Digital I/O.<br>Parallel Slave Port data.                     |

| RD7/PSP7          | 30          | 33           | 5           | 1/0           | ST/TTL <sup>(3)</sup> | Faraller Slave Folt data.                                     |

| RD7/PSP7          | 30          | - 33         | Э           | I/O           | 51/11L*/              | Digital I/O.                                                  |

| PSP7              |             |              |             | 1/O           |                       | Parallel Slave Port data.                                     |

| -                 |             |              |             |               |                       | PORTE is a bi-directional I/O port.                           |

| RE0/RD/AN5        | 8           | 9            | 25          |               | ST/TTL <sup>(3)</sup> |                                                               |

| RE0               |             | -            |             | I/O           |                       | Digital I/O.                                                  |

| RD                |             |              |             | I             |                       | Read control for parallel slave port .                        |

| AN5               |             |              |             | I             |                       | Analog input 5.                                               |

| RE1/WR/AN6        | 9           | 10           | 26          |               | ST/TTL <sup>(3)</sup> |                                                               |

| RE1               |             |              |             | I/O           |                       | Digital I/O.                                                  |

| WR                |             |              |             | 1             |                       | Write control for parallel slave port .                       |

| AN6               |             |              |             | I             | o <i></i> (3)         | Analog input 6.                                               |

| RE2/CS/AN7        | 10          | 11           | 27          |               | ST/TTL <sup>(3)</sup> |                                                               |

| RE2<br>CS         |             |              |             | I/O<br>I      |                       | Digital I/O.<br>Chip select control for parallel slave port . |

| AN7               |             |              |             | 1             |                       | Analog input 7.                                               |

| Vss               | 12,31       | 13,34        | 6,29        | P             | _                     | Ground reference for logic and I/O pins.                      |

| VDD               | 11,32       | 12,35        | 7,28        | Р             | _                     | Positive supply for logic and I/O pins.                       |

| NC                | · -         | 1,17,2       | 12,13,      |               | _                     | These pins are not internally connected. These pins should    |

|                   |             | 8, 40        | 33, 34      |               |                       | be left unconnected.                                          |

| Legend: I = input |             | O = 0        |             | I/C           | ) = input/outpu       | ut P = power                                                  |

#### **TABLE 1-3:** PIC16F74 AND PIC16F77 PINOUT DESCRIPTION (CONTINUED)

**Note 1:** This buffer is a Schmitt Trigger input when configured as an external interrupt.

2: This buffer is a Schmitt Trigger input when used in Serial Programming mode.

3: This buffer is a Schmitt Trigger input when configured as general purpose I/O and a TTL input when used in the Parallel Slave Port mode (for interfacing to a microprocessor bus).

4: This buffer is a Schmitt Trigger input when configured in RC Oscillator mode and a CMOS input otherwise.

### 2.2.2.5 PIR1 Register

The PIR1 register contains the individual flag bits for the peripheral interrupts.

| Note: | Interrupt flag bits are set when an interrupt  |

|-------|------------------------------------------------|

|       | condition occurs, regardless of the state of   |

|       | its corresponding enable bit or the global     |

|       | enable bit, GIE (INTCON<7>). User soft-        |

|       | ware should ensure the appropriate interrupt   |

|       | bits are clear prior to enabling an interrupt. |

### REGISTER 2-5: PIR1 REGISTER (ADDRESS 0Ch)

| R/W-0                | R/W-0 | R-0  | R-0  | R/W-0 | R/W-0  | R/W-0  | R/W-0  |

|----------------------|-------|------|------|-------|--------|--------|--------|

| PSPIF <sup>(1)</sup> | ADIF  | RCIF | TXIF | SSPIF | CCP1IF | TMR2IF | TMR1IF |

| bit 7                |       |      |      |       |        |        | bit 0  |

| bit 7 | <b>PSPIF<sup>(1)</sup>:</b> Parallel Slave Port Read/Write Interrupt Flag bit<br>1 = A read or a write operation has taken place (must be cleared in software)<br>0 = No read or write has occurred                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|-------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 6 | ADIF: A/D Converter Interrupt Flag bit<br>1 = An A/D conversion is completed (must be cleared in software)<br>0 = The A/D conversion is not complete                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| bit 5 | RCIF: USART Receive Interrupt Flag bit<br>1 = The USART receive buffer is full<br>0 = The USART receive buffer is empty                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| bit 4 | <b>TXIF</b> : USART Transmit Interrupt Flag bit<br>1 = The USART transmit buffer is empty<br>0 = The USART transmit buffer is full                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| bit 3 | <ul> <li>SSPIF: Synchronous Serial Port (SSP) Interrupt Flag</li> <li>1 = The SSP interrupt condition has occurred, and must be cleared in software before returning from the Interrupt Service Routine. The conditions that will set this bit are:</li> <li><u>SPI</u> <ul> <li>A transmission/reception has taken place.</li> <li><u>I<sup>2</sup>C Slave</u></li> <li>A transmission/reception has taken place.</li> <li><u>I<sup>2</sup>C Master</u></li> <li>A transmission/reception has taken place.</li> <li>The initiated START condition was completed by the SSP module.</li> <li>The initiated Restart condition was completed by the SSP module.</li> <li>The initiated Restart condition was completed by the SSP module.</li> <li>A START condition occurred while the SSP module was IDLE (multi-master system).</li> <li>A STOP condition has occurred</li> </ul> </li> </ul> |

| bit 2 | CCP1IF: CCP1 Interrupt Flag bit<br><u>Capture mode:</u><br>1 = A TMR1 register capture occurred (must be cleared in software)<br>0 = No TMR1 register capture occurred<br><u>Compare mode:</u><br>1 = A TMR1 register compare match occurred (must be cleared in software)<br>0 = No TMR1 register compare match occurred<br><u>PWM mode:</u><br>Unused in this mode                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| bit 1 | <b>TMR2IF</b> : TMR2 to PR2 Match Interrupt Flag bit<br>1 = TMR2 to PR2 match occurred (must be cleared in software)<br>0 = No TMR2 to PR2 match occurred                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| bit 0 | <ul> <li>TMR1IF: TMR1 Overflow Interrupt Flag bit</li> <li>1 = TMR1 register overflowed (must be cleared in software)</li> <li>0 = TMR1 register did not overflow</li> <li>Note 1: PSPIF is reserved on 28-pin devices; always maintain this bit clear.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|       | Legend:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|       | R = Readable bit $W = Writable bit$ $U = Unimplemented bit, read as '0'$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|       | N = Readable bit W = Witable bit 0 = Offinite Hendrad bit, fead as 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

'1' = Bit is set

'0' = Bit is cleared

- n = Value at POR reset

x = Bit is unknown

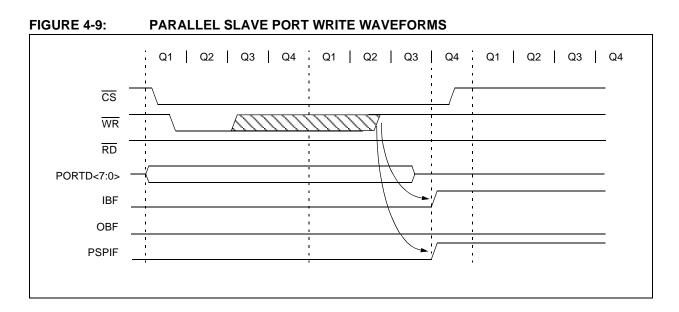

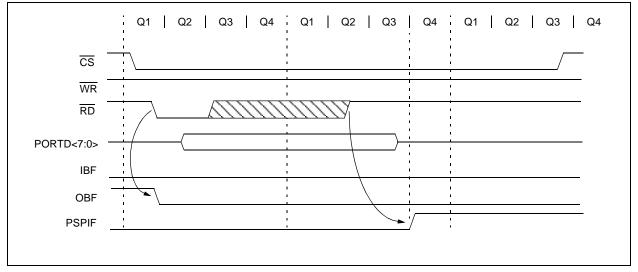

### FIGURE 4-10: PARALLEL SLAVE PORT READ WAVEFORMS

### TABLE 4-11: REGISTERS ASSOCIATED WITH PARALLEL SLAVE PORT

| Address | Name   | Bit 7                | Bit 6   | Bit 5      | Bit 4         | Bit 3    | Bit 2   | Bit 1       | Bit 0    | Value on:<br>POR,<br>BOR | Value on<br>all other<br>RESETS |

|---------|--------|----------------------|---------|------------|---------------|----------|---------|-------------|----------|--------------------------|---------------------------------|

| 08h     | PORTD  | Port data I          | atch wh | nen writte | en: Port pins | when rea | d       |             |          | xxxx xxxx                | uuuu uuuu                       |

| 09h     | PORTE  | —                    |         | —          |               | —        | RE2     | RE1         | RE0      | xxx                      | uuu                             |

| 89h     | TRISE  | IBF                  | OBF     | IBOV       | PSPMODE       | _        | PORTE D | Data Direct | ion Bits | 0000 -111                | 0000 -111                       |

| 0Ch     | PIR1   | PSPIF <sup>(1)</sup> | ADIF    | RCIF       | TXIF          | SSPIF    | CCP1IF  | TMR2IF      | TMR1IF   | 0000 0000                | 0000 0000                       |

| 8Ch     | PIE1   | PSPIE <sup>(1)</sup> | ADIE    | RCIE       | TXIE          | SSPIE    | CCP1IE  | TMR2IE      | TMR1IE   | 0000 0000                | 0000 0000                       |

| 9Fh     | ADCON1 | _                    | _       | _          | _             | _        | PCFG2   | PCFG1       | PCFG0    | 000                      | 000                             |

Legend: x = unknown, u = unchanged, - = unimplemented, read as '0'. Shaded cells are not used by the Parallel Slave Port.

**Note 1:** Bits PSPIE and PSPIF are reserved on the PIC16F73/76; always maintain these bits clear.

# PIC16F7X

NOTES:

\_

# PIC16F7X

# REGISTER 8-1: CCP1CON REGISTER/CCP2CON REGISTER (ADDRESS: 17h/1Dh)

| bit 7-6                                                                                          | U-0<br>—                                                                                              | U-0          | R/W-0<br>CCPxX               | R/W-0       | R/W-0        | R/W-0       | R/W-0       | R/W-0   |  |  |  |  |

|--------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------|--------------|------------------------------|-------------|--------------|-------------|-------------|---------|--|--|--|--|

| bit 7-6                                                                                          | —<br>bit 7                                                                                            | _            | CCDvV                        |             |              |             |             |         |  |  |  |  |

| Dit 7-6                                                                                          | bit 7                                                                                                 |              | COFXA                        | CCPxY       | CCPxM3       | CCPxM2      | CCPxM1      | CCPxM0  |  |  |  |  |

| bit 5-4 ()<br>()<br>()<br>()<br>()<br>()<br>()<br>()<br>()<br>()<br>()<br>()<br>()<br>(          |                                                                                                       |              |                              |             |              |             |             | bit 0   |  |  |  |  |

| ()<br>()<br>()<br>()<br>()<br>()<br>()<br>()<br>()<br>()<br>()<br>()<br>()<br>(                  | Unimplem                                                                                              | ented: Rea   | ad as '0'                    |             |              |             |             |         |  |  |  |  |

| 1<br>1<br>1<br>2<br>2<br>2<br>2<br>1<br>2<br>1<br>2<br>1<br>1<br>1<br>1<br>1<br>1<br>1<br>1<br>1 | CCPxX:CC                                                                                              | PxY: PWN     | l Least Signi                | ficant bits |              |             |             |         |  |  |  |  |

| bit 3-0                                                                                          | <u>Capture mo</u><br>Unused                                                                           | ode:         |                              |             |              |             |             |         |  |  |  |  |

| -<br>bit 3-0                                                                                     | <u>Compare n</u><br>Unused                                                                            | <u>node:</u> |                              |             |              |             |             |         |  |  |  |  |

| bit 3-0                                                                                          | PWM mode:                                                                                             |              |                              |             |              |             |             |         |  |  |  |  |

|                                                                                                  | These bits                                                                                            | are the two  | LSbs of the                  | PWM duty    | cycle. The e | ight MSbs a | re found in | CCPRxL. |  |  |  |  |

| ,                                                                                                | CCPxM3:CCPxM0: CCPx Mode Select bits                                                                  |              |                              |             |              |             |             |         |  |  |  |  |

|                                                                                                  | 0000 = Capture/Compare/PWM disabled (resets CCPx module)                                              |              |                              |             |              |             |             |         |  |  |  |  |

|                                                                                                  |                                                                                                       |              | , every fallin               |             |              |             |             |         |  |  |  |  |

| (                                                                                                | 0101 <b>= Ca</b>                                                                                      | pture mode   | , every rising               | g edge      |              |             |             |         |  |  |  |  |

| (                                                                                                | 0110 = Capture mode, every 4th rising edge                                                            |              |                              |             |              |             |             |         |  |  |  |  |

|                                                                                                  | 0111 = Capture mode, every 16th rising edge                                                           |              |                              |             |              |             |             |         |  |  |  |  |

|                                                                                                  | 1000 = Compare mode, set output on match (CCPxIF bit is set)                                          |              |                              |             |              |             |             |         |  |  |  |  |

|                                                                                                  | 1001 = Compare mode, clear output on match (CCPxIF bit is set)                                        |              |                              |             |              |             |             |         |  |  |  |  |

| -                                                                                                | 1010 = Compare mode, generate software interrupt on match (CCPxIF bit is set, CCPx pin is unaffected) |              |                              |             |              |             |             |         |  |  |  |  |

| :                                                                                                | CC                                                                                                    |              | e, trigger sp<br>ïmer1; CCP2 |             | •            |             | •           |         |  |  |  |  |

| :                                                                                                | 11xx = PW                                                                                             | /M mode      |                              |             |              |             |             |         |  |  |  |  |

|                                                                                                  |                                                                                                       |              |                              |             |              |             |             |         |  |  |  |  |

|                                                                                                  | Legend:                                                                                               |              |                              |             |              |             |             |         |  |  |  |  |

| Legend:                  |                  |                      |                    |

|--------------------------|------------------|----------------------|--------------------|

| R = Readable bit         | W = Writable bit | U = Unimplemented    | l bit, read as '0' |

| - n = Value at POR reset | '1' = Bit is set | '0' = Bit is cleared | x = Bit is unknown |

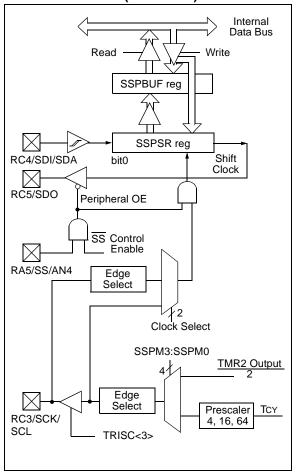

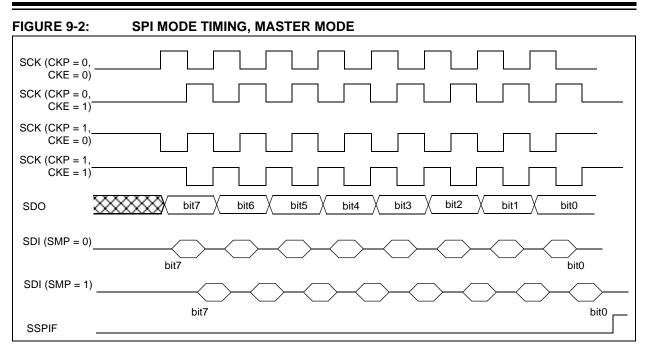

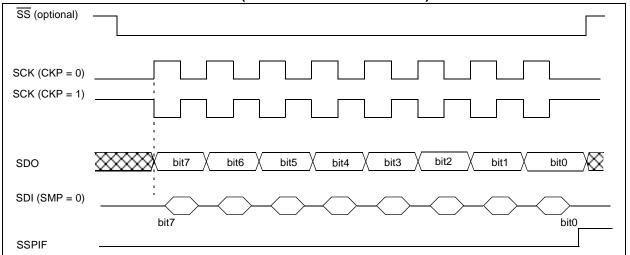

#### FIGURE 9-1: SSP BLOCK DIAGRAM (SPI MODE)

To enable the serial port, SSP enable bit, SSPEN (SSPCON<5>) must be set. To reset or reconfigure SPI mode, clear bit SSPEN, re-initialize the SSPCON register, and then set bit SSPEN. This configures the SDI, SDO, SCK, and SS pins as serial port pins. For the pins to behave as the serial port function, they must have their data direction bits (in the TRISC register) appropriately programmed. That is:

- SDI must have TRISC<4> set

- SDO must have TRISC<5> cleared

- SCK (Master mode) must have TRISC<3> cleared

- SCK (Slave mode) must have TRISC<3> set

- SS must have TRISA<5> set and ADCON must be configured such that RA5 is a digital I/O

Note 1: When the SPI is in Slave mode with SS pin control enabled (SSPCON<3:0> = 0100), the SPI module will reset if the SS pin is set to VDD.

- 2: If the SPI is used in Slave mode with CKE = '1', then the SS pin control must be enabled.

- 3: When the SPI is in Slave mode with  $\overline{SS}$  pin control enabled (SSPCON<3:0> = '0100'), the state of the  $\overline{SS}$  pin can affect the state read back from the TRISC<5> bit. The Peripheral OE signal from the SSP module into PORTC controls the state that is read back from the TRISC<5> bit (see Section 4.3 for information on PORTC). If Read-Modify-Write instructions, such as BSF are performed on the TRISC register while the  $\overline{SS}$  pin is high, this will cause the TRISC<5> bit to be set, thus disabling the SDO output.

# PIC16F7X

© 2002 Microchip Technology Inc.

### 10.0 UNIVERSAL SYNCHRONOUS ASYNCHRONOUS RECEIVER TRANSMITTER (USART)

The Universal Synchronous Asynchronous Receiver Transmitter (USART) module is one of the two serial I/O modules. (USART is also known as a Serial Communications Interface or SCI.) The USART can be configured as a full duplex asynchronous system that can communicate with peripheral devices, such as CRT terminals and personal computers, or it can be configured as a half duplex synchronous system that can communicate with peripheral devices, such as A/D or D/A integrated circuits, serial EEPROMs, etc. The USART can be configured in the following modes:

- Asynchronous (full duplex)

- Synchronous Master (half duplex)

- Synchronous Slave (half duplex)

Bit SPEN (RCSTA<7>) and bits TRISC<7:6> have to be set in order to configure pins RC6/TX/CK and RC7/RX/DT as the Universal Synchronous Asynchronous Receiver Transmitter.

### REGISTER 10-1: TXSTA: TRANSMIT STATUS AND CONTROL REGISTER (ADDRESS 98h)

|       | R/W-0                                                                                                                            | R/W-0                                            | R/W-0        | R/W-0        | U-0      | R/W-0      | R-1          | R/W-0 |  |  |  |

|-------|----------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------|--------------|--------------|----------|------------|--------------|-------|--|--|--|

|       | CSRC                                                                                                                             | TX9                                              | TXEN         | SYNC         | —        | BRGH       | TRMT         | TX9D  |  |  |  |

|       | bit 7                                                                                                                            |                                                  |              |              |          |            |              | bit 0 |  |  |  |

|       |                                                                                                                                  |                                                  |              |              |          |            |              |       |  |  |  |

| bit 7 | CSRC: Clock Source Select bit                                                                                                    |                                                  |              |              |          |            |              |       |  |  |  |

|       | <u>Asynchronous mode:</u><br>Don't care                                                                                          |                                                  |              |              |          |            |              |       |  |  |  |

|       | <u>Synchronous mode:</u><br>1 = Master mode (clock generated internally from BRG)<br>0 = Slave mode (clock from external source) |                                                  |              |              |          |            |              |       |  |  |  |

| bit 6 | 1 = Selects                                                                                                                      | Transmit Ena<br>s 9-bit transn<br>s 8-bit transn | nission      |              |          |            |              |       |  |  |  |

| bit 5 | 1 = Transn                                                                                                                       | nsmit Enable<br>nit enabled<br>nit disabled      | e bit        |              |          |            |              |       |  |  |  |

|       | Note:                                                                                                                            | SREN/CRE                                         | N overrides  | TXEN in Sy   | nc mode. |            |              |       |  |  |  |

| bit 4 | 1 = Synchi                                                                                                                       | ART Mode S<br>ronous mode<br>nronous mod         | )            |              |          |            |              |       |  |  |  |

| bit 3 | •                                                                                                                                | ented: Read                                      |              |              |          |            |              |       |  |  |  |

| bit 2 | BRGH: Hig                                                                                                                        | gh Baud Rate                                     | e Select bit |              |          |            |              |       |  |  |  |

|       | <u>Asynchron</u><br>1 = High s<br>0 = Low sp                                                                                     | peed                                             |              |              |          |            |              |       |  |  |  |

|       | <u>Synchrono</u><br>Unused in                                                                                                    |                                                  |              |              |          |            |              |       |  |  |  |

| bit 1 | <b>TRMT</b> : Tra<br>1 = TSR e<br>0 = TSR fu                                                                                     |                                                  | egister Stat | us bit       |          |            |              |       |  |  |  |

| bit 0 | <b>TX9D:</b> 9th<br>Can be pa                                                                                                    | bit of Transn<br>rity bit                        | nit Data     |              |          |            |              |       |  |  |  |

|       | Legend:                                                                                                                          |                                                  |              |              |          |            |              |       |  |  |  |

|       | R = Reada                                                                                                                        | ble bit                                          | W = W        | Vritable bit | U = Unin | nplemented | bit, read as | '0'   |  |  |  |

| 0                                          |                  |                      |                    |  |

|--------------------------------------------|------------------|----------------------|--------------------|--|

| R = Readable bit                           | W = Writable bit | U = Unimplemented    | bit, read as '0'   |  |

| <ul> <li>n = Value at POR reset</li> </ul> | '1' = Bit is set | '0' = Bit is cleared | x = Bit is unknown |  |

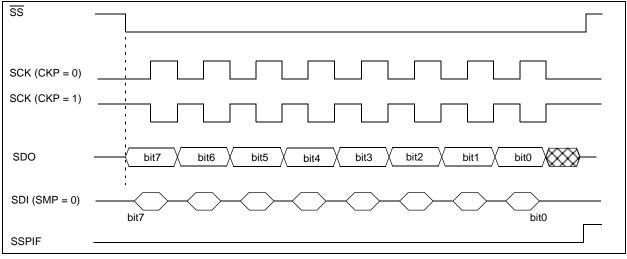

### FIGURE 10-5: ASYNCHRONOUS RECEPTION

Steps to follow when setting up an Asynchronous Reception:

- 1. Initialize the SPBRG register for the appropriate baud rate. If a high speed baud rate is desired, set bit BRGH (Section 10.1).

- 2. Enable the asynchronous serial port by clearing bit SYNC and setting bit SPEN.

- 3. If interrupts are desired, then set enable bit RCIE.

- 4. If 9-bit reception is desired, then set bit RX9.

- 5. Enable the reception by setting bit CREN.

- 6. Flag bit RCIF will be set when reception is complete and an interrupt will be generated if enable bit RCIE is set.

- 7. Read the RCSTA register to get the ninth bit (if enabled) and determine if any error occurred during reception.

- 8. Read the 8-bit received data by reading the RCREG register.

- 9. If any error occurred, clear the error by clearing enable bit CREN.

- 10. If using interrupts, ensure that GIE and PEIE in the INTCON register are set.

| Address                | Name   | Bit 7                | Bit 6     | Bit 5       | Bit 4 | Bit 3 | Bit 2  | Bit 1  | Bit 0  | Value on:<br>POR,<br>BOR | Value on<br>all other<br>RESETS |

|------------------------|--------|----------------------|-----------|-------------|-------|-------|--------|--------|--------|--------------------------|---------------------------------|

| 0Bh, 8Bh,<br>10Bh,18Bh | INTCON | GIE                  | PEIE      | TMR0IE      | INTE  | RBIE  | TMR0IF | INTF   | RBIF   | 0000 000x                | 0000 000u                       |

| 0Ch                    | PIR1   | PSPIF <sup>(1)</sup> | ADIF      | RCIF        | TXIF  | SSPIF | CCP1IF | TMR2IF | TMR1IF | 0000 0000                | 0000 0000                       |

| 18h                    | RCSTA  | SPEN                 | RX9       | SREN        | CREN  |       | FERR   | OERR   | RX9D   | 0000 -00x                | 0000 -00x                       |

| 1Ah                    | RCREG  | USART R              | eceive Re | gister      |       |       |        |        |        | 0000 0000                | 0000 0000                       |

| 8Ch                    | PIE1   | PSPIE <sup>(1)</sup> | ADIE      | RCIE        | TXIE  | SSPIE | CCP1IE | TMR2IE | TMR1IE | 0000 0000                | 0000 0000                       |

| 98h                    | TXSTA  | CSRC                 | TX9       | TXEN        | SYNC  |       | BRGH   | TRMT   | TX9D   | 0000 -010                | 0000 -010                       |

| 99h                    | SPBRG  | Baud Rate            | Generato  | or Register |       |       |        |        |        | 0000 0000                | 0000 0000                       |

### TABLE 10-6: REGISTERS ASSOCIATED WITH ASYNCHRONOUS RECEPTION

Legend: x = unknown, - = unimplemented locations read as '0'. Shaded cells are not used for asynchronous reception. Note 1: Bits PSPIE and PSPIF are reserved on the PIC16F73/76 devices; always maintain these bits clear.

### 10.3 USART Synchronous Master Mode

In Synchronous Master mode, the data is transmitted in a half-duplex manner (i.e., transmission and reception do not occur at the same time). When transmitting data, the reception is inhibited and vice versa. Synchronous mode is entered by setting bit SYNC (TXSTA<4>). In addition, enable bit SPEN (RCSTA<7>) is set in order to configure the RC6/TX/CK and RC7/RX/DT I/O pins to CK (clock) and DT (data) lines, respectively. The Master mode indicates that the processor transmits the master clock on the CK line. The Master mode is entered by setting bit CSRC (TXSTA<7>).

### 10.3.1 USART SYNCHRONOUS MASTER TRANSMISSION

The USART transmitter block diagram is shown in Figure 10-1. The heart of the transmitter is the transmit (serial) shift register (TSR). The shift register obtains its data from the read/write transmit buffer register TXREG. The TXREG register is loaded with data in software. The TSR register is not loaded until the last bit has been transmitted from the previous load. As soon as the last bit is transmitted, the TSR is loaded with new data from the TXREG (if available). Once the TXREG register transfers the data to the TSR register (occurs in one TCYCLE), the TXREG is empty and interrupt bit TXIF (PIR1<4>) is set. The interrupt can be enabled/disabled by setting/clearing enable bit TXIE (PIE1<4>). Flag bit TXIF will be set, regardless of the state of enable bit TXIE and cannot be cleared in software. It will reset only when new data is loaded into the TXREG register. While flag bit TXIF indicates the status of the TXREG register, another bit TRMT (TXSTA<1>) shows the status of the TSR register. TRMT is a read only bit, which is set when the TSR is empty. No interrupt logic is tied to this bit, so the user has to poll this bit in order to determine if the TSR register is empty. The TSR is not mapped in data memory, so it is not available to the user.

Transmission is enabled by setting enable bit TXEN (TXSTA<5>). The actual transmission will not occur until the TXREG register has been loaded with data. The first data bit will be shifted out on the next available rising edge of the clock on the CK line. Data out is stable around the falling edge of the synchronous clock (Figure 10-6). The transmission can also be started by first loading the TXREG register and then setting bit TXEN (Figure 10-7). This is advantageous when slow baud rates are selected, since the BRG is kept in RESET when bits TXEN, CREN and SREN are clear. Setting enable bit TXEN will start the BRG, creating a shift clock immediately. Normally, when transmission is first started, the TSR register is empty, so a transfer to the TXREG register will result in an immediate transfer to TSR, resulting in an empty TXREG. Back-to-back transfers are possible.

Clearing enable bit TXEN during a transmission will cause the transmission to be aborted and will reset the transmitter. The DT and CK pins will revert to hiimpedance. If either bit CREN or bit SREN is set during a transmission, the transmission is aborted and the DT pin reverts to a hi-impedance state (for a reception). The CK pin will remain an output if bit CSRC is set (internal clock). The transmitter logic, however, is not reset, although it is disconnected from the pins. In order to reset the transmitter, the user has to clear bit TXEN. If bit SREN is set (to interrupt an on-going transmission and receive a single word), then after the single word is received, bit SREN will be cleared and the serial port will revert back to transmitting, since bit TXEN is still set. The DT line will immediately switch from Hiimpedance Receive mode to transmit and start driving. To avoid this, bit TXEN should be cleared.

In order to select 9-bit transmission, the TX9 (TXSTA<6>) bit should be set and the ninth bit should be written to bit TX9D (TXSTA<0>). The ninth bit must be written before writing the 8-bit data to the TXREG register. This is because a data write to the TXREG can result in an immediate transfer of the data to the TSR register (if the TSR is empty). If the TSR was empty and the TXREG was written before writing the "new" TX9D, the "present" value of bit TX9D is loaded.

Steps to follow when setting up a Synchronous Master Transmission:

- 1. Initialize the SPBRG register for the appropriate baud rate (Section 10.1).

- 2. Enable the synchronous master serial port by setting bits SYNC, SPEN and CSRC.

- 3. If interrupts are desired, set enable bit TXIE.

- 4. If 9-bit transmission is desired, set bit TX9.

- 5. Enable the transmission by setting bit TXEN.

- 6. If 9-bit transmission is selected, the ninth bit should be loaded in bit TX9D.

- 7. Start transmission by loading data to the TXREG register.

- 8. If using interrupts, ensure that GIE and PEIE in the INTCON register are set.

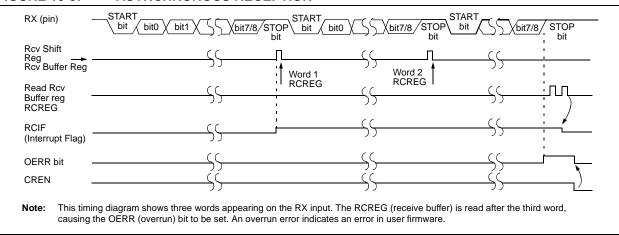

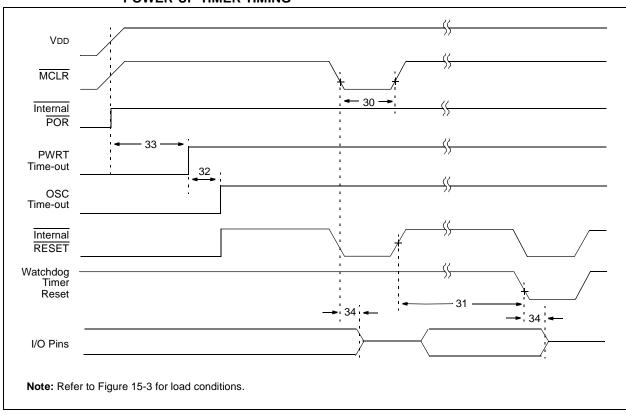

### 12.0 SPECIAL FEATURES OF THE CPU

These devices have a host of features intended to maximize system reliability, minimize cost through elimination of external components, provide power saving operating modes and offer code protection. These are:

- Oscillator Selection

- RESET

- Power-on Reset (POR)

- Power-up Timer (PWRT)

- Oscillator Start-up Timer (OST)

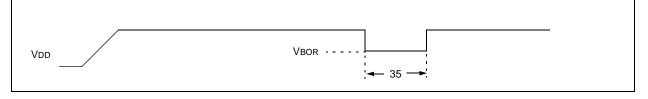

- Brown-out Reset (BOR)

- Interrupts

- Watchdog Timer (WDT)

- SLEEP

- Code Protection

- ID Locations

- In-Circuit Serial Programming

These devices have a Watchdog Timer, which can be enabled or disabled, using a configuration bit. It runs off its own RC oscillator for added reliability.

There are two timers that offer necessary delays on power-up. One is the Oscillator Start-up Timer (OST), intended to keep the chip in RESET until the crystal oscillator is stable. The other is the Power-up Timer (PWRT), which provides a fixed delay of 72 ms (nominal) on power-up only. It is designed to keep the part in RESET while the power supply stabilizes, and is enabled or disabled, using a configuration bit. With these two timers on-chip, most applications need no external RESET circuitry. SLEEP mode is designed to offer a very low current power-down mode. The user can wake-up from SLEEP through external RESET, Watchdog Timer Wake-up, or through an interrupt.

Several oscillator options are also made available to allow the part to fit the application. The RC oscillator option saves system cost while the LP crystal option saves power. Configuration bits are used to select the desired oscillator mode.

Additional information on special features is available in the PICmicro<sup>™</sup> Mid-Range Reference Manual (DS33023).

# 12.1 Configuration Bits

The configuration bits can be programmed (read as '0'), or left unprogrammed (read as '1'), to select various device configurations. These bits are mapped in program memory location 2007h.

The user will note that address 2007h is beyond the user program memory space, which can be accessed only during programming.

# TABLE 14-1: DEVELOPMENT TOOLS FROM MICROCHIP

|                                                                      | PIC12C   | PIC140 | PIC16C   | PIC16C6 | PIC16CX  | PIC16F6 | PIC16C | 2091019 | 90910Id | PIC16F8 | 62912Id | PIC17C4 | 2271219 | PIC18CX | PIC18FX | 83CXX<br>52CXX\<br>54CXX\ | ххсэн | МСКЕХХ | MCP251 |

|----------------------------------------------------------------------|----------|--------|----------|---------|----------|---------|--------|---------|---------|---------|---------|---------|---------|---------|---------|---------------------------|-------|--------|--------|

| MPLAB <sup>®</sup> Integrated<br>Development Environment             | >        | >      | >        | >       | >        | >       | >      | >       | >       | ^       | >       | >       | >       | >       | >       |                           |       |        |        |

| MPLAB <sup>®</sup> C17 C Compiler                                    |          |        |          |         |          |         |        |         |         |         |         | >       | ~       |         |         |                           |       |        |        |