Welcome to E-XFL.COM

### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

## Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

### Details

| Product Status             | Obsolete                                                                 |

|----------------------------|--------------------------------------------------------------------------|

| Core Processor             | PIC                                                                      |

| Core Size                  | 8-Bit                                                                    |

| Speed                      | 20MHz                                                                    |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                                        |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                    |

| Number of I/O              | 33                                                                       |

| Program Memory Size        | 14KB (8K x 14)                                                           |

| Program Memory Type        | FLASH                                                                    |

| EEPROM Size                | -                                                                        |

| RAM Size                   | 368 x 8                                                                  |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 5.5V                                                                |

| Data Converters            | A/D 8x8b                                                                 |

| Oscillator Type            | External                                                                 |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                        |

| Mounting Type              | Surface Mount                                                            |

| Package / Case             | 44-VQFN Exposed Pad                                                      |

| Supplier Device Package    | 44-QFN (8x8)                                                             |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16lf77-i-ml |

|                            |                                                                          |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

PIC16F7X

# 28/40-Pin 8-Bit CMOS FLASH Microcontrollers

## **Devices Included in this Data Sheet:**

- PIC16F73PIC16F74

- PIC16F76PIC16F77

# **High Performance RISC CPU:**

- High performance RISC CPU

- Only 35 single word instructions to learn

- All single cycle instructions except for program branches which are two-cycle

- Operating speed: DC 20 MHz clock input DC - 200 ns instruction cycle

- Up to 8K x 14 words of FLASH Program Memory, Up to 368 x 8 bytes of Data Memory (RAM)

- Pinout compatible to the PIC16C73B/74B/76/77

- Pinout compatible to the PIC16F873/874/876/877

- Interrupt capability (up to 12 sources)

- Eight level deep hardware stack

- Direct, Indirect and Relative Addressing modes

- Processor read access to program memory

## **Special Microcontroller Features:**

- Power-on Reset (POR)

- Power-up Timer (PWRT) and Oscillator Start-up Timer (OST)

- Watchdog Timer (WDT) with its own on-chip RC oscillator for reliable operation

- Programmable code protection

- Power saving SLEEP mode

- Selectable oscillator options

- In-Circuit Serial Programming<sup>™</sup> (ICSP<sup>™</sup>) via two pins

## **Peripheral Features:**

- Timer0: 8-bit timer/counter with 8-bit prescaler

- Timer1: 16-bit timer/counter with prescaler, can be incremented during SLEEP via external crystal/clock

- Timer2: 8-bit timer/counter with 8-bit period register, prescaler and postscaler

- Two Capture, Compare, PWM modules

- Capture is 16-bit, max. resolution is 12.5 ns

- Compare is 16-bit, max. resolution is 200 ns

PWM max. resolution is 10-bit

- 8-bit, up to 8-channel Analog-to-Digital converter

- Synchronous Serial Port (SSP) with SPI™ (Master mode) and I<sup>2</sup>C<sup>™</sup> (Slave)

- Universal Synchronous Asynchronous Receiver Transmitter (USART/SCI)

- Parallel Slave Port (PSP), 8-bits wide with external RD, WR and CS controls (40/44-pin only)

- Brown-out detection circuitry for Brown-out Reset (BOR)

## **CMOS Technology:**

- Low power, high speed CMOS FLASH technology

- Fully static design

- Wide operating voltage range: 2.0V to 5.5V

- High Sink/Source Current: 25 mA

- Industrial temperature range

- Low power consumption:

- < 2 mA typical @ 5V, 4 MHz

- 20 μA typical @ 3V, 32 kHz

- < 1 µA typical standby current

|          | Program Memory                  | Data            |     |            | 0 h.it            | CCD          | SS              | P                           |       | Timere             |

|----------|---------------------------------|-----------------|-----|------------|-------------------|--------------|-----------------|-----------------------------|-------|--------------------|

| Device   | (# Single Word<br>Instructions) | SRAM<br>(Bytes) | I/O | Interrupts | 8-bit<br>A/D (ch) | CCP<br>(PWM) | SPI<br>(Master) | l <sup>2</sup> C<br>(Slave) | USART | Timers<br>8/16-bit |

| PIC16F73 | 4096                            | 192             | 22  | 11         | 5                 | 2            | Yes             | Yes                         | Yes   | 2 / 1              |

| PIC16F74 | 4096                            | 192             | 33  | 12         | 8                 | 2            | Yes             | Yes                         | Yes   | 2/1                |

| PIC16F76 | 8192                            | 368             | 22  | 11         | 5                 | 2            | Yes             | Yes                         | Yes   | 2 / 1              |

| PIC16F77 | 8192                            | 368             | 33  | 12         | 8                 | 2            | Yes             | Yes                         | Yes   | 2 / 1              |

# **Table of Contents**

| 1.0   | Device Overview                                                 | 5 |

|-------|-----------------------------------------------------------------|---|

| 2.0   | Device Overview                                                 | 3 |

| 3.0   | Reading Program Memory                                          | 9 |

| 4.0   | I/O Ports                                                       |   |

| 5.0   | Timer0 Module                                                   | 3 |

| 6.0   | Timer1 Module                                                   | 7 |

| 7.0   | Timer2 Module                                                   | 1 |

| 8.0   | Capture/Compare/PWM Modules                                     | 3 |

| 9.0   | Synchronous Serial Port (SSP) Module                            | 9 |

| 10.0  | Universal Synchronous Asynchronous Receiver Transmitter (USART) |   |

| 11.0  | Analog-to-Digital Converter (A/D) Module                        |   |

| 12.0  | Special Features of the CPU                                     | 9 |

| 13.0  | Instruction Set Summary 109                                     | 5 |

| 14.0  | Development Support                                             |   |

| 15.0  | Electrical Characteristics                                      | 9 |

| 16.0  | DC and AC Characteristics Graphs and Tables                     | 1 |

| 17.0  | Packaging Information 15                                        | 1 |

| Apper | ndix A: Revision History                                        | 1 |

|       | ndix B: Device Differences                                      |   |

| Apper | ndix C: Conversion Considerations                               | 2 |

| Index |                                                                 | 3 |

| On-Li | ne Support                                                      | 9 |

|       | er Response                                                     |   |

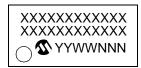

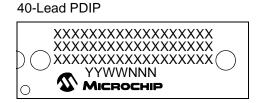

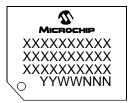

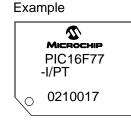

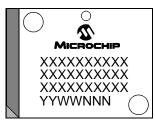

| PIC16 | F7X Product Identification System                               | 1 |

# TO OUR VALUED CUSTOMERS

It is our intention to provide our valued customers with the best documentation possible to ensure successful use of your Microchip products. To this end, we will continue to improve our publications to better suit your needs. Our publications will be refined and enhanced as new volumes and updates are introduced.

If you have any questions or comments regarding this publication, please contact the Marketing Communications Department via E-mail at **docerrors@mail.microchip.com** or fax the **Reader Response Form** in the back of this data sheet to (480) 792-4150. We welcome your feedback.

# Most Current Data Sheet

To obtain the most up-to-date version of this data sheet, please register at our Worldwide Web site at:

http://www.microchip.com

You can determine the version of a data sheet by examining its literature number found on the bottom outside corner of any page. The last character of the literature number is the version number, (e.g., DS30000A is version A of document DS30000).

## Errata

An errata sheet, describing minor operational differences from the data sheet and recommended workarounds, may exist for current devices. As device/documentation issues become known to us, we will publish an errata sheet. The errata will specify the revision of silicon and revision of document to which it applies.

To determine if an errata sheet exists for a particular device, please check with one of the following:

- Microchip's Worldwide Web site; http://www.microchip.com

- Your local Microchip sales office (see last page)

- The Microchip Corporate Literature Center; U.S. FAX: (480) 792-7277

When contacting a sales office or the literature center, please specify which device, revision of silicon and data sheet (include literature number) you are using.

# **Customer Notification System**

Register on our web site at www.microchip.com/cn to receive the most current information on all of our products.

| TABLE 1-2: | PIC16F73 AND PIC16F76 PINOUT DESCRIPTION (CONTINUED) |

|------------|------------------------------------------------------|

|------------|------------------------------------------------------|

| Pin Name        | DIP<br>SSOP<br>SOIC<br>Pin# | MLF<br>Pin# | I/O/P<br>Type | Buffer<br>Type        | Description                                                      |

|-----------------|-----------------------------|-------------|---------------|-----------------------|------------------------------------------------------------------|

|                 |                             |             |               |                       | PORTB is a bi-directional I/O port. PORTB can be software        |

|                 |                             |             |               | (o(1)                 | programmed for internal weak pull-up on all inputs.              |

| RB0/INT         | 21                          | 18          |               | TTL/ST <sup>(1)</sup> |                                                                  |

| RB0             |                             |             | I/O           |                       | Digital I/O.                                                     |

| INT             |                             |             | I             |                       | External interrupt.                                              |

| RB1             | 22                          | 19          | I/O           | TTL                   | Digital I/O.                                                     |

| RB2             | 23                          | 20          | I/O           | TTL                   | Digital I/O.                                                     |

| RB3/PGM         | 24                          | 21          |               | TTL                   |                                                                  |

| RB3             |                             |             | I/O           |                       | Digital I/O.                                                     |

| PGM             |                             |             | I/O           |                       | Low voltage ICSP programming enable pin.                         |

| RB4             | 25                          | 22          | I/O           | TTL                   | Digital I/O.                                                     |

| RB5             | 26                          | 23          | I/O           | TTL                   | Digital I/O.                                                     |

| RB6/PGC         | 27                          | 24          | ., 0          | TTL/ST <sup>(2)</sup> | Digital i/ O.                                                    |

| RB6             | 21                          | 24          | I/O           | 112/31.7              | Digital I/O.                                                     |

| PGC             |                             |             | I/O           |                       | In-Circuit Debugger and ICSP programming clock.                  |

|                 | 20                          | 25          | ., O          | TTL/ST <sup>(2)</sup> |                                                                  |

| RB7/PGD<br>RB7  | 28                          | 25          | I/O           | 11L/51(-)             | Digital I/O.                                                     |

| PGD             |                             |             | 1/O           |                       | In-Circuit Debugger and ICSP programming data.                   |

| FGD             |                             |             | 1/0           |                       |                                                                  |

|                 |                             |             |               |                       | PORTC is a bi-directional I/O port.                              |

| RC0/T1OSO/T1CKI | 11                          | 8           |               | ST                    |                                                                  |

| RC0             |                             |             | I/O           |                       | Digital I/O.                                                     |

| T1OSO           |                             |             | 0             |                       | Timer1 oscillator output.                                        |

| T1CKI           |                             |             | I             |                       | Timer1 external clock input.                                     |

| RC1/T1OSI/CCP2  | 12                          | 9           |               | ST                    |                                                                  |

| RC1             |                             |             | I/O           |                       | Digital I/O.                                                     |

| T1OSI           |                             |             | I             |                       | Timer1 oscillator input.                                         |

| CCP2            |                             |             | I/O           |                       | Capture2 input, Compare2 output, PWM2 output.                    |

| RC2/CCP1        | 13                          | 10          |               | ST                    |                                                                  |

| RC2             |                             |             | I/O           |                       | Digital I/O.                                                     |

| CCP1            |                             |             | I/O           |                       | Capture1 input/Compare1 output/PWM1 output.                      |

| RC3/SCK/SCL     | 14                          | 11          |               | ST                    |                                                                  |

| RC3             |                             |             | I/O           |                       | Digital I/O.                                                     |

| SCK             |                             |             | I/O           |                       | Synchronous serial clock input/output for SPI mode.              |

| SCL             |                             |             | I/O           |                       | Synchronous serial clock input/output for I <sup>2</sup> C mode. |

| RC4/SDI/SDA     | 15                          | 12          |               | ST                    |                                                                  |

| RC4             |                             |             | I/O           |                       | Digital I/O.                                                     |

| SDI             |                             |             | I             |                       | SPI data in.                                                     |

| SDA             |                             |             | I/O           |                       | I <sup>2</sup> C data I/O.                                       |

| RC5/SDO         | 16                          | 13          |               | ST                    |                                                                  |

| RC5             |                             |             | I/O           |                       | Digital I/O.                                                     |

| SDO             |                             |             | 0             |                       | SPI data out.                                                    |

| RC6/TX/CK       | 17                          | 14          |               | ST                    |                                                                  |

| RC6             |                             |             | I/O           |                       | Digital I/O.                                                     |

| TX              |                             |             | 0             |                       | USART asynchronous transmit.                                     |

| СК              |                             |             | I/O           |                       | USART 1 synchronous clock.                                       |

| RC7/RX/DT       | 18                          | 15          |               | ST                    |                                                                  |

| RC7             |                             |             | I/O           |                       | Digital I/O.                                                     |

| RX              |                             |             | I             |                       | USART asynchronous receive.                                      |

| DT              |                             |             | I/O           |                       | USART synchronous data.                                          |

| Vss             | 8, 19                       | 5, 16       | Р             | —                     | Ground reference for logic and I/O pins.                         |

| V 55            | 1                           | 47          | Р             | 1                     | Desitive events for legic and 1/0 nine                           |

| VDD             | 20                          | 17          | Р             | —                     | Positive supply for logic and I/O pins.                          |

This buffer is a Schmitt Trigger input when used in Serial Programming mode.

This buffer is a Schmitt Trigger input when configured in RC Oscillator mode and a CMOS input otherwise.

## TABLE 1-3:PIC16F74 AND PIC16F77 PINOUT DESCRIPTION

| OSC1/CLKI<br>OSC1<br>CLKI<br>OSC2/CLKO<br>OSC2<br>CLKO<br>MCLR/VPP<br>MCLR<br>VPP | 13 | 14<br>15 | 30<br>31 | 1        | ST/CMOS <sup>(4)</sup> | Oscillator crystal or external clock input.<br>Oscillator crystal input or external clock source input.<br>ST buffer when configured in RC mode. Otherwise<br>CMOS.<br>External clock source input. Always associated with pin |

|-----------------------------------------------------------------------------------|----|----------|----------|----------|------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| CLKI<br>OSC2/CLKO<br>OSC2<br>CLKO<br><u>MCLR/VPP</u><br>MCLR                      | 14 | 15       | 31       | I        |                        | Oscillator crystal input or external clock source input.<br>ST buffer when configured in RC mode. Otherwise<br>CMOS.<br>External clock source input. Always associated with pin                                                |

| OSC2/CLKO<br>OSC2<br>CLKO<br>MCLR/VPP<br>MCLR                                     | 14 | 15       | 31       |          |                        | CMOS.<br>External clock source input. Always associated with pin                                                                                                                                                               |

| OSC2/CLKO<br>OSC2<br>CLKO<br>MCLR/VPP<br>MCLR                                     | 14 | 15       | 31       |          |                        | External clock source input. Always associated with pin                                                                                                                                                                        |

| OSC2<br>CLKO<br>MCLR/VPP<br>MCLR                                                  | 14 | 15       | 31       |          |                        |                                                                                                                                                                                                                                |

| OSC2<br>CLKO<br>MCLR/VPP<br>MCLR                                                  | 14 | 15       | 31       | 0        |                        | function OSC1 (see OSC1/CLKI, OSC2/CLKO pins).                                                                                                                                                                                 |

| CLKO<br>MCLR/VPP<br>MCLR                                                          |    |          |          | <u> </u> | I —                    | Oscillator crystal or clock output.                                                                                                                                                                                            |

| MCLR/Vpp<br>MCLR                                                                  |    |          |          | 0        |                        | Oscillator crystal output.                                                                                                                                                                                                     |

| MCLR/Vpp<br>MCLR                                                                  |    |          |          |          |                        | Connects to crystal or resonator in Crystal Oscillator                                                                                                                                                                         |

| MCLR/Vpp<br>MCLR                                                                  |    |          |          |          |                        | mode.                                                                                                                                                                                                                          |

| MCLR                                                                              |    |          |          | 0        |                        | In RC mode, OSC2 pin outputs CLKO, which has 1/4                                                                                                                                                                               |

| MCLR                                                                              |    |          |          |          |                        | the frequency of OSC1 and denotes the instruction                                                                                                                                                                              |

| MCLR                                                                              |    |          |          |          |                        | cycle rate.                                                                                                                                                                                                                    |

|                                                                                   | 1  | 2        | 18       |          | ST                     | Master Clear (input) or programming voltage (output).                                                                                                                                                                          |

| Vpp                                                                               |    |          |          | I        |                        | Master Clear (Reset) input. This pin is an active low                                                                                                                                                                          |

| VPP                                                                               |    |          |          |          |                        | RESET to the device.                                                                                                                                                                                                           |

|                                                                                   |    |          |          | Р        |                        | Programming voltage input.                                                                                                                                                                                                     |

|                                                                                   |    |          |          |          |                        | PORTA is a bi-directional I/O port.                                                                                                                                                                                            |

| RA0/AN0                                                                           | 2  | 3        | 19       |          | TTL                    |                                                                                                                                                                                                                                |

| RA0                                                                               |    |          |          | I/O      |                        | Digital I/O.                                                                                                                                                                                                                   |

| AN0                                                                               |    |          |          | I        |                        | Analog input 0.                                                                                                                                                                                                                |

| RA1/AN1                                                                           | 3  | 4        | 20       |          | TTL                    |                                                                                                                                                                                                                                |

| RA1                                                                               |    |          |          | I/O      |                        | Digital I/O.                                                                                                                                                                                                                   |

| AN1                                                                               |    |          |          | I        |                        | Analog input 1.                                                                                                                                                                                                                |

| RA2/AN2                                                                           | 4  | 5        | 21       |          | TTL                    |                                                                                                                                                                                                                                |

| RA2                                                                               |    |          |          | I/O      |                        | Digital I/O.                                                                                                                                                                                                                   |

| AN2                                                                               |    |          |          | I        |                        | Analog input 2.                                                                                                                                                                                                                |

| RA3/AN3/Vref                                                                      | 5  | 6        | 22       |          | TTL                    |                                                                                                                                                                                                                                |

| RA3                                                                               |    |          |          | I/O      |                        | Digital I/O.                                                                                                                                                                                                                   |

| AN3                                                                               |    |          |          | I        |                        | Analog input 3.                                                                                                                                                                                                                |

| VREF                                                                              |    |          |          | I        |                        | A/D reference voltage input.                                                                                                                                                                                                   |

| RA4/T0CKI                                                                         | 6  | 7        | 23       |          | ST                     |                                                                                                                                                                                                                                |

| RA4                                                                               |    |          |          | I/O      |                        | Digital I/O – Open drain when configured as output.                                                                                                                                                                            |

| TOCKI                                                                             |    |          |          | I        |                        | Timer0 external clock input.                                                                                                                                                                                                   |

| RA5/SS/AN4                                                                        | 7  | 8        | 24       |          | TTL                    |                                                                                                                                                                                                                                |

| RA5                                                                               |    | -        |          | I/O      |                        | Digital I/O.                                                                                                                                                                                                                   |

| SS                                                                                | 1  |          |          | 1        |                        | SPI slave select input.                                                                                                                                                                                                        |

| AN4                                                                               |    |          |          |          | 1                      |                                                                                                                                                                                                                                |

| Legend: I = inpu                                                                  |    | 1        |          |          |                        | Analog input 4.                                                                                                                                                                                                                |

— = Not used TTL = TTL input ST = Schmitt Trigger input

**Note 1:** This buffer is a Schmitt Trigger input when configured as an external interrupt.

2: This buffer is a Schmitt Trigger input when used in Serial Programming mode.

**3:** This buffer is a Schmitt Trigger input when configured as general purpose I/O and a TTL input when used in the Parallel Slave Port mode (for interfacing to a microprocessor bus).

4: This buffer is a Schmitt Trigger input when configured in RC Oscillator mode and a CMOS input otherwise.

| Address              | Name       | Bit 7                                                                                          | Bit 6                         | Bit 5                      | Bit 4          | Bit 3   | Bit 2     | Bit 1  | Bit 0  | Value on:<br>POR,<br>BOR | Details<br>on page |

|----------------------|------------|------------------------------------------------------------------------------------------------|-------------------------------|----------------------------|----------------|---------|-----------|--------|--------|--------------------------|--------------------|

| Bank 1               |            |                                                                                                |                               |                            |                |         |           |        |        |                          |                    |

| 80h <sup>(4)</sup>   | INDF       | Addressing this location uses contents of FSR to address data memory (not a physical register) |                               |                            |                |         |           |        |        |                          | 27, 96             |

| 81h                  | OPTION_REG | RBPU                                                                                           | INTEDG                        | TOCS                       | T0SE           | PSA     | PS2       | PS1    | PS0    | 1111 1111                | 20, 44, 96         |

| 82h <sup>(4)</sup>   | PCL        | Program Counter's (PC) Least Significant Byte                                                  |                               |                            |                |         |           |        |        |                          | 26, 96             |

| 83h <sup>(4)</sup>   | STATUS     | IRP                                                                                            | RP1                           | RP0                        | TO             | PD      | Z         | DC     | С      | 0001 1xxx                | 19, 96             |

| 84h <sup>(4)</sup>   | FSR        | Indirect data memory address pointer                                                           |                               |                            |                |         |           |        |        |                          | 27, 96             |

| 85h                  | TRISA      |                                                                                                | _                             | PORTA Dat                  | a Direction Re | egister |           |        |        | 11 1111                  | 32, 96             |

| 86h                  | TRISB      | PORTB D                                                                                        | ata Direction                 | Register                   |                | •       |           |        |        | 1111 1111                | 34, 96             |

| 87h                  | TRISC      | PORTC D                                                                                        | PORTC Data Direction Register |                            |                |         |           |        |        |                          | 35, 96             |

| 88h <sup>(5)</sup>   | TRISD      | PORTD D                                                                                        | PORTD Data Direction Register |                            |                |         |           |        |        | 1111 1111                | 36, 96             |

| 89h <sup>(5)</sup>   | TRISE      | IBF OBF IBOV PSPMODE — PORTE Data Direction Bits                                               |                               |                            |                |         | 0000 -111 | 38, 96 |        |                          |                    |

| 8Ah <sup>(1,4)</sup> | PCLATH     | — — — Write Buffer for the upper 5 bits of the Program Counter                                 |                               |                            |                |         |           |        | 0 0000 | 21, 96                   |                    |

| 8Bh <sup>(4)</sup>   | INTCON     | GIE                                                                                            | PEIE                          | TMR0IE                     | INTE           | RBIE    | TMR0IF    | INTF   | RBIF   | 0000 000x                | 23, 96             |

| 8Ch                  | PIE1       | PSPIE <sup>(3)</sup>                                                                           | ADIE                          | RCIE                       | TXIE           | SSPIE   | CCP1IE    | TMR2IE | TMR1IE | 0000 0000                | 22,96              |

| 8Dh                  | PIE2       | _                                                                                              | _                             | _                          | _              | _       |           | _      | CCP2IE | 0                        | 24, 97             |

| 8Eh                  | PCON       | _                                                                                              | _                             | _                          | _              |         | _         | POR    | BOR    | dd                       | 25, 97             |

| 8Fh                  | —          | Unimplem                                                                                       | Unimplemented                 |                            |                |         |           |        |        |                          |                    |

| 90h                  | —          | Unimplem                                                                                       | ented                         |                            |                |         |           |        |        | _                        | _                  |

| 91h                  | —          | Unimplem                                                                                       | ented                         |                            |                |         |           |        |        | —                        | —                  |

| 92h                  | PR2        | Timer2 Pe                                                                                      | riod Registe                  | r                          |                |         |           |        |        | 1111 1111                | 52, 97             |

| 93h                  | SSPADD     | Synchrono                                                                                      | ous Serial Po                 | ort (I <sup>2</sup> C mode | ) Address Reg  | gister  |           |        |        | 0000 0000                | 68, 97             |

| 94h                  | SSPSTAT    | SMP                                                                                            | CKE                           | D/A                        | Р              | S       | R/W       | UA     | BF     | 0000 0000                | 60, 97             |

| 95h                  | —          | Unimplem                                                                                       | ented                         |                            |                |         |           |        |        | —                        | —                  |

| 96h                  | —          | Unimplem                                                                                       | ented                         |                            |                |         |           |        |        | —                        | —                  |

| 97h                  | —          | Unimplem                                                                                       | ented                         |                            |                |         | _         |        | -      | —                        | —                  |

| 98h                  | TXSTA      | CSRC                                                                                           | TX9                           | TXEN                       | SYNC           |         | BRGH      | TRMT   | TX9D   | 0000 -010                | 69, 97             |

| 99h                  | SPBRG      | Baud Rate                                                                                      | e Generator I                 | Register                   |                |         |           |        |        | 0000 0000                | 71, 97             |

| 9Ah                  | —          | Unimplem                                                                                       | ented                         |                            |                |         |           |        |        | —                        |                    |

| 9Bh                  | —          | Unimplem                                                                                       | ented                         |                            |                |         |           |        |        | -                        |                    |

| 9Ch                  | —          | Unimplem                                                                                       | ented                         |                            |                |         |           |        |        | _                        |                    |

| 9Dh                  | —          | Unimplem                                                                                       | ented                         |                            |                |         |           |        |        | _                        |                    |

| 9Eh                  | —          | Unimplem                                                                                       | ented                         |                            |                |         |           |        |        | -                        |                    |

| 9Fh                  | ADCON1     | _                                                                                              | _                             | _                          | _              | _       | PCFG2     | PCFG1  | PCFG0  | 000                      | 84, 97             |

| TABLE 2-1: SPECIAL FUNCTION REGISTER SUMMARY (CONTINUED) |

|----------------------------------------------------------|

|----------------------------------------------------------|

$\label{eq:legend: Legend: Legend: u = unchanged, q = value depends on condition, - = unimplemented, read as '0', r = reserved.$ Shaded locations are unimplemented, read as '0'.

Note 1: The upper byte of the program counter is not directly accessible. PCLATH is a holding register for the PC<12:8>, whose contents are transferred to the upper byte of the program counter during branches (CALL or GOTO).

2: Other (non power-up) RESETS include external RESET through MCLR and Watchdog Timer Reset. 3: Bits PSPIE and PSPIF are reserved on the 28-pin devices; always maintain these bits clear.

4: These registers can be addressed from any bank.

5: PORTD, PORTE, TRISD, and TRISE are not physically implemented on the 28-pin devices, read as '0'.

6: This bit always reads as a '1'.

| <b>TABLE 2-1:</b> | SPECIAL FUNCTION REGISTER SUMMARY | (CONTINUED) |

|-------------------|-----------------------------------|-------------|

|-------------------|-----------------------------------|-------------|

| Address               | Name       | Bit 7                          | Bit 6                                                                                          | Bit 5                                                    | Bit 4                             | Bit 3         | Bit 2         | Bit 1         | Bit 0        | Value on:<br>POR,<br>BOR | Details<br>on page |

|-----------------------|------------|--------------------------------|------------------------------------------------------------------------------------------------|----------------------------------------------------------|-----------------------------------|---------------|---------------|---------------|--------------|--------------------------|--------------------|

| Bank 2                |            |                                |                                                                                                |                                                          |                                   |               |               |               |              |                          |                    |

| 100h <sup>(4)</sup>   | INDF       | Addressin                      | Addressing this location uses contents of FSR to address data memory (not a physical register) |                                                          |                                   |               |               |               |              |                          | 27, 96             |

| 101h                  | TMR0       | Timer0 Mo                      | Timer0 Module Register                                                                         |                                                          |                                   |               |               |               |              |                          | 45, 96             |

| 102h <sup>(4)</sup>   | PCL        | Program C                      | Counter (PC)                                                                                   | Least Signif                                             | icant Byte                        |               |               |               |              | 0000 0000                | 26, 96             |

| 103h <sup>(4)</sup>   | STATUS     | IRP                            | RP1                                                                                            | RP0                                                      | ТО                                | PD            | Z             | DC            | С            | 0001 1xxx                | 19, 96             |

| 104h <sup>(4)</sup>   | FSR        | Indirect Da                    | ata Memory /                                                                                   | Address Poir                                             | nter                              |               |               |               |              | xxxx xxxx                | 27, 96             |

| 105h                  | —          | Unimplem                       | ented                                                                                          |                                                          |                                   |               |               |               |              | _                        | —                  |

| 106h                  | PORTB      | PORTB D                        | ata Latch wh                                                                                   | en written: F                                            | ORTB pins w                       | hen read      |               |               |              | xxxx xxxx                | 34, 96             |

| 107h                  | _          | Unimplem                       | ented                                                                                          |                                                          |                                   |               |               |               |              | —                        | —                  |

| 108h                  | —          | Unimplem                       | ented                                                                                          |                                                          |                                   |               |               |               |              | —                        | —                  |

| 109h                  | —          | Unimplem                       | ented                                                                                          |                                                          |                                   |               |               |               |              | _                        | —                  |

| 10Ah <sup>(1,4)</sup> | PCLATH     | —                              | _                                                                                              | Write Buffer for the upper 5 bits of the Program Counter |                                   |               |               |               |              | 0 0000                   | 21, 96             |

| 10Bh <sup>(4)</sup>   | INTCON     | GIE                            | PEIE                                                                                           | TMR0IE                                                   | TMROIE INTE RBIE TMROIF INTF RBIF |               |               |               |              |                          | 23, 96             |

| 10Ch                  | PMDATA     | Data Register Low Byte         |                                                                                                |                                                          |                                   |               |               |               |              |                          | 29, 97             |

| 10Dh                  | PMADR      | Address Register Low Byte      |                                                                                                |                                                          |                                   |               |               |               |              | xxxx xxxx                | 29, 97             |

| 10Eh                  | PMDATH     | Data Register High Byte        |                                                                                                |                                                          |                                   |               |               |               |              | xxxx xxxx                | 29, 97             |

| 10Fh                  | PMADRH     | — — Address Register High Byte |                                                                                                |                                                          |                                   |               |               |               |              |                          | 29, 97             |

| Bank 3                |            |                                |                                                                                                |                                                          |                                   |               |               |               |              |                          |                    |

| 180h <sup>(4)</sup>   | INDF       | Addressin                      | g this locatio                                                                                 | n uses conte                                             | ents of FSR to                    | address data  | a memory (r   | not a physica | al register) | 0000 0000                | 27, 96             |

| 181h                  | OPTION_REG | RBPU                           | INTEDG                                                                                         | TOCS                                                     | TOSE                              | PSA           | PS2           | PS1           | PS0          | 1111 1111                | 20, 44, 96         |

| 182h <sup>(4)</sup>   | PCL        | Program C                      | Counter (PC)                                                                                   | Least Signif                                             | icant Byte                        |               |               |               |              | 0000 0000                | 26, 96             |

| 183h <sup>(4)</sup>   | STATUS     | IRP                            | RP1                                                                                            | RP0                                                      | TO                                | PD            | Z             | DC            | С            | 0001 1xxx                | 19, 96             |

| 184h <sup>(4)</sup>   | FSR        | Indirect Da                    | ata Memory /                                                                                   | Address Poir                                             | nter                              |               |               |               |              | xxxx xxxx                | 27, 96             |

| 185h                  | —          | Unimplem                       | ented                                                                                          |                                                          |                                   |               |               |               |              | _                        | _                  |

| 186h                  | TRISB      | PORTB D                        | ata Direction                                                                                  | Register                                                 |                                   |               |               |               |              | 1111 1111                | 34, 96             |

| 187h                  | —          | Unimplem                       | ented                                                                                          |                                                          |                                   |               |               |               |              | _                        | _                  |

| 188h                  | —          | Unimplem                       | ented                                                                                          |                                                          |                                   |               |               |               |              | _                        | _                  |

| 189h                  | —          | Unimplem                       | Unimplemented                                                                                  |                                                          |                                   |               |               |               |              | _                        | _                  |

| 18Ah <sup>(1,4)</sup> | PCLATH     | _                              |                                                                                                | _                                                        | Write Buffer                      | for the upper | 5 bits of the | Program C     | ounter       | 0 0000                   | 21, 96             |

| 18Bh <sup>(4)</sup>   | INTCON     | GIE                            | PEIE                                                                                           | TMR0IE                                                   | INTE                              | RBIE          | TMR0IF        | INTF          | RBIF         | 0000 000x                | 23, 96             |

| 18Ch                  | PMCON1     | (6)                            | _                                                                                              | —                                                        | —                                 | —             | _             | —             | RD           | 10                       | 29, 97             |

| 18Dh                  | —          | Unimplem                       | ented                                                                                          |                                                          |                                   |               |               |               |              | _                        |                    |

| 18Eh                  | —          | Reserved                       | maintain clea                                                                                  | ar                                                       |                                   |               |               |               |              | 0000 0000                |                    |

| 18Fh                  | _          | Reserved                       | maintain clea                                                                                  | ar                                                       |                                   |               |               |               |              | 0000 0000                |                    |

Legend: x = unknown, u = unchanged, q = value depends on condition, - = unimplemented, read as '0', r = reserved. Shaded locations are unimplemented, read as '0'.

**Note** 1: The upper byte of the program counter is not directly accessible. PCLATH is a holding register for the PC<12:8>, whose contents are transferred to the upper byte of the program counter during branches (CALL or GOTO).

2: Other (non power-up) RESETS include external RESET through MCLR and Watchdog Timer Reset.

3: Bits PSPIE and PSPIF are reserved on the 28-pin devices; always maintain these bits clear.

4: These registers can be addressed from any bank.

5: PORTD, PORTE, TRISD, and TRISE are not physically implemented on the 28-pin devices, read as '0'.

6: This bit always reads as a '1'.

#### 3.0 **READING PROGRAM MEMORY**

The FLASH Program Memory is readable during normal operation over the entire VDD range. It is indirectly addressed through Special Function Registers (SFR). Up to 14-bit numbers can be stored in memory for use as calibration parameters, serial numbers, packed 7-bit ASCII, etc. Executing a program memory location containing data that forms an invalid instruction results in a NOP.

There are five SFRs used to read the program and memory. These registers are:

- PMCON1

- PMDATA

- PMDATH

- PMADR

- PMADRH

The program memory allows word reads. Program memory access allows for checksum calculation and reading calibration tables.

When interfacing to the program memory block, the PMDATH:PMDATA registers form a two-byte word, which holds the 14-bit data for reads. The PMADRH:PMADR registers form a two-byte word, which holds the 13-bit address of the FLASH location being accessed. These devices can have up to 8K words of program FLASH, with an address range from Oh to 3FFFh. The unused upper bits in both the PMDATH and PMADRH registers are not implemented and read as "0's".

#### 3.1 **PMADR**

The address registers can address up to a maximum of 8K words of program FLASH.

When selecting a program address value, the MSByte of the address is written to the PMADRH register and the LSByte is written to the PMADR register. The upper MSbits of PMADRH must always be clear.

#### 3.2 PMCON1 Register

PMCON1 is the control register for memory accesses.

The control bit RD initiates read operations. This bit cannot be cleared, only set, in software. It is cleared in hardware at the completion of the read operation.

#### **REGISTER 3-1:** PMCON1 REGISTER (ADDRESS 18Ch)

|         | R-1                                                                                                             | U-0         | U-0   | U-0 | U-x | U-0 | U-0 | R/S-0 |  |  |  |  |  |  |

|---------|-----------------------------------------------------------------------------------------------------------------|-------------|-------|-----|-----|-----|-----|-------|--|--|--|--|--|--|

|         | reserved — — — — — — RD                                                                                         |             |       |     |     |     |     |       |  |  |  |  |  |  |

|         | bit 7                                                                                                           |             |       |     |     |     |     | bit 0 |  |  |  |  |  |  |

|         |                                                                                                                 |             |       |     |     |     |     |       |  |  |  |  |  |  |

| bit 7   | Reserved: Read as '1'                                                                                           |             |       |     |     |     |     |       |  |  |  |  |  |  |

| bit 6-1 | Unimplemented: Read as '0'                                                                                      |             |       |     |     |     |     |       |  |  |  |  |  |  |

| bit 0   | RD: Read Control bit                                                                                            |             |       |     |     |     |     |       |  |  |  |  |  |  |

|         | 1 = Initiates a FLASH read, RD is cleared in hardware. The RD bit can only be set (not cleared)<br>in software. |             |       |     |     |     |     |       |  |  |  |  |  |  |

|         | 0 = FLASH                                                                                                       | l read comp | leted |     |     |     |     |       |  |  |  |  |  |  |

|         | _                                                                                                               |             |       |     |     |     |     |       |  |  |  |  |  |  |

|         | Legend:                                                                                                         |             |       |     |     |     |     |       |  |  |  |  |  |  |

| Legend:                  |                  |                      |                    |

|--------------------------|------------------|----------------------|--------------------|

| R = Readable bit         | W = Writable bit | U = Unimplemented    | bit, read as '0'   |

| - n = Value at POR reset | '1' = Bit is set | '0' = Bit is cleared | x = Bit is unknown |

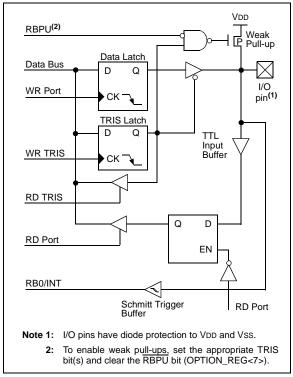

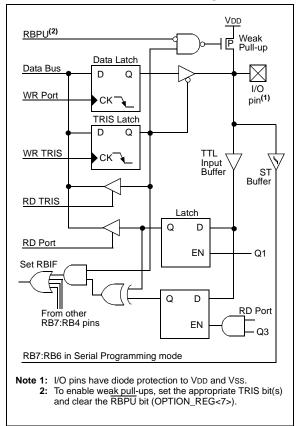

# 4.2 PORTB and the TRISB Register

PORTB is an 8-bit wide, bi-directional port. The corresponding data direction register is TRISB. Setting a TRISB bit (= '1') will make the corresponding PORTB pin an input (i.e., put the corresponding output driver in a Hi-Impedance mode). Clearing a TRISB bit (= '0') will make the corresponding PORTB pin an output (i.e., put the contents of the output latch on the selected pin).

Each of the PORTB pins has a weak internal pull-up. A single control bit can turn on all the pull-ups. This is performed by clearing bit RBPU (OPTION\_REG<7>). The weak pull-up is automatically turned off when the port pin is configured as an output. The pull-ups are disabled on a Power-on Reset.

Four of the PORTB pins (RB7:RB4) have an interrupt-on-change feature. Only pins configured as inputs can cause this interrupt to occur (i.e., any RB7:RB4 pin configured as an output is excluded from the interrupt-on-change comparison). The input pins (of RB7:RB4) are compared with the old value latched on the last read of PORTB. The "mismatch" outputs of RB7:RB4 are ORed together to generate the RB Port Change Interrupt with flag bit RBIF (INTCON<0>). This interrupt can wake the device from SLEEP. The user, in the Interrupt Service Routine, can clear the interrupt in the following manner:

- a) Any read or write of PORTB. This will end the mismatch condition.

- b) Clear flag bit RBIF.

A mismatch condition will continue to set flag bit RBIF. Reading PORTB will end the mismatch condition and allow flag bit RBIF to be cleared.

The interrupt-on-change feature is recommended for wake-up on key depression operation and operations where PORTB is only used for the interrupt-on-change feature. Polling of PORTB is not recommended while using the interrupt-on-change feature.

This interrupt on mismatch feature, together with software configureable pull-ups on these four pins, allow easy interface to a keypad and make it possible for wake-up on key depression. Refer to the Embedded Control Handbook, "Implementing Wake-up on Key Stroke" (AN552).

RB0/INT is an external interrupt input pin and is configured using the INTEDG bit (OPTION\_REG<6>).

RB0/INT is discussed in detail in Section 12.11.1.

### FIGURE 4-4: BLOCK DIAGRAM OF RB7:RB4 PINS

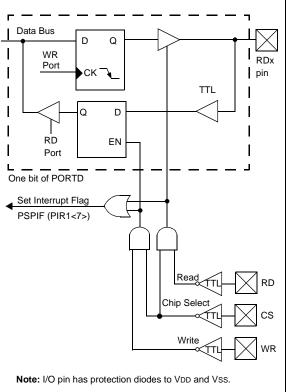

# 4.6 Parallel Slave Port

The Parallel Slave Port (PSP) is not implemented on the PIC16F73 or PIC16F76.

PORTD operates as an 8-bit wide Parallel Slave Port, or Microprocessor Port, when control bit PSPMODE (TRISE<4>) is set. In Slave mode, it is asynchronously readable and writable by an external system using the read control input pin RE0/RD, the write control input pin RE1/WR, and the chip select control input pin RE2/CS.

The PSP can directly interface to an 8-bit microprocessor data bus. The external microprocessor can read or write the PORTD latch as an 8-bit latch. Setting bit PSPMODE enables port pin RE0/RD to be the RD input, RE1/WR to be the WR input and RE2/CS to be the CS (chip select) input. For this functionality, the corresponding data direction bits of the TRISE register (TRISE<2:0>) must be configured as inputs (i.e., set). The A/D port configuration bits PCFG3:PCFG0 (ADCON1<3:0>) must be set to configure pins RE2:RE0 as digital I/O.

There are actually two 8-bit latches, one for data output (external reads) and one for data input (external writes). The firmware writes 8-bit data to the PORTD output data latch and reads data from the PORTD input data latch (note that they have the same address). In this mode, the TRISD register is ignored, since the external device is controlling the direction of data flow.

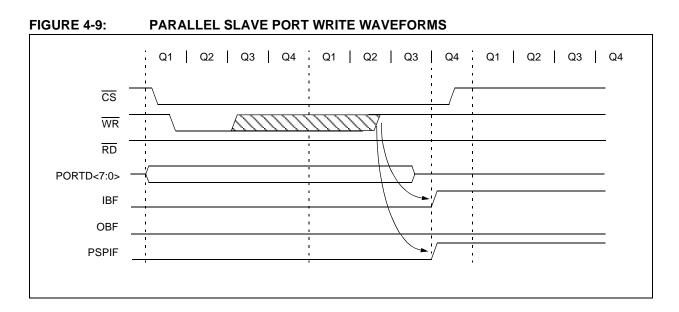

An external write to the PSP occurs when the  $\overline{CS}$  and  $\overline{WR}$  lines are both detected low. Firmware can read the actual data on the PORTD pins during this time. When either the CS or WR lines become high (level triggered), the data on the PORTD pins is latched, and the Input Buffer Full (IBF) status flag bit (TRISE<7>) and interrupt flag bit PSPIF (PIR1<7>) are set on the Q4 clock cycle, following the next Q2 cycle to signal the write is complete (Figure 4-9). Firmware clears the IBF flag by reading the latched PORTD data, and clears the PSPIF bit.

The Input Buffer Overflow (IBOV) status flag bit (TRISE<5>) is set if an external write to the PSP occurs while the IBF flag is set from a previous external write. The previous PORTD data is overwritten with the new data. IBOV is cleared by reading PORTD and clearing IBOV.

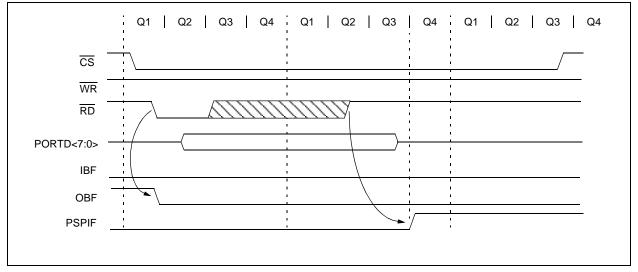

A read from the PSP occurs when both the  $\overline{CS}$  and  $\overline{RD}$  lines are detected low. The data in the PORTD output latch is output to the PORTD pins. The Output Buffer Full (OBF) status flag bit (TRISE<6>) is cleared immediately (Figure 4-10), indicating that the PORTD latch is being read, or has been read by the external bus. If firmware writes new data to the output latch during this time, it is immediately output to the PORTD pins, but OBF will remain cleared.

When either the  $\overline{CS}$  or  $\overline{RD}$  pins are detected high, the PORTD outputs are disabled, and the interrupt flag bit PSPIF is set on the Q4 clock cycle following the next Q2 cycle, indicating that the read is complete. OBF remains low until firmware writes new data to PORTD.

When not in PSP mode, the IBF and OBF bits are held clear. Flag bit IBOV remains unchanged. The PSPIF bit must be cleared by the user in firmware; the interrupt can be disabled by clearing the interrupt enable bit PSPIE (PIE1<7>).

# FIGURE 4-8:

## PORTD AND PORTE BLOCK DIAGRAM (PARALLEL SLAVE PORT)

## FIGURE 4-10: PARALLEL SLAVE PORT READ WAVEFORMS

### TABLE 4-11: REGISTERS ASSOCIATED WITH PARALLEL SLAVE PORT

| Address | Name   | Bit 7                | Bit 6   | Bit 5      | Bit 4         | Bit 3    | Bit 2   | Bit 1       | Bit 0    | Value on:<br>POR,<br>BOR | Value on<br>all other<br>RESETS |

|---------|--------|----------------------|---------|------------|---------------|----------|---------|-------------|----------|--------------------------|---------------------------------|

| 08h     | PORTD  | Port data I          | atch wh | nen writte | en: Port pins | when rea | d       |             |          | xxxx xxxx                | uuuu uuuu                       |

| 09h     | PORTE  | —                    |         | —          |               | —        | RE2     | RE1         | RE0      | xxx                      | uuu                             |

| 89h     | TRISE  | IBF                  | OBF     | IBOV       | PSPMODE       | _        | PORTE D | Data Direct | ion Bits | 0000 -111                | 0000 -111                       |

| 0Ch     | PIR1   | PSPIF <sup>(1)</sup> | ADIF    | RCIF       | TXIF          | SSPIF    | CCP1IF  | TMR2IF      | TMR1IF   | 0000 0000                | 0000 0000                       |

| 8Ch     | PIE1   | PSPIE <sup>(1)</sup> | ADIE    | RCIE       | TXIE          | SSPIE    | CCP1IE  | TMR2IE      | TMR1IE   | 0000 0000                | 0000 0000                       |

| 9Fh     | ADCON1 | _                    | _       | _          | _             | _        | PCFG2   | PCFG1       | PCFG0    | 000                      | 000                             |

Legend: x = unknown, u = unchanged, - = unimplemented, read as '0'. Shaded cells are not used by the Parallel Slave Port.

**Note 1:** Bits PSPIE and PSPIF are reserved on the PIC16F73/76; always maintain these bits clear.

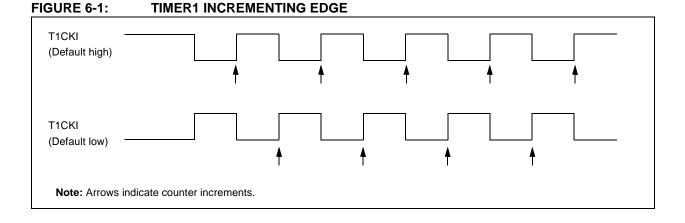

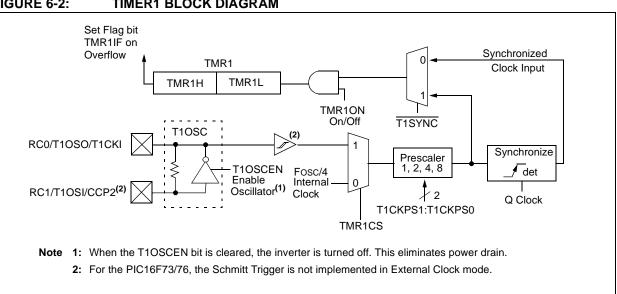

#### 6.1 **Timer1 Operation in Timer Mode**

Timer mode is selected by clearing the TMR1CS (T1CON<1>) bit. In this mode, the input clock to the timer is Fosc/4. The synchronize control bit T1SYNC (T1CON<2>) has no effect, since the internal clock is always in sync.

#### 6.2 **Timer1 Counter Operation**

Timer1 may operate in Asynchronous or Synchronous mode, depending on the setting of the TMR1CS bit.

When Timer1 is being incremented via an external source, increments occur on a rising edge. After Timer1 is enabled in Counter mode, the module must first have a falling edge before the counter begins to increment.

#### 6.3 **Timer1 Operation in Synchronized Counter Mode**

Counter mode is selected by setting bit TMR1CS. In this mode, the timer increments on every rising edge of clock input on pin RC1/T1OSI/CCP2, when bit T1OSCEN is set, or on pin RC0/T1OSO/T1CKI, when bit T1OSCEN is cleared.

If TISYNC is cleared, then the external clock input is synchronized with internal phase clocks. The synchronization is done after the prescaler stage. The prescaler stage is an asynchronous ripple counter.

In this configuration, during SLEEP mode, Timer1 will not increment even if the external clock is present, since the synchronization circuit is shut-off. The prescaler, however, will continue to increment.

#### FIGURE 6-2: TIMER1 BLOCK DIAGRAM

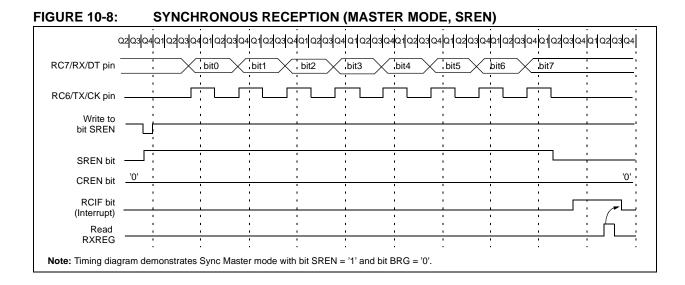

# 10.2 USART Asynchronous Mode

In this mode, the USART uses standard non-return-tozero (NRZ) format (one START bit, eight or nine data bits, and one STOP bit). The most common data format is 8-bits. An on-chip, dedicated, 8-bit baud rate generator can be used to derive standard baud rate frequencies from the oscillator. The USART transmits and receives the LSb first. The USART's transmitter and receiver are functionally independent, but use the same data format and baud rate. The baud rate generator produces a clock, either x16 or x64 of the bit shift rate, depending on bit BRGH (TXSTA<2>). Parity is not supported by the hardware, but can be implemented in software (and stored as the ninth data bit). Asynchronous mode is stopped during SLEEP.

Asynchronous mode is selected by clearing bit SYNC (TXSTA<4>).

The USART Asynchronous module consists of the following important elements:

- · Baud Rate Generator

- Sampling Circuit

- Asynchronous Transmitter

- Asynchronous Receiver

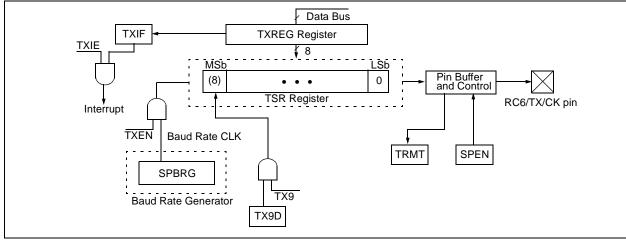

## 10.2.1 USART ASYNCHRONOUS TRANSMITTER

The USART transmitter block diagram is shown in Figure 10-1. The heart of the transmitter is the transmit (serial) shift register (TSR). The shift register obtains its data from the read/write transmit buffer, TXREG. The TXREG register is loaded with data by firmware. The TSR register is not loaded until the STOP bit has been transmitted from the previous load. As soon as the STOP bit is transmitted, the TSR is loaded with new data from the TXREG register (if available). Once the TXREG register transfers the data to the TSR register, the TXREG register is empty. One instruction cycle later, flag bit TXIF (PIR1<4>) and flag bit TRMT (TXSTA<1>)

are set. The TXIF interrupt can be enabled/disabled by setting/clearing enable bit TXIE (PIE1<4>). Flag bit TXIF will be set, regardless of the state of enable bit TXIE and cannot be cleared in software. It will reset only when new data is loaded into the TXREG register. While flag bit TXIF indicates the status of the TXREG register, another bit TRMT (TXSTA<1>) shows the status of the TSR register. Status bit TRMT is a read only bit, which is set one instruction cycle after the TSR register becomes empty, and is cleared one instruction cycle after the TSR register is loaded. No interrupt logic is tied to this bit, so the user has to poll this bit in order to determine if the TSR register is empty.

| Note 1: | The TSR register is not mapped in data      |

|---------|---------------------------------------------|