Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                          |

|----------------------------|--------------------------------------------------------------------------|

| Product Status             | Obsolete                                                                 |

| Core Processor             | PIC                                                                      |

| Core Size                  | 8-Bit                                                                    |

| Speed                      | 20MHz                                                                    |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                                        |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                    |

| Number of I/O              | 33                                                                       |

| Program Memory Size        | 14KB (8K x 14)                                                           |

| Program Memory Type        | FLASH                                                                    |

| EEPROM Size                | -                                                                        |

| RAM Size                   | 368 x 8                                                                  |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 5.5V                                                                |

| Data Converters            | A/D 8x8b                                                                 |

| Oscillator Type            | External                                                                 |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                        |

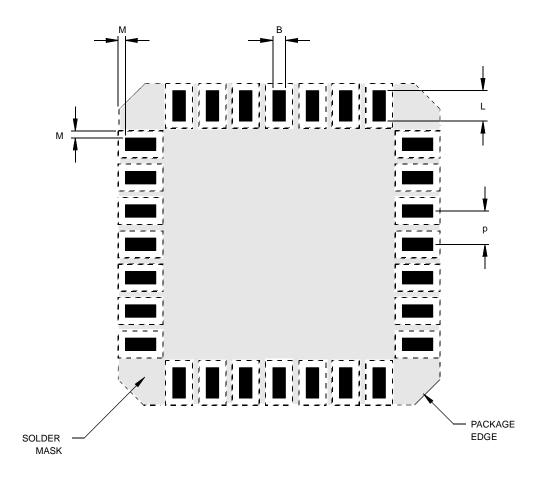

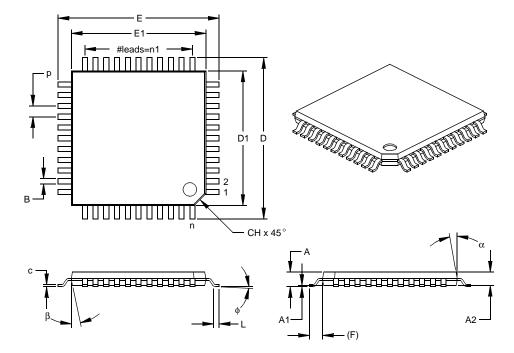

| Mounting Type              | Surface Mount                                                            |

| Package / Case             | 44-LCC (J-Lead)                                                          |

| Supplier Device Package    | 44-PLCC (16.59x16.59)                                                    |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16lf77t-i-l |

|                            |                                                                          |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

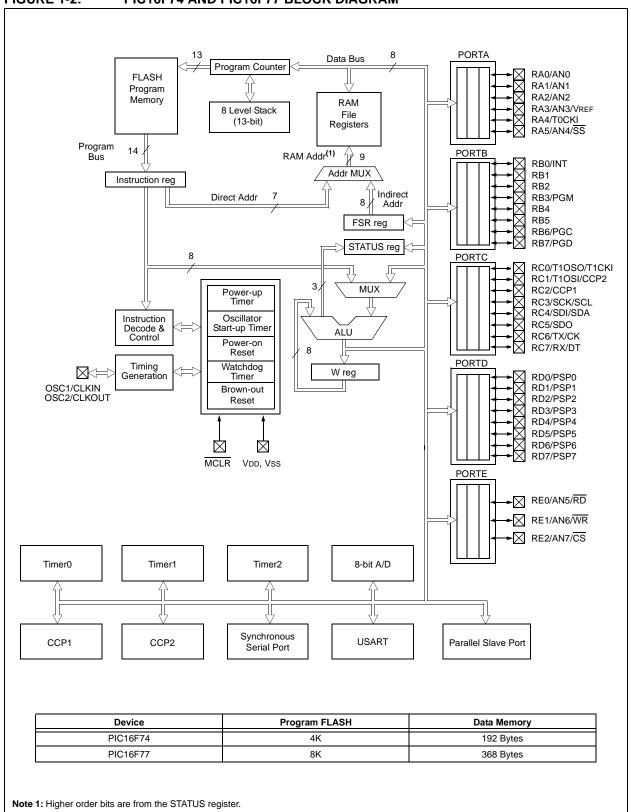

FIGURE 1-2: PIC16F74 AND PIC16F77 BLOCK DIAGRAM

#### PIC16F77/76 REGISTER FILE MAP FIGURE 2-2:

| A                              | File<br>ddress | A                                          | File<br>ddress |                                            | File<br>Address |                                            | File<br>Addres |

|--------------------------------|----------------|--------------------------------------------|----------------|--------------------------------------------|-----------------|--------------------------------------------|----------------|

| Indirect addr.(*)              | 00h            | Indirect addr.(*)                          | 80h            | Indirect addr.(*)                          | 100h            | Indirect addr.(*)                          | 180h           |

| TMR0                           | 01h            | OPTION_REG                                 | 81h            | TMR0                                       | 101h            | OPTION_REG                                 | 181h           |

| PCL                            | 02h            | PCL                                        | 82h            | PCL                                        | 102h            | PCL                                        | 182h           |

| STATUS                         | 03h            | STATUS                                     | 83h            | STATUS                                     | 103h            | STATUS                                     | 183h           |

| FSR                            | 04h            | FSR                                        | 84h            | FSR                                        | 104h            | FSR                                        | 184h           |

| PORTA                          | 05h            | TRISA                                      | 85h            |                                            | 105h            |                                            | 185h           |

| PORTB                          | 06h            | TRISB                                      | 86h            | PORTB                                      | 106h            | TRISB                                      | 186h           |

| PORTC                          | 07h            | TRISC                                      | 87h            |                                            | 107h            |                                            | 187h           |

| PORTD <sup>(1)</sup>           | 08h            | TRISD <sup>(1)</sup>                       | 88h            |                                            | 108h            |                                            | 188h           |

| PORTE <sup>(1)</sup>           | 09h            | TRISE <sup>(1)</sup>                       | 89h            |                                            | 109h            |                                            | 189h           |

| PCLATH                         | 0Ah            | PCLATH                                     | 8Ah            | PCLATH                                     | 10Ah            | PCLATH                                     | 18Ah           |

| INTCON                         | 0Bh            | INTCON                                     | 8Bh            | INTCON                                     | 10Bh            | INTCON                                     | 18Bh           |

| PIR1                           | 0Ch            | PIE1                                       | 8Ch            | PMDATA                                     | 10Ch            | PMCON1                                     | 18Ch           |

| PIR2                           | 0Dh            | PIE2                                       | 8Dh            | PMADR                                      | 10Dh            |                                            | 18Dh           |

| TMR1L                          | 0Eh            | PCON                                       | 8Eh            | PMDATH                                     | 10Eh            |                                            | 18Eh           |

| TMR1H                          | 0Fh            |                                            | 8Fh            | PMADRH                                     | 10Fh            |                                            | 18Fh           |

| T1CON                          | 10h            |                                            | 90h            |                                            | 110h            |                                            | 190h           |

| TMR2                           | 11h            |                                            | 91h            |                                            | 111h            |                                            | 191h           |

| T2CON                          | 12h            | PR2                                        | 92h            |                                            | 112h            |                                            | 192h           |

| SSPBUF                         | 13h            | SSPADD                                     | 93h            |                                            | 113h            |                                            | 193h           |

| SSPCON                         | 14h            | SSPSTAT                                    | 94h            |                                            | 114h            |                                            | 194h           |

| CCPR1L                         | 15h            |                                            | 95h            |                                            | 115h            |                                            | 195h           |

| CCPR1H                         | 16h            |                                            | 96h            |                                            | 116h            |                                            | 196h           |

| CCP1CON                        | 17h            |                                            | 97h            | General                                    | 117h            | General                                    | 197h           |

| RCSTA                          | 18h            | TXSTA                                      | 98h            | Purpose<br>Register                        | 118h            | Purpose<br>Register                        | 198h           |

| TXREG                          | 19h            | SPBRG                                      | 99h            | 16 Bytes                                   | 119h            | 16 Bytes                                   | 199h           |

| RCREG                          | 1Ah            | OF BITO                                    | 9Ah            |                                            | 11Ah            | ,                                          | 19Ah           |

| CCPR2L                         | 1Bh            |                                            | 9Bh            |                                            | 11Bh            |                                            | 19Bh           |

| CCPR2H                         | 1Ch            |                                            | 9Ch            |                                            | 11Ch            |                                            | 19Ch           |

| CCP2CON                        | 1Dh            |                                            | 9Dh            |                                            | 11Dh            |                                            | 19Dh           |

| ADRES                          | 1Eh            |                                            | 9Eh            |                                            | 11Eh            |                                            | 19Eh           |

| ADCON0                         | 1Fh            | ADCON1                                     | 9Fh            |                                            | 11Fh            |                                            | 19Fh           |

| 71200110                       | 20h            | 7.000111                                   |                |                                            | 120h            |                                            |                |

|                                | 2011           |                                            | A0h            |                                            | 12011           |                                            | 1A0h           |

| General<br>Purpose<br>Register |                | General<br>Purpose<br>Register<br>80 Bytes |                | General<br>Purpose<br>Register<br>80 Bytes |                 | General<br>Purpose<br>Register<br>80 Bytes |                |

| 96 Bytes                       |                | accesses                                   | EFh<br>F0h     | accesses                                   | 16Fh<br>170h    | accesses                                   | 1EFh<br>1F0h   |

|                                | 7Fh            | 70h-7Fh                                    | FFh            | 70h-7Fh                                    | 17Fh            | 70h - 7Fh                                  | 1FFh           |

| Bank 0                         |                | Bank 1                                     |                | Bank 2                                     |                 | Bank 3                                     |                |

Unimplemented data memory locations, read as '0'. \* Not a physical register.

Note 1: These registers are not implemented on 28-pin devices.

| <b>TABLE 2-1:</b> | SPECIAL FUNCTION REGISTER SUMMARY | (CONTINUED) |

|-------------------|-----------------------------------|-------------|

|-------------------|-----------------------------------|-------------|

| Address               | Name       | Bit 7       | Bit 6          | Bit 5                                  | Bit 4          | Bit 3          | Bit 2         | Bit 1         | Bit 0        | Value on:<br>POR,<br>BOR | Details<br>on page |  |

|-----------------------|------------|-------------|----------------|----------------------------------------|----------------|----------------|---------------|---------------|--------------|--------------------------|--------------------|--|

| Bank 2                |            |             |                |                                        |                |                |               |               |              |                          |                    |  |

| 100h <sup>(4)</sup>   | INDF       | Addressin   | g this locatio | n uses conte                           | ents of FSR to | address data   | a memory (r   | not a physica | al register) | 0000 0000                | 27, 96             |  |

| 101h                  | TMR0       | Timer0 Mo   | dule Registe   | er                                     |                |                |               |               |              | xxxx xxxx                | 45, 96             |  |

| 102h <sup>(4)</sup>   | PCL        | Program C   | Counter (PC)   | Least Signif                           | icant Byte     |                |               |               |              | 0000 0000                | 26, 96             |  |

| 103h <sup>(4)</sup>   | STATUS     | IRP         | RP1            | RP0                                    | ТО             | PD             | Z             | DC            | С            | 0001 1xxx                | 19, 96             |  |

| 104h <sup>(4)</sup>   | FSR        | Indirect Da | ata Memory /   |                                        | xxxx xxxx      | 27, 96         |               |               |              |                          |                    |  |

| 105h                  | —          | Unimplem    | ented          |                                        |                |                |               |               |              | _                        | —                  |  |

| 106h                  | PORTB      | PORTB D     | ata Latch wh   | en written: F                          | ORTB pins w    | hen read       |               |               |              | xxxx xxxx                | 34, 96             |  |

| 107h                  | _          | Unimplem    | ented          |                                        |                |                |               |               |              | —                        | —                  |  |

| 108h                  | —          | Unimplem    | ented          |                                        | —              | —              |               |               |              |                          |                    |  |

| 109h                  | —          | Unimplem    | ented          |                                        | _              | —              |               |               |              |                          |                    |  |

| 10Ah <sup>(1,4)</sup> | PCLATH     | —           | _              | ounter                                 | 0 0000         | 21, 96         |               |               |              |                          |                    |  |

| 10Bh <sup>(4)</sup>   | INTCON     | GIE         | PEIE           | PEIE TMROIE INTE RBIE TMROIF INTF RBIF |                |                |               |               |              |                          |                    |  |

| 10Ch                  | PMDATA     | Data Regi   | ster Low Byte  | e                                      |                | •              | •             |               | -            | XXXX XXXX                | 29, 97             |  |

| 10Dh                  | PMADR      | Address R   | egister Low    | Byte                                   |                |                |               |               |              | xxxx xxxx                | 29, 97             |  |

| 10Eh                  | PMDATH     | —           | _              | Data Regist                            | ter High Byte  |                |               |               |              | xxxx xxxx                | 29, 97             |  |

| 10Fh                  | PMADRH     |             | _              | _                                      | Address Reg    | gister High By | /te           |               |              | XXXX XXXX                | 29, 97             |  |

| Bank 3                |            |             |                |                                        |                |                |               |               |              |                          |                    |  |

| 180h <sup>(4)</sup>   | INDF       | Addressin   | g this locatio | n uses conte                           | ents of FSR to | address data   | a memory (r   | not a physica | al register) | 0000 0000                | 27, 96             |  |

| 181h                  | OPTION_REG | RBPU        | INTEDG         | TOCS                                   | TOSE           | PSA            | PS2           | PS1           | PS0          | 1111 1111                | 20, 44, 96         |  |

| 182h <sup>(4)</sup>   | PCL        | Program C   | Counter (PC)   | Least Signif                           | icant Byte     |                |               |               |              | 0000 0000                | 26, 96             |  |

| 183h <sup>(4)</sup>   | STATUS     | IRP         | RP1            | RP0                                    | TO             | PD             | Z             | DC            | С            | 0001 1xxx                | 19, 96             |  |

| 184h <sup>(4)</sup>   | FSR        | Indirect Da | ata Memory /   | Address Poir                           | nter           |                |               |               |              | xxxx xxxx                | 27, 96             |  |

| 185h                  | —          | Unimplem    | ented          |                                        |                |                |               |               |              | _                        | _                  |  |

| 186h                  | TRISB      | PORTB D     | ata Direction  | Register                               |                |                |               |               |              | 1111 1111                | 34, 96             |  |

| 187h                  | —          | Unimplem    | ented          |                                        |                |                |               |               |              | _                        | _                  |  |

| 188h                  | —          | Unimplem    | ented          |                                        |                |                |               |               |              | _                        | _                  |  |

| 189h                  | —          | Unimplem    | ented          |                                        | _              | _              |               |               |              |                          |                    |  |

| 18Ah <sup>(1,4)</sup> | PCLATH     | _           |                | _                                      | Write Buffer   | for the upper  | 5 bits of the | Program C     | ounter       | 0 0000                   | 21, 96             |  |

| 18Bh <sup>(4)</sup>   | INTCON     | GIE         | PEIE           | TMR0IE                                 | INTE           | RBIE           | TMR0IF        | INTF          | RBIF         | 0000 000x                | 23, 96             |  |

| 18Ch                  | PMCON1     | (6)         | _              | —                                      | —              | _              | _             | —             | RD           | 10                       | 29, 97             |  |

| 18Dh                  | —          | Unimplem    | ented          |                                        | _              |                |               |               |              |                          |                    |  |

| 18Eh                  | _          | Reserved    | maintain clea  |                                        | 0000 0000      |                |               |               |              |                          |                    |  |

| 18Fh                  | _          | Reserved    | maintain clea  | ar                                     |                |                |               |               |              | 0000 0000                |                    |  |

Legend: x = unknown, u = unchanged, q = value depends on condition, - = unimplemented, read as '0', r = reserved. Shaded locations are unimplemented, read as '0'.

**Note** 1: The upper byte of the program counter is not directly accessible. PCLATH is a holding register for the PC<12:8>, whose contents are transferred to the upper byte of the program counter during branches (CALL or GOTO).

2: Other (non power-up) RESETS include external RESET through MCLR and Watchdog Timer Reset.

3: Bits PSPIE and PSPIF are reserved on the 28-pin devices; always maintain these bits clear.

4: These registers can be addressed from any bank.

5: PORTD, PORTE, TRISD, and TRISE are not physically implemented on the 28-pin devices, read as '0'.

6: This bit always reads as a '1'.

#### 2.2.2.2 OPTION\_REG Register

The OPTION\_REG register is a readable and writable register, which contains various control bits to configure the TMR0 prescaler/WDT postscaler (single assignable register known also as the prescaler), the External INT Interrupt, TMR0 and the weak pull-ups on PORTB.

Note: To achieve a 1:1 prescaler assignment for the TMR0 register, assign the prescaler to the Watchdog Timer.

## **REGISTER 2-2: OPTION\_REG REGISTER (ADDRESS 81h, 181h)**

|                 | R/W-1       | R/W-1                                                                                                         | R/W-1       | R/W-1            | R/W-1          | R/W-1     | R/W-1        | R/W-1   |  |  |  |  |  |  |

|-----------------|-------------|---------------------------------------------------------------------------------------------------------------|-------------|------------------|----------------|-----------|--------------|---------|--|--|--|--|--|--|

|                 | RBPU        | INTEDG                                                                                                        | TOCS        | T0SE             | PSA            | PS2       | PS1          | PS0     |  |  |  |  |  |  |

|                 | bit 7       |                                                                                                               |             |                  |                |           |              | bit 0   |  |  |  |  |  |  |

|                 |             |                                                                                                               |             |                  |                |           |              |         |  |  |  |  |  |  |

| bit 7           |             | DRTB Pull-up I                                                                                                |             |                  |                |           |              |         |  |  |  |  |  |  |

|                 |             | B pull-ups are                                                                                                |             | مرامينا ماريما م |                |           |              |         |  |  |  |  |  |  |

| <b>h</b> it C   |             | B pull-ups are                                                                                                | •           | individual p     | ort latch valu | les       |              |         |  |  |  |  |  |  |

| bit 6           |             | INTEDG: Interrupt Edge Select bit<br>1 = Interrupt on rising edge of RB0/INT pin                              |             |                  |                |           |              |         |  |  |  |  |  |  |

|                 |             | <ul> <li>Interrupt on rising edge of RB0/INT pin</li> <li>Interrupt on falling edge of RB0/INT pin</li> </ul> |             |                  |                |           |              |         |  |  |  |  |  |  |

| bit 5           | TOCS: TM    | TOCS: TMR0 Clock Source Select bit                                                                            |             |                  |                |           |              |         |  |  |  |  |  |  |

|                 |             |                                                                                                               |             |                  |                |           |              |         |  |  |  |  |  |  |

|                 |             | <ul> <li>= Transition on RA4/T0CKI pin</li> <li>= Internal instruction cycle clock (CLKOUT)</li> </ul>        |             |                  |                |           |              |         |  |  |  |  |  |  |

| bit 4           |             | R0 Source Ed                                                                                                  | •           |                  |                |           |              |         |  |  |  |  |  |  |

|                 |             | nent on high-to<br>nent on low-to-                                                                            |             |                  | •              |           |              |         |  |  |  |  |  |  |

| bit 3           |             | scaler Assignm                                                                                                | -           |                  |                |           |              |         |  |  |  |  |  |  |

|                 | 1 = Presca  | aler is assigne                                                                                               | d to the WE |                  |                |           |              |         |  |  |  |  |  |  |

| <b>h</b> it 0 0 |             | aler is assigne                                                                                               |             |                  |                |           |              |         |  |  |  |  |  |  |

| bit 2-0         |             | Prescaler Rat                                                                                                 |             | -                |                |           |              |         |  |  |  |  |  |  |

|                 | Bit V       | alue TMR0 I                                                                                                   | Rate WDT    | Rate             |                |           |              |         |  |  |  |  |  |  |

|                 | 00          | 1.4                                                                                                           | 1:1         |                  |                |           |              |         |  |  |  |  |  |  |

|                 | 00<br>01    |                                                                                                               | 1:2         |                  |                |           |              |         |  |  |  |  |  |  |

|                 | 01          | 1.0                                                                                                           |             |                  |                |           |              |         |  |  |  |  |  |  |

|                 | 10          | 1.0                                                                                                           |             |                  |                |           |              |         |  |  |  |  |  |  |

|                 | 10<br>11    | 1.0                                                                                                           |             |                  |                |           |              |         |  |  |  |  |  |  |

|                 | 11          | 1.14                                                                                                          |             |                  |                |           |              |         |  |  |  |  |  |  |

|                 |             |                                                                                                               |             |                  |                |           |              |         |  |  |  |  |  |  |

|                 | Legend:     |                                                                                                               |             |                  |                |           |              |         |  |  |  |  |  |  |

|                 | R = Reada   | able bit                                                                                                      | W = W       | ritable bit      | U = Unimp      | olemented | bit, read as | '0'     |  |  |  |  |  |  |

|                 | - n = Value | e at POR rese                                                                                                 | t '1' = Bi  | t is set         | '0' = Bit is   | cleared   | x = Bit is ι | unknown |  |  |  |  |  |  |

|                 | L           |                                                                                                               |             |                  |                |           |              |         |  |  |  |  |  |  |

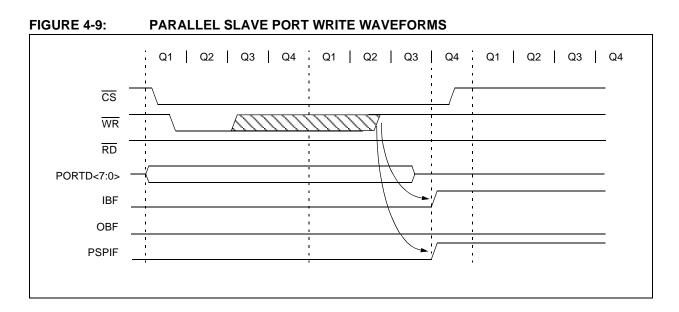

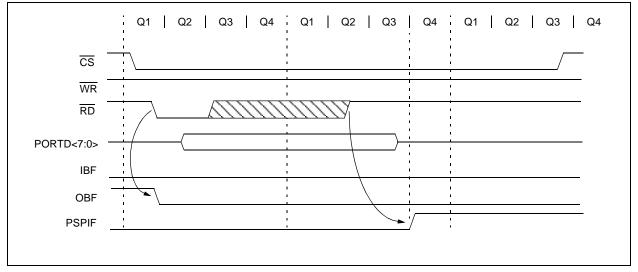

#### FIGURE 4-10: PARALLEL SLAVE PORT READ WAVEFORMS

#### TABLE 4-11: REGISTERS ASSOCIATED WITH PARALLEL SLAVE PORT

| Address | Name   | Bit 7                | Bit 6   | Bit 5      | Bit 4         | Bit 3    | Bit 2   | Bit 1       | Bit 0    | Value on:<br>POR,<br>BOR | Value on<br>all other<br>RESETS |

|---------|--------|----------------------|---------|------------|---------------|----------|---------|-------------|----------|--------------------------|---------------------------------|

| 08h     | PORTD  | Port data I          | atch wh | nen writte | en: Port pins | when rea | d       |             |          | xxxx xxxx                | uuuu uuuu                       |

| 09h     | PORTE  | —                    |         | —          |               | —        | RE2     | RE1         | RE0      | xxx                      | uuu                             |

| 89h     | TRISE  | IBF                  | OBF     | IBOV       | PSPMODE       | _        | PORTE D | Data Direct | ion Bits | 0000 -111                | 0000 -111                       |

| 0Ch     | PIR1   | PSPIF <sup>(1)</sup> | ADIF    | RCIF       | TXIF          | SSPIF    | CCP1IF  | TMR2IF      | TMR1IF   | 0000 0000                | 0000 0000                       |

| 8Ch     | PIE1   | PSPIE <sup>(1)</sup> | ADIE    | RCIE       | TXIE          | SSPIE    | CCP1IE  | TMR2IE      | TMR1IE   | 0000 0000                | 0000 0000                       |

| 9Fh     | ADCON1 | _                    | _       | _          | _             | _        | PCFG2   | PCFG1       | PCFG0    | 000                      | 000                             |

Legend: x = unknown, u = unchanged, - = unimplemented, read as '0'. Shaded cells are not used by the Parallel Slave Port.

**Note 1:** Bits PSPIE and PSPIF are reserved on the PIC16F73/76; always maintain these bits clear.

## 6.4 Timer1 Operation in Asynchronous Counter Mode

If control bit T1SYNC (T1CON<2>) is set, the external clock input is not synchronized. The timer continues to increment asynchronous to the internal phase clocks. The timer will continue to run during SLEEP and can generate an interrupt on overflow, which will wake-up the processor. However, special precautions in software are needed to read/write the timer (Section 6.4.1).

In Asynchronous Counter mode, Timer1 cannot be used as a time-base for capture or compare operations.

### 6.4.1 READING AND WRITING TIMER1 IN ASYNCHRONOUS COUNTER MODE

Reading TMR1H or TMR1L, while the timer is running from an external asynchronous clock, will ensure a valid read (taken care of in hardware). However, the user should keep in mind that reading the 16-bit timer in two 8-bit values itself, poses certain problems, since the timer may overflow between the reads.

For writes, it is recommended that the user simply stop the timer and write the desired values. A write contention may occur by writing to the timer registers, while the register is incrementing. This may produce an unpredictable value in the timer register.

Reading the 16-bit value requires some care. The example code provided in Example 6-1 and Example 6-2 demonstrates how to write to and read Timer1 while it is running in Asynchronous mode.

#### EXAMPLE 6-1: WRITING A 16-BIT FREE-RUNNING TIMER

| ; All  | interrupts | are disabled                                     |  |

|--------|------------|--------------------------------------------------|--|

| CLRF   | TMR1L      | ; Clear Low byte, Ensures no rollover into TMR1H |  |

| MOVLW  | HI_BYTE    | ; Value to load into TMR1H                       |  |

| MOVWF  | TMR1H, F   | ; Write High byte                                |  |

| MOVLW  | LO_BYTE    | ; Value to load into TMR1L                       |  |

| MOVWF  | TMR1H, F   | ; Write Low byte                                 |  |

| ; Re-0 | enable the | Interrupt (if required)                          |  |

| CONTI  | NUE        | ; Continue with your code                        |  |

| 1      |            |                                                  |  |

#### EXAMPLE 6-2: READING A 16-BIT FREE-RUNNING TIMER

| ; All  | interrupts an | ce | disabled                                             |

|--------|---------------|----|------------------------------------------------------|

| MOVF   | TMR1H, W      | ;  | Read high byte                                       |

| MOVWF  | TMPH          |    |                                                      |

| MOVF   | TMR1L, W      | ;  | Read low byte                                        |

| MOVWF  | TMPL          |    |                                                      |

| MOVF   | TMR1H, W      | ;  | Read high byte                                       |

| SUBWF  | TMPH, W       | ;  | Sub 1st read with 2nd read                           |

| BTFSC  | STATUS,Z      | ;  | Is result = 0                                        |

| GOTO   | CONTINUE      | ;  | Good 16-bit read                                     |

| ; TMR1 | L may have ro | 51 | led over between the read of the high and low bytes. |

| ; Read | ing the high  | a  | nd low bytes now will read a good value.             |

| MOVF   | TMR1H, W      | ;  | Read high byte                                       |

| MOVWF  | TMPH          |    |                                                      |

| MOVF   | TMR1L, W      | ;  | Read low byte                                        |

| MOVWF  | TMPL          | ;  | Re-enable the Interrupt (if required)                |

| CONTIN | UE            | ;  | Continue with your code                              |

|        |               |    | -                                                    |

| REGISTER 7-1: | T2CON:          | TIMER2 C                     |             | EGISTER (     | ADDRESS       | 12h)        |                |          |

|---------------|-----------------|------------------------------|-------------|---------------|---------------|-------------|----------------|----------|

|               | U-0             | R/W-0                        | R/W-0       | R/W-0         | R/W-0         | R/W-0       | R/W-0          | R/W-0    |

|               | _               | TOUTPS3                      | TOUTPS2     | TOUTPS1       | TOUTPS0       | TMR2ON      | T2CKPS1        | T2CKPS0  |

|               | bit 7           |                              |             |               |               |             |                | bit 0    |

| bit 7         | Unimplo         | mented: Rea                  | nd as '0'   |               |               |             |                |          |

|               | -               |                              |             |               | 0.1           |             |                |          |

| bit 6-3       |                 |                              | Timer2 Out  | put Postscale | e Select Dits |             |                |          |

|               |                 | :1 Postscale<br>:2 Postscale |             |               |               |             |                |          |

|               |                 | :3 Postscale                 |             |               |               |             |                |          |

|               | •               | .01000000                    |             |               |               |             |                |          |

|               | •               |                              |             |               |               |             |                |          |

|               | •               |                              |             |               |               |             |                |          |

|               | 1111 <b>= 1</b> | :16 Postscale                | Э           |               |               |             |                |          |

| bit 2         | TMR2ON          | I: Timer2 On                 | bit         |               |               |             |                |          |

|               | 1 = Timei       |                              |             |               |               |             |                |          |

|               | 0 = Timei       |                              |             |               |               |             |                |          |

| bit 1-0       | T2CKPS          | 1:T2CKPS0:                   | Timer2 Cloc | k Prescale S  | elect bits    |             |                |          |

|               |                 | scaler is 1                  |             |               |               |             |                |          |

|               |                 | scaler is 4                  |             |               |               |             |                |          |

|               | 1x = Pres       | scaler is 16                 |             |               |               |             |                |          |

|               | Legend:         |                              |             |               |               |             |                |          |

|               | R = Reada       | ahle hit                     | M - M       | /ritable bit  | II – Unim     | olemented I | oit, read as ' | 0'       |

|               | 1. – 1.caua     |                              | vv — v      |               | 0 - 01111     | siomonicui  | 51, 1000 05    | <b>·</b> |

# TABLE 7-1: REGISTERS ASSOCIATED WITH TIMER2 AS A TIMER/COUNTER

- n = Value at POR reset

| Address                | Name   | Bit 7                | Bit 6        | Bit 5   | Bit 4   | Bit 3   | Bit 2  | Bit 1   | Bit 0   | Value<br>PC<br>BC | R,   | all othe<br>RESETS |      |

|------------------------|--------|----------------------|--------------|---------|---------|---------|--------|---------|---------|-------------------|------|--------------------|------|

| 0Bh,8Bh,<br>10Bh, 18Bh | INTCON | GIE                  | PEIE         | TMR0IE  | INTE    | RBIE    | TMR0IF | INTF    | RBIF    | 0000              | 000x | 0000               | 000u |

| 0Ch                    | PIR1   | PSPIF <sup>(1)</sup> | ADIF         | RCIF    | TXIF    | SSPIF   | CCP1IF | TMR2IF  | TMR1IF  | 0000              | 0000 | 0000               | 0000 |

| 8Ch                    | PIE1   | PSPIE <sup>(1)</sup> | ADIE         | RCIE    | TXIE    | SSPIE   | CCP1IE | TMR2IE  | TMR1IE  | 0000              | 0000 | 0000               | 0000 |

| 11h                    | TMR2   | Timer2 M             | odule Regis  | ster    |         |         |        |         |         | 0000              | 0000 | 0000               | 0000 |

| 12h                    | T2CON  |                      | TOUTPS3      | TOUTPS2 | TOUTPS1 | TOUTPS0 | TMR2ON | T2CKPS1 | T2CKPS0 | -000              | 0000 | -000               | 0000 |

| 92h                    | PR2    | Timer2 Pe            | eriod Regist | ter     |         |         |        |         |         | 1111              | 1111 | 1111               | 1111 |

'1' = Bit is set

'0' = Bit is cleared

Legend: x = unknown, u = unchanged, - = unimplemented, read as '0'. Shaded cells are not used by the Timer2 module.

Note 1: Bits PSPIE and PSPIF are reserved on the PIC16F73/76; always maintain these bits clear.

x = Bit is unknown

#### 8.5.3 SETUP FOR PWM OPERATION

The following steps should be taken when configuring the CCP module for PWM operation:

- 1. Set the PWM period by writing to the PR2 register.

- 2. Set the PWM duty cycle by writing to the CCPR1L register and CCP1CON<5:4> bits.

- 3. Make the CCP1 pin an output by clearing the TRISC<2> bit.

- 4. Set the TMR2 prescale value and enable Timer2 by writing to T2CON.

- 5. Configure the CCP1 module for PWM operation.

## TABLE 8-4: EXAMPLE PWM FREQUENCIES AND RESOLUTIONS (Fosc = 20 MHz)

| PWM Frequency             | 1.22 kHz | 4.88 kHz | 19.53 kHz | 78.12 kHz | 156.3 kHz | 208.3 kHz |

|---------------------------|----------|----------|-----------|-----------|-----------|-----------|

| Timer Prescale (1, 4, 16) | 16       | 4        | 1         | 1         | 1         | 1         |

| PR2 Value                 | 0xFF     | 0xFF     | 0xFF      | 0x3F      | 0x1F      | 0x17      |

| Maximum Resolution (bits) | 10       | 10       | 10        | 8         | 7         | 5.5       |

#### TABLE 8-5: REGISTERS ASSOCIATED WITH PWM AND TIMER2

| Address               | Name    | Bit 7                                    | Bit 6                              | Bit 5       | Bit 4     | Bit 3   | Bit 2  | Bit 1   | Bit 0   | PC   | e on:<br>DR,<br>DR | all o | e on<br>other<br>SETS |

|-----------------------|---------|------------------------------------------|------------------------------------|-------------|-----------|---------|--------|---------|---------|------|--------------------|-------|-----------------------|

| 0Bh,8Bh,<br>10Bh,18Bh | INTCON  | GIE                                      | PEIE                               | TMR0IE      | INTE      | RBIE    | TMR0IF | INTF    | RBIF    | 0000 | 000x               | 0000  | 000u                  |

| 0Ch                   | PIR1    | PSPIF <sup>(1)</sup>                     | ADIF                               | RCIF        | TXIF      | SSPIF   | CCP1IF | TMR2IF  | TMR1IF  | 0000 | 0000               | 0000  | 0000                  |

| 0Dh                   | PIR2    | _                                        | —                                  | —           |           | _       | —      |         | CCP2IF  |      | 0                  |       | 0                     |

| 8Ch                   | PIE1    | PSPIE <sup>(1)</sup>                     | ADIE                               | RCIE        | TXIE      | SSPIE   | CCP1IE | TMR2IE  | TMR1IE  | 0000 | 0000               | 0000  | 0000                  |

| 8Dh                   | PIE2    | —                                        | _                                  | _           | _         | —       | —      | _       | CCP2IE  |      | 0                  |       | 0                     |

| 87h                   | TRISC   | PORTC D                                  | Data Directi                       | on Register |           |         |        |         |         | 1111 | 1111               | 1111  | 1111                  |

| 11h                   | TMR2    | Timer2 M                                 | odule Regi                         | ster        |           |         |        |         |         | 0000 | 0000               | 0000  | 0000                  |

| 92h                   | PR2     | Timer2 M                                 | odule Peric                        | d Register  |           |         |        |         |         | 1111 | 1111               | 1111  | 1111                  |

| 12h                   | T2CON   | _                                        | TOUTPS3                            | TOUTPS2     | TOUTPS1   | TOUTPS0 | TMR2ON | T2CKPS1 | T2CKPS0 | -000 | 0000               | -000  | 0000                  |

| 15h                   | CCPR1L  | Capture/C                                | Compare/P                          | WM Registe  | er1 (LSB) |         |        |         |         | xxxx | xxxx               | uuuu  | uuuu                  |

| 16h                   | CCPR1H  | Capture/C                                | Compare/P                          | VM Registe  | er1 (MSB) |         |        |         |         | xxxx | xxxx               | uuuu  | uuuu                  |

| 17h                   | CCP1CON | — — CCP1X CCP1Y CCP1M3 CCP1M2 CCP1M1 CCP |                                    |             |           |         |        |         | CCP1M0  | 00   | 0000               | 00    | 0000                  |

| 1Bh                   | CCPR2L  | Capture/C                                | apture/Compare/PWM Register2 (LSB) |             |           |         |        |         |         |      |                    | uuuu  | uuuu                  |

| 1Ch                   | CCPR2H  | Capture/C                                | Compare/P                          | WM Registe  | er2 (MSB) |         |        |         |         | xxxx | xxxx               | uuuu  | uuuu                  |

| 1Dh                   | CCP2CON | —                                        | —                                  | CCP2X       | CCP2Y     | CCP2M3  | CCP2M2 | CCP2M1  | CCP2M0  | 00   | 0000               | 00    | 0000                  |

Legend: x = unknown, u = unchanged, - = unimplemented, read as '0'. Shaded cells are not used by PWM and Timer2.

Note 1: Bits PSPIE and PSPIF are reserved on the PIC16F73/76; always maintain these bits clear.

| ILN 10-2. | NCOTA. I                                                                           |                                                                                  |                                                |                          |              |              |             |             |  |  |

|-----------|------------------------------------------------------------------------------------|----------------------------------------------------------------------------------|------------------------------------------------|--------------------------|--------------|--------------|-------------|-------------|--|--|

|           | R/W-0                                                                              | R/W-0                                                                            | R/W-0                                          | R/W-0                    | U-0          | R-0          | R-0         | R-x         |  |  |

|           | SPEN                                                                               | RX9                                                                              | SREN                                           | CREN                     | _            | FERR         | OERR        | RX9D        |  |  |

|           | bit 7                                                                              |                                                                                  |                                                |                          |              |              |             | bit 0       |  |  |

| bit 7     | 1 = Serial                                                                         | rial Port Ena<br>port enabled<br>port disabled                                   | (configures                                    | RC7/RX/DT a              | and RC6/TX   | (/CK pins a  | s serial po | rt pins)    |  |  |

| bit 6     | 1 = Select                                                                         | Receive Ena<br>s 9-bit recep<br>s 8-bit recep                                    | tion                                           |                          |              |              |             |             |  |  |

| bit 5     | Asynchron<br>Don't care<br>Synchronc<br>1 = Enable<br>0 = Disable<br>This bit is e | ous mode - M<br>es single rece<br>es single rec<br>cleared after<br>ous mode - S | <u>faster:</u><br>eive<br>eive<br>reception is | complete.                |              |              |             |             |  |  |

| bit 4     | Asynchron<br>1 = Enable<br>0 = Disable<br>Synchronc<br>1 = Enable                  | ous mode:<br>es continuou<br>es continuou<br>ous mode:                           | is receive<br>s receive unt                    | e bit<br>il enable bit C | CREN is clea | ared (CRE    | N overrides | SREN)       |  |  |

| bit 3     | Unimplem                                                                           | ented: Rea                                                                       | d as '0'                                       |                          |              |              |             |             |  |  |

| bit 2     |                                                                                    |                                                                                  |                                                | by reading R             | CREG regis   | ster and rec | eive next v | valid byte) |  |  |

| bit 1     |                                                                                    |                                                                                  |                                                | by clearing bit          | CREN)        |              |             |             |  |  |

| bit 0     |                                                                                    | bit of Receir<br>rity bit (parity                                                |                                                | lated by firmw           | /are)        |              |             |             |  |  |

|           | Legend:                                                                            |                                                                                  |                                                |                          |              |              |             |             |  |  |

|           | R = Reada                                                                          | able bit                                                                         | W = W                                          | /ritable bit             | U = Unim     | plemented    | bit, read a | s 'O'       |  |  |

'1' = Bit is set

'0' = Bit is cleared

#### REGISTER 10-2: RCSTA: RECEIVE STATUS AND CONTROL REGISTER (ADDRESS 18h)

- n = Value at POR reset

x = Bit is unknown

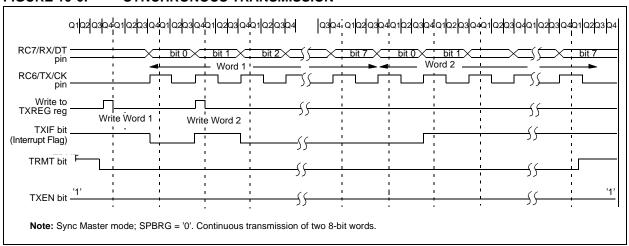

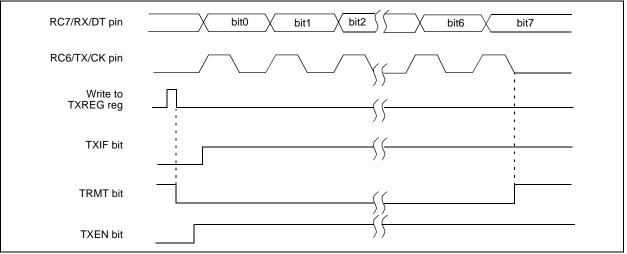

#### FIGURE 10-6: SYNCHRONOUS TRANSMISSION

#### FIGURE 10-7: SYNCHRONOUS TRANSMISSION (THROUGH TXEN)

#### TABLE 10-7: REGISTERS ASSOCIATED WITH SYNCHRONOUS MASTER TRANSMISSION

| Address                | Name   | Bit 7                | Bit 6     | Bit 5      | Bit 4 | Bit 3 | Bit 2  | Bit 1  | Bit 0     | Value on:<br>POR,<br>BOR | Value on<br>all other<br>RESETS |

|------------------------|--------|----------------------|-----------|------------|-------|-------|--------|--------|-----------|--------------------------|---------------------------------|

| 0Bh, 8Bh,<br>10Bh,18Bh | INTCON | GIE                  | PEIE      | TMR0IE     | INTE  | RBIE  | TMR0IF | INTF   | RBIF      | 0000 000x                | 0000 000u                       |

| 0Ch                    | PIR1   | PSPIF <sup>(1)</sup> | ADIF      | RCIF       | TXIF  | SSPIF | CCP1IF | TMR2IF | TMR1IF    | 0000 0000                | 0000 0000                       |

| 18h                    | RCSTA  | SPEN                 | RX9       | SREN       | CREN  | _     | FERR   | OERR   | RX9D      | 0000 -00x                | 0000 -00x                       |

| 19h                    | TXREG  | USART Tr             | ansmit Re | egister    |       |       |        |        |           | 0000 0000                | 0000 0000                       |

| 8Ch                    | PIE1   | PSPIE <sup>(1)</sup> | ADIE      | RCIE       | TXIE  | SSPIE | CCP1IE | TMR2IE | TMR1IE    | 0000 0000                | 0000 0000                       |

| 98h                    | TXSTA  | CSRC                 | TX9       | TXEN       | SYNC  | _     | BRGH   | TRMT   | TX9D      | 0000 -010                | 0000 -010                       |

| 99h                    | SPBRG  | Baud Rate            | Generat   | or Registe | r     |       |        |        | 0000 0000 | 0000 0000                |                                 |

Legend: x = unknown, - = unimplemented, read as '0'. Shaded cells are not used for synchronous master transmission.

Note 1: Bits PSPIE and PSPIF are reserved on the PIC16F73/76 devices; always maintain these bits clear.

# 11.0 ANALOG-TO-DIGITAL CONVERTER (A/D) MODULE

The 8-bit analog-to-digital (A/D) converter module has five inputs for the PIC16F73/76 and eight for the PIC16F74/77.

The A/D allows conversion of an analog input signal to a corresponding 8-bit digital number. The output of the sample and hold is the input into the converter, which generates the result via successive approximation. The analog reference voltage is software selectable to either the device's positive supply voltage (VDD), or the voltage level on the RA3/AN3/VREF pin.

The A/D converter has a unique feature of being able to operate while the device is in SLEEP mode. To operate in SLEEP, the A/D conversion clock must be derived from the A/D's internal RC oscillator. The A/D module has three registers. These registers are:

- A/D Result Register ((ADRES)

- A/D Control Register 0 (ADCON0)

- A/D Control Register 1 ((ADCON1)

The ADCON0 register, shown in Register 11-1, controls the operation of the A/D module. The ADCON1 register, shown in Register 11-2, configures the functions of the port pins. The port pins can be configured as analog inputs (RA3 can also be a voltage reference), or as digital I/O.

Additional information on using the A/D module can be found in the PICmicro<sup>™</sup> Mid-Range MCU Family Reference Manual (DS33023) and in Application Note, AN546 (DS00546).

|                                               | //200110                                                                             |                                                        |                      | <b>50</b> mm, |              |                   |             |        |  |  |  |  |  |

|-----------------------------------------------|--------------------------------------------------------------------------------------|--------------------------------------------------------|----------------------|---------------|--------------|-------------------|-------------|--------|--|--|--|--|--|

|                                               | R/W-0                                                                                | R/W-0                                                  | R/W-0                | R/W-0         | R/W-0        | R/W-0             | U-0         | R/W-0  |  |  |  |  |  |

|                                               | ADCS1                                                                                | ADCS0                                                  | CHS2                 | CHS1          | CHS0         | GO/DONE           |             | ADON   |  |  |  |  |  |

|                                               | bit 7                                                                                |                                                        |                      |               |              |                   |             | bit 0  |  |  |  |  |  |

|                                               |                                                                                      |                                                        |                      |               |              |                   |             |        |  |  |  |  |  |

| bit 7-6                                       |                                                                                      | DCS0: A/D (                                            | Conversion (         | Clock Select  | bits         |                   |             |        |  |  |  |  |  |

|                                               | 00 = Fosc                                                                            |                                                        |                      |               |              |                   |             |        |  |  |  |  |  |

|                                               | 01 = Fosc<br>10 = Fosc                                                               |                                                        |                      |               |              |                   |             |        |  |  |  |  |  |

|                                               |                                                                                      | clock derive                                           | d from the ir        | nternal Δ/D m | odula RC c   | scillator)        |             |        |  |  |  |  |  |

| bit 5 2                                       |                                                                                      | ,                                                      |                      |               |              | Semator)          |             |        |  |  |  |  |  |

| bit 5-3 CHS2:CHS0: Analog Channel Select bits |                                                                                      |                                                        |                      |               |              |                   |             |        |  |  |  |  |  |

|                                               |                                                                                      | 000 = Channel 0 (RA0/AN0)<br>001 = Channel 1 (RA1/AN1) |                      |               |              |                   |             |        |  |  |  |  |  |

|                                               |                                                                                      | annel 2 (RA2                                           | ,                    |               |              |                   |             |        |  |  |  |  |  |

|                                               |                                                                                      | annel 3 (RA3                                           | ,                    |               |              |                   |             |        |  |  |  |  |  |

|                                               |                                                                                      | annel 4 (RA5                                           |                      |               |              |                   |             |        |  |  |  |  |  |

|                                               | 101 <b>= Ch</b> a                                                                    | annel 5 (RE0                                           | (AN5) <sup>(1)</sup> |               |              |                   |             |        |  |  |  |  |  |

|                                               | 101 = Channel 6 (RE1/AN6) <sup>(1)</sup><br>111 = Channel 7 (RE2/AN7) <sup>(1)</sup> |                                                        |                      |               |              |                   |             |        |  |  |  |  |  |

|                                               |                                                                                      |                                                        | ,                    |               |              |                   |             |        |  |  |  |  |  |

| bit 2                                         |                                                                                      | : A/D Conve                                            | rsion Status         | s bit         |              |                   |             |        |  |  |  |  |  |

|                                               | $\frac{\text{If ADON}}{1} =$                                                         |                                                        |                      |               |              | <b>D</b>          |             |        |  |  |  |  |  |

|                                               |                                                                                      |                                                        |                      |               |              | D conversion)     | dware wh    | on the |  |  |  |  |  |

|                                               |                                                                                      | inversion is c                                         |                      |               | utomatically | cleared by hai    |             |        |  |  |  |  |  |

| bit 1                                         | Unimplem                                                                             | nented: Read                                           | d as '0'             |               |              |                   |             |        |  |  |  |  |  |

| bit 0                                         | ADON: A/                                                                             | D On bit                                               |                      |               |              |                   |             |        |  |  |  |  |  |

|                                               | 1 = A/D co                                                                           | nverter mod                                            | ule is opera         | ting          |              |                   |             |        |  |  |  |  |  |

|                                               | 0 = A/D cc                                                                           | onverter mod                                           | ule is shut-c        | off and consu | mes no ope   | erating current   |             |        |  |  |  |  |  |

|                                               | Note 1:                                                                              | A/D channe                                             | els 5, 6 and         | 7 are implem  | nented on th | e PIC16F74/7      | 7 only.     |        |  |  |  |  |  |

|                                               | Legend:                                                                              |                                                        |                      |               |              |                   |             |        |  |  |  |  |  |

|                                               | R = Reada                                                                            | ahle hit                                               | M - M                | Vritable bit  | –   Inir     | nplemented bit    | read as "   | O'     |  |  |  |  |  |

|                                               | IN - INEaua                                                                          |                                                        | vv = v               | VILLADIE DIL  | 0 - 0111     | ubieirierited pit | , icau as i | 5      |  |  |  |  |  |

'1' = Bit is set

'0' = Bit is cleared

# REGISTER 11-1: ADCON0 REGISTER (ADDRESS 1Fh)

- n = Value at POR reset

x = Bit is unknown

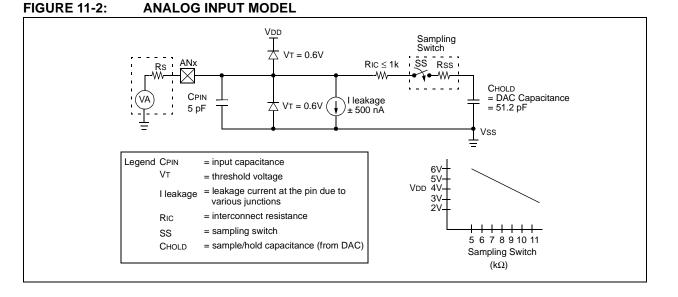

## 11.1 A/D Acquisition Requirements

For the A/D converter to meet its specified accuracy, the charge holding capacitor (CHOLD) must be allowed to fully charge to the input channel voltage level. The analog input model is shown in Figure 11-2. The source impedance (Rs) and the internal sampling switch (Rss) impedance directly affect the time required to charge the capacitor CHOLD. The sampling switch (Rss) impedance varies over the device voltage (VDD), see Figure 11-2. The source impedance affects the offset voltage at the analog input (due to pin leakage current). The maximum recommended impedance for analog sources is 10 k $\Omega$ . After the analog input channel is selected (changed), the acquisition period must pass before the conversion can be started.

To calculate the minimum acquisition time, TACQ, see the PICmicro<sup>TM</sup> Mid-Range MCU Family Reference Manual (DS33023). In general, however, given a maximum source impedance of 10 k $\Omega$  and at a temperature of 100°C, TACQ will be no more than 16 µsec.

#### TABLE 11-1: TAD vs. MAXIMUM DEVICE OPERATING FREQUENCIES (STANDARD DEVICES (C))

| AD Cloc                 | k Source (Tad) | Maximum Device Frequency |

|-------------------------|----------------|--------------------------|

| Operation               | ADCS1:ADCS0    | Max.                     |

| 2Tosc                   | 0.0            | 1.25 MHz                 |

| 8Tosc                   | 01             | 5 MHz                    |

| 32Tosc                  | 10             | 20 MHz                   |

| RC <sup>(1, 2, 3)</sup> | 11             | (Note 1)                 |

Note 1: The RC source has a typical TAD time of 4 µs but can vary between 2-6 µs.

2: When the device frequencies are greater than 1 MHz, the RC A/D conversion clock source is only recommended for SLEEP operation.

3: For extended voltage devices (LC), please refer to the Electrical Specifications section.

| U-0      | U-0 | U-0           | U-0                                         | U-0       | U-0      | U-0       | R/P-1       | U-0    | R/P-1    | R/P-1        | R/P-1 | R/P-1 | R/P-1 |  |

|----------|-----|---------------|---------------------------------------------|-----------|----------|-----------|-------------|--------|----------|--------------|-------|-------|-------|--|

| _        |     |               |                                             | _         |          |           | BOREN       | _      | CP0      | PWRTEN       | WDTEN | FOSC1 | FOSC0 |  |

| bit13    |     |               |                                             |           |          |           |             |        |          |              |       |       | bit0  |  |

|          |     |               |                                             |           |          |           |             |        |          |              |       |       |       |  |

| bit 13-7 |     | Unimp         | lemente                                     | d: Read   | as '1'   |           |             |        |          |              |       |       |       |  |

| bit 6    |     | BOREN         | : Browr                                     | out Re    | set Ena  | ble bit   |             |        |          |              |       |       |       |  |

|          |     | 1 = BO        | R enable                                    | ed        |          |           |             |        |          |              |       |       |       |  |

|          |     | 0 <b>= BO</b> | = BOR disabled                              |           |          |           |             |        |          |              |       |       |       |  |

| bit 5    |     | Unimp         | lemente                                     | d: Read   | as '1'   |           |             |        |          |              |       |       |       |  |

| bit 4    |     | <b>CP0:</b> F | 0: FLASH Program Memory Code Protection bit |           |          |           |             |        |          |              |       |       |       |  |

|          |     | 1 = Coo       | = Code protection off                       |           |          |           |             |        |          |              |       |       |       |  |

|          |     | 0 = All I     | memory                                      | location  | s code   | protecte  | d           |        |          |              |       |       |       |  |

| bit 3    |     | PWRTE         | EN: Pow                                     | er-up Ti  | mer Ena  | able bit  |             |        |          |              |       |       |       |  |

|          |     | 1 = PW        | /RT disa                                    | bled      |          |           |             |        |          |              |       |       |       |  |

|          |     | 0 = PW        | RT enab                                     | oled      |          |           |             |        |          |              |       |       |       |  |

| bit 2    |     | WDTE          | N: Watch                                    | ndog Tim  | er Enal  | ole bit   |             |        |          |              |       |       |       |  |

|          |     | 1 = WD        | T enabl                                     | ed        |          |           |             |        |          |              |       |       |       |  |

|          |     | 0 = WD        | )T disabl                                   | ed        |          |           |             |        |          |              |       |       |       |  |

| bit 1-0  |     | FOSC1         | :FOSCO                                      | : Oscilla | tor Sele | ection bi | ts          |        |          |              |       |       |       |  |

|          |     | 11 = R0       | C oscilla                                   | tor       |          |           |             |        |          |              |       |       |       |  |

|          |     |               | S oscilla                                   |           |          |           |             |        |          |              |       |       |       |  |

|          |     |               | T oscillat                                  |           |          |           |             |        |          |              |       |       |       |  |

|          |     | 00 = LF       | oscillat                                    | or        |          |           |             |        |          |              |       |       |       |  |

|          |     |               |                                             |           |          |           |             |        |          |              |       |       |       |  |

|          |     | Note          | 1. The                                      | erased    | lunnroc  | iramme    | d) value of | the co | onfigura | tion word is | 3FFFh |       |       |  |

# REGISTER 12-1: CONFIGURATION WORD (ADDRESS 2007h)<sup>(1)</sup>

Note 1: The erased (unprogrammed) value of the configuration word is 3FFFh.

| Legend:                       |                      |                                     |

|-------------------------------|----------------------|-------------------------------------|

| R = Readable bit              | P = Programmable bit | U = Unimplemented bit, read as '0'  |

| - n = Value when device is ur | nprogrammed          | u = Unchanged from programmed state |

### 12.10 Power Control/Status Register (PCON)

The Power Control/Status Register, PCON, has two bits to indicate the type of RESET that last occurred.

Bit0 is Brown-out Reset Status bit,  $\overline{\text{BOR}}$ . Bit  $\overline{\text{BOR}}$  is unknown on a Power-on Reset. It must then be set by the user and checked on subsequent RESETS to see

## TABLE 12-3: TIME-OUT IN VARIOUS SITUATIONS

if bit  $\overline{\text{BOR}}$  cleared, indicating a Brown-out Reset occurred. When the Brown-out Reset is disabled, the state of the  $\overline{\text{BOR}}$  bit is unpredictable.

Bit1 is POR (Power-on Reset Status bit). It is cleared on a Power-on Reset and unaffected otherwise. The user must set this bit following a Power-on Reset.

| Oppillator Configuration | Power             | -up       | Drown out         | Wake-up from |

|--------------------------|-------------------|-----------|-------------------|--------------|

| Oscillator Configuration | PWRTE = 0         | PWRTE = 1 | Brown-out         | SLEEP        |

| XT, HS, LP               | 72 ms + 1024 Tosc | 1024 Tosc | 72 ms + 1024 Tosc | 1024 Tosc    |

| RC                       | 72 ms             |           | 72 ms             | —            |

#### TABLE 12-4: STATUS BITS AND THEIR SIGNIFICANCE

| POR<br>(PCON<1>) | BOR<br>(PCON<0>) | TO<br>(STATUS<4>) | PD<br>(STATUS<3>) | Significance                                            |

|------------------|------------------|-------------------|-------------------|---------------------------------------------------------|

| 0                | х                | 1                 | 1                 | Power-on Reset                                          |

| 0                | x                | 0                 | x                 | Illegal, TO is set on POR                               |

| 0                | x                | x                 | 0                 | Illegal, PD is set on POR                               |

| 1                | 0                | 1                 | 1                 | Brown-out Reset                                         |

| 1                | 1                | 0                 | 1                 | WDT Reset                                               |

| 1                | 1                | 0                 | 0                 | WDT Wake-up                                             |

| 1                | 1                | u                 | u                 | MCLR Reset during normal operation                      |

| 1                | 1                | 1                 | 0                 | MCLR Reset during SLEEP or interrupt wake-up from SLEEP |

#### TABLE 12-5: RESET CONDITION FOR SPECIAL REGISTERS

| Condition                          | Program<br>Counter    | STATUS<br>Register | PCON<br>Register |

|------------------------------------|-----------------------|--------------------|------------------|

| Power-on Reset                     | 000h                  | 0001 1xxx          | 0x               |

| MCLR Reset during normal operation | 000h                  | 000u uuuu          | uu               |

| MCLR Reset during SLEEP            | 000h                  | 0001 0uuu          | uu               |

| WDT Reset                          | 000h                  | 0000 luuu          | uu               |

| WDT Wake-up                        | PC + 1                | uuu0 0uuu          | uu               |

| Brown-out Reset                    | 000h                  | 0001 luuu          | u0               |

| Interrupt wake-up from SLEEP       | PC + 1 <sup>(1)</sup> | uuul Ouuu          | uu               |

Legend: u = unchanged, x = unknown, - = unimplemented bit, read as '0'

**Note 1:** When the wake-up is due to an interrupt and the GIE bit is set, the PC is loaded with the interrupt vector (0004h).

#### TABLE 13-2: PIC16F7X INSTRUCTION SET

| Mnemo     | onic,   | Description                                        | Cycles         |        | 14-Bit    | Opcode   | •         | Status       | Notes   |

|-----------|---------|----------------------------------------------------|----------------|--------|-----------|----------|-----------|--------------|---------|

| Opera     | nds     | Description                                        | Cycles         | MSb    |           |          | LSb       | Affected     | Notes   |