Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                                           |

|----------------------------|---------------------------------------------------------------------------|

| Product Status             | Active                                                                    |

| Core Processor             | PIC                                                                       |

| Core Size                  | 8-Bit                                                                     |

| Speed                      | 20MHz                                                                     |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                                         |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                     |

| Number of I/O              | 33                                                                        |

| Program Memory Size        | 14KB (8K x 14)                                                            |

| Program Memory Type        | FLASH                                                                     |

| EEPROM Size                | -                                                                         |

| RAM Size                   | 368 x 8                                                                   |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 5.5V                                                                 |

| Data Converters            | A/D 8x8b                                                                  |

| Oscillator Type            | External                                                                  |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                         |

| Mounting Type              | Surface Mount                                                             |

| Package / Case             | 44-TQFP                                                                   |

| Supplier Device Package    | 44-TQFP (10x10)                                                           |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16lf77t-i-pt |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

TABLE 1-3: PIC16F74 AND PIC16F77 PINOUT DESCRIPTION (CONTINUED)

| Pin Name          | DIP<br>Pin# | PLCC<br>Pin# | QFP<br>Pin# | I/O/P<br>Type | Buffer<br>Type        | Description                                                                                                          |

|-------------------|-------------|--------------|-------------|---------------|-----------------------|----------------------------------------------------------------------------------------------------------------------|

|                   |             |              |             |               |                       | PORTB is a bi-directional I/O port. PORTB can be software programmed for internal weak pull-up on all inputs.        |

| RB0/INT           | 33          | 36           | 8           |               | TTL/ST <sup>(1)</sup> |                                                                                                                      |

| RB0<br>INT        |             |              |             | I/O<br>I      |                       | Digital I/O. External interrupt.                                                                                     |

| RB1               | 34          | 37           | 9           | I/O           | TTL                   | Digital I/O.                                                                                                         |

| RB2               | 35          | 38           | 10          | I/O           | TTL                   | Digital I/O.                                                                                                         |

| RB3/PGM           | 36          | 39           | 11          |               | TTL                   |                                                                                                                      |

| RB3               |             |              |             | I/O           |                       | Digital I/O.                                                                                                         |

| PGM               |             |              |             | I/O           |                       | Low voltage ICSP programming enable pin.                                                                             |

| RB4               | 37          | 41           | 14          | I/O           | TTL                   | Digital I/O.                                                                                                         |

| RB5               | 38          | 42           | 15          | I/O           | TTL                   | Digital I/O.                                                                                                         |

| RB6/PGC           | 39          | 43           | 16          |               | TTL/ST <sup>(2)</sup> |                                                                                                                      |

| RB6               |             |              |             | I/O           |                       | Digital I/O.                                                                                                         |

| PGC               |             |              |             | I/O           | 4-1                   | In-Circuit Debugger and ICSP programming clock.                                                                      |

| RB7/PGD           | 40          | 44           | 17          |               | TTL/ST <sup>(2)</sup> |                                                                                                                      |

| RB7               |             |              |             | I/O           |                       | Digital I/O.                                                                                                         |

| PGD               |             |              |             | I/O           |                       | In-Circuit Debugger and ICSP programming data.                                                                       |

|                   |             |              |             |               |                       | PORTC is a bi-directional I/O port.                                                                                  |

| RC0/T1OSO/T1CKI   | 15          | 16           | 32          |               | ST                    | 5: :: 11/0                                                                                                           |

| RC0<br>T1OSO      |             |              |             | I/O<br>O      |                       | Digital I/O.                                                                                                         |

| T1CKI             |             |              |             | ı             |                       | Timer1 oscillator output. Timer1 external clock input.                                                               |

| RC1/T1OSI/CCP2    | 16          | 18           | 35          | '             | ST                    | Time i external desix input.                                                                                         |

| RC1               | 10          | '0           | 33          | I/O           | 01                    | Digital I/O.                                                                                                         |

| T1OSI             |             |              |             | I             |                       | Timer1 oscillator input.                                                                                             |

| CCP2              |             |              |             | I/O           |                       | Capture2 input, Compare2 output, PWM2 output.                                                                        |

| RC2/CCP1          | 17          | 19           | 36          |               | ST                    |                                                                                                                      |

| RC2               |             |              |             | I/O           |                       | Digital I/O.                                                                                                         |

| CCP1              |             |              |             | I/O           |                       | Capture1 input/Compare1 output/PWM1 output                                                                           |

| RC3/SCK/SCL       | 18          | 20           | 37          |               | ST                    | 51.1.110                                                                                                             |

| RC3<br>SCK        |             |              |             | I/O<br>I/O    |                       | Digital I/O                                                                                                          |

| SCL               |             |              |             | 1/0           |                       | Synchronous serial clock input/output for SPI mode. Synchronous serial clock input/output for I <sup>2</sup> C mode. |

| RC4/SDI/SDA       | 23          | 25           | 42          | 1/0           | ST                    | Cyricinolous schai clock inputoutput for 1 o mode.                                                                   |

| RC4               | 23          | 23           | 42          | I/O           | 31                    | Digital I/O.                                                                                                         |

| SDI               |             |              |             | ı, ü          |                       | SPI data in.                                                                                                         |

| SDA               |             |              |             | I/O           |                       | I <sup>2</sup> C data I/O.                                                                                           |

| RC5/SDO           | 24          | 26           | 43          |               | ST                    |                                                                                                                      |

| RC5               |             |              |             | I/O           |                       | Digital I/O.                                                                                                         |

| SDO               |             |              |             | 0             |                       | SPI data out.                                                                                                        |

| RC6/TX/CK         | 25          | 27           | 44          |               | ST                    |                                                                                                                      |

| RC6               |             |              |             | I/O           |                       | Digital I/O.                                                                                                         |

| TX<br>CK          |             |              |             | O<br>I/O      |                       | USART asynchronous transmit.                                                                                         |

|                   | 20          | 20           |             | 1/0           | C.T.                  | USART 1 synchronous clock.                                                                                           |

| RC7/RX/DT<br>RC7  | 26          | 29           | 1           | I/O           | ST                    | Digital I/O.                                                                                                         |

| RX<br>RX          |             |              |             | 1,0           |                       | USART asynchronous receive.                                                                                          |

| DT                |             |              |             | I/O           |                       | USART synchronous data.                                                                                              |

| Legend: L = input |             | 0 - 0        | L           |               | ) – innut/outni       | 1                                                                                                                    |

Legend: I = input O

O = output TTL = TTL input I/O = input/output

P = power

ST = Schmitt Trigger input

Note 1: This buffer is a Schmitt Trigger input when configured as an external interrupt.

<sup>2:</sup> This buffer is a Schmitt Trigger input when used in Serial Programming mode.

<sup>3:</sup> This buffer is a Schmitt Trigger input when configured as general purpose I/O and a TTL input when used in the Parallel Slave Port mode (for interfacing to a microprocessor bus).

<sup>4:</sup> This buffer is a Schmitt Trigger input when configured in RC Oscillator mode and a CMOS input otherwise.

#### 2.2.2 SPECIAL FUNCTION REGISTERS

The Special Function Registers are registers used by the CPU and peripheral modules for controlling the desired operation of the device. These registers are implemented as static RAM. A list of these registers is given in Table 2-1. The Special Function Registers can be classified into two sets: core (CPU) and peripheral. Those registers associated with the core functions are described in detail in this section. Those related to the operation of the peripheral features are described in detail in the peripheral feature section.

TABLE 2-1: SPECIAL FUNCTION REGISTER SUMMARY

| Address              | Name    | Bit 7                | Bit 6                                  | Bit 5         | Bit 4           | Bit 3         | Bit 2         | Bit 1         | Bit 0        | Value on:<br>POR,<br>BOR | Details<br>on page |

|----------------------|---------|----------------------|----------------------------------------|---------------|-----------------|---------------|---------------|---------------|--------------|--------------------------|--------------------|

| Bank 0               |         |                      |                                        |               |                 |               |               |               |              |                          |                    |

| 00h <sup>(4)</sup>   | INDF    | Addressin            | g this locatio                         | n uses conte  | nts of FSR to   | address data  | a memory (r   | not a physica | al register) | 0000 0000                | 27, 96             |

| 01h                  | TMR0    | Timer0 Mo            | 0 Module Register                      |               |                 |               |               |               |              | xxxx xxxx                | 45, 96             |

| 02h <sup>(4)</sup>   | PCL     | Program C            | am Counter (PC) Least Significant Byte |               |                 |               |               |               |              | 0000 0000                | 26, 96             |

| 03h <sup>(4)</sup>   | STATUS  | IRP                  | RP1                                    | RP0           | TO              | PD            | Z             | DC            | С            | 0001 1xxx                | 19, 96             |

| 04h <sup>(4)</sup>   | FSR     | Indirect Da          | ata Memory /                           | Address Poir  | nter            | •             |               |               | •            | xxxx xxxx                | 27, 96             |

| 05h                  | PORTA   | _                    | _                                      | PORTA Dat     | a Latch when    | written: POF  | RTA pins wh   | en read       |              | 0x 0000                  | 32, 96             |

| 06h                  | PORTB   | PORTB D              | ata Latch wh                           | en written: P | ORTB pins w     | hen read      | •             |               |              | xxxx xxxx                | 34, 96             |

| 07h                  | PORTC   | PORTC D              | ata Latch wh                           | en written: P | ORTC pins w     | hen read      |               |               |              | xxxx xxxx                | 35, 96             |

| 08h <sup>(5)</sup>   | PORTD   | PORTD D              | ata Latch wh                           | en written: P | ORTD pins w     | hen read      |               |               |              | xxxx xxxx                | 36, 96             |

| 09h <sup>(5)</sup>   | PORTE   | _                    | _                                      | _             | _               | _             | RE2           | RE1           | RE0          | xxx                      | 39, 96             |

| 0Ah <sup>(1,4)</sup> | PCLATH  | _                    | _                                      | _             | Write Buffer    | for the upper | 5 bits of the | Program C     | ounter       | 0 0000                   | 26, 96             |

| 0Bh <sup>(4)</sup>   | INTCON  | GIE                  | PEIE                                   | TMR0IE        | INTE            | RBIE          | TMR0IF        | INTF          | RBIF         | 0000 000x                | 21, 96             |

| 0Ch                  | PIR1    | PSPIF <sup>(3)</sup> | ADIF                                   | RCIF          | TXIF            | SSPIF         | CCP1IF        | TMR2IF        | TMR1IF       | 0000 0000                | 23, 96             |

| 0Dh                  | PIR2    | _                    | _                                      | _             | _               | _             | _             | _             | CCP2IF       | 0                        | 24, 96             |

| 0Eh                  | TMR1L   | Holding Re           | egister for th                         | e Least Sign  | ificant Byte of | the 16-bit TN | /IR1 Registe  | er            |              | xxxx xxxx                | 50, 96             |

| 0Fh                  | TMR1H   | Holding Re           | egister for th                         | e Most Signi  | ficant Byte of  | the 16-bit TM | IR1 Registe   | r             |              | xxxx xxxx                | 50, 96             |

| 10h                  | T1CON   |                      | -                                      | T1CKPS1       | T1CKPS0         | T10SCEN       | T1SYNC        | TMR1CS        | TMR10N       | 00 0000                  | 47, 96             |

| 11h                  | TMR2    | Timer2 Mo            | dule Registe                           | er            |                 |               | •             |               | •            | 0000 0000                | 52, 96             |

| 12h                  | T2CON   | _                    | TOUTPS3                                | TOUTPS2       | TOUTPS          | TOUTPS0       | TMR2ON        | T2CKPS1       | T2CKPS0      | -000 0000                | 52, 96             |

| 13h                  | SSPBUF  | Synchrono            | ous Serial Po                          | rt Receive B  | uffer/Transmi   | t Register    |               |               |              | xxxx xxxx                | 64, 68, 96         |

| 14h                  | SSPCON  | WCOL                 | SSPOV                                  | SSPEN         | CKP             | SSPM3         | SSPM2         | SSPM1         | SSPM0        | 0000 0000                | 61, 96             |

| 15h                  | CCPR1L  | Capture/C            | ompare/PWI                             | M Register1   | (LSB)           |               |               |               |              | xxxx xxxx                | 56, 96             |

| 16h                  | CCPR1H  | Capture/C            | ompare/PWI                             | M Register1   | (MSB)           |               |               |               |              | xxxx xxxx                | 56, 96             |

| 17h                  | CCP1CON | _                    | _                                      | CCP1X         | CCP1Y           | CCP1M3        | CCP1M2        | CCP1M1        | CCP1M0       | 00 0000                  | 54, 96             |

| 18h                  | RCSTA   | SPEN                 | RX9                                    | SREN          | CREN            | _             | FERR          | OERR          | RX9D         | 0000 -00x                | 70, 96             |

| 19h                  | TXREG   | USART Tr             | ansmit Data                            | Register      |                 |               |               |               |              | 0000 0000                | 74, 96             |

| 1Ah                  | RCREG   | USART R              | eceive Data                            | Register      |                 |               |               |               |              | 0000 0000                | 76, 96             |

| 1Bh                  | CCPR2L  | Capture/C            | ompare/PWI                             | M Register2   | (LSB)           |               |               |               |              | xxxx xxxx                | 58, 96             |

| 1Ch                  | CCPR2H  | Capture/C            | ompare/PWI                             | M Register2   | (MSB)           | <b>.</b>      |               |               | <u> </u>     | xxxx xxxx                | 58, 96             |

| 1Dh                  | CCP2CON | _                    | _                                      | CCP2X         | CCP2Y           | CCP2M3        | CCP2M2        | CCP2M1        | CCP2M0       | 00 0000                  | 54, 96             |

| 1Eh                  | ADRES   | A/D Resul            | t Register By                          | rte           | T               | T             | ı             |               | 1            | xxxx xxxx                | 88, 96             |

| 1Fh                  | ADCON0  | ADCS1                | ADCS0                                  | CHS2          | CHS1            | CHS0          | GO/<br>DONE   | _             | ADON         | 0000 00-0                | 83, 96             |

Legend: x = unknown, u = unchanged, q = value depends on condition, -= unimplemented, read as '0', r = reserved. Shaded locations are unimplemented, read as '0'.

Note 1: The upper byte of the program counter is not directly accessible. PCLATH is a holding register for the PC<12:8>, whose contents are transferred to the upper byte of the program counter during branches (CALL or GOTO).

- 2: Other (non power-up) RESETS include external RESET through MCLR and Watchdog Timer Reset.

- 3: Bits PSPIE and PSPIF are reserved on the 28-pin devices; always maintain these bits clear.

- 4: These registers can be addressed from any bank.

- 5: PORTD, PORTE, TRISD, and TRISE are not physically implemented on the 28-pin devices, read as '0'.

- 6: This bit always reads as a '1'.

#### 2.2.2.2 OPTION\_REG Register

The OPTION\_REG register is a readable and writable register, which contains various control bits to configure the TMR0 prescaler/WDT postscaler (single assignable register known also as the prescaler), the External INT Interrupt, TMR0 and the weak pull-ups on PORTB.

Note: To achieve a 1:1 prescaler assignment for the TMR0 register, assign the prescaler to the Watchdog Timer.

### REGISTER 2-2: OPTION\_REG REGISTER (ADDRESS 81h, 181h)

| R/W-1 | R/W-1  | R/W-1 | R/W-1 | R/W-1 | R/W-1 | R/W-1 | R/W-1 |

|-------|--------|-------|-------|-------|-------|-------|-------|

| RBPU  | INTEDG | T0CS  | T0SE  | PSA   | PS2   | PS1   | PS0   |

| bit 7 |        |       |       |       |       |       | hit 0 |

bit 7 RBPU: PORTB Pull-up Enable bit

1 = PORTB pull-ups are disabled

0 = PORTB pull-ups are enabled by individual port latch values

bit 6 INTEDG: Interrupt Edge Select bit

1 = Interrupt on rising edge of RB0/INT pin0 = Interrupt on falling edge of RB0/INT pin

bit 5 TOCS: TMR0 Clock Source Select bit

1 = Transition on RA4/T0CKI pin

0 = Internal instruction cycle clock (CLKOUT)

bit 4 T0SE: TMR0 Source Edge Select bit

1 = Increment on high-to-low transition on RA4/T0CKI pin

0 = Increment on low-to-high transition on RA4/T0CKI pin

bit 3 **PSA**: Prescaler Assignment bit

1 = Prescaler is assigned to the WDT

0 = Prescaler is assigned to the Timer0 module

bit 2-0 **PS2:PS0**: Prescaler Rate Select bits

| Bit Value | TMR0 Rate | WDT Rate |

|-----------|-----------|----------|

| 000       | 1:2       | 1:1      |

| 001       | 1:4       | 1:2      |

| 010       | 1:8       | 1:4      |

| 011       | 1:16      | 1:8      |

| 100       | 1:32      | 1:16     |

| 101       | 1:64      | 1:32     |

| 110       | 1:128     | 1:64     |

| 111       | 1:256     | 1:128    |

| egend: |  |

|--------|--|

|--------|--|

$R = Readable \ bit \qquad \qquad W = Writable \ bit \qquad \qquad U = Unimplemented \ bit, read \ as '0'$

- n = Value at POR reset '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

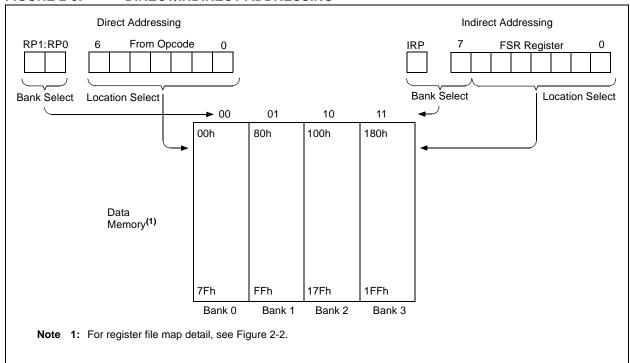

## 2.5 Indirect Addressing, INDF and FSR Registers

The INDF register is not a physical register. Addressing the INDF register will cause indirect addressing.

Indirect addressing is possible by using the INDF register. Any instruction using the INDF register actually accesses the register pointed to by the File Select Register, FSR. Reading the INDF register itself indirectly (FSR = '0') will read 00h. Writing to the INDF register indirectly results in a no operation (although status bits may be affected). An effective 9-bit address is obtained by concatenating the 8-bit FSR register and the IRP bit (STATUS<7>), as shown in Figure 2-5.

A simple program to clear RAM locations 20h-2Fh using indirect addressing is shown in Example 2-2.

#### **EXAMPLE 2-2: INDIRECT ADDRESSING**

|        | MOVLW | 0x20  | ;initialize pointer  |

|--------|-------|-------|----------------------|

|        | MOVWF | FSR   | ;to RAM              |

| NEXT   | CLRF  | INDF  | clear INDF register; |

|        | INCF  | FSR,F | ;inc pointer         |

|        | BTFSS | FSR,4 | ;all done?           |

|        | GOTO  | NEXT  | ;no clear next       |

| CONTIN | UE    |       |                      |

| :      |       |       | ;yes continue        |

|        |       |       |                      |

## FIGURE 2-5: DIRECT/INDIRECT ADDRESSING

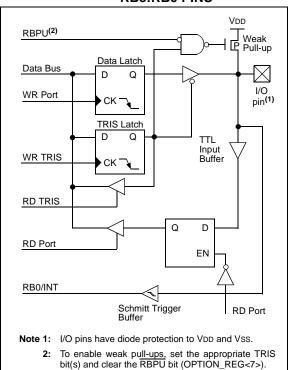

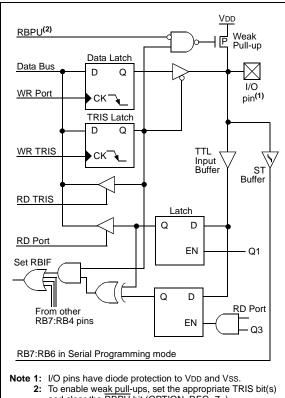

#### 4.2 **PORTB** and the TRISB Register

PORTB is an 8-bit wide, bi-directional port. The corresponding data direction register is TRISB. Setting a TRISB bit (= '1') will make the corresponding PORTB pin an input (i.e., put the corresponding output driver in a Hi-Impedance mode). Clearing a TRISB bit (= '0') will make the corresponding PORTB pin an output (i.e., put the contents of the output latch on the selected pin).

Each of the PORTB pins has a weak internal pull-up. A single control bit can turn on all the pull-ups. This is performed by clearing bit RBPU (OPTION\_REG<7>). The weak pull-up is automatically turned off when the port pin is configured as an output. The pull-ups are disabled on a Power-on Reset.

**BLOCK DIAGRAM OF** FIGURE 4-3: RB3:RB0 PINS

Four of the PORTB pins (RB7:RB4) have an interrupt-on-change feature. Only pins configured as inputs can cause this interrupt to occur (i.e., any RB7:RB4 pin configured as an output is excluded from the interrupt-on-change comparison). The input pins (of RB7:RB4) are compared with the old value latched on the last read of PORTB. The "mismatch" outputs of RB7:RB4 are ORed together to generate the RB Port Change Interrupt with flag bit RBIF (INTCON<0>).

This interrupt can wake the device from SLEEP. The user, in the Interrupt Service Routine, can clear the interrupt in the following manner:

- Any read or write of PORTB. This will end the mismatch condition.

- Clear flag bit RBIF.

A mismatch condition will continue to set flag bit RBIF. Reading PORTB will end the mismatch condition and allow flag bit RBIF to be cleared.

The interrupt-on-change feature is recommended for wake-up on key depression operation and operations where PORTB is only used for the interrupt-on-change feature. Polling of PORTB is not recommended while using the interrupt-on-change feature.

This interrupt on mismatch feature, together with software configureable pull-ups on these four pins, allow easy interface to a keypad and make it possible for wake-up on key depression. Refer to the Embedded Control Handbook, "Implementing Wake-up on Key Stroke" (AN552).

RB0/INT is an external interrupt input pin and is configured using the INTEDG bit (OPTION\_REG<6>).

RB0/INT is discussed in detail in Section 12.11.1.

FIGURE 4-4: **BLOCK DIAGRAM OF RB7:RB4 PINS**

and clear the RBPU bit (OPTION\_REG<7>).

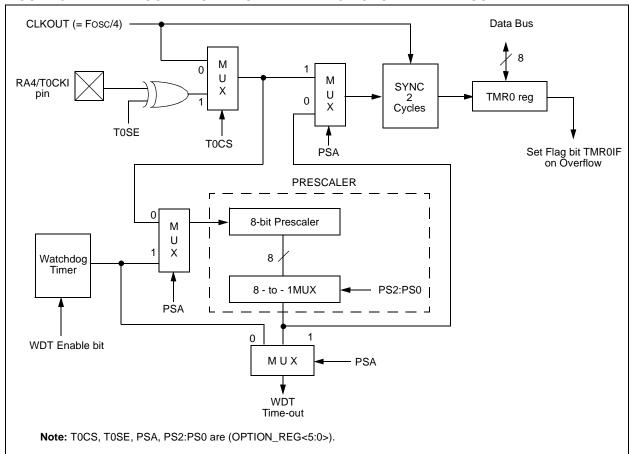

## 5.0 TIMERO MODULE

The Timer0 module timer/counter has the following features:

- · 8-bit timer/counter

- · Readable and writable

- · 8-bit software programmable prescaler

- · Internal or external clock select

- · Interrupt on overflow from FFh to 00h

- · Edge select for external clock

Additional information on the Timer0 module is available in the PICmicro™ Mid-Range MCU Family Reference Manual (DS33023).

Figure 5-1 is a block diagram of the Timer0 module and the prescaler shared with the WDT.

Timer0 operation is controlled through the OPTION\_REG register (Register 5-1 on the following page). Timer mode is selected by clearing bit TOCS (OPTION\_REG<5>). In Timer mode, the Timer0 module will increment every instruction cycle (without prescaler). If the TMR0 register is written, the increment is inhibited for the following two instruction cycles. The user can work around this by writing an adjusted value to the TMR0 register.

Counter mode is selected by setting bit T0CS (OPTION\_REG<5>). In Counter mode, Timer0 will increment, either on every rising or falling edge of pin RA4/T0CKI. The incrementing edge is determined by the Timer0 Source Edge Select bit T0SE (OPTION\_REG<4>). Clearing bit T0SE selects the rising edge. Restrictions on the external clock input are discussed in detail in Section 5.2.

The prescaler is mutually exclusively shared between the Timer0 module and the Watchdog Timer. The prescaler is not readable or writable. Section 5.3 details the operation of the prescaler.

### 5.1 Timer0 Interrupt

The TMR0 interrupt is generated when the TMR0 register overflows from FFh to 00h. This overflow sets bit TMR0IF (INTCON<2>). The interrupt can be masked by clearing bit TMR0IE (INTCON<5>). Bit TMR0IF must be cleared in software by the Timer0 module Interrupt Service Routine, before re-enabling this interrupt. The TMR0 interrupt cannot awaken the processor from SLEEP, since the timer is shut-off during SLEEP.

FIGURE 5-1: BLOCK DIAGRAM OF THE TIMERO MODULE AND PRESCALER

#### 5.3 Prescaler

There is only one prescaler available on the microcontroller; it is shared exclusively between the Timer0 module and the Watchdog Timer. The usage of the prescaler is also mutually exclusive: that is, a prescaler assignment for the Timer0 module means that there is no prescaler for the Watchdog Timer, and vice versa. This prescaler is not readable or writable (see Figure 5-1).

The PSA and PS2:PS0 bits (OPTION\_REG<3:0>) determine the prescaler assignment and prescale ratio. Examples of code for assigning the prescaler assignment are shown in Example 5-1 and Example 5-2. Note that when the prescaler is being assigned to the WDT with ratios other than 1:1, lines 2 and 3 (highlighted) are optional. If a prescale ratio of 1:1 is to used,

however, these lines must be used to set a temporary value. The final 1:1 value is then set in lines 10 and 11 (highlighted). (Line numbers are included in the example for illustrative purposes only, and are not part of the actual code.)

When assigned to the Timer0 module, all instructions writing to the TMR0 register (e.g. CLRF1, MOVWF1, BSF1, x....etc.) will clear the prescaler. When assigned to WDT, a CLRWDT instruction will clear the prescaler along with the Watchdog Timer.

**Note:** Writing to TMR0 when the prescaler is assigned to Timer0, will clear the prescaler count but will not change the prescaler assignment.

#### **EXAMPLE 5-1: CHANGING THE PRESCALER ASSIGNMENT FROM TIMER0 TO WDT**

```

1) BSF

STATUS, RPO

2) MOVLW b'xx0x0xxx'

; Select clock source and prescale value of

3) MOVWF OPTION_REG ; other than 1:1

STATUS, RPO ; Bank0

4) BCF

; Clear TMR0 and prescaler

5) CLRF

TMR0

STATUS, RP1

BSF

; Bank1

7)

MOVLW b'xxxx1xxx'

; Select WDT, do not change prescale value

8) MOVWF OPTION_REG

; Clears WDT and prescaler

9)

CLRWDT

10) MOVLW b'xxxx1xxx'

; Select new prescale value and WDT

11) MOVWF OPTION REG

12) BCF

STATUS, RP0

; Bank0

```

#### **EXAMPLE 5-2: CHANGING THE PRESCALER ASSIGNMENT FROM WDT TO TIMER0**

```

CLRWDT ; Clear WDT and prescaler

BSF STATUS, RPO ; Bank1

MOVLW b'xxxx0xxx' ; Select TMR0, new prescale

MOVWF OPTION_REG ; value and clock source

BCF STATUS, RPO ; Bank0

```

#### TABLE 5-1: REGISTERS ASSOCIATED WITH TIMERO

| Address               | Name       | Bit 7  | Bit 6     | Bit 5  | Bit 4 | Bit 3     | Bit 2     | Bit 1 | Bit 0 | Value on:<br>POR,<br>BOR | Value on<br>all other<br>RESETS |  |

|-----------------------|------------|--------|-----------|--------|-------|-----------|-----------|-------|-------|--------------------------|---------------------------------|--|

| 01h,101h              | TMR0       | Timer0 | Module Re | gister |       | xxxx xxxx | uuuu uuuu |       |       |                          |                                 |  |

| 0Bh,8Bh,<br>10Bh,18Bh | INTCON     | GIE    | PEIE      | TMR0IE | INTE  | RBIE      | TMR0IF    | INTF  | RBIF  | 0000 000x                | 0000 000u                       |  |

| 81h,181h              | OPTION_REG | RBPU   | INTEDG    | T0CS   | T0SE  | PSA       | PS2       | PS1   | PS0   | 1111 1111                | 1111 1111                       |  |

Legend: x = unknown, u = unchanged, - = unimplemented locations read as '0'. Shaded cells are not used by Timer0.

### REGISTER 7-1: T2CON: TIMER2 CONTROL REGISTER (ADDRESS 12h)

| U-0   | R/W-0   | R/W-0   | R/W-0   | R/W-0   | R/W-0  | R/W-0   | R/W-0   |

|-------|---------|---------|---------|---------|--------|---------|---------|

| _     | TOUTPS3 | TOUTPS2 | TOUTPS1 | TOUTPS0 | TMR2ON | T2CKPS1 | T2CKPS0 |

| bit 7 |         |         |         |         |        |         | bit 0   |

bit 7 Unimplemented: Read as '0'

bit 6-3 TOUTPS3:TOUTPS0: Timer2 Output Postscale Select bits

0000 = 1:1 Postscale 0001 = 1:2 Postscale 0010 = 1:3 Postscale

•

1111 = 1:16 Postscale

bit 2 TMR2ON: Timer2 On bit

1 = Timer2 is on 0 = Timer2 is off

bit 1-0 T2CKPS1:T2CKPS0: Timer2 Clock Prescale Select bits

00 = Prescaler is 1 01 = Prescaler is 4 1x = Prescaler is 16

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

- n = Value at POR reset '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

#### TABLE 7-1: REGISTERS ASSOCIATED WITH TIMER2 AS A TIMER/COUNTER

| Address                | Name   | Bit 7                | Bit 6        | Bit 5   | Bit 4   | Bit 3   | Bit 2  | Bit 1   | Bit 0   | Value<br>PC<br>BC | R,   |      | e on<br>other<br>ETS |

|------------------------|--------|----------------------|--------------|---------|---------|---------|--------|---------|---------|-------------------|------|------|----------------------|

| 0Bh,8Bh,<br>10Bh, 18Bh | INTCON | GIE                  | PEIE         | TMR0IE  | INTE    | RBIE    | TMR0IF | INTF    | RBIF    | 0000              | 000x | 0000 | 000u                 |

| 0Ch                    | PIR1   | PSPIF <sup>(1)</sup> | ADIF         | RCIF    | TXIF    | SSPIF   | CCP1IF | TMR2IF  | TMR1IF  | 0000              | 0000 | 0000 | 0000                 |

| 8Ch                    | PIE1   | PSPIE <sup>(1)</sup> | ADIE         | RCIE    | TXIE    | SSPIE   | CCP1IE | TMR2IE  | TMR1IE  | 0000              | 0000 | 0000 | 0000                 |

| 11h                    | TMR2   | Timer2 M             | odule Regis  | ster    |         |         |        |         |         | 0000              | 0000 | 0000 | 0000                 |

| 12h                    | T2CON  | _                    | TOUTPS3      | TOUTPS2 | TOUTPS1 | TOUTPS0 | TMR2ON | T2CKPS1 | T2CKPS0 | -000              | 0000 | -000 | 0000                 |

| 92h                    | PR2    | Timer2 Pe            | eriod Regist | er      |         |         |        |         |         | 1111              | 1111 | 1111 | 1111                 |

Legend: x = unknown, u = unchanged, - = unimplemented, read as '0'. Shaded cells are not used by the Timer2 module.

Note 1: Bits PSPIE and PSPIF are reserved on the PIC16F73/76; always maintain these bits clear.

## 10.2 USART Asynchronous Mode

In this mode, the USART uses standard non-return-to-zero (NRZ) format (one START bit, eight or nine data bits, and one STOP bit). The most common data format is 8-bits. An on-chip, dedicated, 8-bit baud rate generator can be used to derive standard baud rate frequencies from the oscillator. The USART transmits and receives the LSb first. The USART's transmitter and receiver are functionally independent, but use the same data format and baud rate. The baud rate generator produces a clock, either x16 or x64 of the bit shift rate, depending on bit BRGH (TXSTA<2>). Parity is not supported by the hardware, but can be implemented in software (and stored as the ninth data bit). Asynchronous mode is stopped during SLEEP.

Asynchronous mode is selected by clearing bit SYNC (TXSTA<4>).

The USART Asynchronous module consists of the following important elements:

- · Baud Rate Generator

- Sampling Circuit

- · Asynchronous Transmitter

- · Asynchronous Receiver

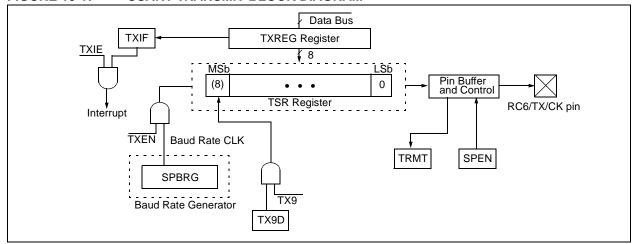

## 10.2.1 USART ASYNCHRONOUS TRANSMITTER

The USART transmitter block diagram is shown in Figure 10-1. The heart of the transmitter is the transmit (serial) shift register (TSR). The shift register obtains its data from the read/write transmit buffer, TXREG. The TXREG register is loaded with data by firmware. The TSR register is not loaded until the STOP bit has been transmitted from the previous load. As soon as the STOP bit is transmitted, the TSR is loaded with new data from the TXREG register (if available). Once the TXREG register transfers the data to the TSR register, the TXREG register is empty. One instruction cycle later, flag bit TXIF (PIR1<4>) and flag bit TRMT (TXSTA<1>)

are set. The TXIF interrupt can be enabled/disabled by setting/clearing enable bit TXIE (PIE1<4>). Flag bit TXIF will be set, regardless of the state of enable bit TXIE and cannot be cleared in software. It will reset only when new data is loaded into the TXREG register. While flag bit TXIF indicates the status of the TXREG register, another bit TRMT (TXSTA<1>) shows the status of the TSR register. Status bit TRMT is a read only bit, which is set one instruction cycle after the TSR register becomes empty, and is cleared one instruction cycle after the TSR register is loaded. No interrupt logic is tied to this bit, so the user has to poll this bit in order to determine if the TSR register is empty.

- **Note 1:** The TSR register is not mapped in data memory, so it is not available to the user.

- 2: Flag bit TXIF is set when enable bit TXEN is set. TXIF is cleared by loading TXREG.

Transmission is enabled by setting enable bit TXEN (TXSTA<5>). The actual transmission will not occur until the TXREG register has been loaded with data and the baud rate generator (BRG) has produced a shift clock (Figure 10-2). The transmission can also be started by first loading the TXREG register and then setting enable bit TXEN. Normally, when transmission is first started, the TSR register is empty. At that point, transfer to the TXREG register will result in an immediate transfer to TSR, resulting in an empty TXREG. A back-to-back transfer is thus possible (Figure 10-3). Clearing enable bit TXEN during a transmission will cause the transmission to be aborted and will reset the transmitter. As a result, the RC6/TX/CK pin will revert to hi-impedance.

In order to select 9-bit transmission, transmit bit TX9 (TXSTA<6>) should be set and the ninth bit should be written to TX9D (TXSTA<0>). The ninth bit must be written before writing the 8-bit data to the TXREG register. This is because a data write to the TXREG register can result in an immediate transfer of the data to the TSR register (if the TSR is empty). In such a case, an incorrect ninth data bit may be loaded in the TSR register.

FIGURE 10-1: USART TRANSMIT BLOCK DIAGRAM

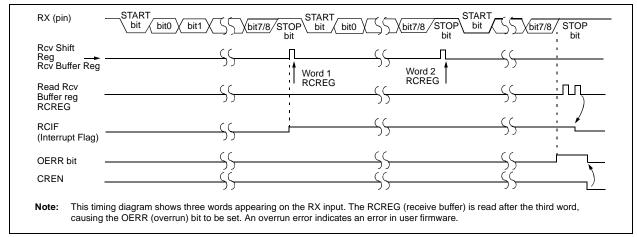

Steps to follow when setting up an Asynchronous Reception:

- Initialize the SPBRG register for the appropriate baud rate. If a high speed baud rate is desired, set bit BRGH (Section 10.1).

- Enable the asynchronous serial port by clearing bit SYNC and setting bit SPEN.

- If interrupts are desired, then set enable bit RCIE.

- 4. If 9-bit reception is desired, then set bit RX9.

- 5. Enable the reception by setting bit CREN.

- Flag bit RCIF will be set when reception is complete and an interrupt will be generated if enable bit RCIE is set.

- Read the RCSTA register to get the ninth bit (if enabled) and determine if any error occurred during reception.

- Read the 8-bit received data by reading the RCREG register.

- If any error occurred, clear the error by clearing enable bit CREN.

- 10. If using interrupts, ensure that GIE and PEIE in the INTCON register are set.

### TABLE 10-6: REGISTERS ASSOCIATED WITH ASYNCHRONOUS RECEPTION

| Address                | Name   | Bit 7                | Bit 6     | Bit 5      | Bit 4 | Bit 3 | Bit 2  | Bit 1  | Bit 0  | Value on:<br>POR,<br>BOR | Value on<br>all other<br>RESETS |

|------------------------|--------|----------------------|-----------|------------|-------|-------|--------|--------|--------|--------------------------|---------------------------------|

| 0Bh, 8Bh,<br>10Bh,18Bh | INTCON | GIE                  | PEIE      | TMR0IE     | INTE  | RBIE  | TMR0IF | INTF   | RBIF   | 0000 000x                | 0000 000u                       |

| 0Ch                    | PIR1   | PSPIF <sup>(1)</sup> | ADIF      | RCIF       | TXIF  | SSPIF | CCP1IF | TMR2IF | TMR1IF | 0000 0000                | 0000 0000                       |

| 18h                    | RCSTA  | SPEN                 | RX9       | SREN       | CREN  | _     | FERR   | OERR   | RX9D   | 0000 -00x                | 0000 -00x                       |

| 1Ah                    | RCREG  | USART R              | eceive Re | gister     |       |       |        |        |        | 0000 0000                | 0000 0000                       |

| 8Ch                    | PIE1   | PSPIE <sup>(1)</sup> | ADIE      | RCIE       | TXIE  | SSPIE | CCP1IE | TMR2IE | TMR1IE | 0000 0000                | 0000 0000                       |

| 98h                    | TXSTA  | CSRC                 | TX9       | TXEN       | SYNC  | _     | BRGH   | TRMT   | TX9D   | 0000 -010                | 0000 -010                       |

| 99h                    | SPBRG  | Baud Rate            | Generato  | r Register | r     |       |        |        |        | 0000 0000                | 0000 0000                       |

Legend: x = unknown, - = unimplemented locations read as '0'. Shaded cells are not used for asynchronous reception.

Note 1: Bits PSPIE and PSPIF are reserved on the PIC16F73/76 devices; always maintain these bits clear.

## REGISTER 11-2: ADCON1 REGISTER (ADDRESS 9Fh)

| U-0   | U-0 | U-0 | U-0 | U-0 | R/W-0 | R/W-0 | R/W-0 |

|-------|-----|-----|-----|-----|-------|-------|-------|

| _     | _   | _   | _   | _   | PCFG2 | PCFG1 | PCFG0 |

| bit 7 |     |     |     |     |       |       | bit 0 |

bit 7-3 Unimplemented: Read as '0'

bit 2-0 PCFG2:PCFG0: A/D Port Configuration Control bits

| PCFG2:PCFG0 | RA0 | RA1 | RA2 | RA5 | RA3  | RE0 <sup>(1)</sup> | RE1 <sup>(1)</sup> | RE2 <sup>(1)</sup> | VREF |

|-------------|-----|-----|-----|-----|------|--------------------|--------------------|--------------------|------|

| 000         | Α   | Α   | Α   | Α   | Α    | Α                  | Α                  | Α                  | VDD  |

| 001         | Α   | Α   | Α   | Α   | VREF | Α                  | Α                  | Α                  | RA3  |

| 010         | Α   | Α   | Α   | Α   | Α    | D                  | D                  | D                  | Vdd  |

| 011         | Α   | Α   | Α   | Α   | VREF | D                  | D                  | D                  | RA3  |

| 100         | Α   | Α   | D   | D   | Α    | D                  | D                  | D                  | Vdd  |

| 101         | Α   | Α   | D   | D   | VREF | D                  | D                  | D                  | RA3  |

| 11x         | D   | D   | D   | D   | D    | D                  | D                  | D                  | Vdd  |

A = Analog input D = Digital I/O

Note 1: RE0, RE1 and RE2 are implemented on the PIC16F74/77 only.

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

- n = Value at POR reset '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

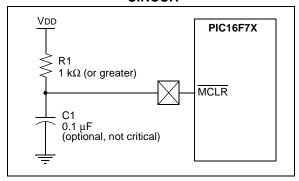

## 12.4 MCLR

PIC16F7X devices have a noise filter in the MCLR Reset path. The filter will detect and ignore small pulses.

It should be noted that a WDT Reset does not drive  $\overline{\text{MCLR}}$  pin low.

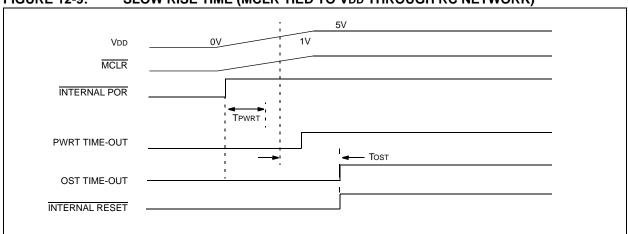

The behavior of the ESD protection on the MCLR pin has been altered from previous devices of this family. Voltages applied to the pin that exceed its specification can result in both MCLR Resets and excessive current beyond the device specification during the ESD event. For this reason, Microchip recommends that the MCLR pin no longer be tied directly to VDD. The use of an RC network, as shown in Figure 12-5, is suggested.

FIGURE 12-5: RECOMMENDED MCLR

CIRCUIT

## 12.5 Power-on Reset (POR)

A Power-on Reset pulse is generated on-chip when VDD rise is detected (in the range of 1.2V - 1.7V). To take advantage of the POR, tie the MCLR pin to VDD as described in Section 12.4. A maximum rise time for VDD is specified. See the Electrical Specifications for details.

When the device starts normal operation (exits the RESET condition), device operating parameters (voltage, frequency, temperature,...) must be met to ensure operation. If these conditions are not met, the device must be held in RESET until the operating conditions are met. For additional information, refer to Application Note, AN607, "Power-up Trouble Shooting" (DS00607).

## 12.6 Power-up Timer (PWRT)

The Power-up Timer provides a fixed 72 ms nominal time-out on power-up only from the POR. The Power-up Timer operates on an internal RC oscillator. The chip is kept in RESET as long as the PWRT is active. The PWRT's time delay allows VDD to rise to an acceptable level. A configuration bit is provided to enable/ disable the PWRT.

The power-up time delay will vary from chip to chip, due to VDD, temperature and process variation. See DC parameters for details (TPWRT, parameter #33).

## 12.7 Oscillator Start-up Timer (OST)

The Oscillator Start-up Timer (OST) provides 1024 oscillator cycles (from OSC1 input) delay after the PWRT delay is over (if enabled). This helps to ensure that the crystal oscillator or resonator has started and stabilized.

The OST time-out is invoked only for XT, LP and HS modes and only on Power-on Reset, or wake-up from SLEEP.

## 12.8 Brown-out Reset (BOR)

The configuration bit, BODEN, can enable or disable the Brown-out Reset circuit. If VDD falls below VBOR (parameter D005, about 4V) for longer than TBOR (parameter #35, about 100  $\mu\text{S}$ ), the brown-out situation will reset the device. If VDD falls below VBOR for less than TBOR, a RESET may not occur.

Once the brown-out occurs, the device will remain in Brown-out Reset until VDD rises above VBOR. The Power-up Timer then keeps the device in RESET for TPWRT (parameter #33, about 72 mS). If VDD should fall below VBOR during TPWRT, the Brown-out Reset process will restart when VDD rises above VBOR, with the Power-up Timer Reset. The Power-up Timer is always enabled when the Brown-out Reset circuit is enabled, regardless of the state of the PWRT configuration bit.

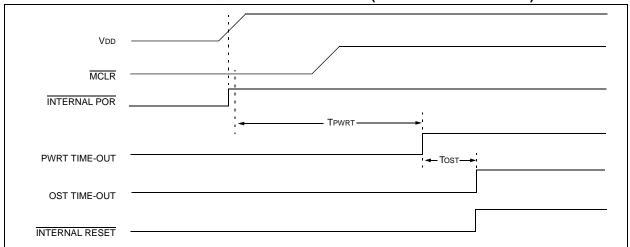

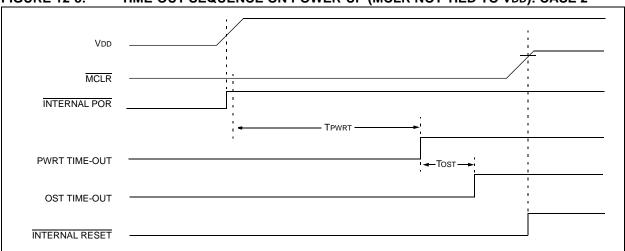

#### 12.9 Time-out Sequence

On power-up, the time-out sequence is as follows: the PWRT delay starts (if enabled) when a POR Reset occurs. Then, OST starts counting 1024 oscillator cycles when PWRT ends (LP, XT, HS). When the OST ends, the device comes out of RESET.

If MCLR is kept low long enough, all delays will expire. Bringing MCLR high will begin execution immediately. This is useful for testing purposes or to synchronize more than one PIC16F7X device operating in parallel.

Table 12-5 shows the RESET conditions for the STATUS, PCON and PC registers, while Table 12-6 shows the RESET conditions for all the registers.

FIGURE 12-7: TIME-OUT SEQUENCE ON POWER-UP (MCLR NOT TIED TO VDD): CASE 1

FIGURE 12-8: TIME-OUT SEQUENCE ON POWER-UP (MCLR NOT TIED TO VDD): CASE 2

FIGURE 12-9: SLOW RISE TIME (MCLR TIED TO VDD THROUGH RC NETWORK)

# PIC16F7X

| SWAPF            | Swap Nibbles in f                                                                                                                                                  |  |  |  |  |  |

|------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| Syntax:          | [ label ] SWAPF f,d                                                                                                                                                |  |  |  |  |  |

| Operands:        | $0 \le f \le 127$<br>$d \in [0,1]$                                                                                                                                 |  |  |  |  |  |

| Operation:       | $(f<3:0>) \rightarrow (destination<7:4>),$<br>$(f<7:4>) \rightarrow (destination<3:0>)$                                                                            |  |  |  |  |  |

| Status Affected: | None                                                                                                                                                               |  |  |  |  |  |

| Description:     | The upper and lower nibbles of register 'f' are exchanged. If 'd' is 0, the result is placed in the W register. If 'd' is 1, the result is placed in register 'f'. |  |  |  |  |  |

| XORWF            | Exclusive OR W with f                                                                                                                                                       |  |  |  |  |

|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| Syntax:          | [ label ] XORWF f,d                                                                                                                                                         |  |  |  |  |

| Operands:        | $0 \le f \le 127$<br>$d \in [0,1]$                                                                                                                                          |  |  |  |  |

| Operation:       | (W) .XOR. (f) $\rightarrow$ (destination)                                                                                                                                   |  |  |  |  |

| Status Affected: | Z                                                                                                                                                                           |  |  |  |  |

| Description:     | Exclusive OR the contents of the W register with register 'f'. If 'd' is 0, the result is stored in the W register. If 'd' is 1, the result is stored back in register 'f'. |  |  |  |  |

| XORLW            | Exclusive OR Literal with W                                                                                       |  |  |  |

|------------------|-------------------------------------------------------------------------------------------------------------------|--|--|--|

| Syntax:          | [ label ] XORLW k                                                                                                 |  |  |  |

| Operands:        | $0 \le k \le 255$                                                                                                 |  |  |  |

| Operation:       | (W) .XOR. $k \rightarrow (W)$                                                                                     |  |  |  |

| Status Affected: | Z                                                                                                                 |  |  |  |

| Description:     | The contents of the W register are XOR'ed with the eight-bit literal 'k'. The result is placed in the W register. |  |  |  |

# PIC16F7X

NOTES:

## 15.0 ELECTRICAL CHARACTERISTICS

#### **Absolute Maximum Ratings †**

| Ambient temperature under bias                                                                            | 55 to +125°C                                       |

|-----------------------------------------------------------------------------------------------------------|----------------------------------------------------|

| Storage temperature                                                                                       | 65°C to +150°C                                     |

| Voltage on any pin with respect to Vss (except VDD, MCLR. and RA4)                                        | 0.3V to (VDD + 0.3V)                               |

| Voltage on VDD with respect to Vss                                                                        | 0.3 to +6.5V                                       |

| Voltage on MCLR with respect to Vss (Note 2)                                                              | 0 to +13.5V                                        |

| Voltage on RA4 with respect to Vss                                                                        | 0 to +12V                                          |

| Total power dissipation (Note 1)                                                                          | 1.0W                                               |

| Maximum current out of Vss pin                                                                            | 300 mA                                             |

| Maximum current into VDD pin                                                                              | 250 mA                                             |

| Input clamp current, IiK (VI < 0 or VI > VDD)                                                             | ± 20 mA                                            |

| Output clamp current, lok (Vo < 0 or Vo > VDD)                                                            |                                                    |

| Maximum output current sunk by any I/O pin                                                                | 25 mA                                              |

| Maximum output current sourced by any I/O pin                                                             | 25 mA                                              |

| Maximum current sunk by PORTA, PORTB, and PORTE (combined) (Note 3)                                       | 200 mA                                             |

| Maximum current sourced by PORTA, PORTB, and PORTE (combined) (Note 3)                                    | 200 mA                                             |

| Maximum current sunk by PORTC and PORTD (combined) (Note 3)                                               | 200 mA                                             |

| Maximum current sourced by PORTC and PORTD (combined) (Note 3)                                            | 200 mA                                             |

| Note 4. Dower discipation is calculated as follows: Ddis VDD v (IDD \ \\ \\ \\ \\ \\ \\ \\ \\ \\ \\ \\ \\ | Vouly loui + \(\frac{\chi}{2}\) \(\frac{\chi}{2}\) |

- Note 1: Power dissipation is calculated as follows: Pdis = VDD x {IDD  $\Sigma$  IOH} +  $\Sigma$  {(VDD VOH) x IOH} +  $\Sigma$ (VOI x IOL)

- 2: Voltage spikes at the  $\overline{MCLR}$  pin may cause latchup. A series resistor of greater than 1 k $\Omega$  should be used to pull  $\overline{MCLR}$  to VDD, rather than tying the pin directly to VDD.

- 3: PORTD and PORTE are not implemented on the PIC16F73/76 devices.

† NOTICE: Stresses above those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress rating only and functional operation of the device at those or any other conditions above those indicated in the operation listings of this specification is not implied. Exposure to maximum rating conditions for extended periods may affect device reliability.

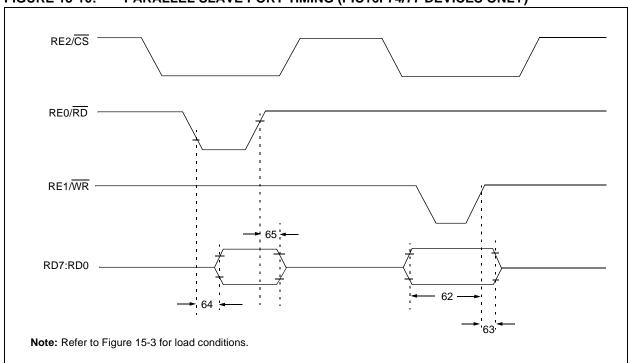

FIGURE 15-10: PARALLEL SLAVE PORT TIMING (PIC16F74/77 DEVICES ONLY)

TABLE 15-6: PARALLEL SLAVE PORT REQUIREMENTS (PIC16F74/77 DEVICES ONLY)

| Parameter No. | Symbol   | Characteristic                  |                       | Min      | Тур† | Max      | Units    | Conditions          |

|---------------|----------|---------------------------------|-----------------------|----------|------|----------|----------|---------------------|

| 62            | TdtV2wrH | Data in valid before WR↑ or CS1 | (setup time)          | 20<br>25 | _    | 1 1      | ns<br>ns | Extended range only |

| 63*           | TwrH2dtl | WR↑ or CS↑ to data in invalid   | Standard(F)           | 20       | _    |          | ns       |                     |

|               |          | (hold time)                     | Extended( <b>LF</b> ) | 35       | _    | _        | ns       |                     |

| 64            | TrdL2dtV | RD↓ and CS↓ to data out valid   |                       | _        | _    | 80<br>90 | ns<br>ns | Extended range only |

| 65            | TrdH2dtl | RD↑ or CS↓ to data out invalid  |                       | 10       | _    | 30       | ns       |                     |

<sup>\*</sup> These parameters are characterized but not tested.

<sup>†</sup> Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

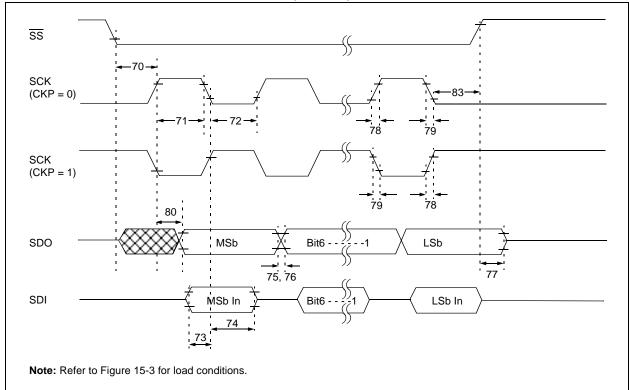

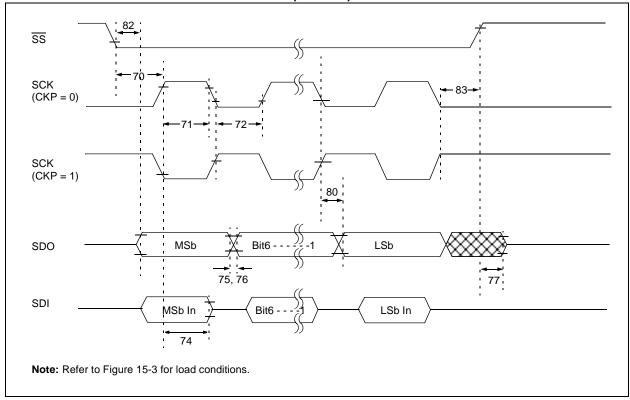

FIGURE 15-13: SPI SLAVE MODE TIMING (CKE = 0)

FIGURE 15-14: SPI SLAVE MODE TIMING (CKE = 1)

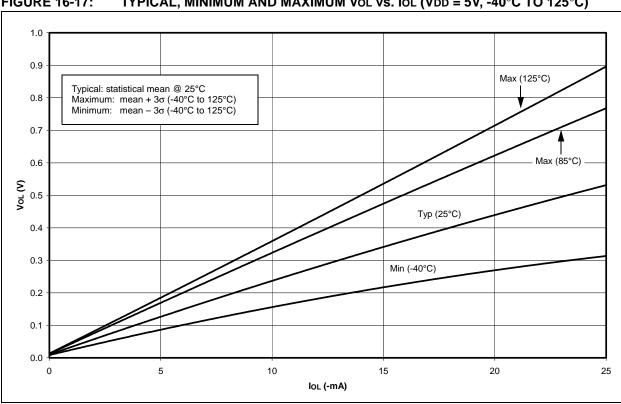

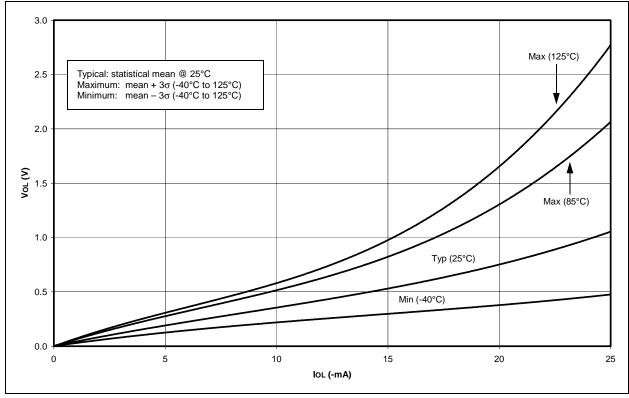

**FIGURE 16-17:** TYPICAL, MINIMUM AND MAXIMUM Vol vs. Iol (VDD = 5V, -40°C TO 125°C)

## PIC16F7X PRODUCT IDENTIFICATION SYSTEM

To order or obtain information, e.g., on pricing or delivery, refer to the factory or the listed sales office.

| <u>x</u>                                          | xxx<br>_                                                                                                                                                                                                                                                                            | Examples:                                                                                                                                                                                                                                                                                                                                                                                    |

|---------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Range                                             |                                                                                                                                                                                                                                                                                     | <ul> <li>a) PIC16F77-I/P 301 = Industrial temp., PDIP package, normal VDD limits, QTP pattern #301.</li> <li>b) PIC16LF76-I/SO = Industrial temp., SOIC package, Extended VDD limits.</li> <li>c) PIC16F74-E/P = Extended temp., PDIP package, normal VDD limits.</li> </ul>                                                                                                                 |

| $I = -40^{\circ}C \text{ to } +85^{\circ}C$       | (Industrial)                                                                                                                                                                                                                                                                        | Note 1: F = CMOS FLASH  LF = Low Power CMOS FLASH                                                                                                                                                                                                                                                                                                                                            |

| PT = TQFP (Thin Quad<br>SO = SOIC                 | d Flatpack)                                                                                                                                                                                                                                                                         | 2: T = in tape and reel - SOIC, PLCC, SSOP, TQFP packages only.                                                                                                                                                                                                                                                                                                                              |

| QTP, SQTP, Code or Special I<br>(blank otherwise) | Requirements                                                                                                                                                                                                                                                                        |                                                                                                                                                                                                                                                                                                                                                                                              |

|                                                   | PIC16F7X <sup>(1)</sup> , PIC16F7XT <sup>(1)</sup> ; PIC16LF7X <sup>(1)</sup> , PIC16LF7XT <sup>(1)</sup> I = -40°C to +85°C E = -40°C to +125°C  ML = MLF (Micro Lead PT = TQFP (Thin Qua SO = SOIC SP = Skinny Plastic DI P = PDIP L = PLCC SS = SSOP  QTP, SQTP, Code or Special | PIC16F7X <sup>(1)</sup> , PIC16F7XT <sup>(1)</sup> ; VDD range 4.0V to 5.5V PIC16LF7X <sup>(1)</sup> , PIC16LF7XT <sup>(1)</sup> ; VDD range 2.0V to 5.5V  I = -40°C to +85°C (Industrial) E = -40°C to +125°C (Extended)  ML = MLF (Micro Lead Frame) PT = TQFP (Thin Quad Flatpack) SO = SOIC SP = Skinny Plastic DIP P = PDIP L = PLCC SS = SSOP  QTP, SQTP, Code or Special Requirements |

## **Sales and Support**

#### Data Sheets

Products supported by a preliminary Data Sheet may have an errata sheet describing minor operational differences and recommended workarounds. To determine if an errata sheet exists for a particular device, please contact one of the following:

- 1. Your local Microchip sales office

- 2. The Microchip Corporate Literature Center U.S. FAX: (480) 792-7277

- 3. The Microchip Worldwide Site (www.microchip.com)

Please specify which device, revision of silicon and Data Sheet (include Literature #) you are using.

#### **New Customer Notification System**

Register on our web site (www.microchip.com/cn) to receive the most current information on our products.