Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Obsolete                                                                   |

|----------------------------|----------------------------------------------------------------------------|

| Core Processor             | PIC                                                                        |

| Core Size                  | 8-Bit                                                                      |

| Speed                      | 20MHz                                                                      |

| Connectivity               | I²C, SPI, UART/USART                                                       |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                      |

| Number of I/O              | 33                                                                         |

| Program Memory Size        | 14KB (8K x 14)                                                             |

| Program Memory Type        | FLASH                                                                      |

| EEPROM Size                | -                                                                          |

| RAM Size                   | 368 x 8                                                                    |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 5.5V                                                                  |

| Data Converters            | A/D 8x8b                                                                   |

| Oscillator Type            | External                                                                   |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                          |

| Mounting Type              | Surface Mount                                                              |

| Package / Case             | 44-TQFP                                                                    |

| Supplier Device Package    | 44-TQFP (10x10)                                                            |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16lf77t-i-ptg |

|                            |                                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

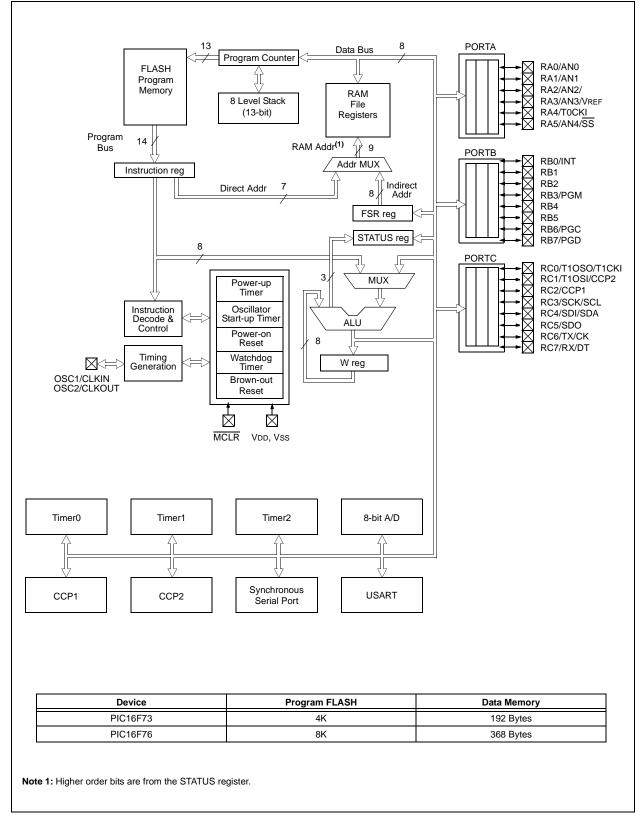

#### 1.0 **DEVICE OVERVIEW**

This document contains device specific information about the following devices:

- PIC16F73

- PIC16F74

- PIC16F76

- PIC16F77

PIC16F73/76 devices are available only in 28-pin packages, while PIC16F74/77 devices are available in 40-pin and 44-pin packages. All devices in the PIC16F7X family share common architecture, with the following differences:

- The PIC16F73 and PIC16F76 have one-half of the total on-chip memory of the PIC16F74 and **PIC16F77**

- The 28-pin devices have 3 I/O ports, while the 40/44-pin devices have 5

- · The 28-pin devices have 11 interrupts, while the 40/44-pin devices have 12

- The 28-pin devices have 5 A/D input channels, while the 40/44-pin devices have 8

- The Parallel Slave Port is implemented only on the 40/44-pin devices

PIC16F7X DEVICE FEATURES **PIC16F74 PIC16F76 Key Features PIC16F73 PIC16F77 Operating Frequency** DC - 20 MHz DC - 20 MHz DC - 20 MHz DC - 20 MHz **RESETS** (and Delays) POR, BOR POR. BOR POR. BOR POR, BOR (PWRT, OST) (PWRT, OST) (PWRT, OST) (PWRT, OST) FLASH Program Memory 4K 4K 8K 8K (14-bit words) Data Memory (bytes) 368 192 192 368 Interrupts 11 12 11 12 I/O Ports Ports A,B,C Ports A,B,C Ports A,B,C,D,E Ports A,B,C,D,E Timers 3 3 3 3 Capture/Compare/PWM Modules 2 2 2 2 SSP, USART Serial Communications SSP, USART SSP. USART SSP, USART Parallel Communications PSP PSP 8-bit Analog-to-Digital Module **5 Input Channels** 8 Input Channels 5 Input Channels 8 Input Channels Instruction Set **35 Instructions 35 Instructions** 35 Instructions **35 Instructions** Packaging 28-pin DIP 40-pin PDIP 28-pin DIP 40-pin PDIP 28-pin SOIC 44-pin PLCC 28-pin SOIC 44-pin PLCC 28-pin SSOP 44-pin TQFP 28-pin SSOP 44-pin TQFP 28-pin MLF 28-pin MLF

#### **TABLE 1-1:**

The available features are summarized in Table 1-1. Block diagrams of the PIC16F73/76 and PIC16F74/77 devices are provided in Figure 1-1 and Figure 1-2, respectively. The pinouts for these device families are listed in Table 1-2 and Table 1-3.

Additional information may be found in the PICmicro™ Mid-Range Reference Manual (DS33023), which may be obtained from your local Microchip Sales Representative or downloaded from the Microchip website. The Reference Manual should be considered a complementary document to this data sheet, and is highly recommended reading for a better understanding of the device architecture and operation of the peripheral modules.

| TABLE 1-2: | PIC16F73 AND PIC16F76 PINOUT DESCRIPTION (CONTINUED) |

|------------|------------------------------------------------------|

|------------|------------------------------------------------------|

| Pin Name        | DIP<br>SSOP<br>SOIC<br>Pin# | MLF<br>Pin# |      | Buffer<br>Type        | Description                                                      |  |  |

|-----------------|-----------------------------|-------------|------|-----------------------|------------------------------------------------------------------|--|--|

|                 |                             |             |      |                       | PORTB is a bi-directional I/O port. PORTB can be software        |  |  |

|                 |                             |             |      | (o(1)                 | programmed for internal weak pull-up on all inputs.              |  |  |

| RB0/INT         | 21                          | 18          | 1/0  | TTL/ST <sup>(1)</sup> |                                                                  |  |  |

| RB0             |                             |             | I/O  |                       | Digital I/O.                                                     |  |  |

| INT             |                             |             | I    |                       | External interrupt.                                              |  |  |

| RB1             | 22                          | 19          | I/O  | TTL                   | Digital I/O.                                                     |  |  |

| RB2             | 23                          | 20          | I/O  | TTL                   | Digital I/O.                                                     |  |  |

| RB3/PGM         | 24                          | 21          |      | TTL                   |                                                                  |  |  |

| RB3             |                             |             | I/O  |                       | Digital I/O.                                                     |  |  |

| PGM             |                             |             | I/O  |                       | Low voltage ICSP programming enable pin.                         |  |  |

| RB4             | 25                          | 22          | I/O  | TTL                   | Digital I/O.                                                     |  |  |

| RB5             | 26                          | 23          | I/O  | TTL                   | Digital I/O.                                                     |  |  |

| RB6/PGC         | 27                          | 24          | ., 0 | TTL/ST <sup>(2)</sup> | Digital i/ O.                                                    |  |  |

| RB6             | 21                          | 24          | I/O  | 112/31.7              | Digital I/O.                                                     |  |  |

| PGC             |                             |             | I/O  |                       | In-Circuit Debugger and ICSP programming clock.                  |  |  |

|                 | 20                          | 25          | ., O | TTL/ST <sup>(2)</sup> |                                                                  |  |  |

| RB7/PGD<br>RB7  | 28                          | 25          | I/O  | 11L/51(-)             | Digital I/O.                                                     |  |  |

| PGD             |                             |             | 1/O  |                       | In-Circuit Debugger and ICSP programming data.                   |  |  |

| FGD             |                             |             | 1/0  |                       |                                                                  |  |  |

|                 |                             |             |      |                       | PORTC is a bi-directional I/O port.                              |  |  |

| RC0/T1OSO/T1CKI | 11                          | 8           |      | ST                    |                                                                  |  |  |

| RC0             |                             |             | I/O  |                       | Digital I/O.                                                     |  |  |

| T1OSO           |                             |             | 0    |                       | Timer1 oscillator output.                                        |  |  |

| T1CKI           |                             |             | I    |                       | Timer1 external clock input.                                     |  |  |

| RC1/T1OSI/CCP2  | 12                          | 9           |      | ST                    |                                                                  |  |  |

| RC1             |                             |             | I/O  |                       | Digital I/O.                                                     |  |  |

| T1OSI           |                             |             |      |                       | Timer1 oscillator input.                                         |  |  |

| CCP2            |                             |             | I/O  |                       | Capture2 input, Compare2 output, PWM2 output.                    |  |  |

| RC2/CCP1        | 13                          | 10          |      | ST                    |                                                                  |  |  |

| RC2             |                             |             | I/O  |                       | Digital I/O.                                                     |  |  |

| CCP1            |                             |             | I/O  |                       | Capture1 input/Compare1 output/PWM1 output.                      |  |  |

| RC3/SCK/SCL     | 14                          | 11          |      | ST                    |                                                                  |  |  |

| RC3             |                             |             | I/O  |                       | Digital I/O.                                                     |  |  |

| SCK             |                             |             | I/O  |                       | Synchronous serial clock input/output for SPI mode.              |  |  |

| SCL             |                             |             | I/O  |                       | Synchronous serial clock input/output for I <sup>2</sup> C mode. |  |  |

| RC4/SDI/SDA     | 15                          | 12          |      | ST                    |                                                                  |  |  |

| RC4             |                             |             | I/O  |                       | Digital I/O.                                                     |  |  |

| SDI             |                             |             | 1    |                       | SPI data in.                                                     |  |  |

| SDA             |                             |             | I/O  |                       | I <sup>2</sup> C data I/O.                                       |  |  |

| RC5/SDO         | 16                          | 13          |      | ST                    |                                                                  |  |  |

| RC5             |                             |             | I/O  |                       | Digital I/O.                                                     |  |  |

| SDO             |                             |             | 0    |                       | SPI data out.                                                    |  |  |

| RC6/TX/CK       | 17                          | 14          |      | ST                    |                                                                  |  |  |

| RC6             |                             |             | I/O  |                       | Digital I/O.                                                     |  |  |

| TX              |                             |             | 0    |                       | USART asynchronous transmit.                                     |  |  |

| CK              |                             |             | I/O  |                       | USART 1 synchronous clock.                                       |  |  |

| RC7/RX/DT       | 18                          | 15          |      | ST                    |                                                                  |  |  |

| RC7             |                             |             | I/O  |                       | Digital I/O.                                                     |  |  |

| RX              |                             |             | I    |                       | USART asynchronous receive.                                      |  |  |

| DT              |                             |             | I/O  |                       | USART synchronous data.                                          |  |  |

| Vss             | 8, 19                       | 5, 16       | Р    | —                     | Ground reference for logic and I/O pins.                         |  |  |

| V 55            | 1                           | 47          | Р    | 1                     | Desitive events for legic and 1/0 nine                           |  |  |

| VDD             | 20                          | 17          | Р    | —                     | Positive supply for logic and I/O pins.                          |  |  |

This buffer is a Schmitt Trigger input when used in Serial Programming mode.

This buffer is a Schmitt Trigger input when configured in RC Oscillator mode and a CMOS input otherwise.

### TABLE 1-3:PIC16F74 AND PIC16F77 PINOUT DESCRIPTION

| OSC1/CLKI<br>OSC1<br>CLKI<br>OSC2/CLKO<br>OSC2<br>CLKO<br>MCLR/VPP<br>MCLR<br>VPP | 13 | 14<br>15 | 30<br>31 | 1        | ST/CMOS <sup>(4)</sup> | Oscillator crystal or external clock input.<br>Oscillator crystal input or external clock source input.<br>ST buffer when configured in RC mode. Otherwise<br>CMOS.<br>External clock source input. Always associated with pin |

|-----------------------------------------------------------------------------------|----|----------|----------|----------|------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| CLKI<br>OSC2/CLKO<br>OSC2<br>CLKO<br><u>MCLR/VPP</u><br>MCLR                      | 14 | 15       | 31       | I        |                        | Oscillator crystal input or external clock source input.<br>ST buffer when configured in RC mode. Otherwise<br>CMOS.<br>External clock source input. Always associated with pin                                                |

| OSC2/CLKO<br>OSC2<br>CLKO<br>MCLR/VPP<br>MCLR                                     | 14 | 15       | 31       |          |                        | CMOS.<br>External clock source input. Always associated with pin                                                                                                                                                               |

| OSC2/CLKO<br>OSC2<br>CLKO<br>MCLR/VPP<br>MCLR                                     | 14 | 15       | 31       |          |                        | External clock source input. Always associated with pin                                                                                                                                                                        |

| OSC2<br>CLKO<br>MCLR/VPP<br>MCLR                                                  | 14 | 15       | 31       |          |                        |                                                                                                                                                                                                                                |

| OSC2<br>CLKO<br>MCLR/VPP<br>MCLR                                                  | 14 | 15       | 31       | 0        |                        | function OSC1 (see OSC1/CLKI, OSC2/CLKO pins).                                                                                                                                                                                 |

| CLKO<br>MCLR/VPP<br>MCLR                                                          |    |          |          | <u> </u> | I —                    | Oscillator crystal or clock output.                                                                                                                                                                                            |

| MCLR/Vpp<br>MCLR                                                                  |    |          |          | 0        |                        | Oscillator crystal output.                                                                                                                                                                                                     |

| MCLR/Vpp<br>MCLR                                                                  |    |          |          |          |                        | Connects to crystal or resonator in Crystal Oscillator                                                                                                                                                                         |

| MCLR/Vpp<br>MCLR                                                                  |    |          |          |          |                        | mode.                                                                                                                                                                                                                          |

| MCLR                                                                              |    |          |          | 0        |                        | In RC mode, OSC2 pin outputs CLKO, which has 1/4                                                                                                                                                                               |

| MCLR                                                                              |    |          |          |          |                        | the frequency of OSC1 and denotes the instruction                                                                                                                                                                              |

| MCLR                                                                              |    |          |          |          |                        | cycle rate.                                                                                                                                                                                                                    |

|                                                                                   | 1  | 2        | 18       |          | ST                     | Master Clear (input) or programming voltage (output).                                                                                                                                                                          |

| Vpp                                                                               |    |          |          | I        |                        | Master Clear (Reset) input. This pin is an active low                                                                                                                                                                          |

| VPP                                                                               |    |          |          |          |                        | RESET to the device.                                                                                                                                                                                                           |

|                                                                                   |    |          |          | Р        |                        | Programming voltage input.                                                                                                                                                                                                     |

|                                                                                   |    |          |          |          |                        | PORTA is a bi-directional I/O port.                                                                                                                                                                                            |

| RA0/AN0                                                                           | 2  | 3        | 19       |          | TTL                    |                                                                                                                                                                                                                                |

| RA0                                                                               |    |          |          | I/O      |                        | Digital I/O.                                                                                                                                                                                                                   |

| AN0                                                                               |    |          |          | I        |                        | Analog input 0.                                                                                                                                                                                                                |

| RA1/AN1                                                                           | 3  | 4        | 20       |          | TTL                    |                                                                                                                                                                                                                                |

| RA1                                                                               |    |          |          | I/O      |                        | Digital I/O.                                                                                                                                                                                                                   |

| AN1                                                                               |    |          |          | I        |                        | Analog input 1.                                                                                                                                                                                                                |

| RA2/AN2                                                                           | 4  | 5        | 21       |          | TTL                    |                                                                                                                                                                                                                                |

| RA2                                                                               |    |          |          | I/O      |                        | Digital I/O.                                                                                                                                                                                                                   |

| AN2                                                                               |    |          |          | I        |                        | Analog input 2.                                                                                                                                                                                                                |

| RA3/AN3/Vref                                                                      | 5  | 6        | 22       |          | TTL                    |                                                                                                                                                                                                                                |

| RA3                                                                               |    |          |          | I/O      |                        | Digital I/O.                                                                                                                                                                                                                   |

| AN3                                                                               |    |          |          | I        |                        | Analog input 3.                                                                                                                                                                                                                |

| VREF                                                                              |    |          |          | I        |                        | A/D reference voltage input.                                                                                                                                                                                                   |

| RA4/T0CKI                                                                         | 6  | 7        | 23       |          | ST                     |                                                                                                                                                                                                                                |

| RA4                                                                               |    |          |          | I/O      |                        | Digital I/O – Open drain when configured as output.                                                                                                                                                                            |

| TOCKI                                                                             |    |          |          | I        |                        | Timer0 external clock input.                                                                                                                                                                                                   |

| RA5/SS/AN4                                                                        | 7  | 8        | 24       |          | TTL                    |                                                                                                                                                                                                                                |

| RA5                                                                               |    | -        |          | I/O      |                        | Digital I/O.                                                                                                                                                                                                                   |

| SS                                                                                | 1  |          |          | 1        |                        | SPI slave select input.                                                                                                                                                                                                        |

| AN4                                                                               |    |          |          |          | 1                      |                                                                                                                                                                                                                                |

| Legend: I = inpu                                                                  |    | 1        |          |          |                        | Analog input 4.                                                                                                                                                                                                                |

— = Not used TTL = TTL input ST = Schmitt Trigger input

**Note 1:** This buffer is a Schmitt Trigger input when configured as an external interrupt.

2: This buffer is a Schmitt Trigger input when used in Serial Programming mode.

**3:** This buffer is a Schmitt Trigger input when configured as general purpose I/O and a TTL input when used in the Parallel Slave Port mode (for interfacing to a microprocessor bus).

4: This buffer is a Schmitt Trigger input when configured in RC Oscillator mode and a CMOS input otherwise.

| Name       | Bit# | Buffer Type           | Function                                                                                                                                                                                                                          |

|------------|------|-----------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| RE0/RD/AN5 | bit0 | ST/TTL <sup>(1)</sup> | Input/output port pin or read control input in Parallel Slave Port mode or<br>analog input.<br>For RD (PSP mode):<br>1 = IDLE<br>0 = Read operation. Contents of PORTD register output to PORTD I/O<br>pins (if chip selected).   |

| RE1/WR/AN6 | bit1 | ST/TTL <sup>(1)</sup> | Input/output port pin or write control input in Parallel Slave Port mode<br>or analog input.<br>For WR (PSP mode):<br>1 = IDLE<br>0 = Write operation. Value of PORTD I/O pins latched into PORTD<br>register (if chip selected). |

| RE2/CS/AN7 | bit2 | ST/TTL <sup>(1)</sup> | Input/output port pin or chip select control input in Parallel Slave Port<br>mode or analog input.<br>For CS (PSP mode):<br>1 = Device is not selected<br>0 = Device is selected                                                  |

Legend: ST = Schmitt Trigger input, TTL = TTL input **Note 1:** Input buffers are Schmitt Triggers when in I/O mode and TTL buffers when in Parallel Slave Port mode.

| TABLE 4-10: SUMMARY OF REGISTERS ASSOCIATED WITH PORTE | <b>TABLE 4-10</b> : | SUMMARY OF REGISTERS ASSOCIATED WITH PORTE |

|--------------------------------------------------------|---------------------|--------------------------------------------|

|--------------------------------------------------------|---------------------|--------------------------------------------|

| Addr | Name   | Bit 7 | Bit 6 | Bit 5 | Bit 4   | Bit 3 | Bit 2                     | Bit 1 | Bit 0     | Value on:<br>POR,<br>BOR | Value on all<br>other<br>RESETS |

|------|--------|-------|-------|-------|---------|-------|---------------------------|-------|-----------|--------------------------|---------------------------------|

| 09h  | PORTE  | —     | —     |       | —       | _     | RE2                       | RE1   | RE0       | xxx                      | uuu                             |

| 89h  | TRISE  | IBF   | OBF   | IBOV  | PSPMODE | _     | PORTE Data Direction bits |       | 0000 -111 | 0000 -111                |                                 |

| 9Fh  | ADCON1 | —     | _     |       | _       | _     | PCFG2                     | PCFG1 | PCFG0     | 000                      | 000                             |

Legend: x = unknown, u = unchanged, - = unimplemented, read as '0'. Shaded cells are not used by PORTE.

# REGISTER 11-2: ADCON1 REGISTER (ADDRESS 9Fh)

| U-0   | U-0 | U-0 | U-0 | U-0 | R/W-0 | R/W-0 | R/W-0 |

|-------|-----|-----|-----|-----|-------|-------|-------|

| _     | —   |     | —   |     | PCFG2 | PCFG1 | PCFG0 |

| bit 7 |     |     |     |     |       |       | bit 0 |

bit 7-3 Unimplemented: Read as '0'

bit 2-0 PCFG2:PCFG0: A/D Port Configuration Control bits

| PCFG2:PCFG0 | RA0 | RA1 | RA2 | RA5 | RA3  | RE0 <sup>(1)</sup> | RE1 <sup>(1)</sup> | RE2 <sup>(1)</sup> | VREF |

|-------------|-----|-----|-----|-----|------|--------------------|--------------------|--------------------|------|

| 000         | Α   | Α   | Α   | Α   | Α    | Α                  | А                  | А                  | Vdd  |

| 001         | Α   | Α   | Α   | Α   | VREF | Α                  | А                  | Α                  | RA3  |

| 010         | Α   | Α   | Α   | Α   | Α    | D                  | D                  | D                  | Vdd  |

| 011         | Α   | Α   | Α   | Α   | VREF | D                  | D                  | D                  | RA3  |

| 100         | Α   | Α   | D   | D   | Α    | D                  | D                  | D                  | Vdd  |

| 101         | Α   | Α   | D   | D   | VREF | D                  | D                  | D                  | RA3  |

| 11x         | D   | D   | D   | D   | D    | D                  | D                  | D                  | Vdd  |

A = Analog input

D = Digital I/O

Note 1: RE0, RE1 and RE2 are implemented on the PIC16F74/77 only.

| Legend:                  |                  |                      |                    |

|--------------------------|------------------|----------------------|--------------------|

| R = Readable bit         | W = Writable bit | U = Unimplemented    | bit, read as '0'   |

| - n = Value at POR reset | '1' = Bit is set | '0' = Bit is cleared | x = Bit is unknown |

# **12.2 Oscillator Configurations**

#### 12.2.1 OSCILLATOR TYPES

The PIC16F7X can be operated in four different oscillator modes. The user can program two configuration bits (FOSC1 and FOSC0) to select one of these four modes:

- LP Low Power Crystal

- XT Crystal/Resonator

- HS High Speed Crystal/Resonator

- RC Resistor/Capacitor

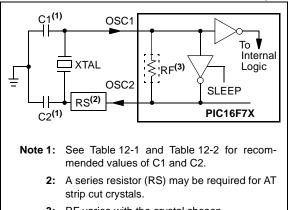

# 12.2.2 CRYSTAL OSCILLATOR/CERAMIC RESONATORS

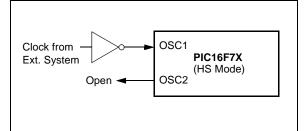

In XT, LP or HS modes, a crystal or ceramic resonator is connected to the OSC1/CLKIN and OSC2/CLKOUT pins to establish oscillation (Figure 12-1). The PIC16F7X oscillator design requires the use of a parallel cut crystal. Use of a series cut crystal may give a frequency out of the crystal manufacturers specifications. When in HS mode, the device can accept an external clock source to drive the OSC1/CLKIN pin (Figure 12-2). See Figure 15-1 or Figure 15-2 (depending on the part number and VDD range) for valid external clock frequencies.

#### FIGURE 12-1: CRYSTAL/CERAMIC RESONATOR OPERATION (HS, XT OR LP OSC CONFIGURATION)

3: RF varies with the crystal chosen.

#### FIGURE 12-2:

#### EXTERNAL CLOCK INPUT OPERATION (HS OSC CONFIGURATION)

#### TABLE 12-1: CERAMIC RESONATORS (FOR DESIGN GUIDANCE ONLY)

| 1    | Typical Capacitor Values Used: |       |       |  |  |  |  |  |  |

|------|--------------------------------|-------|-------|--|--|--|--|--|--|

| Mode | Mode Freq OSC1 OSC2            |       |       |  |  |  |  |  |  |

| XT   | 455 kHz                        | 56 pF | 56 pF |  |  |  |  |  |  |

|      | 2.0 MHz                        | 47 pF | 47 pF |  |  |  |  |  |  |

|      | 4.0 MHz                        | 33 pF | 33 pF |  |  |  |  |  |  |

| HS   | 8.0 MHz                        | 27 pF | 27 pF |  |  |  |  |  |  |

|      | 16.0 MHz                       | 22 pF | 22 pF |  |  |  |  |  |  |

Capacitor values are for design guidance only.

These capacitors were tested with the resonators listed below for basic start-up and operation. These values were not optimized.

Different capacitor values may be required to produce acceptable oscillator operation. The user should test the performance of the oscillator over the expected VDD and temperature range for the application.

See the notes at the bottom of page 92 for additional information.

| Resonators Used: |                        |

|------------------|------------------------|

| 455 kHz          | Panasonic EFO-A455K04B |

| 2.0 MHz          | Murata Erie CSA2.00MG  |

| 4.0 MHz          | Murata Erie CSA4.00MG  |

| 8.0 MHz          | Murata Erie CSA8.00MT  |

| 16.0 MHz         | Murata Erie CSA16.00MX |

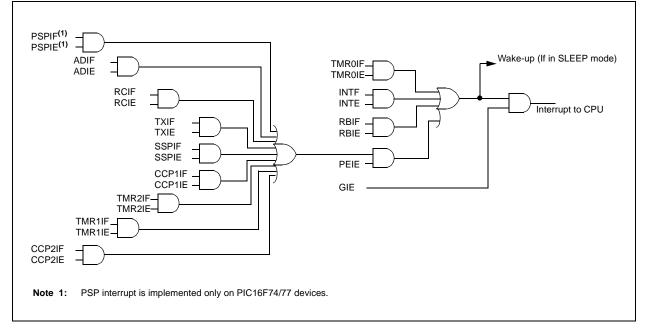

### 12.11 Interrupts

The PIC16F7X family has up to 12 sources of interrupt. The interrupt control register (INTCON) records individual interrupt requests in flag bits. It also has individual and global interrupt enable bits.

| Note: | Individual interrupt flag bits are set, regard- |

|-------|-------------------------------------------------|

|       | less of the status of their corresponding       |

|       | mask bit or the GIE bit.                        |

A global interrupt enable bit, GIE (INTCON<7>) enables (if set) all unmasked interrupts, or disables (if cleared) all interrupts. When bit GIE is enabled and an interrupt's flag bit and mask bit are set, the interrupt will vector immediately. Individual interrupts can be disabled through their corresponding enable bits in various registers. Individual interrupt bits are set, regardless of the status of the GIE bit. The GIE bit is cleared on RESET.

The "return from interrupt" instruction, RETFIE, exits the interrupt routine, as well as sets the GIE bit, which re-enables interrupts.

The RB0/INT pin interrupt, the RB port change interrupt and the TMR0 overflow interrupt flags are contained in the INTCON register.

The peripheral interrupt flags are contained in the Special Function Registers, PIR1 and PIR2. The corresponding interrupt enable bits are contained in Special Function Registers, PIE1 and PIE2, and the peripheral interrupt enable bit is contained in Special Function Register, INTCON.

When an interrupt is responded to, the GIE bit is cleared to disable any further interrupt, the return address is pushed onto the stack and the PC is loaded with 0004h. Once in the Interrupt Service Routine, the source(s) of the interrupt can be determined by polling the interrupt flag bits. The interrupt flag bit(s) must be cleared in software before re-enabling interrupts to avoid recursive interrupts.

For external interrupt events, such as the INT pin or PORTB change interrupt, the interrupt latency will be three or four instruction cycles. The exact latency depends when the interrupt event occurs, relative to the current Q cycle. The latency is the same for one or two-cycle instructions. Individual interrupt flag bits are set, regardless of the status of their corresponding mask bit, PEIE bit, or the GIE bit.

#### FIGURE 12-10: INTERRUPT LOGIC

#### 12.11.1 INT INTERRUPT

External interrupt on the RB0/INT pin is edge triggered, either rising, if bit INTEDG (OPTION\_REG<6>) is set, or falling, if the INTEDG bit is clear. When a valid edge appears on the RB0/INT pin, flag bit INTF (INTCON<1>) is set. This interrupt can be disabled by clearing enable bit INTE (INTCON<4>). Flag bit INTF must be cleared in software in the Interrupt Service Routine before re-enabling this interrupt. The INT interrupt can wake-up the processor from SLEEP, if bit INTE was set prior to going into SLEEP. The status of global interrupt enable bit GIE decides whether or not the processor branches to the interrupt vector following wakeup. See Section 12.14 for details on SLEEP mode.

#### 12.11.2 TMR0 INTERRUPT

An overflow (FFh  $\rightarrow$  00h) in the TMR0 register will set flag bit TMR0IF (INTCON<2>). The interrupt can be enabled/disabled by setting/clearing enable bit TMR0IE (INTCON<5>). (Section 5.0)

#### 12.11.3 PORTB INTCON CHANGE

An input change on PORTB<7:4> sets flag bit RBIF (INTCON<0>). The interrupt can be enabled/disabled by setting/clearing enable bit RBIE (INTCON<4>), see Section 4.2.

## 12.12 Context Saving During Interrupts

During an interrupt, only the return PC value is saved on the stack. Typically, users may wish to save key registers during an interrupt (i.e., W, PCLATH and STA-TUS registers). This will have to be implemented in software, as shown in Example 12-1.

For the PIC16F73/74 devices, the register W\_TEMP must be defined in both banks 0 and 1 and must be defined at the same offset from the bank base address (i.e., If W\_TEMP is defined at 20h in bank 0, it must also be defined at A0h in bank 1.). The registers, PCLATH\_TEMP and STATUS\_TEMP, are only defined in bank 0.

Since the upper 16 bytes of each bank are common in the PIC16F76/77 devices, temporary holding registers W\_TEMP, STATUS\_TEMP and PCLATH\_TEMP should be placed in here. These 16 locations don't require banking and, therefore, make it easier for context save and restore. The same code shown in Example 12-1 can be used.

|       | LIZ-I. SAVING S          | TATUS, W, AND FCEATH REGISTERS IN RAM                   |

|-------|--------------------------|---------------------------------------------------------|

| MOVWF | W_TEMP                   | ;Copy W to TEMP register                                |

| SWAPF | STATUS,W                 | ;Swap status to be saved into W                         |

| CLRF  | STATUS                   | ;bank 0, regardless of current bank, Clears IRP,RP1,RP0 |

| MOVWF | STATUS_TEMP              | ;Save status to bank zero STATUS_TEMP register          |

| MOVF  | PCLATH, W                | ;Only required if using pages 1, 2 and/or 3             |

| MOVWF | F PCLATH_TEMP            | ;Save PCLATH into W                                     |

| CLRF  | PCLATH                   | ;Page zero, regardless of current page                  |

| :     |                          |                                                         |

| :(ISR | 2)                       | ;Insert user code here                                  |

| :     |                          |                                                         |

| MOVF  | PCLATH_TEMP, W           | ;Restore PCLATH                                         |

| MOVWF | PCLATH                   | ;Move W into PCLATH                                     |

| SWAPF | <pre>STATUS_TEMP,W</pre> | ;Swap STATUS_TEMP register into W                       |

|       |                          | ;(sets bank to original state)                          |

| MOVWF | r status                 | ;Move W into STATUS register                            |

| SWAPF | F W_TEMP,F               | ;Swap W_TEMP                                            |

| SWAPF | F W_TEMP,W               | ;Swap W_TEMP into W                                     |

|       |                          |                                                         |

#### EXAMPLE 12-1: SAVING STATUS, W, AND PCLATH REGISTERS IN RAM

# 13.2 Instruction Descriptions

| ADDLW            | Add Literal and W                                                                                                          |

|------------------|----------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [label] ADDLW k                                                                                                            |

| Operands:        | $0 \le k \le 255$                                                                                                          |

| Operation:       | $(W) + k \to (W)$                                                                                                          |

| Status Affected: | C, DC, Z                                                                                                                   |

| Description:     | The contents of the W register<br>are added to the eight-bit literal 'k'<br>and the result is placed in the W<br>register. |

| ADDWF            | Add W and f                                                                                                                                                                    |

|------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [label] ADDWF f,d                                                                                                                                                              |

| Operands:        | $0 \le f \le 127$<br>$d \in [0,1]$                                                                                                                                             |

| Operation:       | (W) + (f) $\rightarrow$ (destination)                                                                                                                                          |

| Status Affected: | C, DC, Z                                                                                                                                                                       |

| Description:     | Add the contents of the W register<br>with register 'f'. If 'd' is 0, the result<br>is stored in the W register. If 'd' is<br>1, the result is stored back in<br>register 'f'. |

| BCF              | Bit Clear f                                                         |

|------------------|---------------------------------------------------------------------|

| Syntax:          | [ <i>label</i> ] BCF f,b                                            |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ 0 \leq b \leq 7 \end{array}$ |

| Operation:       | $0 \rightarrow (f < b >)$                                           |

| Status Affected: | None                                                                |

| Description:     | Bit 'b' in register 'f' is cleared.                                 |

| BSF              | Bit Set f                                                           |

|------------------|---------------------------------------------------------------------|

| Syntax:          | [ <i>label</i> ] BSF f,b                                            |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ 0 \leq b \leq 7 \end{array}$ |

| Operation:       | $1 \rightarrow (f < b >)$                                           |

| Status Affected: | None                                                                |

| Description:     | Bit 'b' in register 'f' is set.                                     |

| ANDLW            | AND Literal with W                                                                                                     |

|------------------|------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [ <i>label</i> ] ANDLW k                                                                                               |

| Operands:        | $0 \le k \le 255$                                                                                                      |

| Operation:       | (W) .AND. (k) $\rightarrow$ (W)                                                                                        |

| Status Affected: | Z                                                                                                                      |

| Description:     | The contents of W register are<br>AND'ed with the eight-bit literal<br>'k'. The result is placed in the W<br>register. |

| BTFSS            | Bit Test f, Skip if Set                                                                                                                                                                                        |

|------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [ label ] BTFSS f,b                                                                                                                                                                                            |

| Operands:        | $0 \le f \le 127$<br>$0 \le b < 7$                                                                                                                                                                             |

| Operation:       | skip if (f <b>) = 1</b>                                                                                                                                                                                        |

| Status Affected: | None                                                                                                                                                                                                           |

| Description:     | If bit 'b' in register 'f' is '0', the next<br>instruction is executed.<br>If bit 'b' is '1', then the next instruc-<br>tion is discarded and a NOP is<br>executed instead, making this a<br>2TcY instruction. |

| ANDWF            | AND W with f                                                                                                                                                |

|------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [label] ANDWF f,d                                                                                                                                           |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ d \in \left[ 0,1 \right] \end{array}$                                                                                |

| Operation:       | (W) .AND. (f) $\rightarrow$ (destination)                                                                                                                   |

| Status Affected: | Z                                                                                                                                                           |

| Description:     | AND the W register with register<br>'f'. If 'd' is 0, the result is stored in<br>the W register. If 'd' is 1, the result<br>is stored back in register 'f'. |

| BTFSC            | Bit Test, Skip if Clear                                                                                                                                                                                        |

|------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [ label ] BTFSC f,b                                                                                                                                                                                            |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ 0 \leq b \leq 7 \end{array}$                                                                                                                                            |

| Operation:       | skip if $(f < b >) = 0$                                                                                                                                                                                        |

| Status Affected: | None                                                                                                                                                                                                           |

| Description:     | If bit 'b' in register 'f' is '1', the next instruction is executed.<br>If bit 'b', in register 'f', is '0', the next instruction is discarded, and a NOP is executed instead, making this a 2TCY instruction. |

| SWAPF            | Swap Nibbles in f                                                                                                                                                  |

|------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [label] SWAPF f,d                                                                                                                                                  |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ d \in \ [0,1] \end{array}$                                                                                                  |

| Operation:       | $(f<3:0>) \rightarrow (destination<7:4>), (f<7:4>) \rightarrow (destination<3:0>)$                                                                                 |

| Status Affected: | None                                                                                                                                                               |

| Description:     | The upper and lower nibbles of register 'f' are exchanged. If 'd' is 0, the result is placed in the W register. If 'd' is 1, the result is placed in register 'f'. |

| XORWF            | Exclusive OR W with f                                                                                                                                                       |

|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [label] XORWF f,d                                                                                                                                                           |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ d \in \left[0,1\right] \end{array}$                                                                                                  |

| Operation:       | (W) .XOR. (f) $\rightarrow$ (destination)                                                                                                                                   |

| Status Affected: | Z                                                                                                                                                                           |

| Description:     | Exclusive OR the contents of the W register with register 'f'. If 'd' is 0, the result is stored in the W register. If 'd' is 1, the result is stored back in register 'f'. |

| XORLW            | Exclusive OR Literal with W                                                                                                |  |  |

|------------------|----------------------------------------------------------------------------------------------------------------------------|--|--|

| Syntax:          | [ <i>label</i> ] XORLW k                                                                                                   |  |  |

| Operands:        | $0 \le k \le 255$                                                                                                          |  |  |

| Operation:       | (W) .XOR. $k \rightarrow (W)$                                                                                              |  |  |

| Status Affected: | Z                                                                                                                          |  |  |

| Description:     | The contents of the W register<br>are XOR'ed with the eight-bit<br>literal 'k'. The result is placed in<br>the W register. |  |  |

# 14.0 DEVELOPMENT SUPPORT

The PICmicro<sup>®</sup> microcontrollers are supported with a full range of hardware and software development tools:

- Integrated Development Environment

- MPLAB® IDE Software

- Assemblers/Compilers/Linkers

- MPASM<sup>™</sup> Assembler

- MPLAB C17 and MPLAB C18 C Compilers

- MPLINK<sup>™</sup> Object Linker/ MPLIB<sup>™</sup> Object Librarian

- Simulators

- MPLAB SIM Software Simulator

- Emulators

- MPLAB ICE 2000 In-Circuit Emulator

- ICEPIC™ In-Circuit Emulator

- In-Circuit Debugger

- MPLAB ICD

- Device Programmers

- PRO MATE<sup>®</sup> II Universal Device Programmer

- PICSTART<sup>®</sup> Plus Entry-Level Development Programmer

- Low Cost Demonstration Boards

- PICDEM<sup>™</sup>1 Demonstration Board

- PICDEM 2 Demonstration Board

- PICDEM 3 Demonstration Board

- PICDEM 17 Demonstration Board

- KEELOQ® Demonstration Board

#### 14.1 MPLAB Integrated Development Environment Software

The MPLAB IDE software brings an ease of software development previously unseen in the 8-bit microcontroller market. The MPLAB IDE is a Windows<sup>®</sup>-based application that contains:

- · An interface to debugging tools

- simulator

- programmer (sold separately)

- emulator (sold separately)

- in-circuit debugger (sold separately)

- · A full-featured editor

- · A project manager

- Customizable toolbar and key mapping

- · A status bar

- On-line help

The MPLAB IDE allows you to:

- Edit your source files (either assembly or 'C')

- One touch assemble (or compile) and download to PICmicro emulator and simulator tools (automatically updates all project information)

- Debug using:

- source files

- absolute listing file

- machine code

The ability to use MPLAB IDE with multiple debugging tools allows users to easily switch from the costeffective simulator to a full-featured emulator with minimal retraining.

#### 14.2 MPASM Assembler

The MPASM assembler is a full-featured universal macro assembler for all PICmicro MCU's.

The MPASM assembler has a command line interface and a Windows shell. It can be used as a stand-alone application on a Windows 3.x or greater system, or it can be used through MPLAB IDE. The MPASM assembler generates relocatable object files for the MPLINK object linker, Intel<sup>®</sup> standard HEX files, MAP files to detail memory usage and symbol reference, an absolute LST file that contains source lines and generated machine code, and a COD file for debugging.

The MPASM assembler features include:

- Integration into MPLAB IDE projects.

- User-defined macros to streamline assembly code.

- Conditional assembly for multi-purpose source files.

- Directives that allow complete control over the assembly process.

### 14.3 MPLAB C17 and MPLAB C18 C Compilers

The MPLAB C17 and MPLAB C18 Code Development Systems are complete ANSI 'C' compilers for Microchip's PIC17CXXX and PIC18CXXX family of microcontrollers, respectively. These compilers provide powerful integration capabilities and ease of use not found with other compilers.

For easier source level debugging, the compilers provide symbol information that is compatible with the MPLAB IDE memory display.

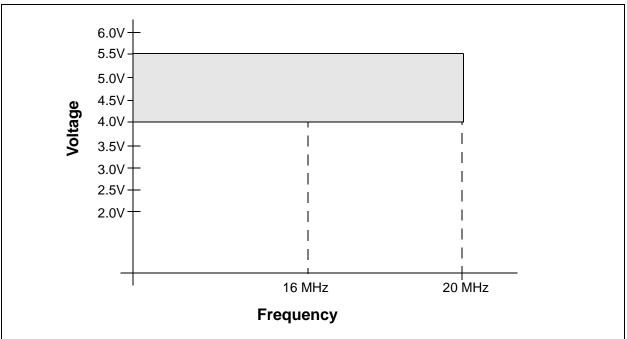

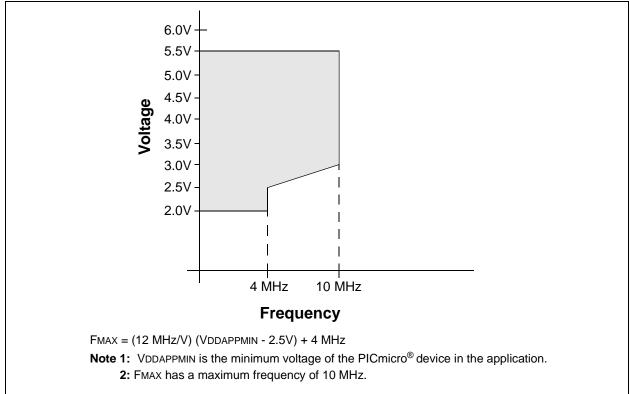

### FIGURE 15-2: PIC16LF7X VOLTAGE-FREQUENCY GRAPH

# 15.2 DC Characteristics: PIC16F73/74/76/77 (Industrial, Extended) PIC16LF73/74/76/77 (Industrial) (Continued)

| DC CHA       | ARACT | ERISTICS                              | Standard<br>Operating                                                          |      |     | -40°0 | <b>s (unless otherwise stated)</b><br>$C \le TA \le +85^{\circ}C$ for industrial<br>$C \le TA \le +125^{\circ}C$ for extended |  |

|--------------|-------|---------------------------------------|--------------------------------------------------------------------------------|------|-----|-------|-------------------------------------------------------------------------------------------------------------------------------|--|

|              |       |                                       | Operating voltage VDD range as described in DC Specification,<br>Section 15.1. |      |     |       |                                                                                                                               |  |

| Param<br>No. | Sym   | Characteristic                        | Min                                                                            | Тур† | Max | Units | Conditions                                                                                                                    |  |

|              | Vol   | Output Low Voltage                    |                                                                                |      |     |       |                                                                                                                               |  |

| D080         |       | I/O ports                             |                                                                                | —    | 0.6 | V     | IOL = 8.5 mA, VDD = 4.5V,<br>-40°C to +125°C                                                                                  |  |

| D083         |       | OSC2/CLKOUT (RC osc config)           | —                                                                              | —    | 0.6 | V     | Io∟ = 1.6 mA, VDD = 4.5V,<br>-40°C to +125°C                                                                                  |  |

|              |       |                                       |                                                                                | —    | 0.6 | V     | IOL = 1.2 mA, VDD = 4.5V,<br>-40°C to +125°C                                                                                  |  |

|              | Vон   | Output High Voltage                   |                                                                                |      |     |       |                                                                                                                               |  |

| D090         |       | I/O ports (Note 3)                    | Vdd - 0.7                                                                      | _    | —   | V     | IOH = -3.0 mA, VDD = 4.5V,<br>-40°С to +125°С                                                                                 |  |

| D092         |       | OSC2/CLKOUT (RC osc config)           | Vdd - 0.7                                                                      | —    | —   | V     | ІОН = -1.3 mA, VDD = 4.5V,<br>-40°С to +125°С                                                                                 |  |

|              |       |                                       | Vdd - 0.7                                                                      | —    | —   | V     | IOH = -1.0 mA, VDD = 4.5V,<br>-40°С to +125°С                                                                                 |  |

| D150*        | Vod   | Open Drain High Voltage               |                                                                                | _    | 12  | V     | RA4 pin                                                                                                                       |  |

|              |       | Capacitive Loading Specs on (         | Dutput Pir                                                                     | IS   |     |       |                                                                                                                               |  |

| D100         | Cosc2 | OSC2 pin                              | _                                                                              | —    | 15  | pF    | In XT, HS and LP modes when<br>external clock is used to drive<br>OSC1                                                        |  |

| D101         | Сю    | All I/O pins and OSC2<br>(in RC mode) | —                                                                              | —    | 50  | pF    |                                                                                                                               |  |

| D102         | Св    | SCL, SDA in I <sup>2</sup> C mode     | —                                                                              | —    | 400 | pF    |                                                                                                                               |  |

|              |       | Program FLASH Memory                  |                                                                                | I I  |     |       | 1                                                                                                                             |  |

| D130         | ЕΡ    | Endurance                             | 100                                                                            | 1000 | _   | E/W   | 25°C at 5V                                                                                                                    |  |

| D131         | Vpr   | VDD for Read                          | 2.0                                                                            | —    | 5.5 | V     |                                                                                                                               |  |

\* These parameters are characterized but not tested.

† Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

**Note 1:** In RC oscillator configuration, the OSC1/CLKIN pin is a Schmitt Trigger input. It is not recommended that the PIC16F7X be driven with external clock in RC mode.

2: The leakage current on the MCLR pin is strongly dependent on the applied voltage level. The specified levels represent normal operating conditions. Higher leakage current may be measured at different input voltages.

3: Negative current is defined as current sourced by the pin.

NOTES:

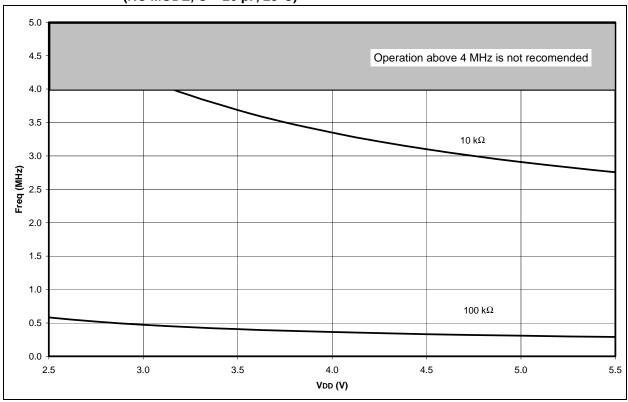

### FIGURE 16-7: AVERAGE FOSC vs. VDD FOR VARIOUS VALUES OF R (RC MODE, C = 20 pF, 25°C)

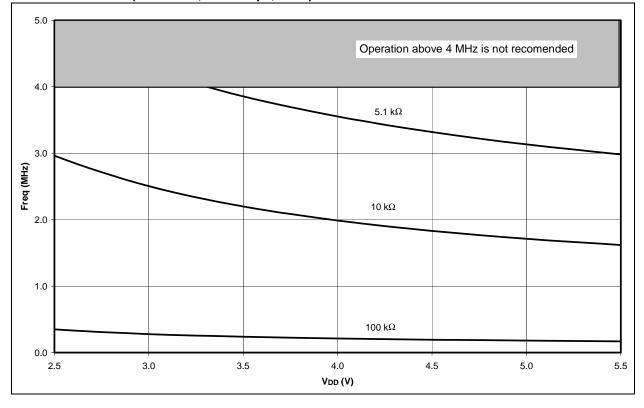

FIGURE 16-8: AVERAGE Fosc vs. VDD FOR VARIOUS VALUES OF R (RC MODE, C = 100 pF, 25°C)

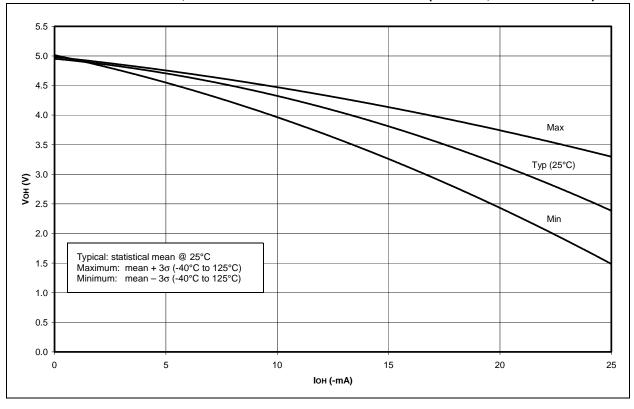

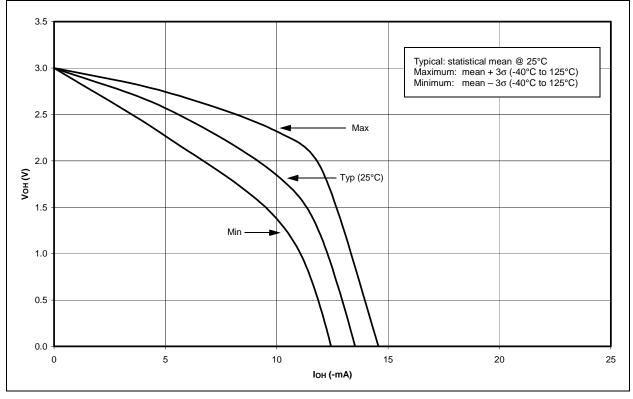

FIGURE 16-15: TYPICAL, MINIMUM AND MAXIMUM VOH vs. IOH (VDD = 5V, -40°C TO 125°C)

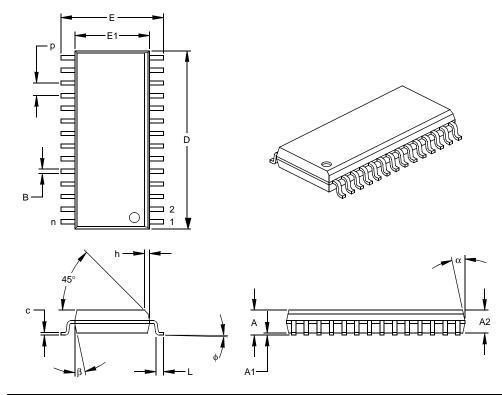

28-Lead Plastic Small Outline (SO) - Wide, 300 mil (SOIC)

| Units                    |          |      | INCHES* |      | MILLIMETERS |       |       |

|--------------------------|----------|------|---------|------|-------------|-------|-------|

| Dimension                | n Limits | MIN  | NOM     | MAX  | MIN         | NOM   | MAX   |

| Number of Pins           | n        |      | 28      |      |             | 28    |       |

| Pitch                    | р        |      | .050    |      |             | 1.27  |       |

| Overall Height           | А        | .093 | .099    | .104 | 2.36        | 2.50  | 2.64  |

| Molded Package Thickness | A2       | .088 | .091    | .094 | 2.24        | 2.31  | 2.39  |

| Standoff §               | A1       | .004 | .008    | .012 | 0.10        | 0.20  | 0.30  |

| Overall Width            | Е        | .394 | .407    | .420 | 10.01       | 10.34 | 10.67 |

| Molded Package Width     | E1       | .288 | .295    | .299 | 7.32        | 7.49  | 7.59  |

| Overall Length           | D        | .695 | .704    | .712 | 17.65       | 17.87 | 18.08 |

| Chamfer Distance         | h        | .010 | .020    | .029 | 0.25        | 0.50  | 0.74  |

| Foot Length              | L        | .016 | .033    | .050 | 0.41        | 0.84  | 1.27  |

| Foot Angle Top           | φ        | 0    | 4       | 8    | 0           | 4     | 8     |

| Lead Thickness           | С        | .009 | .011    | .013 | 0.23        | 0.28  | 0.33  |

| Lead Width               | В        | .014 | .017    | .020 | 0.36        | 0.42  | 0.51  |

| Mold Draft Angle Top     | α        | 0    | 12      | 15   | 0           | 12    | 15    |

| Mold Draft Angle Bottom  | β        | 0    | 12      | 15   | 0           | 12    | 15    |

\* Controlling Parameter

§ Significant Characteristic

Notes:

Dimensions D and E1 do not include mold flash or protrusions. Mold flash or protrusions shall not exceed .010" (0.254mm) per side.

JEDEC Equivalent: MS-013 Drawing No. C04-052

5

| USART Synchronous Transmission       |    |

|--------------------------------------|----|

| (Through TXEN)                       |    |

| Wake-up from SLEEP via Interrupt1    |    |

| Watchdog Timer1                      |    |

| Timing Parameter Symbology1          | 25 |

| Timing Requirements                  |    |

| Capture/Compare/PWM (CCP1 and CCP2)1 |    |

| CLKOUT and I/O1                      |    |

| External Clock1                      | -  |

| I <sup>2</sup> C Bus Data1           | 36 |

| I2C Bus START/STOP Bits1             | 35 |

| Parallel Slave Port1                 | 31 |

| RESET, Watchdog Timer, Oscillator    |    |

| Start-up Timer, Power-up Timer       |    |

| and Brown-out Reset1                 | 28 |

| SPI Mode1                            | 34 |

| Timer0 and Timer1 External Clock1    | 29 |

| USART Synchronous Receive1           |    |

| USART Synchronous Transmission1      |    |

| TMR1CS bit                           |    |

| TMR10N bit                           | 47 |

| TMR2ON bit                           |    |

| TOUTPS<3:0> bits                     | -  |

| TRISA Register                       | -  |

| TRISB Register                       |    |

| TRISC Register                       |    |

| TRISD Register                       |    |

| TRISE Register                       |    |

| IBF Bit                              |    |

| IBOV Bit                             |    |

| PSPMODE bit                          |    |

| TXSTA Register                       | 01 |

| SYNC bit                             | 69 |

| TRMT bit                             |    |

| TX9 bit                              |    |

| TX9 bit                              |    |

| TXEN bit                             |    |

|                                      | 09 |

| U                                    |    |

| UA6                                | 60         |

|------------------------------------|------------|

| Universal Synchronous Asynchronous |            |

| Receiver Transmitter. See USART    |            |

| Update Address bit, UA6            | 60         |

| USART6                             | ;9         |

| Asynchronous Mode7                 | '3         |

| Asynchronous Receiver7             | '5         |

| Asynchronous Reception7            | '6         |

| Associated Registers7              | <i>'</i> 6 |

| Asynchronous Transmission          |            |

| Associated Registers7              | <b>'</b> 4 |

| Asynchronous Transmitter7          | '3         |

| Baud Rate Generator (BRG)71               |

|-------------------------------------------|

| Baud Rate Formula                         |

| Baud Rates, Asynchronous Mode             |

| (BRGH = 0)                                |

| Baud Rates, Asynchronous Mode             |

| (BRGH = 1)                                |

| Sampling71                                |

| Mode Select (SYNC Bit) 69                 |

| Overrun Error (OERR Bit)                  |

| RC6/TX/CK Pin9, 11                        |

| RC7/RX/DT Pin9, 11                        |

| Serial Port Enable (SPEN Bit)             |

| Single Receive Enable (SREN Bit)70        |

| Synchronous Master Mode77                 |

| Synchronous Master Reception              |

| Associated Registers 80                   |

| Synchronous Master Transmission           |

| Associated Registers                      |

| Synchronous Slave Mode 80                 |

| Synchronous Slave Reception               |

| Associated Registers 81                   |

| Synchronous Slave Transmission            |

| Associated Registers81                    |

| Transmit Data, 9th Bit (TX9D)69           |

| Transmit Enable (TXEN bit)69              |

| Transmit Enable, Nine-bit (TX9 bit)       |

| Transmit Shift Register Status (TRMT bit) |

#### W

| Wake-up from SLEEP                |            |

|-----------------------------------|------------|

| Interrupts                        |            |

| MCLR Reset                        |            |

| WDT Reset                         |            |

| Wake-up Using Interrupts          | 102        |

| Watchdog Timer (WDT)              |            |

| Associated Registers              | 101        |

| Enable (WDTE Bit)                 | 101        |

| Postscaler. See Postscaler, WDT   |            |

| Programming Considerations        | 101        |

| RC Oscillator                     | 101        |

| Time-out Period                   | 101        |

| WDT Reset, Normal Operation       | 93, 95, 96 |

| WDT Reset, SLEEP                  | 93, 95, 96 |

| WCOL bit                          |            |

| Write Collision Detect bit (WCOL) | 61         |

| WWW, On-Line Support              |            |

# PIC16F7X PRODUCT IDENTIFICATION SYSTEM

To order or obtain information, e.g., on pricing or delivery, refer to the factory or the listed sales office.

| PART NO.          | X /XX XXX<br>Temperature Package Pattern                                                                                                                                                      | Examples:<br>a) PIC16F77-I/P 301 = Industrial temp., PDIP                                                                                                                                                                       |

|-------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Device            | Range<br>PIC16F7X <sup>(1)</sup> , PIC16F7XT <sup>(1)</sup> ; VDD range 4.0V to 5.5V<br>PIC16LF7X <sup>(1)</sup> , PIC16LF7XT <sup>(1)</sup> ; VDD range 2.0V to 5.5V                         | <ul> <li>package, normal VDD limits, QTP pattern #301.</li> <li>b) PIC16LF76-I/SO = Industrial temp., SOIC package, Extended VDD limits.</li> <li>c) PIC16F74-E/P = Extended temp., PDIP package, normal VDD limits.</li> </ul> |

| Temperature Range | $ \begin{array}{rcl} I &=& -40^{\circ}\text{C to} & +85^{\circ}\text{C} & (\text{Industrial}) \\ \text{E} &=& -40^{\circ}\text{C to} & +125^{\circ}\text{C} & (\text{Extended}) \end{array} $ | Note 1: F = CMOS FLASH<br>LF = Low Power CMOS FLASH                                                                                                                                                                             |

| Package           | $\begin{array}{llllllllllllllllllllllllllllllllllll$                                                                                                                                          | 2: T = in tape and reel - SOIC, PLCC,<br>SSOP, TQFP packages only.                                                                                                                                                              |