Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                                  |

|----------------------------|-----------------------------------------------------------------------------------------|

| Core Processor             | ARM® Cortex®-M3                                                                         |

| Core Size                  | 32-Bit Single-Core                                                                      |

| Speed                      | 120MHz                                                                                  |

| Connectivity               | CANbus, Ethernet, I <sup>2</sup> C, IrDA, LINbus, Memory Card, SPI, UART/USART, USB OTG |

| Peripherals                | Brown-out Detect/Reset, DMA, I <sup>2</sup> S, LCD, POR, PWM, WDT                       |

| Number of I/O              | 140                                                                                     |

| Program Memory Size        | 512KB (512K x 8)                                                                        |

| Program Memory Type        | FLASH                                                                                   |

| EEPROM Size                | -                                                                                       |

| RAM Size                   | 132K x 8                                                                                |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                                             |

| Data Converters            | A/D 24x12b; D/A 2x12b                                                                   |

| Oscillator Type            | Internal                                                                                |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                       |

| Mounting Type              | Surface Mount                                                                           |

| Package / Case             | 201-UFBGA                                                                               |

| Supplier Device Package    | 176+25UFBGA (10x10)                                                                     |

| Purchase URL               | https://www.e-xfl.com/product-detail/stmicroelectronics/stm32f217ieh6                   |

|                            |                                                                                         |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| 9 | Revi | sion history                    |

|---|------|---------------------------------|

| 8 | Orde | ering information               |

|   | 7.6  | Thermal characteristics         |

|   | 7.5  | UFBGA176+25 package information |

|   | 7.4  | LQFP176 package information 160 |

| Р                                | Peripherals              | STM32    | F215Rx | STM32 | 2F215Vx | STM32 | F215Zx | STM32                | 2F217Vx                 | STM32F217Zx |      | STM3 | 2F217lx |

|----------------------------------|--------------------------|----------|--------|-------|---------|-------|--------|----------------------|-------------------------|-------------|------|------|---------|

| Flash memory in Kb               |                          | 512      | 1024   | 512   | 1024    | 512   | 1024   | 512                  | 1024                    | 512         | 1024 | 512  | 1024    |

| System                           |                          | 512      | 1024   | 512   | 1024    | 512   |        | 8(112+16)            | 1024                    | 512         | 1024 | 512  | 1024    |

| SRAM in Kbytes Backup            |                          |          | 1      | 1     | 4       |       | 1      |                      | 4                       |             | 4    |      | 4       |

| FSMC memory cont                 | -                        | N        |        |       | +       | •     | •      |                      | 4<br>Yes <sup>(1)</sup> |             | +    |      | +       |

| Ethernet <sup>(2)</sup>          |                          |          | 0      | l     | No      |       |        | 1                    | 162.                    |             | Yes  |      |         |

| Ellemet                          |                          |          |        |       | INU     |       |        | 10                   |                         |             | Tes  |      |         |

|                                  | General-purpose          |          |        |       |         |       |        | 10                   |                         |             |      |      |         |

|                                  | Advanced-control         |          |        |       |         |       |        | 2                    |                         |             |      |      |         |

| Timers                           | Basic                    |          | 2      |       |         |       |        |                      |                         |             |      |      |         |

|                                  | IWDG                     |          | Yes    |       |         |       |        |                      |                         |             |      |      |         |

|                                  | WWDG                     |          |        |       |         |       |        | Yes                  |                         |             |      |      |         |

| RTC                              |                          |          | Yes    |       |         |       |        |                      |                         |             |      |      |         |

| Random number ge                 | nerator                  |          |        |       |         |       |        | Yes                  |                         |             |      |      |         |

|                                  | SPI / (I <sup>2</sup> S) |          |        |       |         |       |        | 3/(2) <sup>(3)</sup> |                         |             |      |      |         |

|                                  | I <sup>2</sup> C         | 3        |        |       |         |       |        |                      |                         |             |      |      |         |

| Communication                    | USART<br>UART            | 4 2      |        |       |         |       |        |                      |                         |             |      |      |         |

| menaces                          | USB OTG FS               | Yes      |        |       |         |       |        |                      |                         |             |      |      |         |

|                                  | USB OTG HS               | Yes      |        |       |         |       |        |                      |                         |             |      |      |         |

|                                  | CAN                      | 2        |        |       |         |       |        |                      |                         |             |      |      |         |

| Camera interface <sup>(2)</sup>  | ·                        |          |        |       | No      |       |        |                      |                         |             | Yes  |      |         |

| Encryption                       |                          |          |        |       |         |       |        | Yes                  |                         |             |      |      |         |

| GPIOs                            |                          | 5        | 1      | 8     | 82      | 11    | 14     | 8                    | 32                      | 1           | 14   | 1    | 40      |

| SDIO                             |                          |          |        |       |         |       |        | Yes                  |                         |             |      |      |         |

| 12-bit ADC<br>Number of channels |                          |          |        |       |         |       |        | 3                    |                         |             |      |      |         |

|                                  |                          | 1        | 6      |       | 16      | 2     | 4      |                      | 16                      | 2           | 24   | :    | 24      |

| 12-bit DAC<br>Number of channels |                          | Yes<br>2 |        |       |         |       |        |                      |                         |             |      |      |         |

| Maximum CPU frequ                | uency                    | 120 MHz  |        |       |         |       |        |                      |                         |             |      |      |         |

| Operating voltage                |                          |          |        |       |         |       | 1.8    | V to 3.6 V           |                         |             |      |      |         |

#### Table 2. STM32F215xx and STM32F217xx: features and peripheral counts

577

15/10

STM32F21xxx

# 3.4 Embedded Flash memory

The STM32F21x devices embed a 128-bit wide Flash memory of 128 Kbytes, 256 Kbytes, 512 Kbytes, 768 Kbytes or 1 Mbyte available for storing programs and data.

The devices also feature 512 bytes of OTP memory that can be used to store critical user data such as Ethernet MAC addresses or cryptographic keys.

# 3.5 CRC (cyclic redundancy check) calculation unit

The CRC (cyclic redundancy check) calculation unit is used to get a CRC code from a 32-bit data word and a fixed generator polynomial.

Among other applications, CRC-based techniques are used to verify data transmission or storage integrity. In the scope of the EN/IEC 60335-1 standard, they offer a means of verifying the Flash memory integrity. The CRC calculation unit helps compute a software signature during runtime, to be compared with a reference signature generated at link-time and stored at a given memory location.

# 3.6 Embedded SRAM

All STM32F21x products embed:

- Up to 128 Kbytes of system SRAM accessed (read/write) at CPU clock speed with 0 wait states

- 4 Kbytes of backup SRAM.

The content of this area is protected against possible unwanted write accesses, and is retained in Standby or VBAT mode.

# 3.7 Multi-AHB bus matrix

The 32-bit multi-AHB bus matrix interconnects all the masters (CPU, DMAs, Ethernet, USB HS) and the slaves (Flash memory, RAM, FSMC, AHB and APB peripherals) and ensures a seamless and efficient operation even when several high-speed peripherals work simultaneously.

#### Pinouts and pin description

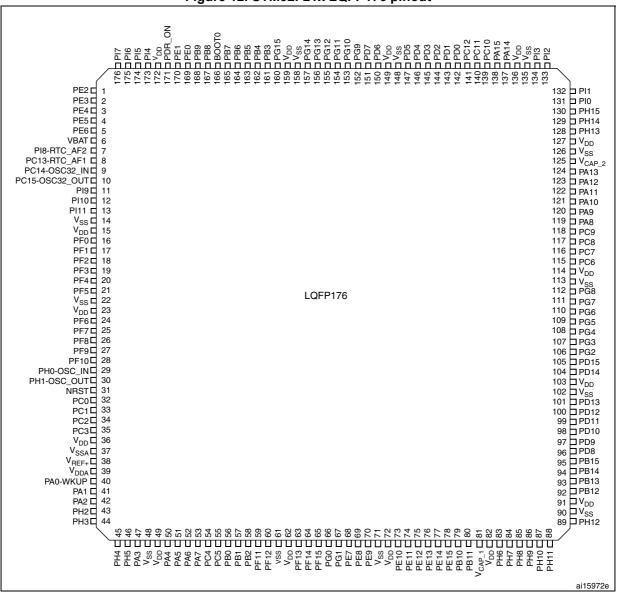

#### Figure 12. STM32F21x LQFP176 pinout

1. RFU means "reserved for future use". This pin can be tied to  $V_{\text{DD}}, V_{\text{SS}}$  or left unconnected.

2. The above figure shows the package top view.

LQFP100

1

2

3

LQFP64

-

-

-

|         |         |          |                                                      |                | •  |                         |                                                       |   |

|---------|---------|----------|------------------------------------------------------|----------------|----|-------------------------|-------------------------------------------------------|---|

| Pins    | 5       |          |                                                      |                |    |                         |                                                       |   |

| LQFP144 | LQFP176 | UFBGA176 | Pin name<br>(function after<br>reset) <sup>(1)</sup> | function after |    | Additional<br>functions |                                                       |   |

| 1       | 1       | A2       | PE2                                                  | I/O            | FT | -                       | TRACECLK, FSMC_A23,<br>ETH_MII_TXD3, EVENTOUT         | - |

| 2       | 2       | A1       | PE3                                                  | I/O            | FT | -                       | TRACED0, FSMC_A19,<br>EVENTOUT                        | - |

| 3       | 3       | B1       | PE4                                                  | I/O            | FT | -                       | TRACED1, FSMC_A20,<br>DCMI_D4/ EVENTOUT               | - |

| 4       | 4       | B2       | PE5                                                  | I/O            | FT | -                       | TRACED2, FSMC_A21,<br>TIM9_CH1, DCMI_D6,<br>EVENTOLIT | - |

Table 7. STM32F21x pin and ball definitions

| - | 4 | 4  | 4  | B2 | PE5                          | I/O | FT | -      | TIM9_CH1, DCMI_D6,<br>EVENTOUT                       | -                        |

|---|---|----|----|----|------------------------------|-----|----|--------|------------------------------------------------------|--------------------------|

| - | 5 | 5  | 5  | B3 | PE6                          | I/O | FT | -      | TRACED3, FSMC_A22,<br>TIM9_CH2, DCMI_D7,<br>EVENTOUT | -                        |

| 1 | 6 | 6  | 6  | C1 | V <sub>BAT</sub>             | S   | -  | -      | -                                                    | -                        |

| - | - | -  | 7  | D2 | PI8                          | I/O | FT | (2)(3) | EVENTOUT                                             | RTC_AF2                  |

| 2 | 7 | 7  | 8  | D1 | PC13                         | I/O | FT | (2)(3) | EVENTOUT                                             | RTC_AF1                  |

| 3 | 8 | 8  | 9  | E1 | PC14/OSC32_IN<br>(PC14)      | I/O | FT | (2)(3) | EVENTOUT                                             | OSC32_IN <sup>(4)</sup>  |

| 4 | 9 | 9  | 10 | F1 | PC15/<br>OSC32_OUT<br>(PC15) | I/O | FT | (2)(3) | EVENTOUT                                             | OSC32_OUT <sup>(4)</sup> |

| - | - | -  | 11 | D3 | PI9                          | I/O | FT | -      | CAN1_RX, EVENTOUT                                    | -                        |

| - | - | -  | 12 | E3 | PI10                         | I/O | FT | -      | ETH_MII_RX_ER, EVENTOUT                              | -                        |

| - | - | -  | 13 | E4 | PI11                         | I/O | FT | -      | OTG_HS_ULPI_DIR,<br>EVENTOUT                         | -                        |

| - | - | -  | 14 | F2 | V <sub>SS</sub>              | S   |    | -      | -                                                    | -                        |

| - | - | -  | 15 | F3 | V <sub>DD</sub>              | S   |    | -      | -                                                    | -                        |

| - | - | 10 | 16 | E2 | PF0                          | I/O | FT | -      | FSMC_A0, I2C2_SDA,<br>EVENTOUT                       | -                        |

| - | - | 11 | 17 | H3 | PF1                          | I/O | FT | -      | FSMC_A1, I2C2_SCL,<br>EVENTOUT                       | -                        |

| - | - | 12 | 18 | H2 | PF2                          | I/O | FT | -      | FSMC_A2, I2C2_SMBA,<br>EVENTOUT                      | -                        |

| - | - | 13 | 19 | J2 | PF3                          | I/O | FT | (4)    | FSMC_A3, EVENTOUT                                    | ADC3_IN9                 |

|        |         | Pins    | ;       |          |                                                      |          |                 |      |                                                                                              |                         |

|--------|---------|---------|---------|----------|------------------------------------------------------|----------|-----------------|------|----------------------------------------------------------------------------------------------|-------------------------|

| LQFP64 | LQFP100 | LQFP144 | LQFP176 | UFBGA176 | Pin name<br>(function after<br>reset) <sup>(1)</sup> | Pin type | I / O structure | Note | Alternate functions                                                                          | Additional<br>functions |

| 38     | 64      | 97      | 116     | G15      | PC7                                                  | I/O      | FT              | -    | I2S3_MCK,<br>TIM8_CH2,SDIO_D7,<br>USART6_RX,<br>DCMI_D1,TIM3_CH2,<br>EVENTOUT                | -                       |

| 39     | 65      | 98      | 117     | G14      | PC8                                                  | I/O      | FT              | -    | TIM8_CH3,SDIO_D0,<br>TIM3_CH3, USART6_CK,<br>DCMI_D2, EVENTOUT                               | -                       |

| 40     | 66      | 99      | 118     | F14      | PC9                                                  | I/O      | FT              | -    | I2S2_CKIN, I2S3_CKIN,<br>MCO2, TIM8_CH4,SDIO_D1,<br>I2C3_SDA, DCMI_D3,<br>TIM3_CH4, EVENTOUT | -                       |

| 41     | 67      | 100     | 119     | F15      | PA8                                                  | I/O      | FT              | -    | MCO1, USART1_CK,<br>TIM1_CH1, I2C3_SCL,<br>OTG_FS_SOF, EVENTOUT                              | -                       |

| 42     | 68      | 101     | 120     | E15      | PA9                                                  | I/O      | FT              | -    | USART1_TX, TIM1_CH2,<br>I2C3_SMBA, DCMI_D0,<br>EVENTOUT                                      | OTG_FS_<br>VBUS         |

| 43     | 69      | 102     | 121     | D15      | PA10                                                 | I/O      | FT              | -    | USART1_RX, TIM1_CH3,<br>OTG_FS_ID,DCMI_D1,<br>EVENTOUT                                       | -                       |

| 44     | 70      | 103     | 122     | C15      | PA11                                                 | I/O      | FT              | -    | USART1_CTS, CAN1_RX,<br>TIM1_CH4, OTG_FS_DM,<br>EVENTOUT                                     | -                       |

| 45     | 71      | 104     | 123     | B15      | PA12                                                 | I/O      | FT              | -    | USART1_RTS, CAN1_TX,<br>TIM1_ETR, OTG_FS_DP,<br>EVENTOUT                                     | -                       |

| 46     | 72      | 105     | 124     | A15      | PA13<br>(JTMS-SWDIO)                                 | I/O      | FT              | -    | JTMS-SWDIO, EVENTOUT                                                                         | -                       |

| 47     | 73      | 106     | 125     | F13      | V <sub>CAP_2</sub>                                   | S        | -               | -    | -                                                                                            | -                       |

| -      | 74      | 107     | 126     | F12      | V <sub>SS</sub>                                      | S        | -               | -    | -                                                                                            |                         |

| 48     | 75      | 108     | 127     | G13      | V <sub>DD</sub>                                      | S        | -               | -    | -                                                                                            | -                       |

| -      | -       | -       | 128     | E12      | PH13                                                 | I/O      | FT              | -    | TIM8_CH1N, CAN1_TX,<br>EVENTOUT                                                              | -                       |

| -      | -       | -       | 129     | E13      | PH14                                                 | I/O      | FT              | -    | TIM8_CH2N, DCMI_D4,<br>EVENTOUT                                                              | -                       |

Table 7. STM32F21x pin and ball definitions (continued)

|        |         | Pins    | ;       |          |                                                      |          |                 |      |                                                                   |                         |

|--------|---------|---------|---------|----------|------------------------------------------------------|----------|-----------------|------|-------------------------------------------------------------------|-------------------------|

| LQFP64 | LQFP100 | LQFP144 | LQFP176 | UFBGA176 | Pin name<br>(function after<br>reset) <sup>(1)</sup> | Pin type | I / O structure | Note | Alternate functions                                               | Additional<br>functions |

| 54     | 83      | 116     | 144     | D12      | PD2                                                  | I/O      | FT              | -    | TIM3_ETR,UART5_RX<br>SDIO_CMD, DCMI_D11,<br>EVENTOUT              | -                       |

| -      | 84      | 117     | 145     | D11      | PD3                                                  | I/O      | FT              | -    | FSMC_CLK,USART2_CTS,<br>EVENTOUT                                  | -                       |

| -      | 85      | 118     | 146     | D10      | PD4                                                  | I/O      | FT              | -    | FSMC_NOE,USART2_RTS,<br>EVENTOUT                                  | -                       |

| -      | 86      | 119     | 147     | C11      | PD5                                                  | I/O      | FT              | -    | FSMC_NWE,USART2_TX,<br>EVENTOUT                                   | -                       |

| -      | -       | 120     | 148     | D8       | V <sub>SS</sub>                                      | S        |                 | -    | -                                                                 | -                       |

| -      | -       | 121     | 149     | C8       | V <sub>DD</sub>                                      | S        |                 | -    | -                                                                 | -                       |

| -      | 87      | 122     | 150     | B11      | PD6                                                  | I/O      | FT              | -    | FSMC_NWAIT,USART2_RX,<br>EVENTOUT                                 | -                       |

| -      | 88      | 123     | 151     | A11      | PD7                                                  | I/O      | FT              | -    | USART2_CK,FSMC_NE1,<br>FSMC_NCE2, EVENTOUT                        | -                       |

| -      | -       | 124     | 152     | C10      | PG9                                                  | I/O      | FT              | -    | USART6_RX,<br>FSMC_NE2,FSMC_NCE3,<br>EVENTOUT                     | -                       |

| -      | -       | 125     | 153     | B10      | PG10                                                 | I/O      | FT              | -    | FSMC_NCE4_1, FSMC_NE3,<br>EVENTOUT                                | -                       |

| -      | -       | 126     | 154     | В9       | PG11                                                 | I/O      | FT              | -    | FSMC_NCE4_2,<br>ETH_MII_TX_EN,<br>ETH_RMII_TX_EN,<br>EVENTOUT     | -                       |

| -      | -       | 127     | 155     | B8       | PG12                                                 | I/O      | FT              | -    | FSMC_NE4, USART6_RTS,<br>EVENTOUT                                 | -                       |

| -      | -       | 128     | 156     | A8       | PG13                                                 | I/O      | FT              | -    | FSMC_A24, USART6_CTS,<br>ETH_MII_TXD0,<br>ETH_RMII_TXD0, EVENTOUT | -                       |

| -      | -       | 129     | 157     | A7       | PG14                                                 | I/O      | FT              | -    | FSMC_A25, USART6_TX,<br>ETH_MII_TXD1,<br>ETH_RMII_TXD1, EVENTOUT  | -                       |

| -      | -       | 130     | 158     | D7       | V <sub>SS</sub>                                      | S        | -               | -    | -                                                                 | -                       |

| -      | -       | 131     | 159     | C7       | V <sub>DD</sub>                                      | S        | -               | -    | -                                                                 | -                       |

Table 7. STM32F21x pin and ball definitions (continued)

|                                         |                                                                                    |                                                                                           |      |      |      | ,    |

|-----------------------------------------|------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------|------|------|------|------|

| Symbol                                  | Parameter                                                                          | Conditions                                                                                | Min  | Тур  | Max  | Unit |

| M                                       | Brownout level 2                                                                   | Falling edge                                                                              | 2.44 | 2.50 | 2.56 | V    |

| V <sub>BOR2</sub>                       | threshold                                                                          | Rising edge                                                                               | 2.53 | 2.59 | 2.63 | V    |

| M                                       | Brownout level 3                                                                   | Falling edge                                                                              | 2.75 | 2.83 | 2.88 | V    |

| V <sub>BOR3</sub>                       | threshold                                                                          | Rising edge                                                                               | 2.85 | 2.92 | 2.97 | V    |

| V <sub>BORhyst</sub> <sup>(1)</sup>     | BOR hysteresis                                                                     | -                                                                                         | -    | 100  | -    | mV   |

| T <sub>RSTTEMPO</sub> <sup>(1)(2)</sup> | Reset temporization                                                                | -                                                                                         | 0.5  | 1.5  | 3.0  | ms   |

| I <sub>RUSH</sub> <sup>(1)</sup>        | InRush current on<br>voltage regulator<br>power-on (POR or<br>wakeup from Standby) | -                                                                                         | -    | 160  | 200  | mA   |

| E <sub>RUSH</sub> <sup>(1)</sup>        | InRush energy on<br>voltage regulator<br>power-on (POR or<br>wakeup from Standby)  | V <sub>DD</sub> = 1.8 V, T <sub>A</sub> = 105 °C,<br>I <sub>RUSH</sub> = 171 mA for 31 μs | -    | -    | 5.4  | μC   |

| Table 18. Embedded reset and | power control block characteristics ( | (continued) |

|------------------------------|---------------------------------------|-------------|

|                              |                                       |             |

1. Guaranteed by design, not tested in production.

2. The reset temporization is measured from the power-on (POR reset or wakeup from  $V_{BAT}$ ) to the instant when first instruction is read by the user application code.

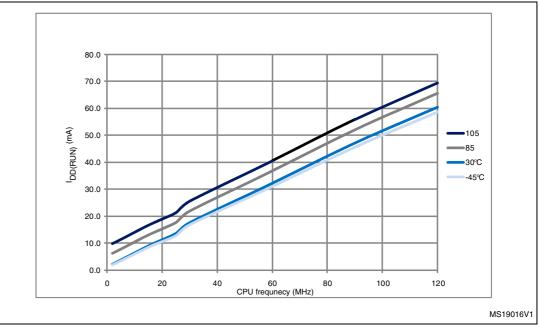

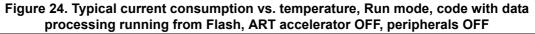

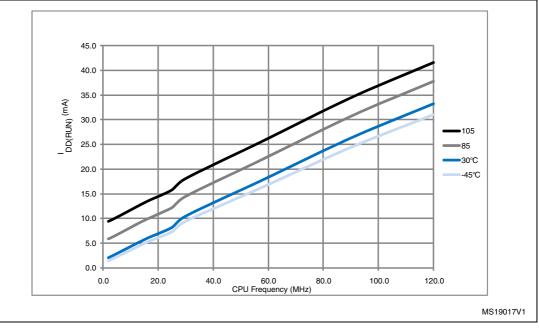

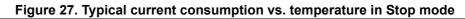

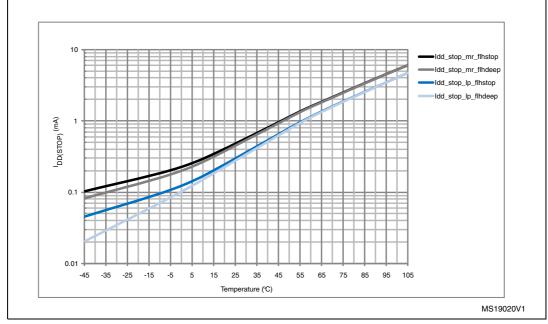

## 6.3.6 Supply current characteristics

The current consumption is a function of several parameters and factors such as the operating voltage, ambient temperature, I/O pin loading, device software configuration, operating frequencies, I/O pin switching rate, program location in memory and executed binary code.

The current consumption is measured as described in *Figure 18: Current consumption measurement scheme*.

All Run mode current consumption measurements given in this section are performed using  ${\sf CoreMark}^{\textcircled{R}}$  code.

Figure 23. Typical current consumption vs. temperature, Run mode, code with data processing running from Flash, ART accelerator OFF, peripherals ON

|        |                                       |                                                                                                                                                  | Тур                       |                           | Max                       |                            |      |

|--------|---------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------|---------------------------|---------------------------|----------------------------|------|

| Symbol | Parameter                             | Conditions                                                                                                                                       | T <sub>A</sub> =<br>25 °C | T <sub>A</sub> =<br>25 °C | T <sub>A</sub> =<br>85 °C | T <sub>A</sub> =<br>105 °C | Unit |

|        | Supply current<br>in Stop mode        | Flash in Stop mode, low-speed and high-speed<br>internal RC oscillators and high-speed oscillator<br>OFF (no independent watchdog)               | 0.55                      | 1.2                       | 11.00                     | 20.00                      |      |

|        | with main<br>regulator in<br>Run mode | Flash in Deep power down mode, low-speed<br>and high-speed internal RC oscillators and<br>high-speed oscillator OFF (no independent<br>watchdog) | 0.50                      | 1.2                       | 11.00                     | 20.00                      | mA   |

|        |                                       | Flash in Stop mode, low-speed and high-speed<br>internal RC oscillators and high-speed oscillator<br>OFF (no independent watchdog)               | 0.35                      | 1.1                       | 8.00                      | 15.00                      | IIIA |

|        | regulator in<br>Low-power<br>mode     | Flash in Deep power down mode, low-speed<br>and high-speed internal RC oscillators and<br>high-speed oscillator OFF (no independent<br>watchdog) | 0.30                      | 1.1                       | 8.00                      | 15.00                      |      |

Table 22. Typical and maximum current consumptions in Stop mode

All typical and maximum values from table 18 and figure 26 will be reduced over time by up to 50% as part

of ST continuous improvement of test procedures. New versions of the datasheet will be released to reflect

these changes

|                      |           |                                                      |                            | Тур                        |                            | Ма                                             |         |      |

|----------------------|-----------|------------------------------------------------------|----------------------------|----------------------------|----------------------------|------------------------------------------------|---------|------|

| Symbol               | Parameter | Conditions                                           | Т                          | A = 25 °C                  | C                          | T <sub>A</sub> = 85 °C T <sub>A</sub> = 105 °C |         | Unit |

| •                    |           |                                                      | V <sub>DD</sub> =<br>1.8 V | V <sub>DD</sub> =<br>2.4 V | V <sub>DD</sub> =<br>3.3 V | V <sub>DD</sub> =                              | = 3.6 V |      |

|                      |           | Backup SRAM ON, low-speed oscillator and RTC ON      | 3.0                        | 3.4                        | 4.0                        | 15.1                                           | 25.8    |      |

| I <sub>DD_STBY</sub> |           | Backup SRAM OFF, low-<br>speed oscillator and RTC ON | 2.4                        | 2.7                        | 3.3                        | 12.4                                           | 20.5    | μA   |

|                      |           | Backup SRAM ON, RTC OFF                              | 2.4                        | 2.6                        | 3.0                        | 12.5                                           | 24.8    |      |

|                      |           | Backup SRAM OFF, RTC OFF                             | 1.7                        | 1.9                        | 2.2                        | 9.8                                            | 19.2    |      |

#### Table 23. Typical and maximum current consumptions in Standby mode

1. Guaranteed by characterization results, not tested in production.

| Table | 24. Typical and maximum cu | rrent consumptions in | n V <sub>BAT</sub> mode |

|-------|----------------------------|-----------------------|-------------------------|

|       |                            |                       |                         |

|                      |                                    |                                                     | Тур                    |                            |                            | Ма                      |         |    |

|----------------------|------------------------------------|-----------------------------------------------------|------------------------|----------------------------|----------------------------|-------------------------|---------|----|

| Symbol               | Parameter                          | r Conditions                                        | T <sub>A</sub> = 25 °C |                            | T <sub>A</sub> = 85 °C     | T <sub>A</sub> = 105 °C | Unit    |    |

|                      |                                    |                                                     |                        | V <sub>DD</sub> =<br>2.4 V | V <sub>DD</sub> =<br>3.3 V | V <sub>DD</sub> =       | = 3.6 V |    |

|                      |                                    | Backup SRAM ON, low-speed<br>oscillator and RTC ON  | 1.29                   | 1.42                       | 1.68                       | 12                      | 19      |    |

| I <sub>DD_VBAT</sub> | Backup<br>domain supply<br>current | Backup SRAM OFF, low-speed<br>oscillator and RTC ON | 0.62                   | 0.73                       | 0.96                       | 8                       | 10      | μA |

|                      |                                    | Backup SRAM ON, RTC OFF                             | 0.79                   | 0.81                       | 0.86                       | 9                       | 16      |    |

|                      |                                    | Backup SRAM OFF, RTC OFF                            | 0.10                   | 0.10                       | 0.10                       | 5                       | 7       |    |

1. Guaranteed by characterization results, not tested in production.

## **On-chip peripheral current consumption**

The current consumption of the on-chip peripherals is given in *Table 25*. The MCU is placed under the following conditions:

- At startup, all I/O pins are configured as analog inputs by firmware.

- All peripherals are disabled unless otherwise mentioned

- The given value is calculated by measuring the current consumption

- with all peripherals clocked off

- with one peripheral clocked on (with only the clock applied)

- The code is running from Flash memory and the Flash memory access time is equal to 3 wait states at 120 MHz

- Prefetch and Cache ON

- When the peripherals are enabled, HCLK = 120MHz,  $f_{PCLK1}$  =  $f_{HCLK}/4,$  and  $f_{PCLK2}$  =  $f_{HCLK}/2$

- The typical values are obtained for V\_{DD} = 3.3 V and T\_A= 25  $^\circ\text{C},$  unless otherwise specified.

DocID17050 Rev 13

# 6.3.8 External clock source characteristics

### High-speed external user clock generated from an external source

The characteristics given in *Table 27* result from tests performed using an high-speed external clock source, and under ambient temperature and supply voltage conditions summarized in *Table 13*.

| Symbol                                     | Parameter                                           | Conditions                       | Min         | Тур | Max                | Unit |

|--------------------------------------------|-----------------------------------------------------|----------------------------------|-------------|-----|--------------------|------|

| f <sub>HSE_ext</sub>                       | External user clock source frequency <sup>(1)</sup> |                                  | 1           | -   | 26                 | MHz  |

| V <sub>HSEH</sub>                          | OSC_IN input pin high level voltage                 |                                  | $0.7V_{DD}$ | -   | $V_{DD}$           | V    |

| V <sub>HSEL</sub>                          | OSC_IN input pin low level voltage                  | -                                | $V_{SS}$    | -   | $0.3V_{\text{DD}}$ | v    |

| t <sub>w(HSE)</sub><br>t <sub>w(HSE)</sub> | OSC_IN high or low time <sup>(1)</sup>              |                                  | 5           | -   | -                  | ns   |

| t <sub>r(HSE)</sub><br>t <sub>f(HSE)</sub> | OSC_IN rise or fall time <sup>(1)</sup>             |                                  | -           | -   | 20                 | 115  |

| C <sub>in(HSE)</sub>                       | OSC_IN input capacitance <sup>(1)</sup>             | -                                | -           | 5   | -                  | pF   |

| DuCy <sub>(HSE)</sub>                      | Duty cycle                                          | -                                | 45          | -   | 55                 | %    |

| ١ <sub>L</sub>                             | OSC_IN Input leakage current                        | $V_{SS} \leq V_{IN} \leq V_{DD}$ | -           | -   | ±1                 | μA   |

Table 27. High-speed external user clock characteristics

1. Guaranteed by design, not tested in production.

## Low-speed external user clock generated from an external source

The characteristics given in *Table 28* result from tests performed using an low-speed external clock source, and under ambient temperature and supply voltage conditions summarized in *Table 13*.

| Symbol                                     | Parameter                                           | Conditions                       | Min                 | Тур    | Max                | Unit |

|--------------------------------------------|-----------------------------------------------------|----------------------------------|---------------------|--------|--------------------|------|

| f <sub>LSE_ext</sub>                       | User External clock source frequency <sup>(1)</sup> |                                  | -                   | 32.768 | 1000               | kHz  |

| V <sub>LSEH</sub>                          | OSC32_IN input pin high level voltage               |                                  | $0.7 V_{\text{DD}}$ | -      | $V_{DD}$           | v    |

| V <sub>LSEL</sub>                          | OSC32_IN input pin low level voltage                |                                  | $V_{SS}$            | -      | $0.3V_{\text{DD}}$ |      |

| t <sub>w(LSE)</sub><br>t <sub>f(LSE)</sub> | OSC32_IN high or low time <sup>(1)</sup>            | -                                | 450                 | -      | -                  | ns   |

| t <sub>r(LSE)</sub><br>t <sub>f(LSE)</sub> | OSC32_IN rise or fall time <sup>(1)</sup>           |                                  | -                   | -      | 50                 | 115  |

| C <sub>in(LSE)</sub>                       | OSC32_IN input capacitance <sup>(1)</sup>           | -                                | -                   | 5      | -                  | pF   |

| DuCy <sub>(LSE)</sub>                      | Duty cycle                                          | -                                | 30                  | -      | 70                 | %    |

| ١L                                         | OSC32_IN Input leakage current                      | $V_{SS} \leq V_{IN} \leq V_{DD}$ | -                   | -      | ±1                 | μA   |

1. Guaranteed by design, not tested in production.

| Symbol                               | Parameter                                    | Conditions                                  |                    | Min          | Тур         | Мах          | Unit |

|--------------------------------------|----------------------------------------------|---------------------------------------------|--------------------|--------------|-------------|--------------|------|

|                                      |                                              |                                             | RMS                | -            | 25          | -            |      |

|                                      | Cycle-to-cycle jitter                        | r<br>t<br>System clock                      |                    | -            | ±150        | -            |      |

|                                      | Period Jitter                                | 120 MHz                                     | RMS                | -            | 15          | -            |      |

| Jitter <sup>(3)</sup>                |                                              |                                             | peak<br>to<br>peak | -            | <u>+200</u> | -            | ps   |

|                                      | Main clock output (MCO) for<br>RMII Ethernet | Cycle to cycle at 50 MHz<br>on 1000 samples |                    | -            | 32          | -            |      |

|                                      | Main clock output (MCO) for MII<br>Ethernet  | Cycle to cycle at 25 MHz on 1000 samples    |                    | -            | 40          | -            |      |

|                                      | Bit Time CAN jitter                          | Cycle to cycle at 1 MHz<br>on 1000 samples  |                    | -            | 330         | -            |      |

| I <sub>DD(PLL)</sub> <sup>(4)</sup>  | PLL power consumption on VDD                 | VCO freq = 192 MHz<br>VCO freq = 432 MHz    |                    | 0.15<br>0.45 | -           | 0.40<br>0.75 | mA   |

| I <sub>DDA(PLL)</sub> <sup>(4)</sup> | PLL power consumption on VDDA                | VCO freq = 192 MHz<br>VCO freq = 432 MHz    |                    | 0.30<br>0.55 | -           | 0.40<br>0.85 | mA   |

Table 33. Main PLL characteristics (continued)

1. Take care of using the appropriate division factor M to obtain the specified PLL input clock values. The M factor is shared between PLL and PLLI2S.

2. Guaranteed by design, not tested in production.

3. The use of 2 PLLs in parallel could degraded the Jitter up to +30%.

4. Guaranteed by characterization results, not tested in production.

#### Table 34. PLLI2S (audio PLL) characteristics

| Symbol                  | Parameter                         | Conditions         | Min                 | Тур | Мах                 | Unit |

|-------------------------|-----------------------------------|--------------------|---------------------|-----|---------------------|------|

| f <sub>PLLI2S_IN</sub>  | PLLI2S input clock <sup>(1)</sup> | -                  | 0.95 <sup>(2)</sup> | 1   | 2.10 <sup>(2)</sup> | MHz  |

| f <sub>PLLI2S_OUT</sub> | PLLI2S multiplier output clock    | -                  | -                   | -   | 216                 | MHz  |

| f <sub>VCO_OUT</sub>    | PLLI2S VCO output                 | -                  | 192                 | -   | 432                 | MHz  |

| +                       | PLLI2S lock time                  | VCO freq = 192 MHz | 75                  | -   | 200                 |      |

| <sup>t</sup> LOCK       |                                   | VCO freq = 432 MHz | 100                 | -   | 300                 | μs   |

| Symbol                                  | Parameter                             | Conditions                                                                |     | Min          | Тур  | Мах          | Unit |

|-----------------------------------------|---------------------------------------|---------------------------------------------------------------------------|-----|--------------|------|--------------|------|

|                                         | Master I2S clock jitter               | Cycle to cycle at<br>12.288 MHz on<br>48KHz period,<br>N=432, R=5<br>Peak | RMS | -            | 90   | -            |      |

|                                         |                                       |                                                                           | to  | -            | ±280 | -            | ps   |

| Jitter <sup>(3)</sup>                   |                                       | Average frequency of<br>12.288 MHz<br>N=432, R=5<br>on 1000 samples       |     | -            | 90   | -            | ps   |

|                                         | WS I2S clock jitter                   | Cycle to cycle at 48 I<br>on 1000 samples                                 | KHz | -            | 400  | -            | ps   |

| I <sub>DD(PLLI2S)</sub> <sup>(4)</sup>  | PLLI2S power consumption on $V_{DD}$  | VCO freq = 192 MHz<br>VCO freq = 432 MHz                                  |     | 0.15<br>0.45 | -    | 0.40<br>0.75 | mA   |

| I <sub>DDA(PLLI2S)</sub> <sup>(4)</sup> | PLLI2S power consumption on $V_{DDA}$ | VCO freq = 192 MHz<br>VCO freq = 432 MHz                                  |     | 0.30<br>0.55 | -    | 0.40<br>0.85 | mA   |

Table 34. PLLI2S (audio PLL) characteristics (continued)

1. Take care of using the appropriate division factor M to have the specified PLL input clock values.

2. Guaranteed by design, not tested in production.

3. Value given with main PLL running.

4. Guaranteed by characterization results, not tested in production.

| Symbol                 | Parameter                       | Parameter Conditions Min                                        |        | Мах                     | Unit                 |

|------------------------|---------------------------------|-----------------------------------------------------------------|--------|-------------------------|----------------------|

|                        |                                 | AHB/APB2                                                        | 1      | -                       | t <sub>TIMxCLK</sub> |

| t <sub>res(TIM)</sub>  | Timer resolution time           | prescaler distinct<br>from 1, f <sub>TIMxCLK</sub> =<br>120 MHz | 8.3    | -                       | ns                   |

|                        |                                 | AHB/APB2                                                        | 1      | -                       | t <sub>TIMxCLK</sub> |

|                        |                                 | prescaler = 1,<br>f <sub>TIMxCLK</sub> = 60 MHz                 | 16.7   | -                       | ns                   |

| f <sub>EXT</sub>       | Timer external clock            |                                                                 | 0      | f <sub>TIMxCLK</sub> /2 | MHz                  |

| 'EXT                   | frequency on CH1 to CH4         |                                                                 | 0      | 60                      | MHz                  |

| Res <sub>TIM</sub>     | Timer resolution                |                                                                 | -      | 16                      | bit                  |

| +                      | 16-bit counter clock period     | f <sub>TIMxCLK</sub> = 120 MHz<br>APB2 = 60 MHz                 | 1      | 65536                   | t <sub>TIMxCLK</sub> |

| <sup>t</sup> COUNTER   | when internal clock is selected |                                                                 | 0.0083 | 546                     | μs                   |

| tury ocupit            | Maximum possible count          |                                                                 | -      | 65536 × 65536           | t <sub>TIMxCLK</sub> |

| t <sub>MAX_COUNT</sub> | Maximum possible count          |                                                                 | -      | 35.79                   | S                    |

Table 50. Characteristics of TIMx connected to the APB2 domain<sup>(1)</sup>

1. TIMx is used as a general term to refer to the TIM1, TIM8, TIM9, TIM10, and TIM11 timers.

# 6.3.19 Communications interfaces

## I<sup>2</sup>C interface characteristics

STM32F215xx and STM32F217xx  $I^2C$  interface meets the requirements of the standard  $I^2C$  communication protocol with the following restrictions: the I/O pins SDA and SCL are mapped to are not "true" open-drain. When configured as open-drain, the PMOS connected between the I/O pin and V<sub>DD</sub> is disabled, but is still present.

The I<sup>2</sup>C characteristics are described in *Table 51*. Refer also to *Section 6.3.16: I/O port characteristics* for more details on the input/output alternate function characteristics (SDA and SCL).

DocID17050 Rev 13

### **USB OTG FS characteristics**

The USB OTG interface is USB-IF certified (Full-Speed). This interface is present in both the USB OTG HS and USB OTG FS controllers.

| Symbol                              | Parameter                           | Мах | Unit |  |  |  |

|-------------------------------------|-------------------------------------|-----|------|--|--|--|

| t <sub>STARTUP</sub> <sup>(1)</sup> | USB OTG FS transceiver startup time | 1   | μs   |  |  |  |

Table 55. USB OTG FS startup time

1. Guaranteed by design, not tested in production.

| Sym                                                           | bol                            | Parameter                                                 | Conditions                                                       | Min <sup>(1)</sup> | Тур  | Max <sup>(1)</sup> | Unit |

|---------------------------------------------------------------|--------------------------------|-----------------------------------------------------------|------------------------------------------------------------------|--------------------|------|--------------------|------|

|                                                               | $V_{DD}$                       | USB OTG FS operating<br>voltage                           |                                                                  | 3.0 <sup>(2)</sup> | -    | 3.6                | ۷    |

| Input                                                         | V <sub>DI</sub> <sup>(3)</sup> | Differential input sensitivity                            | I(USB_FS_DP/DM,<br>USB_HS_DP/DM)                                 | 0.2                | -    | -                  |      |

| levels                                                        | V <sub>CM</sub> <sup>(3)</sup> | Differential common mode range                            | Includes V <sub>DI</sub> range                                   | 0.8                | -    | 2.5                | V    |

|                                                               | $V_{SE}^{(3)}$                 | Single ended receiver threshold                           |                                                                  | 1.3                | -    | 2.0                |      |

| Output                                                        | $V_{OL}$                       | Static output level low                                   | $\rm R_L$ of 1.5 k\Omega to 3.6 $\rm V^{(4)}$                    | -                  | -    | 0.3                | V    |

| levels                                                        | $V_{OH}$                       | Static output level high                                  | ${\sf R}_{\sf L}$ of 15 k $\Omega$ to ${\sf V}_{\sf SS}{}^{(4)}$ | 2.8                | -    | 3.6                | v    |

| Б                                                             |                                | PA11, PA12, PB14, PB15<br>(USB_FS_DP/DM,<br>USB_HS_DP/DM) | V <sub>IN</sub> = V <sub>DD</sub>                                | 17                 | 21   | 24                 |      |

| R <sub>PD</sub><br>PA9, PB13<br>(OTG_FS_VBUS,<br>OTG_HS_VBUS) | (OTG_FS_VBUS,                  | VIN - VDD                                                 | 0.65                                                             | 1.1                | 2.0  | kΩ                 |      |

|                                                               |                                | PA12, PB15 (USB_FS_DP,<br>USB_HS_DP)                      | V <sub>IN</sub> = V <sub>SS</sub>                                | 1.5                | 1.8  | 2.1                |      |

| R <sub>PU</sub>                                               |                                | PA9, PB13<br>(OTG_FS_VBUS,<br>OTG_HS_VBUS)                | V <sub>IN</sub> = V <sub>SS</sub>                                | 0.25               | 0.37 | 0.55               |      |

### Table 56. USB OTG FS DC electrical characteristics

1. All the voltages are measured from the local ground potential.

2. The STM32F215xx and STM32F217xx USB OTG FS functionality is ensured down to 2.7 V but not the full USB OTG FS electrical characteristics which are degraded in the 2.7-to-3.0 V  $V_{DD}$  voltage range.

3. Guaranteed by design, not tested in production.

4. R<sub>L</sub> is the load connected on the USB OTG FS drivers

|                           |                                                | (00110110 |     |      |

|---------------------------|------------------------------------------------|-----------|-----|------|

| Symbol                    | Parameter                                      | Min       | Мах | Unit |

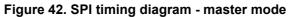

| t <sub>su(ADV-CLKH)</sub> | FSMC_A/D[15:0] valid data before FSMC_CLK high | 5         | -   | ns   |

| t <sub>h(CLKH-ADV)</sub>  | FSMC_A/D[15:0] valid data after FSMC_CLK high  | 0         | -   | ns   |

|                           |                                                |           |     |      |

## Table 75. Synchronous multiplexed NOR/PSRAM read timings<sup>(1)(2)</sup> (continued)

1. C<sub>L</sub> = 30 pF.

2. Guaranteed by characterization results, not tested in production.

#### Figure 60. Synchronous multiplexed PSRAM write timings

Table 76. Synchronous multiplexed PSRAM write timings<sup>(1)(2)</sup>

| Symbol                     | nbol Parameter                           |                        | Max | Unit |

|----------------------------|------------------------------------------|------------------------|-----|------|

| t <sub>w(CLK)</sub>        | FSMC_CLK period                          | 2T <sub>HCLK</sub> - 1 | -   | ns   |

| t <sub>d(CLKL-NExL)</sub>  | FSMC_CLK low to FSMC_NEx low (x=02)      | -                      | 0   | ns   |

| t <sub>d(CLKL-NExH)</sub>  | FSMC_CLK low to FSMC_NEx high (x= 02)    | 2                      | -   | ns   |

| t <sub>d(CLKL-NADVL)</sub> | FSMC_CLK low to FSMC_NADV low            | -                      | 2   | ns   |

| t <sub>d(CLKL-NADVH)</sub> | FSMC_CLK low to FSMC_NADV high           | 3                      | -   | ns   |

| t <sub>d(CLKL-AV)</sub>    | FSMC_CLK low to FSMC_Ax valid (x=1625)   | -                      | 0   | ns   |

| t <sub>d(CLKL-AIV)</sub>   | FSMC_CLK low to FSMC_Ax invalid (x=1625) | 7                      | -   | ns   |

DocID17050 Rev 13

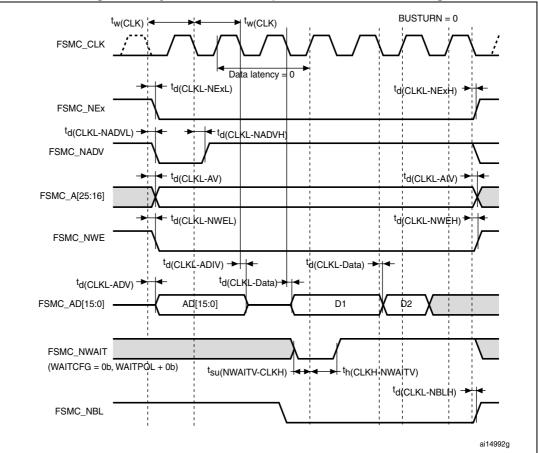

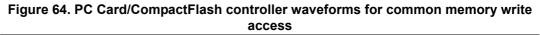

Figure 63. PC Card/CompactFlash controller waveforms for common memory read access

1. FSMC\_NCE4\_2 remains high (inactive during 8-bit access.

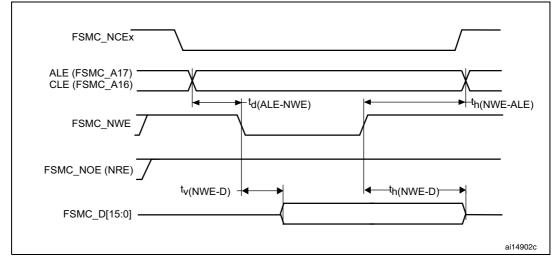

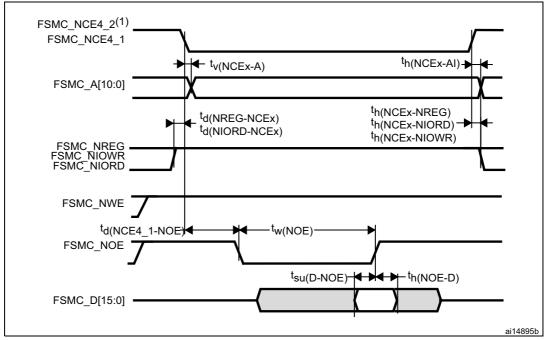

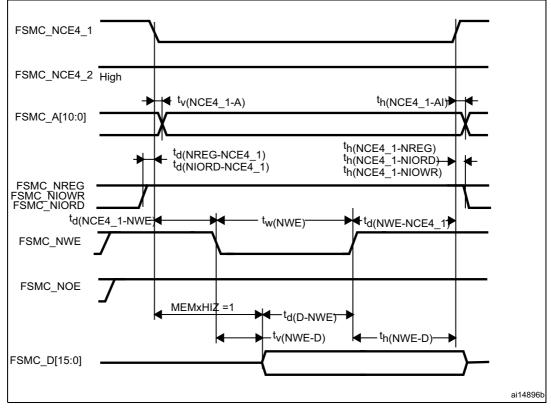

Figure 69. NAND controller waveforms for read access

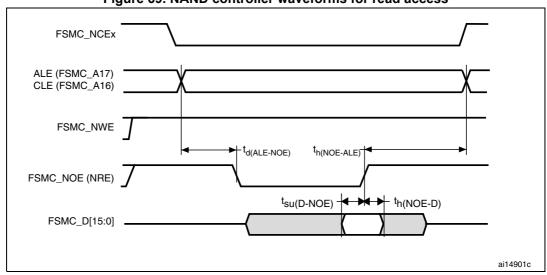

Figure 70. NAND controller waveforms for write access