Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                                         |

|----------------------------|-----------------------------------------------------------------------------------------|

| Product Status             | Active                                                                                  |

| Core Processor             | ARM® Cortex®-M3                                                                         |

| Core Size                  | 32-Bit Single-Core                                                                      |

| Speed                      | 120MHz                                                                                  |

| Connectivity               | CANbus, Ethernet, I <sup>2</sup> C, IrDA, LINbus, Memory Card, SPI, UART/USART, USB OTG |

| Peripherals                | Brown-out Detect/Reset, DMA, I <sup>2</sup> S, LCD, POR, PWM, WDT                       |

| Number of I/O              | 140                                                                                     |

| Program Memory Size        | 512KB (512K x 8)                                                                        |

| Program Memory Type        | FLASH                                                                                   |

| EEPROM Size                | -                                                                                       |

| RAM Size                   | 132K x 8                                                                                |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                                             |

| Data Converters            | A/D 24x12b; D/A 2x12b                                                                   |

| Oscillator Type            | Internal                                                                                |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                       |

| Mounting Type              | Surface Mount                                                                           |

| Package / Case             | 176-LQFP                                                                                |

| Supplier Device Package    | 176-LQFP (24x24)                                                                        |

| Purchase URL               | https://www.e-xfl.com/product-detail/stmicroelectronics/stm32f217iet6                   |

|                            |                                                                                         |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

|            | ultra fine pitch ball grid array package outline                         | 163 |

|------------|--------------------------------------------------------------------------|-----|

| Figure 86. | UFBGA176+25 - 201-ball, 10 x 10 mm, 0.65 mm pitch, ultra fine pitch ball |     |

|            | grid array package recommended footprint                                 | 164 |

| Figure 87. | UFBGA176+25 marking (package top view)                                   | 165 |

# 1 Introduction

This datasheet provides the description of the STM32F215xx and STM32F217xx lines of microcontrollers. For more details on the whole STMicroelectronics STM32 family, refer to *Section 2.1: Full compatibility throughout the family*.

The STM32F215xx and STM32F217xx datasheet should be read in conjunction with the STM32F20x/STM32F21x reference manual. They will be referred to as STM32F21x devices throughout the document.

For information on programming, erasing and protection of the internal Flash memory, refer to the STM32F20x/STM32F21x Flash programming manual (PM0059).

The reference and Flash programming manuals are both available from the STMicroelectronics website *www.st.com*.

For information on the Cortex<sup>®</sup>-M3 core refer to the Cortex<sup>®</sup>-M3 Technical Reference Manual, available from the *www.arm.com* website.

1. RFU = reserved for future use.

1. RFU = reserved for future use.

DocID17050 Rev 13

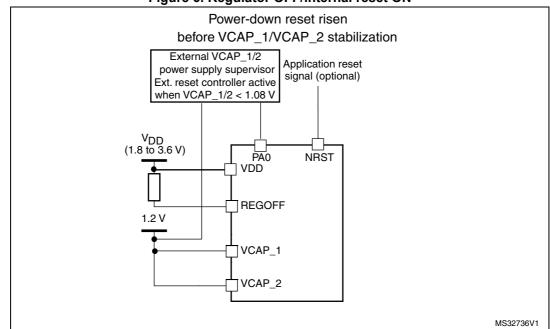

#### Figure 6. Regulator OFF/internal reset ON

The following conditions must be respected:

- V<sub>DD</sub> should always be higher than V<sub>CAP\_1</sub> and V<sub>CAP\_2</sub> to avoid current injection between power domains.

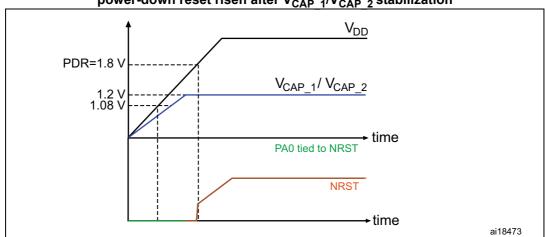

- If the time for V<sub>CAP\_1</sub> and V<sub>CAP\_2</sub> to reach 1.08 V is faster than the time for V<sub>DD</sub> to reach 1.8 V, then PA0 should be kept low to cover both conditions: until V<sub>CAP\_1</sub> and V<sub>CAP\_2</sub> reach 1.08 V and until V<sub>DD</sub> reaches 1.8 V (see *Figure 7*).

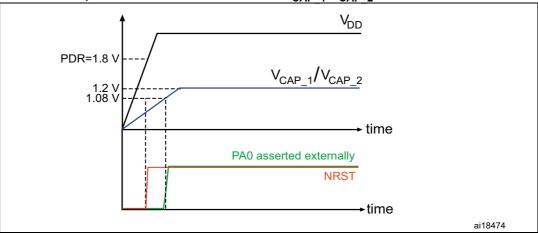

- Otherwise, If the time for V<sub>CAP\_1</sub> and V<sub>CAP\_2</sub> to reach 1.08 V is slower than the time for V<sub>DD</sub> to reach 1.8 V, then PA0 should be asserted low externally (see *Figure 8*).

- If V<sub>CAP\_1</sub> and V<sub>CAP\_2</sub> go below 1.08 V and V<sub>DD</sub> is higher than 1.8 V, then a reset must be asserted on PA0 pin.

integrated power-on reset (POR)/ power-down reset (PDR) circuitry is disabled.

An external power supply supervisor should monitor both the external 1.2 V and the external  $V_{DD}$  supply voltage, and should maintain the device in reset mode as long as they remain below a specified threshold. The  $V_{DD}$  specified threshold, below which the device must be maintained under reset, is 1.8 V. This supply voltage can drop to 1.7 V when the device operates in the 0 to 70 °C temperature range. A comprehensive set of power-saving modes allows the design of low-power applications.

# Figure 7. Startup in regulator OFF: slow V<sub>DD</sub> slope, power-down reset risen after V<sub>CAP 1</sub>/V<sub>CAP 2</sub> stabilization

1. This figure is valid both whatever the internal reset mode (ON or OFF).

### 3.16.3 Regulator ON/OFF and internal reset ON/OFF availability

| Table 3. Regulator ON/OFF and internal reset ON/ | OFF availability |

|--------------------------------------------------|------------------|

|--------------------------------------------------|------------------|

| Package                                 | Regulator ON/internal reset ON       | Regulator ON/internal<br>reset OFF | Regulator<br>OFF/internal reset ON   |

|-----------------------------------------|--------------------------------------|------------------------------------|--------------------------------------|

| LQFP64<br>LQFP100<br>LQFP144<br>LQFP176 | Yes                                  | No                                 | No                                   |

| UFBGA176                                | Yes<br>REGOFF set to V <sub>SS</sub> | No                                 | Yes<br>REGOFF set to V <sub>DD</sub> |

and the HSE crystal oscillators are disabled. The voltage regulator can also be put either in normal or in low-power mode.

The device can be woken up from the Stop mode by any of the EXTI line. The EXTI line source can be one of the 16 external lines, the PVD output, the RTC alarm / wakeup / tamper / time stamp events, the USB OTG FS/HS wakeup or the Ethernet wakeup.

#### • Standby mode

The Standby mode is used to achieve the lowest power consumption. The internal voltage regulator is switched off so that the entire 1.2 V domain is powered off. The PLL, the HSI RC and the HSE crystal oscillators are also switched off. After entering Standby mode, the SRAM and register contents are lost except for registers in the backup domain and the backup SRAM when selected.

The device exits the Standby mode when an external reset (NRST pin), an IWDG reset, a rising edge on the WKUP pin, or an RTC alarm / wakeup / tamper /time stamp event occurs.

*Note:* The RTC, the IWDG, and the corresponding clock sources are not stopped when the device enters the Stop or Standby mode.

# 3.19 V<sub>BAT</sub> operation

The  $V_{\text{BAT}}$  pin allows to power the device  $V_{\text{BAT}}$  domain from an external battery or an external supercapacitor.

$V_{BAT}$  operation is activated when  $V_{DD}$  is not present.

The VBAT pin supplies the RTC, the backup registers and the backup SRAM.

Note: When the microcontroller is supplied from  $V_{BAT}$ , external interrupts and RTC alarm/events do not exit it from  $V_{BAT}$  operation.

## 3.20 Timers and watchdogs

The STM32F21x devices include two advanced-control timers, eight general-purpose timers, two basic timers and two watchdog timers.

All timer counters can be frozen in debug mode.

Table 4 compares the features of the advanced-control, general-purpose and basic timers.

| Timer type           | Timer         | Counter<br>resolution | Counter<br>type         | Prescaler<br>factor                   | DMA<br>request<br>generation |   | Complementary<br>output | Max<br>interface<br>clock | Max<br>timer<br>clock |

|----------------------|---------------|-----------------------|-------------------------|---------------------------------------|------------------------------|---|-------------------------|---------------------------|-----------------------|

| Advanced-<br>control | TIM1,<br>TIM8 | 16-bit                | Up,<br>Down,<br>Up/down | Any integer<br>between 1<br>and 65536 | Yes                          | 4 | Yes                     | 60<br>MHz                 | 120<br>MHz            |

CAN is used). The 256 bytes of SRAM which are allocated for each CAN are not shared with any other peripheral.

# 3.28 Universal serial bus on-the-go full-speed (OTG\_FS)

The devices embed an USB OTG full-speed device/host/OTG peripheral with integrated transceivers. The USB OTG FS peripheral is compliant with the USB 2.0 specification and with the OTG 1.0 specification. It has software-configurable endpoint setting and supports suspend/resume. The USB OTG full-speed controller requires a dedicated 48 MHz clock that is generated by a PLL connected to the HSE oscillator. The major features are:

- Combined Rx and Tx FIFO size of 320 × 35 bits with dynamic FIFO sizing

- Supports the session request protocol (SRP) and host negotiation protocol (HNP)

- 4 bidirectional endpoints

- 8 host channels with periodic OUT support

- HNP/SNP/IP inside (no need for any external resistor)

- For OTG/Host modes, a power switch is needed in case bus-powered devices are connected

- Internal FS OTG PHY support

### 3.29 Universal serial bus on-the-go high-speed (OTG\_HS)

The STM32F21x devices embed a USB OTG high-speed (up to 480 Mb/s) device/host/OTG peripheral. The USB OTG HS supports both full-speed and high-speed operations. It integrates the transceivers for full-speed operation (12 MB/s) and features a UTMI low-pin interface (ULPI) for high-speed operation (480 MB/s). When using the USB OTG HS in HS mode, an external PHY device connected to the ULPI is required.

The USB OTG HS peripheral is compliant with the USB 2.0 specification and with the OTG 1.0 specification. It has software-configurable endpoint setting and supports suspend/resume. The USB OTG full-speed controller requires a dedicated 48 MHz clock that is generated by a PLL connected to the HSE oscillator. The major features are:

- Combined Rx and Tx FIFO size of 1024× 35 bits with dynamic FIFO sizing

- Supports the session request protocol (SRP) and host negotiation protocol (HNP)

- 6 bidirectional endpoints

- 12 host channels with periodic OUT support

- Internal FS OTG PHY support

- External HS or HS OTG operation supporting ULPI in SDR mode. The OTG PHY is connected to the microcontroller ULPI port through 12 signals. It can be clocked using the 60 MHz output.

- Internal USB DMA

- HNP/SNP/IP inside (no need for any external resistor)

- For OTG/Host modes, a power switch is needed in case bus-powered devices are connected

### 3.30 Audio PLL (PLLI2S)

The devices feature an additional dedicated PLL for audio I<sup>2</sup>S application. It allows to achieve error-free I<sup>2</sup>S sampling clock accuracy without compromising on the CPU performance, while using USB peripherals.

The PLLI2S configuration can be modified to manage an  $I^2S$  sample rate change without disabling the main PLL (PLL) used for CPU, USB and Ethernet interfaces.

The audio PLL can be programmed with very low error to obtain sampling rates ranging from 8 kHz to 192 kHz.

In addition to the audio PLL, a master clock input pin can be used to synchronize the I2S flow with an external PLL (or Codec output).

### 3.31 Digital camera interface (DCMI)

The camera interface is not available in STM32F215xx devices.

STM32F217xx products embed a camera interface that can connect with camera modules and CMOS sensors through an 8-bit to 14-bit parallel interface, to receive video data. The camera interface can sustain up to 27 Mbyte/s at 27 MHz or 48 Mbyte/s at 48 MHz. It features:

- Programmable polarity for the input pixel clock and synchronization signals

- Parallel data communication can be 8-, 10-, 12- or 14-bit

- Supports 8-bit progressive video monochrome or raw Bayer format, YCbCr 4:2:2 progressive video, RGB 565 progressive video or compressed data (like JPEG)

- Supports continuous mode or snapshot (a single frame) mode

- Capability to automatically crop the image

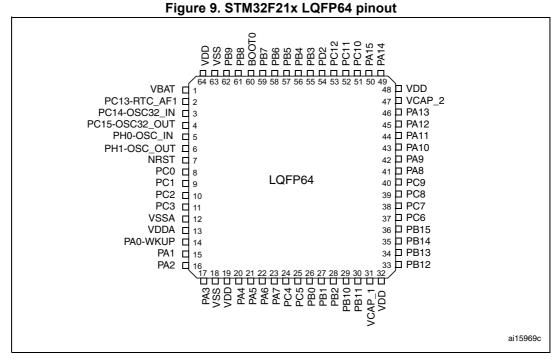

# 4 Pinouts and pin description

1. The above figure shows the package top view.

|        |         | Pins    | \$      |          |                                                      |          |                 |      |                                                                               |                         |

|--------|---------|---------|---------|----------|------------------------------------------------------|----------|-----------------|------|-------------------------------------------------------------------------------|-------------------------|

| LQFP64 | LQFP100 | LQFP144 | LQFP176 | UFBGA176 | Pin name<br>(function after<br>reset) <sup>(1)</sup> | Pin type | I / O structure | Note | Alternate functions                                                           | Additional<br>functions |

| -      | 57      | 79      | 98      | N15      | PD10                                                 | I/O      | FT              | -    | FSMC_D15, USART3_CK,<br>EVENTOUT                                              | -                       |

| -      | 58      | 80      | 99      | N14      | PD11                                                 | I/O      | FT              | -    | FSMC_A16,USART3_CTS,<br>EVENTOUT                                              | -                       |

| -      | 59      | 81      | 100     | N13      | PD12                                                 | I/O      | FT              | -    | FSMC_A17,TIM4_CH1,<br>USART3_RTS, EVENTOUT                                    | -                       |

| -      | 60      | 82      | 101     | M15      | PD13                                                 | I/O      | FT              | -    | FSMC_A18,TIM4_CH2,<br>EVENTOUT                                                | -                       |

| -      | -       | 83      | 102     | -        | V <sub>SS</sub>                                      | S        |                 | -    | -                                                                             | -                       |

| -      | -       | 84      | 103     | J13      | V <sub>DD</sub>                                      | S        |                 | -    | -                                                                             | -                       |

| -      | 61      | 85      | 104     | M14      | PD14                                                 | I/O      | FT              | -    | FSMC_D0,TIM4_CH3,<br>EVENTOUT                                                 | -                       |

| -      | 62      | 86      | 105     | L14      | PD15                                                 | I/O      | FT              | -    | FSMC_D1,TIM4_CH4,<br>EVENTOUT                                                 | -                       |

| -      | -       | 87      | 106     | L15      | PG2                                                  | I/O      | FT              | -    | FSMC_A12, EVENTOUT                                                            | -                       |

| -      | -       | 88      | 107     | K15      | PG3                                                  | I/O      | FT              | -    | FSMC_A13, EVENTOUT                                                            | -                       |

| -      | -       | 89      | 108     | K14      | PG4                                                  | I/O      | FT              | -    | FSMC_A14, EVENTOUT                                                            | -                       |

| -      | -       | 90      | 109     | K13      | PG5                                                  | I/O      | FT              | I    | FSMC_A15, EVENTOUT                                                            | _                       |

| -      | -       | 91      | 110     | J15      | PG6                                                  | I/O      | FT              | -    | FSMC_INT2, EVENTOUT                                                           | -                       |

| -      | -       | 92      | 111     | J14      | PG7                                                  | I/O      | FT              | -    | FSMC_INT3,USART6_CK,<br>EVENTOUT                                              | -                       |

| -      | -       | 93      | 112     | H14      | PG8                                                  | I/O      | FT              | -    | USART6_RTS,<br>ETH_PPS_OUT, EVENTOUT                                          | -                       |

| -      | -       | 94      | 113     | G12      | V <sub>SS</sub>                                      | S        | -               | -    | -                                                                             | -                       |

| -      | -       | 95      | 114     | H13      | V <sub>DD</sub>                                      | S        | -               | -    | -                                                                             | -                       |

| 37     | 63      | 96      | 115     | H15      | PC6                                                  | I/O      | FT              | -    | I2S2_MCK,<br>TIM8_CH1,SDIO_D6,<br>USART6_TX,<br>DCMI_D0,TIM3_CH1,<br>EVENTOUT | -                       |

Table 7. STM32F21x pin and ball definitions (continued)

Pinouts and pin description

DocID17050 Rev 13

|        |          | AF0            | AF1                    | AF2       | AF3          | AF4            | AF5            | AF6                 | AF7        | AF8                | AF9                       | AF10               | AF11                                       | AF12                 | AF13       |       |          |

|--------|----------|----------------|------------------------|-----------|--------------|----------------|----------------|---------------------|------------|--------------------|---------------------------|--------------------|--------------------------------------------|----------------------|------------|-------|----------|

|        | Port     | SYS            | TIM1/2                 | TIM3/4/5  | TIM8/9/10/11 | 12C1/12C2/12C3 | SPI1/SPI2/I2S2 | SPI3/I2S3           | USART1/2/3 | UART4/5/<br>USART6 | CAN1/CAN2/<br>TIM12/13/14 |                    | ETH                                        | FSMC/SDIO/<br>OTG_HS | DCMI       | AF014 | AF15     |

|        | PA0-WKUP | -              | TIM2_CH1_ETR           | TIM 5_CH1 | TIM8_ETR     | -              | -              |                     | USART2_CTS | UART4_TX           | -                         | -                  | ETH_MII_CRS                                | -                    | -          | -     | EVENTOUT |

|        | PA1      | -              | TIM2_CH2               | TIM5_CH2  | -            | -              | -              |                     | USART2_RTS | UART4_RX           | -                         | -                  | ETH_MII<br>_RX_CLK<br>ETH_RMII<br>_REF_CLK | -                    | -          | -     | EVENTOUT |

|        | PA2      | -              | TIM2_CH3               | TIM5_CH3  | TIM9_CH1     | -              | -              |                     | USART2_TX  | -                  | -                         | -                  | ETH_MDIO                                   | -                    | -          | -     | EVENTOUT |

|        | PA3      | -              | TIM2_CH4               | TIM5_CH4  | TIM9_CH2     | -              | -              |                     | USART2_RX  | -                  | -                         | OTG_HS_ULPI_D0     | ETH _MII_COL                               | -                    | -          | -     | EVENTOUT |

|        | PA4      | -              | -                      | -         | -            | -              | SPI1_NSS       | SPI3_NSS<br>I2S3_WS | USART2_CK  | -                  | -                         |                    | -                                          | OTG_HS_SOF           | DCMI_HSYNC | -     | EVENTOUT |

|        | PA5      | -              | TIM2_CH1_ETR           | -         | TIM8_CH1N    | -              | SPI1_SCK       | -                   | -          | -                  | -                         | OTG_HS_ULPI_C<br>K | -                                          | -                    | -          | -     | EVENTOUT |

|        | PA6      | -              | TIM1_BKIN              | TIM3_CH1  | TIM8_BKIN    | -              | SPI1_MISO      | -                   | -          | -                  | TIM13_CH1                 | -                  | -                                          | -                    | DCMI_PIXCK | -     | EVENTOUT |

| Port A | PA7      | -              | TIM1_CH1N              | TIM3_CH2  | TIM8_CH1N    | -              | SPI1_MOSI      | -                   | -          | -                  | TIM14_CH1                 | -                  | ETH_MII_RX_DV<br>ETH_RMII<br>_CRS_DV       | -                    | -          | -     | EVENTOUT |

|        | PA8      | MCO1           | TIM1_CH1               | -         | -            | I2C3_SCL       | -              | -                   | USART1_CK  | -                  | -                         | OTG_FS_SOF         | -                                          | -                    | -          | -     | EVENTOUT |

|        | PA9      | -              | TIM1_CH2               | -         | -            | I2C3_SMBA      | -              | -                   | USART1_TX  | -                  | -                         |                    | -                                          | -                    | DCMI_D0    | -     | EVENTOUT |

|        | PA10     | -              | TIM1_CH3               | -         | -            | -              | -              | -                   | USART1_RX  | -                  | -                         | OTG_FS_ID          | -                                          | -                    | DCMI_D1    | -     | EVENTOUT |

|        | PA11     | -              | TIM1_CH4               | -         | -            | -              | -              | -                   | USART1_CTS | -                  | CAN1_RX                   | OTG_FS_DM          | -                                          | -                    | -          | -     | EVENTOUT |

|        | PA12     | -              | TIM1_ETR               | -         | -            | -              | -              | -                   | USART1_RTS | -                  | CAN1_TX                   | OTG_FS_DP          | -                                          | -                    | -          | -     | EVENTOUT |

|        | PA13     | JTMS-<br>SWDIO | -                      | -         | -            | -              | -              | -                   | -          | -                  | -                         | -                  | -                                          | -                    | -          | -     | EVENTOUT |

|        | PA14     | JTCK-<br>SWCLK | -                      | -         | -            | -              | -              | -                   | -          | -                  | -                         | -                  | -                                          | -                    | -          | -     | EVENTOUT |

|        | PA15     | JTDI           | TIM 2_CH1<br>TIM 2_ETR | -         | -            | -              | SPI1_NSS       | SPI3_NSS<br>I2S3 WS | -          | -                  | -                         | -                  | -                                          | -                    | -          | -     | EVENTOUT |

60/10

| Symbol                 | Parameter                   | Conditions                                                            | Min | Тур | Max | Unit |

|------------------------|-----------------------------|-----------------------------------------------------------------------|-----|-----|-----|------|

| f <sub>OSC_IN</sub>    | Oscillator frequency        | -                                                                     | 4   | -   | 26  | MHz  |

| R <sub>F</sub>         | Feedback resistor           | -                                                                     | -   | 200 | -   | kΩ   |

|                        | HSE current consumption     | V <sub>DD</sub> =3.3 V,<br>ESR= 30 Ω,<br>C <sub>L</sub> =5 pF@25 MHz  | -   | 449 | -   |      |

| I <sub>DD</sub>        |                             | V <sub>DD</sub> =3.3 V,<br>ESR= 30 Ω,<br>C <sub>L</sub> =10 pF@25 MHz | -   | 532 | -   | μA   |

| 9 <sub>m</sub>         | Oscillator transconductance | Startup                                                               | 5   | -   | -   | mA/V |

| $t_{\rm SU(HSE}^{(3)}$ | Startup time                | $V_{DD}$ is stabilized                                                | -   | 2   | -   | ms   |

Table 29. HSE 4-26 MHz oscillator characteristics<sup>(1) (2)</sup>

1. Resonator characteristics given by the crystal/ceramic resonator manufacturer.

2. Guaranteed by characterization results, not tested in production.

t<sub>SU(HSE)</sub> is the startup time measured from the moment it is enabled (by software) to a stabilized 8 MHz oscillation is reached. This value is measured for a standard crystal resonator and it can vary significantly with the crystal manufacturer

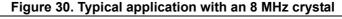

For  $C_{L1}$  and  $C_{L2}$ , it is recommended to use high-quality external ceramic capacitors in the 5 pF to 25 pF range (typ.), designed for high-frequency applications, and selected to match the requirements of the crystal or resonator (see *Figure 30*).  $C_{L1}$  and  $C_{L2}$  are usually the same size. The crystal manufacturer typically specifies a load capacitance which is the series combination of  $C_{L1}$  and  $C_{L2}$ . PCB and MCU pin capacitance must be included (10 pF can be used as a rough estimate of the combined pin and board capacitance) when sizing  $C_{L1}$  and  $C_{L2}$ .

Note:

For information on electing the crystal, refer to the application note AN2867 "Oscillator design guide for ST microcontrollers" available from the ST website <u>www.st.com</u>.

1.  $R_{EXT}$  value depends on the crystal characteristics.

### Low-speed external clock generated from a crystal/ceramic resonator

The low-speed external (LSE) clock can be supplied with a 32.768 kHz crystal/ceramic resonator oscillator. All the information given in this paragraph are based on characterization results obtained with typical external components specified in *Table 30*. In the application, the resonator and the load capacitors have to be placed as close as possible to the oscillator pins in order to minimize output distortion and startup stabilization time. Refer to the crystal resonator manufacturer for more details on the resonator characteristics (frequency, package, accuracy).

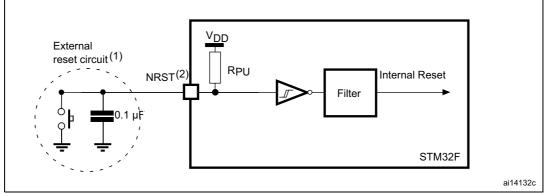

#### 6.3.17 **NRST** pin characteristics

The NRST pin input driver uses CMOS technology. It is connected to a permanent pull-up resistor, R<sub>PU</sub> (see Table 48).

Unless otherwise specified, the parameters given in Table 48 are derived from tests performed under the ambient temperature and  $V_{\text{DD}}$  supply voltage conditions summarized in Table 13.

| Symbol                               | Parameter                                       | Conditions              | Min | Тур | Max | Unit |

|--------------------------------------|-------------------------------------------------|-------------------------|-----|-----|-----|------|

| R <sub>PU</sub>                      | Weak pull-up equivalent resistor <sup>(1)</sup> | $V_{IN} = V_{SS}$       | 30  | 40  | 50  | kΩ   |

| V <sub>F(NRST)</sub> <sup>(2)</sup>  | NRST Input filtered pulse                       | -                       | -   | -   | 100 | ns   |

| V <sub>NF(NRST)</sub> <sup>(2)</sup> | NRST Input not filtered pulse                   | V <sub>DD</sub> > 2.7 V | 300 | -   | -   | ns   |

| T <sub>NRST_OUT</sub>                | Generated reset pulse duration                  | Internal Reset source   | 20  | -   | -   | μs   |

Table 48. NRST pin characteristics

The pull-up is designed with a true resistance in series with a switchable PMOS. This PMOS contribution to the series 1. resistance must be minimum (~10% order).

2. Guaranteed by design, not tested in production.

### Figure 38. Recommended NRST pin protection

- The reset network protects the device against parasitic resets. 1.

- The user must ensure that the level on the NRST pin can go below the V<sub>IL(NRST)</sub> max level specified in 2. Table 48. Otherwise the reset is not taken into account by the device.

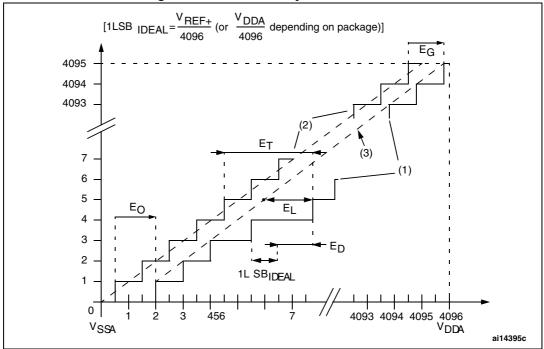

- 1. Example of an actual transfer curve.

- 2. Ideal transfer curve.

- 3. End point correlation line.

E<sub>T</sub> = Total Unadjusted Error: maximum deviation between the actual and the ideal transfer curves.

EO = Offset Error: deviation between the first actual transition and the first ideal one.

EG = Gain Error: deviation between the last ideal transition and the last actual one.

ED = Differential Linearity Error: maximum deviation between any actual steps and the ideal one. EL = Integral Linearity Error: maximum deviation between any actual transition and the end point

EL = Integral Linearity Error: maximum deviation between any actual transition and the end point correlation line.

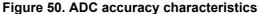

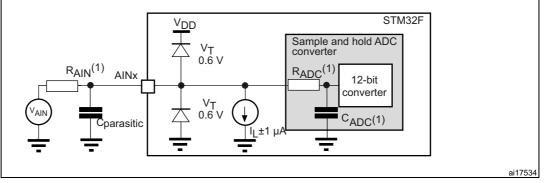

- 1. Refer to Table 65 for the values of  $\mathsf{R}_{\mathsf{AIN}},\,\mathsf{R}_{\mathsf{ADC}}$  and  $\mathsf{C}_{\mathsf{ADC}}.$

- C<sub>parasitic</sub> represents the capacitance of the PCB (dependent on soldering and PCB layout quality) plus the pad capacitance (roughly 7 pF). A high C<sub>parasitic</sub> value downgrades conversion accuracy. To remedy this, f<sub>ADC</sub> should be reduced.

|                               |                                                                                                                       |     |     |     | (******** |                                                                                                        |  |  |

|-------------------------------|-----------------------------------------------------------------------------------------------------------------------|-----|-----|-----|-----------|--------------------------------------------------------------------------------------------------------|--|--|

| Symbol                        | Parameter                                                                                                             | Min | Тур | Мах | Unit      | Comments                                                                                               |  |  |

| Update<br>rate <sup>(1)</sup> | Max frequency for a<br>correct DAC_OUT change<br>when small variation in the<br>input code (from code i to<br>i+1LSB) | -   | -   | 1   | MS/s      | $C_{LOAD} \le 50 \text{ pF},$<br>$R_{LOAD} \ge 5 \text{ k}\Omega$                                      |  |  |

| t <sub>wakeup</sub> (3)       | Wakeup time from off state<br>(Setting the ENx bit in the<br>DAC Control register)                                    | -   | 6.5 | 10  | μs        | $C_{LOAD} \le 50$ pF, $R_{LOAD} \ge 5$ k $\Omega$ input code between lowest and highest possible ones. |  |  |

| PSRR+ <sup>(1)</sup>          | Power supply rejection<br>ratio (to V <sub>DDA</sub> ) (static DC<br>measurement)                                     | -   | -67 | -40 | dB        | No R <sub>LOAD</sub> , C <sub>LOAD</sub> = 50 pF                                                       |  |  |

Table 67. DAC characteristics (continued)

1. Guaranteed by design, not tested in production.

2. The quiescent mode corresponds to a state where the DAC maintains a stable output level to ensure that no dynamic consumption occurs.

3. Guaranteed by characterization results, not tested in production.

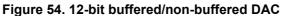

1. The DAC integrates an output buffer that can be used to reduce the output impedance and to drive external loads directly, without the use of an external operational amplifier. The buffer can be bypassed by configuring the BOFFx bit in the DAC\_CR register.

### 6.3.22 Temperature sensor characteristics

### Table 68. Temperature sensor characteristics

| Symbol                             | Parameter                                                      | Min | Тур  | Max       | Unit  |

|------------------------------------|----------------------------------------------------------------|-----|------|-----------|-------|

| T <sub>L</sub> <sup>(1)</sup>      | V <sub>SENSE</sub> linearity with temperature                  | -   | ±1   | <u>+2</u> | °C    |

| Avg_Slope <sup>(1)</sup>           | Average slope                                                  | -   | 2.5  | -         | mV/°C |

| V <sub>25</sub> <sup>(1)</sup>     | Voltage at 25 °C                                               | -   | 0.76 | -         | V     |

| t <sub>START</sub> <sup>(2)</sup>  | Startup time                                                   | -   | 6    | 10        | μs    |

| T <sub>S_temp</sub> <sup>(2)</sup> | ADC sampling time when reading the temperature (1 °C accuracy) | 10  | -    | -         | μs    |

DocID17050 Rev 13

1. Guaranteed by characterization results, not tested in production.

2. Guaranteed by design, not tested in production.

|                           |                                                |     | ge (certainaca) |      |  |

|---------------------------|------------------------------------------------|-----|-----------------|------|--|

| Symbol                    | Parameter                                      | Min | Мах             | Unit |  |

| t <sub>su(ADV-CLKH)</sub> | FSMC_A/D[15:0] valid data before FSMC_CLK high | 5   | -               | ns   |  |

| t <sub>h(CLKH-ADV)</sub>  | FSMC_A/D[15:0] valid data after FSMC_CLK high  | 0   | -               | ns   |  |

|                           |                                                |     |                 |      |  |

### Table 75. Synchronous multiplexed NOR/PSRAM read timings<sup>(1)(2)</sup> (continued)

1. C<sub>L</sub> = 30 pF.

2. Guaranteed by characterization results, not tested in production.

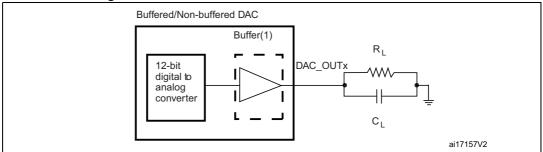

#### Figure 60. Synchronous multiplexed PSRAM write timings

Table 76. Synchronous multiplexed PSRAM write timings<sup>(1)(2)</sup>

| Symbol                     | Parameter                                | Min                    | Max | Unit |

|----------------------------|------------------------------------------|------------------------|-----|------|

| t <sub>w(CLK)</sub>        | FSMC_CLK period                          | 2T <sub>HCLK</sub> - 1 | -   | ns   |

| t <sub>d(CLKL-NExL)</sub>  | FSMC_CLK low to FSMC_NEx low (x=02)      | -                      | 0   | ns   |

| t <sub>d(CLKL-NExH)</sub>  | FSMC_CLK low to FSMC_NEx high (x= 02)    | 2                      | -   | ns   |

| t <sub>d(CLKL-NADVL)</sub> | FSMC_CLK low to FSMC_NADV low            | -                      | 2   | ns   |

| t <sub>d(CLKL-NADVH)</sub> | FSMC_CLK low to FSMC_NADV high           | 3                      | -   | ns   |

| t <sub>d(CLKL-AV)</sub>    | FSMC_CLK low to FSMC_Ax valid (x=1625)   | -                      | 0   | ns   |

| t <sub>d(CLKL-AIV)</sub>   | FSMC_CLK low to FSMC_Ax invalid (x=1625) | 7                      | -   | ns   |

DocID17050 Rev 13

| Symbol                       | Parameter                                 | Min                      | Мах                      | Unit |

|------------------------------|-------------------------------------------|--------------------------|--------------------------|------|

| t <sub>w(NIOWR)</sub>        | FSMC_NIOWR low width                      | 8T <sub>HCLK</sub> - 0.5 | -                        | ns   |

| t <sub>v(NIOWR-D)</sub>      | FSMC_NIOWR low to FSMC_D[15:0] valid      | -                        | 5T <sub>HCLK</sub> - 1   | ns   |

| t <sub>h(NIOWR-D)</sub>      | FSMC_NIOWR high to FSMC_D[15:0] invalid   | 8T <sub>HCLK</sub> - 3   | -                        | ns   |

| t <sub>d(NCE4_1-NIOWR)</sub> | FSMC_NCE4_1 low to FSMC_NIOWR valid       | -                        | 5T <sub>HCLK</sub> + 1.5 | ns   |

| t <sub>h(NCEx-NIOWR)</sub>   | FSMC_NCEx high to FSMC_NIOWR invalid      | 5T <sub>HCLK</sub>       | -                        | ns   |

| t <sub>d(NIORD-NCEx)</sub>   | FSMC_NCEx low to FSMC_NIORD valid         | -                        | 5T <sub>HCLK</sub> + 1   | ns   |

| t <sub>h(NCEx-NIORD)</sub>   | FSMC_NCEx high to FSMC_NIORD) valid       | 5Т <sub>НСLК</sub> – 0.5 | -                        | ns   |

| t <sub>w(NIORD)</sub>        | FSMC_NIORD low width                      | 8T <sub>HCLK</sub> + 1   | -                        | ns   |

| t <sub>su(D-NIORD)</sub>     | FSMC_D[15:0] valid before FSMC_NIORD high | 9.5                      | -                        | ns   |

| t <sub>d(NIORD-D)</sub>      | FSMC_D[15:0] valid after FSMC_NIORD high  | 0                        | -                        | ns   |

| Table 80. Switching characteristics for PC Card/CF read and write cycles in I/O space <sup>(1)</sup> | )(2) |

|------------------------------------------------------------------------------------------------------|------|

|------------------------------------------------------------------------------------------------------|------|

1. C<sub>L</sub> = 30 pF.

2. Guaranteed by characterization results, not tested in production.

### NAND controller waveforms and timings

*Figure 69* through *Figure 72* represent synchronous waveforms, together with *Table 81* and *Table 82* provides the corresponding timings. The results shown in this table are obtained with the following FSMC configuration:

- COM.FSMC\_SetupTime = 0x01;

- COM.FSMC\_WaitSetupTime = 0x03;

- COM.FSMC\_HoldSetupTime = 0x02;

- COM.FSMC\_HiZSetupTime = 0x01;

- ATT.FSMC\_SetupTime = 0x01;

- ATT.FSMC\_WaitSetupTime = 0x03;

- ATT.FSMC\_HoldSetupTime = 0x02;

- ATT.FSMC\_HiZSetupTime = 0x01;

- Bank = FSMC\_Bank\_NAND;

- MemoryDataWidth = FSMC\_MemoryDataWidth\_16b;

- ECC = FSMC\_ECC\_Enable;

- ECCPageSize = FSMC\_ECCPageSize\_512Bytes;

- TCLRSetupTime = 0;

- TARSetupTime = 0;

In all timing tables, the  $T_{HCLK}$  is the HCLK clock period.

| Table 94. Document revision history (continued) |          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |

|-------------------------------------------------|----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Date                                            | Revision | Changes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |

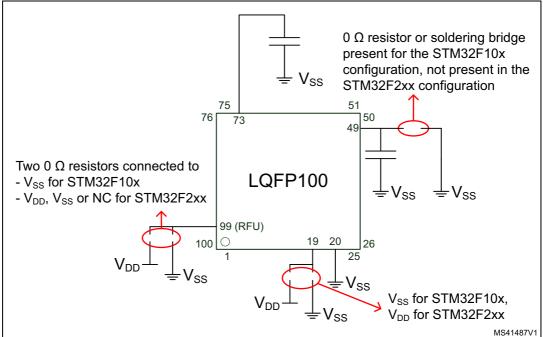

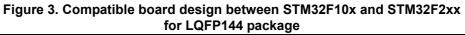

| Date                                            |          | Changes         Changed datasheet status to "Full Datasheet".         APB1 frequency changed form 36 MHz to 30 MHz.         Introduced concept of SRAM1 and SRAM2.         LQFP176 now in production.         Removed WLCSP64+2 package.         Updated Figure 3: Compatible board design between STM32F10x and STM32F2xx for LQFP144 package and Figure 2: Compatible board design between STM32F10x and STM32F2xx for LQFP100 package.         Added camera interface for STM32F217Vx devices in Table 2:         STM32F215xx and STM32F217xx: features and peripheral counts.         Removed 16 MHz internal RC oscillator accuracy in Section 3.12:         Clocks and startup.         Updated Section 3.16: Voltage regulator.         Modified I <sup>2</sup> S sampling frequency range in Section 3.12: Clocks and startup, Section 3.24: Inter-integrated sound (I2S), and Section 3.30:         Audio PLL (PLLI2S).         Updated Section 3.17: Real-time clock (RTC), backup SRAM and backup registers and description of TIM2 and TIM5 in Section 3.20.2:                                                                                                                                                                                                                                                                                                                                                                |  |  |

| 22-Apr-2011                                     | 4        | Modified maximum baud rate (oversampling by 16) for USART1 in<br><i>Table 5: USART feature comparison.</i><br>Updated note related to RFU pin below <i>Figure 10: STM32F21x</i><br><i>LQFP100 pinout, Figure 11: STM32F21x LQFP144 pinout, Figure 12:</i><br><i>STM32F21x LQFP176 pinout, Figure 13: STM32F21x UFBGA176</i><br><i>ballout,</i> and <i>Table 7: STM32F21x pin and ball definitions.</i><br>Added RTC_50Hz as PB15 alternate function, and TT (3.6 V tolerant<br>I/O) in <i>Table 7: STM32F21x pin and ball definitions</i> and <i>Table 9:</i><br><i>Alternate function mapping.</i><br>PA15 added in <i>Table 7: STM32F21x pin and ball definitions.</i><br>In <i>Table 7: STM32F21x pin and ball definitions,</i> changed I2S2_CK and<br>I2S3_CK to I2S2_SCK and I2S3_SCK, respectively.<br>Removed ETH _RMII_TX_CLK for PC3/AF11 in <i>Table 9: Alternate function</i><br><i>mapping.</i><br>Updated <i>Table 10: Voltage characteristics</i> and <i>Table 11: Current</i><br><i>characteristics.</i><br>T <sub>STG</sub> updated to –65 to +150 in <i>Table 12: Thermal characteristics.</i><br>Added CEXT and ESR in <i>Table 13: General operating conditions</i> as well<br>as Section 6.3.2: VCAP1/VCAP2 external capacitor.<br>Modified Note 3 in <i>Table 14: Limitations depending on the operating</i><br><i>power supply range.</i><br>Updated <i>Table 16: Operating conditions at power-up / power-down</i> |  |  |

|                                                 |          | (regulator ON), and Table 17: Operating conditions at power-up / power-<br>down (regulator OFF).<br>Updated notes below and added OSC_OUT pin in Figure 15: Pin<br>loading conditions. and Figure 16: Pin input voltage.<br>Updated V <sub>PVD</sub> , V <sub>BOR1</sub> , V <sub>BOR2</sub> , V <sub>BOR3</sub> , T <sub>RSTTEMPO</sub> typical value, and<br>I <sub>RUSH</sub> , added E <sub>RUSH</sub> and Note 2 in Table 18: Embedded reset and<br>power control block characteristics.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |  |

| Date        | Date     Revision |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |  |

|-------------|-------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Bute        | Revision          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |  |

|             |                   | Updated $t_{res(TIM)}$ in <i>Table 49: Characteristics of TIMx connected to the</i><br><i>APB1 domain</i> . Modified $t_{res(TIM)}$ and $f_{EXT}$ <i>Table 50: Characteristics of</i><br><i>TIMx connected to the APB2 domain</i> .<br>Changed $t_{w(SCKH)}$ to $t_{w(SCLH)}$ , $t_{w(SCKL)}$ to $t_{w(SCLL)}$ , $t_{r(SCK)}$ to $t_{r(SCL)}$ , and                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |  |

|             |                   | $t_{f(SCK)}$ to $t_{f(SCL)}$ in Table 51: I2C characteristics and Figure 39: I2C bus AC waveforms and measurement circuit.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |  |

|             |                   | Added Table 56: USB OTG FS DC electrical characteristics and updated Table 57: USB OTG FS electrical characteristics.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |

|             |                   | Updated V <sub>DD</sub> minimum value in <i>Table 61: Ethernet DC electrical characteristics</i> .                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |

|             |                   | Updated Table 65: ADC characteristics and RAIN equation.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |  |

|             |                   | Updated R <sub>AIN</sub> equation. Updated Table 67: DAC characteristics.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |

|             |                   | Updated t <sub>START</sub> in Table 68: Temperature sensor characteristics.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |

| 22-Apr-2011 |                   | Updated Table 70: Embedded internal reference voltage.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |

|             | 4<br>(continued)  | Modified FSMC_NOE waveform in <i>Figure 55: Asynchronous non-</i><br><i>multiplexed SRAM/PSRAM/NOR read waveforms</i> . Shifted end of<br>FSMC NEx/NADV/addresses/NWE/NOE/NWAIT of a half FSMC CLK                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |

|             |                   | period, changed $t_{d(CLKH-NExH)}$ to $t_{d(CLKL-NEXH)}$ , $t_{d(CLKH-AIV)}$ to $t_{d(CLKL-NEXH)}$ , $t_{d(CLKH-AIV)}$ to $t_{d(CLKL-NOEH)}$ , and $t_{d(CLKH-NWEH)}$ to $t_{d(CLKL-NWEH)}$ , and updated data latency from 1 to 0 in <i>Figure 59: Synchronous multiplexed NOR/PSRAM read timings</i> , <i>Figure 60: Synchronous non-multiplexed NOR/PSRAM read timings</i> , and <i>Figure 62: Synchronous non-multiplexed NOR/PSRAM read timings</i> , and <i>Figure 62: Synchronous non-multiplexed NOR/PSRAM read timings</i> , and <i>Figure 62: Synchronous non-multiplexed NOR/PSRAM read timings</i> , and <i>Figure 62: Synchronous non-multiplexed NOR/PSRAM read timings</i> , and <i>Figure 62: Synchronous non-multiplexed NOR/PSRAM read timings</i> , and <i>Figure 62: Synchronous non-multiplexed NOR/PSRAM read timings</i> , and <i>Figure 62: Synchronous non-multiplexed NOR/PSRAM read timings</i> , and <i>Figure 62: Synchronous non-multiplexed NOR/PSRAM read timings</i> , and <i>Figure 62: Synchronous non-multiplexed NOR/PSRAM read timings</i> , and <i>Figure 62: Synchronous non-multiplexed NOR/PSRAM read timings</i> , and <i>Figure 62: Synchronous non-multiplexed NOR/PSRAM read timings</i> , and <i>Figure 62: Synchronous non-multiplexed NOR/PSRAM read timings</i> , and <i>Figure 62: Synchronous non-multiplexed NOR/PSRAM read timings</i> , and <i>Figure 62: Synchronous non-multiplexed NOR/PSRAM read timings</i> , and <i>Figure 62: Synchronous non-multiplexed NOR/PSRAM read timings</i> , and <i>Figure 62: Synchronous non-multiplexed NOR/PSRAM read timings</i> , and <i>Figure 62: Synchronous non-multiplexed NOR/PSRAM read timings</i> , and <i>Figure 62: Synchronous non-multiplexed NOR/PSRAM read timings</i> , and <i>Figure 62: Synchronous non-multiplexed NOR/PSRAM read timings</i> , and <i>Figure 62: Synchronous non-multiplexed NOR/PSRAM read timings</i> , and <i>Figure 62: Synchronous non-multiplexed NOR/PSRAM read timings</i> , and <i>Figure 63: Synchronous non-multiplexed NOR/PSRAM read timings</i> , and <i>Figure 64: Synchronous non-multiplexed NOR/PSRAM read timings</i> , and <i>Figure 64: Synchronous non-multiplexed NOR/PSRAM read timings</i> , and <i>Figure 64: Synchronous read timi</i> |  |  |