Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                                  |

|----------------------------|-----------------------------------------------------------------------------------------|

| Core Processor             | ARM® Cortex®-M3                                                                         |

| Core Size                  | 32-Bit Single-Core                                                                      |

| Speed                      | 120MHz                                                                                  |

| Connectivity               | CANbus, Ethernet, I <sup>2</sup> C, IrDA, LINbus, Memory Card, SPI, UART/USART, USB OTG |

| Peripherals                | Brown-out Detect/Reset, DMA, I <sup>2</sup> S, LCD, POR, PWM, WDT                       |

| Number of I/O              | 140                                                                                     |

| Program Memory Size        | 1MB (1M x 8)                                                                            |

| Program Memory Type        | FLASH                                                                                   |

| EEPROM Size                | -                                                                                       |

| RAM Size                   | 132K x 8                                                                                |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                                             |

| Data Converters            | A/D 24x12b; D/A 2x12b                                                                   |

| Oscillator Type            | Internal                                                                                |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                       |

| Mounting Type              | Surface Mount                                                                           |

| Package / Case             | 201-UFBGA                                                                               |

| Supplier Device Package    | 176+25UFBGA (10x10)                                                                     |

| Purchase URL               | https://www.e-xfl.com/product-detail/stmicroelectronics/stm32f217igh6                   |

|                            |                                                                                         |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| Reference   | Part numbers                                                                   |  |  |  |  |  |  |

|-------------|--------------------------------------------------------------------------------|--|--|--|--|--|--|

| STM32F215xx | STM32F215RG, STM32F215VG, STM32F215ZG<br>STM32F215RE, STM32F215VE, STM32F215ZE |  |  |  |  |  |  |

| STM32F217xx | STM32F217VG, STM32F217IG, STM32F217ZG<br>STM32F217VE, STM32F217IE, STM32F217ZE |  |  |  |  |  |  |

## Table 1. Device summary

# List of figures

| Figure 1.    | Compatible board design between STM32F10x and STM32F2xx                            |     |

|--------------|------------------------------------------------------------------------------------|-----|

|              | for LQFP64 package                                                                 | 17  |

| Figure 2.    | Compatible board design between STM32F10x and STM32F2xx                            |     |

|              | for LQFP100 package                                                                | 18  |

| Figure 3.    | Compatible board design between STM32F10x and STM32F2xx                            |     |

|              | for LQFP144 package                                                                | 18  |

| Figure 4.    | STM32F21x block diagram                                                            | 19  |

| Figure 5.    | Multi-AHB matrix                                                                   | 22  |

| Figure 6.    | Regulator OFF/internal reset ON                                                    | 27  |

| Figure 7.    | Startup in regulator OFF: slow V <sub>DD</sub> slope,                              |     |

| U U          | power-down reset risen after V <sub>CAP 1</sub> /V <sub>CAP 2</sub> stabilization  | 28  |

| Figure 8.    | Startup in regulator OFF: fast V <sub>DD</sub> slope,                              |     |

| U            | power-down reset risen before V <sub>CAP_1</sub> /V <sub>CAP_2</sub> stabilization | 28  |

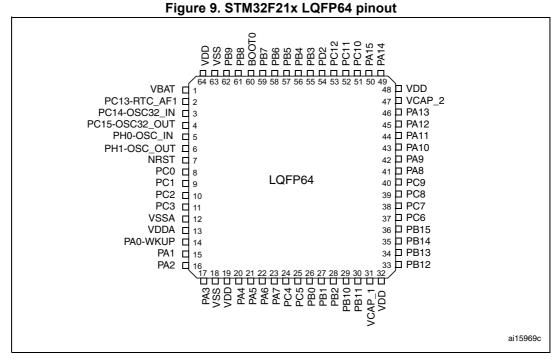

| Figure 9.    | STM32F21x LQFP64 pinout                                                            | 41  |

| Figure 10.   | STM32F21x LQFP100 pinout                                                           |     |

| Figure 11.   | STM32F21x LQFP144 pinout                                                           |     |

| Figure 12.   | STM32F21x LQFP176 pinout                                                           |     |

| Figure 13.   | STM32F21x UFBGA176 ballout                                                         |     |

| Figure 14.   | Memory map.                                                                        |     |

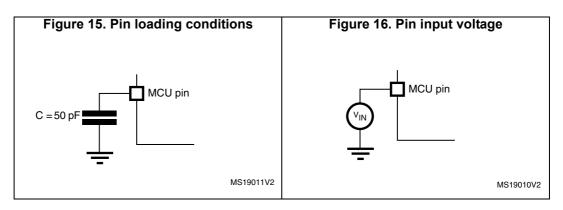

| Figure 15.   | Pin loading conditions.                                                            |     |

| Figure 16.   | Pin input voltage                                                                  |     |

| Figure 17.   | Power supply scheme                                                                |     |

| Figure 18.   | Current consumption measurement scheme                                             |     |

| Figure 19.   | Number of wait states versus $f_{CPU}$ and $V_{DD}$ range                          |     |

| Figure 20.   | External capacitor C <sub>FXT</sub>                                                |     |

| Figure 21.   | Typical current consumption vs. temperature, Run mode, code with data              |     |

| 1 iguro 2 11 | processing running from RAM, and peripherals ON                                    | 80  |

| Figure 22.   | Typical current consumption vs. temperature, Run mode, code with data              |     |

|              | processing running from RAM, and peripherals OFF                                   | 80  |

| Figure 23.   | Typical current consumption vs. temperature, Run mode, code with data              |     |

| 1 igui o 201 | processing running from Flash, ART accelerator OFF, peripherals ON                 | 81  |

| Figure 24.   | Typical current consumption vs. temperature, Run mode, code with data              |     |

| rigaro 2 n.  | processing running from Flash, ART accelerator OFF, peripherals OFF.               | 81  |

| Figure 25.   | Typical current consumption vs. temperature in Sleep mode,                         |     |

| 1 iguro 20.  | peripherals ON                                                                     | 83  |

| Figure 26.   | Typical current consumption vs. temperature in Sleep mode,                         | 00  |

| 1 iguro 20.  | peripherals OFF                                                                    | 83  |

| Figure 27.   | Typical current consumption vs. temperature in Stop mode.                          |     |

| Figure 28.   | High-speed external clock source AC timing diagram                                 |     |

| Figure 29.   | Low-speed external clock source AC timing diagram                                  |     |

| Figure 30.   | Typical application with an 8 MHz crystal                                          |     |

| Figure 31.   | Typical application with a 32.768 kHz crystal                                      |     |

| Figure 32.   | ACC <sub>HSI</sub> versus temperature                                              |     |

| Figure 33.   | ACC <sub>I SI</sub> versus temperature                                             |     |

| Figure 34.   | PLL output clock waveforms in center spread mode                                   |     |

| Figure 35.   | PLL output clock waveforms in down spread mode                                     |     |

| Figure 36.   | FT I/O input characteristics                                                       |     |

| Figure 37.   | I/O AC characteristics definition                                                  |     |

| iguie or.    |                                                                                    | 103 |

## 1 Introduction

This datasheet provides the description of the STM32F215xx and STM32F217xx lines of microcontrollers. For more details on the whole STMicroelectronics STM32 family, refer to *Section 2.1: Full compatibility throughout the family*.

The STM32F215xx and STM32F217xx datasheet should be read in conjunction with the STM32F20x/STM32F21x reference manual. They will be referred to as STM32F21x devices throughout the document.

For information on programming, erasing and protection of the internal Flash memory, refer to the STM32F20x/STM32F21x Flash programming manual (PM0059).

The reference and Flash programming manuals are both available from the STMicroelectronics website *www.st.com*.

For information on the Cortex<sup>®</sup>-M3 core refer to the Cortex<sup>®</sup>-M3 Technical Reference Manual, available from the *www.arm.com* website.

## 4 Pinouts and pin description

1. The above figure shows the package top view.

|        |         | Pins    | ;       |          |                                                      |          |                 |      |                                                                                              |                         |

|--------|---------|---------|---------|----------|------------------------------------------------------|----------|-----------------|------|----------------------------------------------------------------------------------------------|-------------------------|

| LQFP64 | LQFP100 | LQFP144 | LQFP176 | UFBGA176 | Pin name<br>(function after<br>reset) <sup>(1)</sup> | Pin type | I / O structure | Note | Alternate functions                                                                          | Additional<br>functions |

| 38     | 64      | 97      | 116     | G15      | PC7                                                  | I/O      | FT              | -    | I2S3_MCK,<br>TIM8_CH2,SDIO_D7,<br>USART6_RX,<br>DCMI_D1,TIM3_CH2,<br>EVENTOUT                | -                       |

| 39     | 65      | 98      | 117     | G14      | PC8                                                  | I/O      | FT              | -    | TIM8_CH3,SDIO_D0,<br>TIM3_CH3, USART6_CK,<br>DCMI_D2, EVENTOUT                               | -                       |

| 40     | 66      | 99      | 118     | F14      | PC9                                                  | I/O      | FT              | -    | I2S2_CKIN, I2S3_CKIN,<br>MCO2, TIM8_CH4,SDIO_D1,<br>I2C3_SDA, DCMI_D3,<br>TIM3_CH4, EVENTOUT | -                       |

| 41     | 67      | 100     | 119     | F15      | PA8                                                  | I/O      | FT              | -    | MCO1, USART1_CK,<br>TIM1_CH1, I2C3_SCL,<br>OTG_FS_SOF, EVENTOUT                              | -                       |

| 42     | 68      | 101     | 120     | E15      | PA9                                                  | I/O      | FT              | -    | USART1_TX, TIM1_CH2,<br>I2C3_SMBA, DCMI_D0,<br>EVENTOUT                                      | OTG_FS_<br>VBUS         |

| 43     | 69      | 102     | 121     | D15      | PA10                                                 | I/O      | FT              | -    | USART1_RX, TIM1_CH3,<br>OTG_FS_ID,DCMI_D1,<br>EVENTOUT                                       | -                       |

| 44     | 70      | 103     | 122     | C15      | PA11                                                 | I/O      | FT              | -    | USART1_CTS, CAN1_RX,<br>TIM1_CH4, OTG_FS_DM,<br>EVENTOUT                                     | -                       |

| 45     | 71      | 104     | 123     | B15      | PA12                                                 | I/O      | FT              | -    | USART1_RTS, CAN1_TX,<br>TIM1_ETR, OTG_FS_DP,<br>EVENTOUT                                     | -                       |

| 46     | 72      | 105     | 124     | A15      | PA13<br>(JTMS-SWDIO)                                 | I/O      | FT              | -    | JTMS-SWDIO, EVENTOUT                                                                         | -                       |

| 47     | 73      | 106     | 125     | F13      | V <sub>CAP_2</sub>                                   | S        | -               | -    | -                                                                                            | -                       |

| -      | 74      | 107     | 126     | F12      | V <sub>SS</sub>                                      | S        | -               | -    | -                                                                                            |                         |

| 48     | 75      | 108     | 127     | G13      | V <sub>DD</sub>                                      | S        | -               | -    | -                                                                                            | -                       |

| -      | -       | -       | 128     | E12      | PH13                                                 | I/O      | FT              | -    | TIM8_CH1N, CAN1_TX,<br>EVENTOUT                                                              | -                       |

| -      | -       | -       | 129     | E13      | PH14                                                 | I/O      | FT              | -    | TIM8_CH2N, DCMI_D4,<br>EVENTOUT                                                              | -                       |

Table 7. STM32F21x pin and ball definitions (continued)

## 6 Electrical characteristics

## 6.1 Parameter conditions

Unless otherwise specified, all voltages are referenced to V<sub>SS</sub>.

## 6.1.1 Minimum and maximum values

Unless otherwise specified the minimum and maximum values are guaranteed in the worst conditions of ambient temperature, supply voltage and frequencies by tests in production on 100% of the devices with an ambient temperature at  $T_A = 25$  °C and  $T_A = T_A max$  (given by the selected temperature range).

Data based on characterization results, design simulation and/or technology characteristics are indicated in the table footnotes and are not tested in production. Based on characterization, the minimum and maximum values refer to sample tests and represent the mean value plus or minus three times the standard deviation (mean $\pm 3\Sigma$ ).

## 6.1.2 Typical values

Unless otherwise specified, typical data are based on  $T_A = 25$  °C,  $V_{DD} = 3.3$  V (for the 1.8 V  $\leq$ V<sub>DD</sub>  $\leq$ 3.6 V voltage range). They are given only as design guidelines and are not tested.

Typical ADC accuracy values are determined by characterization of a batch of samples from a standard diffusion lot over the full temperature range, where 95% of the devices have an error less than or equal to the value indicated (mean $\pm 2\Sigma$ ).

## 6.1.3 Typical curves

Unless otherwise specified, all typical curves are given only as design guidelines and are not tested.

## 6.1.4 Loading capacitor

The loading conditions used for pin parameter measurement are shown in *Figure 15*.

### 6.1.5 Pin input voltage

The input voltage measurement on a pin of the device is described in *Figure 16*.

| Symbol                                 | Parameter                                                                                                          | Conditions                                               | Min  | Max                  | Unit |

|----------------------------------------|--------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------|------|----------------------|------|

| $V_{DD}$                               | Standard operating voltage                                                                                         | -                                                        | 1.8  | 3.6                  |      |

| V <sub>DDA</sub> <sup>(1)</sup>        | Analog operating voltage<br>(ADC limited to 1 M samples)                                                           | Must be the same potential as $V_{DD}^{(2)}$             | 1.8  | 3.6                  |      |

| V DDA                                  | Analog operating voltage<br>(ADC limited to 2 M samples)                                                           |                                                          | 2.4  | 3.6                  |      |

| $V_{BAT}$                              | Backup operating voltage                                                                                           | 1.65                                                     | 3.6  |                      |      |

|                                        | Input voltage on RST and FT pins                                                                                   | $2 \text{ V} \le \text{V}_{\text{DD}} \le 3.6 \text{ V}$ | -0.3 | 5.5                  | V    |

| V                                      | input voltage on KST and FT pins                                                                                   | $1.7 \text{ V} \le \text{V}_{\text{DD}} \le 2 \text{ V}$ | -0.3 | 5.2                  |      |

| V <sub>IN</sub>                        | Input voltage on TTa pins                                                                                          | -                                                        | -0.3 | V <sub>DD</sub> +0.3 |      |

|                                        | Input voltage on BOOT0 pin                                                                                         | -                                                        | 0    | 9                    |      |

| V <sub>CAP1</sub><br>V <sub>CAP2</sub> | Internal core voltage to be supplied externally in REGOFF mode                                                     | -                                                        | 1.1  | 1.3                  |      |

|                                        |                                                                                                                    | LQFP64                                                   | -    | 444                  |      |

|                                        | Power dissipation at T <sub>A</sub> = 85 °C for<br>suffix 6 or T <sub>A</sub> = 105 °C for suffix 7 <sup>(3)</sup> | LQFP100                                                  | -    | 434                  |      |

| PD                                     |                                                                                                                    | LQFP144                                                  | -    | 500                  | mW   |

|                                        |                                                                                                                    | LQFP176                                                  | -    | 526                  |      |

|                                        |                                                                                                                    | UFBGA176                                                 | -    | 513                  |      |

|                                        | Ambient temperature for 6 suffix                                                                                   | Maximum power dissipation                                | -40  | 85                   | °C   |

| T.                                     | version                                                                                                            | Low-power dissipation <sup>(4)</sup>                     | -40  | 105                  | C    |

| ΤΑ                                     | Ambient temperature for 7 suffix                                                                                   | Maximum power dissipation                                | -40  | 105                  | °C   |

|                                        | version                                                                                                            | Low-power dissipation <sup>(4)</sup>                     | -40  | 125                  |      |

| TJ                                     | Junction temperature range                                                                                         | 6 suffix version                                         | -40  | 105                  | °C   |

| IJ                                     |                                                                                                                    | 7 suffix version                                         | -40  | 125                  |      |

Table 13. General operating conditions (continued)

1. When the ADC is used, refer to *Table 65: ADC characteristics*.

2. It is recommended to power V<sub>DD</sub> and V<sub>DDA</sub> from the same source. A maximum difference of 300 mV between V<sub>DD</sub> and V<sub>DDA</sub> can be tolerated during power-up and power-down operation.

3. If  $T_A$  is lower, higher  $\mathsf{P}_D$  values are allowed as long as  $T_J$  does not exceed  $T_{Jmax}.$

4. In low-power dissipation state,  $T_A$  can be extended to this range as long as  $T_J$  does not exceed  $T_{Jmax}$ .

|                                                  | Table 14. Linimations depending on the operating power supply range |                                                                               |                                                                                                              |                                                                                                |                                                                                                                                                                                                                                                               |                                                  |  |  |

|--------------------------------------------------|---------------------------------------------------------------------|-------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------|--|--|

| Operating<br>power<br>supply<br>range            | ADC<br>operation                                                    | Maximum<br>Flash<br>memory<br>access<br>frequency<br>(f <sub>Flashmax</sub> ) | Number of wait<br>states at<br>maximum CPU<br>frequency<br>(f <sub>CPUmax</sub> =<br>120 MHz) <sup>(1)</sup> | I/O operation                                                                                  | FSMC_CLK<br>frequency for<br>synchronous<br>accesses                                                                                                                                                                                                          | Possible<br>Flash<br>memory<br>operations        |  |  |

| V <sub>DD</sub> =1.8 to<br>2.1 V                 | Conversion<br>time up to<br>1 Msps                                  | 16 MHz with<br>no Flash<br>memory wait<br>state                               | 7 <sup>(2)</sup>                                                                                             | <ul> <li>Degraded<br/>speed<br/>performance</li> <li>No I/O<br/>compensation</li> </ul>        | Up to 30 MHz                                                                                                                                                                                                                                                  | 8-bit erase<br>and program<br>operations<br>only |  |  |

| V <sub>DD</sub> = 2.1 to<br>2.4 V                | Conversion<br>time up to<br>1 Msps                                  | 18 MHz with<br>no Flash<br>memory wait<br>state                               | 6 <sup>(2)</sup>                                                                                             | <ul> <li>Degraded<br/>speed<br/>performance</li> <li>No I/O<br/>compensation</li> </ul>        | Up to 30 MHz                                                                                                                                                                                                                                                  | 16-bit erase<br>and program<br>operations        |  |  |

| V <sub>DD</sub> = 2.4 to<br>2.7 V                | Conversion<br>time up to<br>2 Msps                                  | 24 MHz with<br>no Flash<br>memory wait<br>state                               | 4 <sup>(2)</sup>                                                                                             | <ul> <li>Degraded<br/>speed<br/>performance</li> <li>I/O<br/>compensation<br/>works</li> </ul> | Up to 48 MHz                                                                                                                                                                                                                                                  | 16-bit erase<br>and program<br>operations        |  |  |

| V <sub>DD</sub> = 2.7 to<br>3.6 V <sup>(3)</sup> | Conversion<br>time up to<br>2 Msps                                  | 30 MHz with<br>no Flash<br>memory wait<br>state                               | 3 <sup>(2)</sup>                                                                                             | <ul> <li>Full-speed<br/>operation</li> <li>I/O<br/>compensation<br/>works</li> </ul>           | $\begin{array}{l} - \mbox{ Up to } \\ 60 \mbox{ MHz } \\ \mbox{ when } \mbox{ V}_{\mbox{DD}} = \\ 3.0 \mbox{ to } 3.6 \mbox{ V} \\ - \mbox{ Up to } \\ 48 \mbox{ MHz } \\ \mbox{ when } \mbox{ V}_{\mbox{DD}} = \\ 2.7 \mbox{ to } 3.0 \mbox{ V} \end{array}$ | 32-bit erase<br>and program<br>operations        |  |  |

Table 14. Limitations depending on the operating power supply range

1. The number of wait states can be reduced by reducing the CPU frequency (see *Figure 19*).

2. Thanks to the ART accelerator and the 128-bit Flash memory, the number of wait states given here does not impact the execution speed from Flash memory since the ART accelerator allows to achieve a performance equivalent to 0 wait state program execution.

3. The voltage range for OTG USB FS can drop down to 2.7 V. However it is degraded between 2.7 and 3 V.

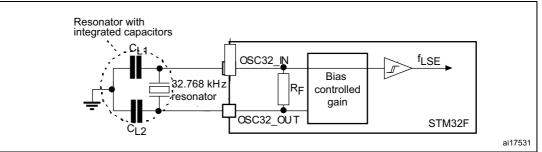

| Symbol                              | Parameter                   | Conditions                    | Min | Тур  | Max | Unit |  |  |  |

|-------------------------------------|-----------------------------|-------------------------------|-----|------|-----|------|--|--|--|

| R <sub>F</sub>                      | Feedback resistor           | -                             | -   | 18.4 | -   | MΩ   |  |  |  |

| I <sub>DD</sub>                     | LSE current consumption     | -                             | -   | -    | 1   | μA   |  |  |  |

| 9 <sub>m</sub>                      | Oscillator Transconductance | -                             | 2.8 | -    | -   | µA/V |  |  |  |

| t <sub>SU(LSE)</sub> <sup>(2)</sup> | startup time                | $V_{\text{DD}}$ is stabilized | -   | 2    | -   | s    |  |  |  |

Table 30. LSE oscillator characteristics ( $f_{LSE}$  = 32.768 kHz) <sup>(1)</sup>

1. Guaranteed by design, not tested in production.

t<sub>SU(LSE)</sub> is the startup time measured from the moment it is enabled (by software) to a stabilized 32.768 kHz oscillation is reached. This value is measured for a standard crystal resonator and it can vary significantly with the crystal manufacturer

Note: For information on electing the crystal, refer to the application note AN2867 "Oscillator design guide for ST microcontrollers" available from the ST website <u>www.st.com</u>.

Figure 31. Typical application with a 32.768 kHz crystal

## 6.3.9 Internal clock source characteristics

The parameters given in *Table 31* and *Table 32* are derived from tests performed under ambient temperature and  $V_{DD}$  supply voltage conditions summarized in *Table 13*.

#### High-speed internal (HSI) RC oscillator

| Symbol                              | Parameter                             | Conditions                           | Min | Тур | Max | Unit |  |  |  |

|-------------------------------------|---------------------------------------|--------------------------------------|-----|-----|-----|------|--|--|--|

| f <sub>HSI</sub>                    | Frequency                             | -                                    | -   | 16  | -   | MHz  |  |  |  |

| 100                                 | HSI user-trimming step <sup>(2)</sup> | -                                    | -   | -   | 1   | %    |  |  |  |

|                                     |                                       | $T_A = -40$ to 105 °C <sup>(3)</sup> | - 8 | -   | 4.5 | %    |  |  |  |

|                                     | Accuracy of the<br>HSI oscillator     | $T_A = -10$ to 85 °C <sup>(3)</sup>  | - 4 | -   | 4   | %    |  |  |  |

|                                     |                                       | $T_A = 25 \ ^{\circ}C^{(4)}$         | – 1 | -   | 1   | %    |  |  |  |

| t <sub>su(HSI)</sub> <sup>(2)</sup> | HSI oscillator startup time           | -                                    | -   | 2.2 | 4.0 | μs   |  |  |  |

| I <sub>DD(HSI)</sub> <sup>(2)</sup> | HSI oscillator power consumption      | -                                    | -   | 60  | 80  | μA   |  |  |  |

Table 31. HSI oscillator characteristics <sup>(1)</sup>

1.  $V_{DD}$  = 3.3 V, T<sub>A</sub> = -40 to 105 °C unless otherwise specified.

2. Guaranteed by design, not tested in production.

- 3. Guaranteed by characterization results.

- 4. Factory calibrated, parts not soldered.

| Symbol                          | Parameter                                        | Conditions                   | Min <sup>(1)</sup> | Тур | Max <sup>(1)</sup> | Unit |

|---------------------------------|--------------------------------------------------|------------------------------|--------------------|-----|--------------------|------|

| t <sub>prog</sub>               | Double word programming                          |                              | -                  | 16  | 100 <sup>(2)</sup> | μs   |

| t <sub>ERASE16KB</sub>          | Sector (16 KB) erase time                        | T <sub>A</sub> = 0 to +40 °C | -                  | 230 | -                  |      |

| t <sub>ERASE64KB</sub>          | Sector (64 KB) erase time                        | V <sub>DD</sub> = 3.3 V      | -                  | 490 | -                  | ms   |

| t <sub>ERASE128KB</sub>         | Sector (128 KB) erase time                       | V <sub>PP</sub> = 8.5 V      | -                  | 875 | -                  |      |

| t <sub>ME</sub>                 | Mass erase time                                  |                              | -                  | 6.9 | -                  | S    |

| V <sub>prog</sub>               | Programming voltage                              | -                            | 2.7                | -   | 3.6                | V    |

| V <sub>PP</sub>                 | V <sub>PP</sub> voltage range                    | -                            | 7                  | -   | 9                  | V    |

| I <sub>PP</sub>                 | Minimum current sunk on the $V_{\rm PP}$ pin     | -                            | 10                 | -   | -                  | mA   |

| t <sub>VPP</sub> <sup>(3)</sup> | Cumulative time during which $V_{PP}$ is applied | -                            | -                  | -   | 1                  | hour |

| Table 38. | Flash | memory | programming | with | V <sub>PP</sub> |

|-----------|-------|--------|-------------|------|-----------------|

|-----------|-------|--------|-------------|------|-----------------|

1. Guaranteed by design, not tested in production.

2. The maximum programming time is measured after 100K erase operations.

3.  $V_{PP}$  should only be connected during programming/erasing.

| Symbol           | Parameter | Conditions                                                                              | Value<br>Min <sup>(1)</sup> | Unit    |

|------------------|-----------|-----------------------------------------------------------------------------------------|-----------------------------|---------|

| N <sub>END</sub> | Endurance | $T_A = -40$ to +85 °C (6 suffix versions)<br>$T_A = -40$ to +105 °C (7 suffix versions) | 10                          | kcycles |

|                  |           | 1 kcycle <sup>(2)</sup> at T <sub>A</sub> = 85 °C                                       | 30                          |         |

| t <sub>RET</sub> |           | 1 kcycle <sup>(2)</sup> at T <sub>A</sub> = 105 °C                                      | 10                          | Years   |

|                  |           | 10 kcycles <sup>(2)</sup> at T <sub>A</sub> = 55 °C                                     | 20                          |         |

#### Table 39. Flash memory endurance and data retention

1. Guaranteed by characterization results, not tested in production.

2. Cycling performed over the whole temperature range.

## 6.3.13 EMC characteristics

Susceptibility tests are performed on a sample basis during device characterization.

### Functional EMS (electromagnetic susceptibility)

While a simple application is executed on the device (toggling 2 LEDs through I/O ports). the device is stressed by two electromagnetic events until a failure occurs. The failure is indicated by the LEDs:

- Electrostatic discharge (ESD) (positive and negative) is applied to all device pins until a functional disturbance occurs. This test is compliant with the IEC 61000-4-2 standard.

- **FTB**: A burst of fast transient voltage (positive and negative) is applied to V<sub>DD</sub> and V<sub>SS</sub> through a 100 pF capacitor, until a functional disturbance occurs. This test is compliant with the IEC 61000-4-4 standard.

A device reset allows normal operations to be resumed.

DocID17050 Rev 13

#### Static latch-up

Two complementary static tests are required on six parts to assess the latch-up performance:

- A supply overvoltage is applied to each power supply pin

- A current injection is applied to each input, output and configurable I/O pin

These tests are compliant with EIA/JESD 78A IC latch-up standard.

| Symbol | Parameter             | Conditions                                     | Class      |

|--------|-----------------------|------------------------------------------------|------------|

| LU     | Static latch-up class | $T_A = +105 \ ^{\circ}C$ conforming to JESD78A | II level A |

## 6.3.15 I/O current injection characteristics

As a general rule, current injection to the I/O pins, due to external voltage below  $V_{SS}$  or above  $V_{DD}$  (for standard, 3 V-capable I/O pins) should be avoided during normal product operation. However, in order to give an indication of the robustness of the microcontroller in cases when abnormal injection accidentally happens, susceptibility tests are performed on a sample basis during device characterization.

#### Functional susceptibility to I/O current injection

While a simple application is executed on the device, the device is stressed by injecting current into the I/O pins programmed in floating input mode. While current is injected into the I/O pin, one at a time, the device is checked for functional failures.

The failure is indicated by an out of range parameter: ADC error above a certain limit (>5 LSB TUE), out of spec current injection on adjacent pins or other functional failure (for example reset, oscillator frequency deviation).

The test results are given in Table 44.

|                  |                                           | Functional s       |                    |      |  |

|------------------|-------------------------------------------|--------------------|--------------------|------|--|

| Symbol           | Description                               | Negative injection | Positive injection | Unit |  |

|                  | Injected current on BOOT0 pin             | -0                 | NA                 |      |  |

|                  | Injected current on NRST pin              | -0                 | NA                 | mA   |  |

| I <sub>INJ</sub> | Injected current on TTa pins: PA4 and PA5 | -0                 | +5                 | mA   |  |

|                  | Injected current on all FT pins           | -5                 | NA                 |      |  |

## Table 44. I/O current injection susceptibility<sup>(1)</sup>

1. NA stands for "not applicable".

Note: It is recommended to add a Schottky diode (pin to ground) to analog pins which may potentially inject negative currents.

| Symbol                                                       | Parameter                                 | Conditions                                                                                 | Min     | Max                             | Unit |

|--------------------------------------------------------------|-------------------------------------------|--------------------------------------------------------------------------------------------|---------|---------------------------------|------|

| f <sub>CK</sub><br>1/t <sub>c(CK)</sub>                      | I <sup>2</sup> S clock frequency          | Master, 16-bit data,<br>audio frequency = 48 kHz, main<br>clock disabled                   | 1.23    | 1.24                            | MHz  |

|                                                              |                                           | Slave                                                                                      | 0       | 64F <sub>S</sub> <sup>(1)</sup> |      |

| t <sub>r(CK)</sub><br>t <sub>f(CK)</sub>                     | I <sup>2</sup> S clock rise and fall time | Capacitive load $C_L = 50 \text{ pF}$                                                      | -       | (2)                             |      |

| t <sub>v(WS)</sub> <sup>(3)</sup>                            | WS valid time                             | Master                                                                                     | 0.3     | -                               |      |

| t <sub>h(WS)</sub> <sup>(3)</sup>                            | WS hold time                              | Master                                                                                     | 0       | -                               |      |

| t <sub>su(WS)</sub> <sup>(3)</sup>                           | WS setup time                             | Slave                                                                                      | 3       | -                               |      |

| t <sub>h(WS)</sub> <sup>(3)</sup>                            | WS hold time                              | Slave                                                                                      | 0       | -                               |      |

| t <sub>w(CKH)</sub> (3)<br>t <sub>w(CKL)</sub> (3)           | CK high and low time                      | Master f <sub>PCLK</sub> = 30 MHz                                                          | 396     | -                               | •    |

| $t_{su(SD\_MR)}^{(3)}_{(3)}$<br>$t_{su(SD\_SR)}^{(3)}$       | Data input setup time                     | Master receiver<br>Slave receiver                                                          | 45<br>0 | -                               | ns   |

| t <sub>h(SD_MR)</sub> (3)(4)<br>t <sub>h(SD_SR)</sub> (3)(4) | Data input hold time                      | Master receiver: f <sub>PCLK</sub> = 30 MHz,<br>Slave receiver: f <sub>PCLK</sub> = 30 MHz | 13<br>0 | -                               | *    |

| t <sub>v(SD_ST)</sub> (3)(4)                                 | Data output valid time                    | Slave transmitter (after enable edge)                                                      | -       | 30                              | *    |

| t <sub>h(SD_ST)</sub> <sup>(3)</sup>                         | Data output hold time                     | Slave transmitter (after enable edge)                                                      | 10      | -                               | •    |

| t <sub>v(SD_MT)</sub> <sup>(3)(4)</sup>                      | Data output valid time                    | Master transmitter (after enable edge)                                                     | -       | 6                               | 1    |

| t <sub>h(SD_MT)</sub> <sup>(3)</sup>                         | Data output hold time                     | Master transmitter (after enable edge)                                                     | 0       | -                               |      |

## Table 54. I<sup>2</sup>S characteristics

F<sub>S</sub> is the sampling frequency. Refer to the I2S section of the STM32F20xxx/21xxx reference manual for more details. f<sub>CK</sub> values reflect only the digital peripheral behavior which leads to a minimum of (I2SDIV/(2\*I2SDIV+ODD), a maximum of (I2SDIV+ODD)/(2\*I2SDIV+ODD) and F<sub>S</sub> maximum values for each mode/condition.

2. Refer to Table 47: I/O AC characteristics.

3. Guaranteed by design, not tested in production.

4. Depends on  $f_{PCLK}$ . For example, if  $f_{PCLK}$ =8 MHz, then  $T_{PCLK}$  = 1/ $f_{PLCLK}$  =125 ns.

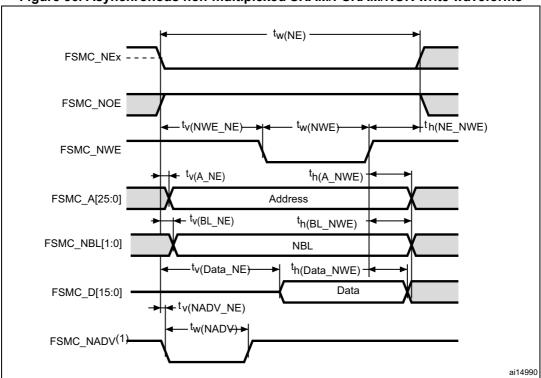

Figure 56. Asynchronous non-multiplexed SRAM/PSRAM/NOR write waveforms

1. Mode 2/B, C and D only. In Mode 1, FSMC\_NADV is not used.

| Table 72. / | Asynchronous non-multiplexed SRA | M/PSRAM/NO | R write timin | gs <sup>(1)(2)</sup> |

|-------------|----------------------------------|------------|---------------|----------------------|

|             |                                  |            |               |                      |

| Symbol                   | Parameter                                | Min                     | Max                     | Unit |

|--------------------------|------------------------------------------|-------------------------|-------------------------|------|

| t <sub>w(NE)</sub>       | FSMC_NE low time                         | 3T <sub>HCLK</sub>      | 3T <sub>HCLK</sub> + 4  | ns   |

| t <sub>v(NWE_NE</sub> )  | FSMC_NEx low to FSMC_NWE low             | T <sub>HCLK</sub> – 0.5 | T <sub>HCLK</sub> + 0.5 | ns   |

| t <sub>w(NWE)</sub>      | FSMC_NWE low time                        | T <sub>HCLK</sub> – 0.5 | T <sub>HCLK</sub> + 3   | ns   |

| t <sub>h(NE_NWE)</sub>   | FSMC_NWE high to FSMC_NE high hold time  | T <sub>HCLK</sub>       | -                       | ns   |

| t <sub>v(A_NE)</sub>     | FSMC_NEx low to FSMC_A valid             | -                       | 0                       | ns   |

| t <sub>h(A_NWE)</sub>    | Address hold time after FSMC_NWE high    | T <sub>HCLK</sub> - 3   | -                       | ns   |

| t <sub>v(BL_NE)</sub>    | FSMC_NEx low to FSMC_BL valid            | -                       | 0.5                     | ns   |

| t <sub>h(BL_NWE)</sub>   | FSMC_BL hold time after FSMC_NWE<br>high | T <sub>HCLK</sub> – 1   | -                       | ns   |

| t <sub>v(Data_NE)</sub>  | Data to FSMC_NEx low to Data valid       | -                       | T <sub>HCLK</sub> + 5   | ns   |

| t <sub>h(Data_NWE)</sub> | Data hold time after FSMC_NWE high       | T <sub>HCLK</sub> +0.5  | -                       | ns   |

| t <sub>v(NADV_NE)</sub>  | FSMC_NEx low to FSMC_NADV low            | -                       | 2                       | ns   |

| t <sub>w(NADV)</sub>     | FSMC_NADV low time                       | -                       | T <sub>HCLK</sub> + 1.5 | ns   |

1. C<sub>L</sub> = 30 pF.

2. Guaranteed by characterization results, not tested in production.

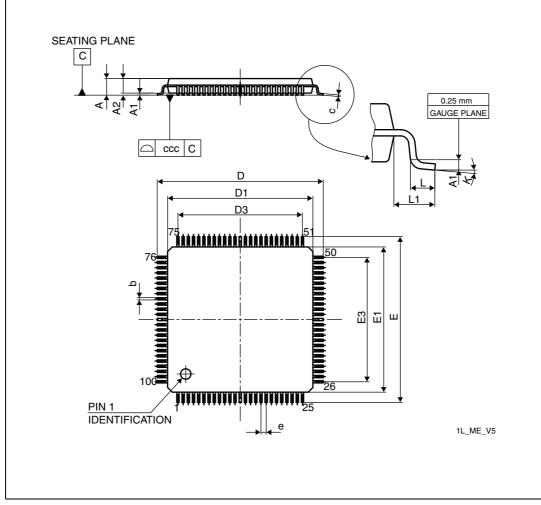

## 7.2 LQFP100 package information

Figure 77. LQFP100 - 100-pin, 14 x 14 mm low-profile quad flat package outline

1. Drawing is not to scale.

| mechanical data |        |             |        |        |                       |        |

|-----------------|--------|-------------|--------|--------|-----------------------|--------|

| Symphol         |        | millimeters |        |        | inches <sup>(1)</sup> |        |

| Symbol          | Min    | Тур         | Max    | Min    | Тур                   | Max    |

| А               | -      | -           | 1.600  | -      | -                     | 0.0630 |

| A1              | 0.050  | -           | 0.150  | 0.0020 | -                     | 0.0059 |

| A2              | 1.350  | 1.400       | 1.450  | 0.0531 | 0.0551                | 0.0571 |

| b               | 0.170  | 0.220       | 0.270  | 0.0067 | 0.0087                | 0.0106 |

| С               | 0.090  | -           | 0.200  | 0.0035 | -                     | 0.0079 |

| D               | 15.800 | 16.000      | 16.200 | 0.6220 | 0.6299                | 0.6378 |

| D1              | 13.800 | 14.000      | 14.200 | 0.5433 | 0.5512                | 0.5591 |

Table 87. LQPF100 - 100-pin, 14 x 14 mm low-profile quad flat package mechanical data

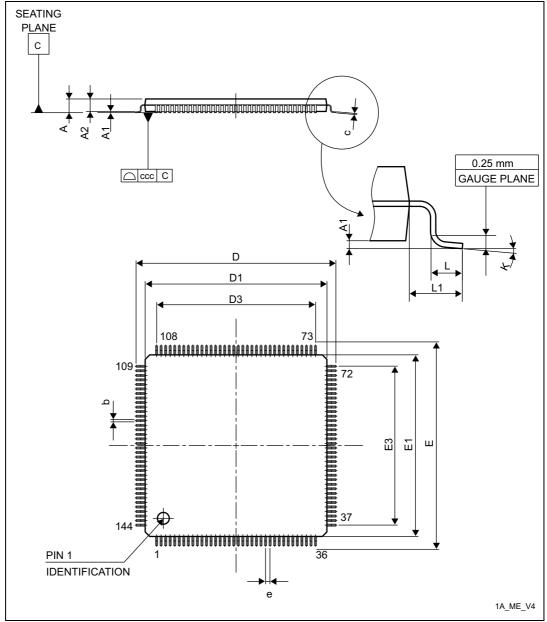

## 7.3 LQFP144 package information

Figure 80. LQFP144 - 144-pin, 20 x 20 mm low-profile quad flat package outline

1. Drawing is not to scale.

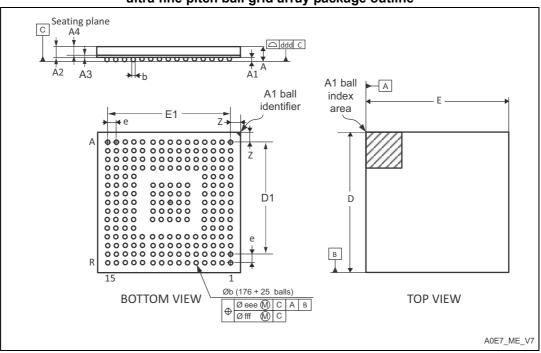

## 7.5 UFBGA176+25 package information

Figure 85. UFBGA176+25 - 201-ball, 10 x 10 mm, 0.65 mm pitch, ultra fine pitch ball grid array package outline

1. Drawing is not to scale.

# Table 90. UFBGA176+25, - 201-ball, 10 x 10 mm, 0.65 mm pitch, ultra fine pitch ball grid array package mechanical data

| Symbol | millimeters |        |        |        | inches <sup>(1)</sup> |        |

|--------|-------------|--------|--------|--------|-----------------------|--------|

| Symbol | Min         | Тур    | Мах    | Min    | Тур                   | Мах    |

| А      | -           | -      | 0.600  | -      | -                     | 0.0236 |

| A1     | -           | -      | 0.110  | -      | -                     | 0.0043 |

| A2     | -           | 0.450  | -      | -      | 0.0177                | -      |

| A3     | -           | 0.130  | -      | -      | 0.0051                | 0.0094 |

| A4     | -           | 0.320  | -      | -      | 0.0126                | -      |

| b      | 0.240       | 0.290  | 0.340  | 0.0094 | 0.0114                | 0.0134 |

| D      | 9.850       | 10.000 | 10.150 | 0.3878 | 0.3937                | 0.3996 |

| D1     | -           | 9.100  | -      | -      | 0.3583                | -      |

| E      | 9.850       | 10.000 | 10.150 | 0.3878 | 0.3937                | 0.3996 |

| E1     | -           | 9.100  | -      | -      | 0.3583                | -      |

| е      | -           | 0.650  | -      | -      | 0.0256                | -      |

| Z      | -           | 0.450  | -      | -      | 0.0177                | -      |

| ddd    | -           | -      | 0.080  | -      | -                     | 0.0031 |

## 7.6 Thermal characteristics

The maximum chip-junction temperature,  $T_{\rm J}$  max, in degrees Celsius, may be calculated using the following equation:

$$T_J max = T_A max + (P_D max x \Theta_{JA})$$

Where:

- T<sub>A</sub> max is the maximum ambient temperature in °C,

- $\Theta_{JA}$  is the package junction-to-ambient thermal resistance, in ° C/W,

- P<sub>D</sub> max is the sum of P<sub>INT</sub> max and P<sub>I/O</sub> max (P<sub>D</sub> max = P<sub>INT</sub> max + P<sub>I/O</sub>max),

- P<sub>INT</sub> max is the product of I<sub>DD</sub> and V<sub>DD</sub>, expressed in Watts. This is the maximum chip internal power.

P<sub>I/O</sub> max represents the maximum power dissipation on output pins where:

$\mathsf{P}_{\mathsf{I}/\mathsf{O}} \max = \Sigma \; (\mathsf{V}_{\mathsf{OL}} \times \mathsf{I}_{\mathsf{OL}}) + \Sigma ((\mathsf{V}_{\mathsf{DD}} - \mathsf{V}_{\mathsf{OH}}) \times \mathsf{I}_{\mathsf{OH}}),$

taking into account the actual V\_{OL} / I\_{OL} and V\_{OH} / I\_{OH} of the I/Os at low and high level in the application.

| Symbol        | Parameter                                                                    | Value | Unit |

|---------------|------------------------------------------------------------------------------|-------|------|

|               | Thermal resistance junction-ambient<br>LQFP 64 - 10 × 10 mm / 0.5 mm pitch   | 45    |      |

|               | Thermal resistance junction-ambient<br>LQFP100 - 14 × 14 mm / 0.5 mm pitch   | 46    |      |

| $\Theta_{JA}$ | Thermal resistance junction-ambient<br>LQFP144 - 20 × 20 mm / 0.5 mm pitch40 |       | °C/W |

|               | Thermal resistance junction-ambient<br>LQFP176 - 24 × 24 mm / 0.5 mm pitch38 |       |      |

|               | Thermal resistance junction-ambient39UFBGA176 - 10× 10 mm / 0.5 mm pitch39   |       |      |

| Table 92. | Package | thermal | characteristics |

|-----------|---------|---------|-----------------|

|-----------|---------|---------|-----------------|

### **Reference document**

JESD51-2 Integrated Circuits Thermal Test Method Environment Conditions - Natural Convection (Still Air). Available from www.jedec.org.

| Date        | Revision         | Changes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|-------------|------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|             |                  | Updated Typical and maximum current consumption conditions, as well<br>as Table 20: Typical and maximum current consumption in Run mode,<br>code with data processing running from Flash memory (ART<br>accelerator disabled) and Table 19: Typical and maximum current<br>consumption in Run mode, code with data processing running from<br>Flash memory (ART accelerator enabled) or RAM. Added Figure 21,<br>Figure 22, Figure 23, and Figure 24.<br>Updated Table 21: Typical and maximum current consumption in Sleep<br>mode, and added Figure 25 and Figure 26.<br>Updated Table 23: Typical and maximum current consumptions in<br>Standby mode and Table 24: Typical and maximum current<br>consumptions in VBAT mode.<br>Updated Table 22: Typical and maximum current consumptions in Stop<br>mode. Added Figure 27: Typical current consumption vs. temperature in<br>Stop mode.<br>Updated Table 23: Typical and maximum current consumptions in Stop<br>mode. Added Figure 27: Typical and maximum current<br>consumptions in VBAT mode.<br>Updated Table 23: Typical and maximum current consumptions in Stop<br>mode. Added Figure 27: Typical current consumption vs. temperature in<br>Stop mode.<br>Updated Table 23: Typical and maximum current<br>consumptions in VBAT mode.<br>Updated On-chip peripheral current consumption conditions and<br>Table 25: Peripheral current consumption.<br>Updated t <sub>WUSTDBY</sub> and t <sub>WUSTOP</sub> and added Note 3 in Table 26: Low-<br>power mode wakeup timings.<br>Maximum f <sub>HSE_ext</sub> and minimum t <sub>w(HSE)</sub> values updated in Table 27:<br>High-speed external user clock characteristics.<br>Updated C and g <sub>m</sub> in Table 29: HSE 4-26 MHz oscillator characteristics. |

| 22-Apr-2011 | 4<br>(continued) | High-speed external user clock characteristics.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|             |                  | Updated $f_{LSI}$ , $t_{su(LSI)}$ and IDD <sub>(LSI)</sub> in <i>Table 32: LSI oscillator characteristics</i> .<br><i>Table 33: Main PLL characteristics</i> : removed note 1, updated $t_{LOCK}$ , jitter, IDD <sub>(PLL)</sub> and IDD <sub>A(PLL)</sub> , added <i>Note 2</i> for $f_{PLL_IN}$ minimum and maximum values.<br><i>Table 34: PLLI2S (audio PLL) characteristics</i> : removed note 1, updated $t_{LOCK}$ , jitter, IDD <sub>(PLLI2S)</sub> and IDD <sub>A(PLLI2S)</sub> , added <i>Note 2</i> for $f_{PLLI2S_IN}$ minimum and maximum values.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|             |                  | Added Note 1 in Table 35: SSCG parameters constraint.<br>Updated Table 36: Flash memory characteristics. Modified Table 37:<br>Flash memory programming and added Note 1 for t <sub>prog</sub> . Updated t <sub>prog</sub><br>and added Note 1 in Table 38: Flash memory programming with VPP.<br>Modified Figure 38: Recommended NRST pin protection.<br>Updated Table 41: EMI characteristics and EMI monitoring conditions in<br>Section : Electromagnetic Interference (EMI).<br>Added Note 2 related to V <sub>ESD(HBM)</sub> in Table 42: ESD absolute maximum<br>ratings.<br>Added Section 6.3.15: I/O current injection characteristics.<br>Updated Table 45: I/O static characteristics. Modified maximum<br>frequency values and conditions in Table 47: I/O AC characteristics.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| Table 94. Do | ocument revision | history | (continued) |

|--------------|------------------|---------|-------------|

|--------------|------------------|---------|-------------|

| Table 94. Document revision history (continued) |          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |

|-------------------------------------------------|----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Date                                            | Revision | Changes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |

| Date                                            |          | Changes         Removed Figure 4. Compatible board design between STM32F10xx and STM32F2xx for LQFP176 package.         Updated number of AHB buses in Section 2: Description and Section 3.12: Clocks and startup.         Updated Note 2 below Figure 4: STM32F21x block diagram.         Changed System memory to System memory + OTP in Figure 14: Memory map.         Added Note 1 below Table 15: VCAP1/VCAP2 operating conditions.         Updated Vote 1 below Table 15: VCAP1/VCAP2 operating conditions.         Updated Note 1 below Table 15: VCAP1/VCAP2 operating conditions.         Updated Note 1 below Table 15: VCAP1/VCAP2 operating conditions.         Updated Note 1 below Table 15: VCAP1/VCAP2 operating conditions.         Updated Note 1 below Table 15: VCAP1/VCAP2 operating conditions.         Updated Note 1 below Table 15: VCAP1/VCAP2 operating conditions.         Updated Note 1 below Table 15: VCAP1/VCAP2 operating conditions.         Updated Note 1 below Table 20: Typical and DAC2_OUT2 operating conditions.         Changed simplex mode into half-duplex mode in Section 3.24: Inter-integrated sound (I2S).         Replaced DAC1_OUT and DAC2_OUT by DAC_OUT1 and DAC_OUT2, respectively.         Changed TIM2_CH1/TIM2_ETR into TIM2_CH1_ETR for PA0 and PA5 in Table 9: Alternate function mapping.         Updated note applying to I <sub>DD</sub> (external clo |  |

| 29-Oct-2012                                     | 8        | in Table 20: Typical and maximum current consumption in Run mode, code with data processing running from Flash memory (ART                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |

|                                                 |          | Updated equations in Section 6.3.11: PLL spread spectrum clock<br>generation (SSCG) characteristics.<br>Swapped TTL and CMOS port conditions for V <sub>OL</sub> and V <sub>OH</sub> in Table 46:<br>Output voltage characteristics. Updated V <sub>IL(NRST)</sub> and V <sub>IH(NRST)</sub> in<br>Table 48: NRST pin characteristics.<br>Updated Table 53: SPI characteristics and Table 54: I2S<br>characteristics.Removed note 1 related to measurement points below<br>Figure 41: SPI timing diagram - slave mode and CPHA = 1, Figure 42:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |

|                                                 |          | SPI timing diagram - master mode, and Figure 43: I2S slave timing<br>diagram (Philips protocol)(1).<br>Updated t <sub>HC</sub> in Table 60: ULPI timing.<br>Updated Figure 47: Ethernet SMI timing diagram, Table 62: Dynamics<br>characteristics: Ethernet MAC signals for SMI and Table 63: Dynamics<br>characteristics: Ethernet MAC signals for RMII.<br>Update f <sub>TRIG</sub> in Table 65: ADC characteristics. Updated I <sub>DDA</sub> description<br>in Table 67: DAC characteristics.<br>Updated note below Figure 52: Power supply and reference decoupling<br>(VREF+ not connected to VDDA) and Figure 53: Power supply and<br>reference decoupling (VREF+ connected to VDDA).<br>Replaced t <sub>d</sub> (CLKL-NOEL) by t <sub>d</sub> (CLKH-NOEL) in Table 75: Synchronous<br>multiplexed NOR/PSRAM read timings, Table 77: Synchronous<br>non-multiplexed NOR/PSRAM read timings and Figure 61: Synchronous<br>non-multiplexed NOR/PSRAM read timings.                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |

| Table 94. Document revision history (continued) |                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|-------------------------------------------------|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Date                                            | Revision         | Changes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 04-Nov-2013                                     | 9<br>(continued) | Updated Figure 75: LQFP64 – 10 x 10 mm 64 pin low-profile quad flat<br>package outline and Table 86: LQFP64 – 10 x 10 mm 64 pin low-profile<br>quad flat package mechanical data. Updated Figure 77: LQFP100, 14 x<br>14 mm 100-pin low-profile quad flat package outline, Figure 80:<br>LQFP144, 20 x 20 mm, 144-pin low-profile quad flat package outline,<br>Figure 83: LQFP176 - Low profile quad flat package 24 × 24 × 1.4 mm,<br>package outline. Updated Figure 85: UFBGA176+25 - ultra thin fine<br>pitch ball grid array 10 × 10 × 0.6 mm, package outline and Figure 85:<br>UFBGA176+25 - ultra thin fine pitch ball grid array 10 × 10 × 0.6 mm,<br>package outline.<br>Removed Appendix A Application block diagrams.            |

| 27-Oct-2014                                     | 10               | Updated V <sub>BAT</sub> voltage range in <i>Figure 17: Power supply scheme</i> . Added<br>caution note in <i>Section 6.1.6: Power supply scheme</i> .<br>Updated V <sub>IN</sub> in <i>Table 13: General operating conditions</i> .<br>Removed note 1 in <i>Table 22: Typical and maximum current</i><br><i>consumptions in Stop mode</i> .<br>Updated <i>Table 44: I/O current injection susceptibility</i> , <i>Section 6.3.16:</i><br><i>I/O port characteristics</i> and <i>Section 6.3.17: NRST pin characteristics</i> .<br>Removed note 3 in <i>Table 68: Temperature sensor characteristics</i> .<br>Added <i>Figure 79: LQFP100 marking (package top view)</i> and <i>Figure 82:</i><br><i>LQFP144 marking (package top view)</i> . |

| 23-Feb-2016                                     | 11               | Updated Section 1: Introduction.<br>Updated Table 31: HSI oscillator characteristics and its footnotes.<br>Updated Figure 34: PLL output clock waveforms in center spread mode,<br>Figure 35: PLL output clock waveforms in down spread mode,<br>Figure 52: Power supply and reference decoupling (VREF+ not<br>connected to VDDA) and Figure 53: Power supply and reference<br>decoupling (VREF+ connected to VDDA).<br>Updated Section 7: Package information and its subsections.                                                                                                                                                                                                                                                          |

| 07-Jul-2016                                     | 12               | Updated Features and Section 2: Description.<br>Updated figures 1, 2 and 3 in Section 2.1: Full compatibility throughout<br>the family.<br>Updated Device marking and Figure 79 in Section 7.2: LQFP100<br>package information.<br>Updated Device marking and Figure 82 in Section 7.3: LQFP144<br>package information.<br>Updated Section 7.5: UFBGA176+25 package information with<br>introduction of Device marking and Figure 87.<br>Updated Table 93: Ordering information scheme.                                                                                                                                                                                                                                                       |