# E·XFL

#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                                  |

|----------------------------|-----------------------------------------------------------------------------------------|

| Core Processor             | ARM® Cortex®-M3                                                                         |

| Core Size                  | 32-Bit Single-Core                                                                      |

| Speed                      | 120MHz                                                                                  |

| Connectivity               | CANbus, Ethernet, I <sup>2</sup> C, IrDA, LINbus, Memory Card, SPI, UART/USART, USB OTG |

| Peripherals                | Brown-out Detect/Reset, DMA, I <sup>2</sup> S, LCD, POR, PWM, WDT                       |

| Number of I/O              | 82                                                                                      |

| Program Memory Size        | 1MB (1M × 8)                                                                            |

| Program Memory Type        | FLASH                                                                                   |

| EEPROM Size                | -                                                                                       |

| RAM Size                   | 132K x 8                                                                                |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                                             |

| Data Converters            | A/D 16x12b; D/A 2x12b                                                                   |

| Oscillator Type            | Internal                                                                                |

| Operating Temperature      | -40°C ~ 105°C (TA)                                                                      |

| Mounting Type              | Surface Mount                                                                           |

| Package / Case             | 100-LQFP                                                                                |

| Supplier Device Package    | 100-LQFP (14x14)                                                                        |

| Purchase URL               | https://www.e-xfl.com/product-detail/stmicroelectronics/stm32f217vgt7                   |

|                            |                                                                                         |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# 1 Introduction

This datasheet provides the description of the STM32F215xx and STM32F217xx lines of microcontrollers. For more details on the whole STMicroelectronics STM32 family, refer to *Section 2.1: Full compatibility throughout the family*.

The STM32F215xx and STM32F217xx datasheet should be read in conjunction with the STM32F20x/STM32F21x reference manual. They will be referred to as STM32F21x devices throughout the document.

For information on programming, erasing and protection of the internal Flash memory, refer to the STM32F20x/STM32F21x Flash programming manual (PM0059).

The reference and Flash programming manuals are both available from the STMicroelectronics website *www.st.com*.

For information on the Cortex<sup>®</sup>-M3 core refer to the Cortex<sup>®</sup>-M3 Technical Reference Manual, available from the *www.arm.com* website.

## 3.4 Embedded Flash memory

The STM32F21x devices embed a 128-bit wide Flash memory of 128 Kbytes, 256 Kbytes, 512 Kbytes, 768 Kbytes or 1 Mbyte available for storing programs and data.

The devices also feature 512 bytes of OTP memory that can be used to store critical user data such as Ethernet MAC addresses or cryptographic keys.

# 3.5 CRC (cyclic redundancy check) calculation unit

The CRC (cyclic redundancy check) calculation unit is used to get a CRC code from a 32-bit data word and a fixed generator polynomial.

Among other applications, CRC-based techniques are used to verify data transmission or storage integrity. In the scope of the EN/IEC 60335-1 standard, they offer a means of verifying the Flash memory integrity. The CRC calculation unit helps compute a software signature during runtime, to be compared with a reference signature generated at link-time and stored at a given memory location.

# 3.6 Embedded SRAM

All STM32F21x products embed:

- Up to 128 Kbytes of system SRAM accessed (read/write) at CPU clock speed with 0 wait states

- 4 Kbytes of backup SRAM.

The content of this area is protected against possible unwanted write accesses, and is retained in Standby or VBAT mode.

## 3.7 Multi-AHB bus matrix

The 32-bit multi-AHB bus matrix interconnects all the masters (CPU, DMAs, Ethernet, USB HS) and the slaves (Flash memory, RAM, FSMC, AHB and APB peripherals) and ensures a seamless and efficient operation even when several high-speed peripherals work simultaneously.

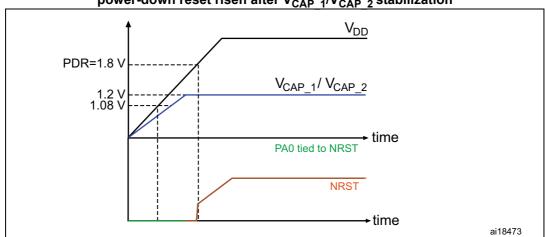

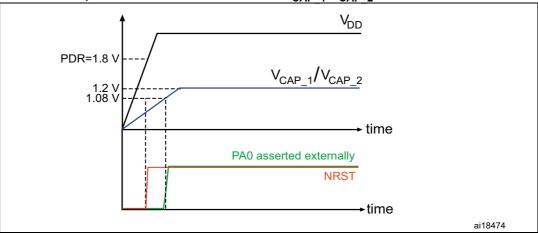

# Figure 7. Startup in regulator OFF: slow V<sub>DD</sub> slope, power-down reset risen after V<sub>CAP 1</sub>/V<sub>CAP 2</sub> stabilization

1. This figure is valid both whatever the internal reset mode (ON or OFF).

## 3.16.3 Regulator ON/OFF and internal reset ON/OFF availability

| Table 3. Regulator ON/OFF and internal reset ON/ | OFF availability |

|--------------------------------------------------|------------------|

|--------------------------------------------------|------------------|

| Package Regulator ON/internal reset ON  |                                      | Regulator ON/internal<br>reset OFF | Regulator<br>OFF/internal reset ON   |  |  |

|-----------------------------------------|--------------------------------------|------------------------------------|--------------------------------------|--|--|

| LQFP64<br>LQFP100<br>LQFP144<br>LQFP176 | Yes                                  | No                                 | No                                   |  |  |

| UFBGA176                                | Yes<br>REGOFF set to V <sub>SS</sub> | No                                 | Yes<br>REGOFF set to V <sub>DD</sub> |  |  |

# 3.17 Real-time clock (RTC), backup SRAM and backup registers

The backup domain of the STM32F21x devices includes:

- The real-time clock (RTC)

- 4 Kbytes of backup SRAM

- 20 backup registers

The real-time clock (RTC) is an independent BCD timer/counter. Its main features are the following:

- Dedicated registers contain the second, minute, hour (in 12/24 hour), week day, date, month, year, in BCD (binary-coded decimal) format.

- Automatic correction for 28, 29 (leap year), 30, and 31 day of the month.

- Programmable alarm and programmable periodic interrupts with wakeup from Stop and Standby modes.

- It is clocked by a 32.768 kHz external crystal, resonator or oscillator, the internal lowpower RC oscillator or the high-speed external clock divided by 128. The internal lowspeed RC has a typical frequency of 32 kHz. The RTC can be calibrated using an external 512 Hz output to compensate for any natural quartz deviation.

- Two alarm registers are used to generate an alarm at a specific time and calendar fields can be independently masked for alarm comparison. To generate a periodic interrupt, a 16-bit programmable binary auto-reload downcounter with programmable resolution is available and allows automatic wakeup and periodic alarms from every 120 µs to every 36 hours.

- A 20-bit prescaler is used for the time base clock. It is by default configured to generate a time base of 1 second from a clock at 32.768 kHz.

- Reference clock detection: a more precise second source clock (50 or 60 Hz) can be used to enhance the calendar precision.

The 4-Kbyte backup SRAM is an EEPROM-like area. It can be used to store data which need to be retained in VBAT and standby mode. This memory area is disabled to minimize power consumption (see *Section 3.18: Low-power modes*). It can be enabled by software.

The backup registers are 32-bit registers used to store 80 bytes of user application data when  $V_{DD}$  power is not present. Backup registers are not reset by a system, a power reset, or when the device wakes up from the Standby mode (see Section 3.18: Low-power modes).

Like backup SRAM, the RTC and backup registers are supplied through a switch that is powered either from the  $V_{\text{DD}}$  supply when present or the  $V_{\text{BAT}}$  pin.

## 3.18 Low-power modes

The STM32F21x family supports three low-power modes to achieve the best compromise between low-power consumption, short startup time and available wakeup sources:

#### Sleep mode

In Sleep mode, only the CPU is stopped. All peripherals continue to operate and can wake up the CPU when an interrupt/event occurs.

#### • Stop mode

The Stop mode achieves the lowest power consumption while retaining the contents of SRAM and registers. All clocks in the 1.2 V domain are stopped, the PLL, the HSI RC

and the HSE crystal oscillators are disabled. The voltage regulator can also be put either in normal or in low-power mode.

The device can be woken up from the Stop mode by any of the EXTI line. The EXTI line source can be one of the 16 external lines, the PVD output, the RTC alarm / wakeup / tamper / time stamp events, the USB OTG FS/HS wakeup or the Ethernet wakeup.

#### • Standby mode

The Standby mode is used to achieve the lowest power consumption. The internal voltage regulator is switched off so that the entire 1.2 V domain is powered off. The PLL, the HSI RC and the HSE crystal oscillators are also switched off. After entering Standby mode, the SRAM and register contents are lost except for registers in the backup domain and the backup SRAM when selected.

The device exits the Standby mode when an external reset (NRST pin), an IWDG reset, a rising edge on the WKUP pin, or an RTC alarm / wakeup / tamper /time stamp event occurs.

*Note:* The RTC, the IWDG, and the corresponding clock sources are not stopped when the device enters the Stop or Standby mode.

# 3.19 V<sub>BAT</sub> operation

The  $V_{\text{BAT}}$  pin allows to power the device  $V_{\text{BAT}}$  domain from an external battery or an external supercapacitor.

$V_{BAT}$  operation is activated when  $V_{DD}$  is not present.

The VBAT pin supplies the RTC, the backup registers and the backup SRAM.

Note: When the microcontroller is supplied from  $V_{BAT}$ , external interrupts and RTC alarm/events do not exit it from  $V_{BAT}$  operation.

# 3.20 Timers and watchdogs

The STM32F21x devices include two advanced-control timers, eight general-purpose timers, two basic timers and two watchdog timers.

All timer counters can be frozen in debug mode.

Table 4 compares the features of the advanced-control, general-purpose and basic timers.

| Timer type           | Timer         | Counter<br>resolution | Counter<br>type         | Prescaler<br>factor                   | DMA<br>request<br>generation |   | Complementary<br>output | Max<br>interface<br>clock | Max<br>timer<br>clock |

|----------------------|---------------|-----------------------|-------------------------|---------------------------------------|------------------------------|---|-------------------------|---------------------------|-----------------------|

| Advanced-<br>control | TIM1,<br>TIM8 | 16-bit                | Up,<br>Down,<br>Up/down | Any integer<br>between 1<br>and 65536 | Yes                          | 4 | Yes                     | 60<br>MHz                 | 120<br>MHz            |

|        |         | Pins    | ;       |          |                                                      |          |                 |      |                                                                                              |                         |

|--------|---------|---------|---------|----------|------------------------------------------------------|----------|-----------------|------|----------------------------------------------------------------------------------------------|-------------------------|

| LQFP64 | LQFP100 | LQFP144 | LQFP176 | UFBGA176 | Pin name<br>(function after<br>reset) <sup>(1)</sup> | Pin type | I / O structure | Note | Alternate functions                                                                          | Additional<br>functions |

| 38     | 64      | 97      | 116     | G15      | PC7                                                  | I/O      | FT              | -    | I2S3_MCK,<br>TIM8_CH2,SDIO_D7,<br>USART6_RX,<br>DCMI_D1,TIM3_CH2,<br>EVENTOUT                | -                       |

| 39     | 65      | 98      | 117     | G14      | PC8                                                  | I/O      | FT              | -    | TIM8_CH3,SDIO_D0,<br>TIM3_CH3, USART6_CK,<br>DCMI_D2, EVENTOUT                               | -                       |

| 40     | 66      | 99      | 118     | F14      | PC9                                                  | I/O      | FT              | -    | I2S2_CKIN, I2S3_CKIN,<br>MCO2, TIM8_CH4,SDIO_D1,<br>I2C3_SDA, DCMI_D3,<br>TIM3_CH4, EVENTOUT | -                       |

| 41     | 67      | 100     | 119     | F15      | PA8                                                  | I/O      | FT              | -    | MCO1, USART1_CK,<br>TIM1_CH1, I2C3_SCL,<br>OTG_FS_SOF, EVENTOUT                              | -                       |

| 42     | 68      | 101     | 120     | E15      | PA9                                                  | I/O      | FT              | -    | USART1_TX, TIM1_CH2,<br>I2C3_SMBA, DCMI_D0,<br>EVENTOUT                                      | OTG_FS_<br>VBUS         |

| 43     | 69      | 102     | 121     | D15      | PA10                                                 | I/O      | FT              | -    | USART1_RX, TIM1_CH3,<br>OTG_FS_ID,DCMI_D1,<br>EVENTOUT                                       | -                       |

| 44     | 70      | 103     | 122     | C15      | PA11                                                 | I/O      | FT              | -    | USART1_CTS, CAN1_RX,<br>TIM1_CH4, OTG_FS_DM,<br>EVENTOUT                                     | -                       |

| 45     | 71      | 104     | 123     | B15      | PA12                                                 | I/O      | FT              | -    | USART1_RTS, CAN1_TX,<br>TIM1_ETR, OTG_FS_DP,<br>EVENTOUT                                     | -                       |

| 46     | 72      | 105     | 124     | A15      | PA13<br>(JTMS-SWDIO)                                 | I/O      | FT              | -    | JTMS-SWDIO, EVENTOUT                                                                         | -                       |

| 47     | 73      | 106     | 125     | F13      | V <sub>CAP_2</sub>                                   | S        | -               | -    | -                                                                                            | -                       |

| -      | 74      | 107     | 126     | F12      | V <sub>SS</sub>                                      | S        | -               | -    | -                                                                                            |                         |

| 48     | 75      | 108     | 127     | G13      | V <sub>DD</sub>                                      | S        | -               | -    | -                                                                                            | -                       |

| -      | -       | -       | 128     | E12      | PH13                                                 | I/O      | FT              | -    | TIM8_CH1N, CAN1_TX,<br>EVENTOUT                                                              | -                       |

| -      | -       | -       | 129     | E13      | PH14                                                 | I/O      | FT              | -    | TIM8_CH2N, DCMI_D4,<br>EVENTOUT                                                              | -                       |

Table 7. STM32F21x pin and ball definitions (continued)

| • | Table 7. STM32F21 | x pin | and | ball | definitions (continued) |

|---|-------------------|-------|-----|------|-------------------------|

|   |                   |       |     |      |                         |

| Table 7. STM32F21X pin and ball definitions (continued) |         |         |         |          |                                                      |          |                 |      |                                                                                                                            |                         |

|---------------------------------------------------------|---------|---------|---------|----------|------------------------------------------------------|----------|-----------------|------|----------------------------------------------------------------------------------------------------------------------------|-------------------------|

| 1                                                       |         | Pins    | 5       |          |                                                      |          |                 |      |                                                                                                                            |                         |

| LQFP64                                                  | LQFP100 | LQFP144 | LQFP176 | UFBGA176 | Pin name<br>(function after<br>reset) <sup>(1)</sup> | Pin type | I / O structure | Note | Alternate functions                                                                                                        | Additional<br>functions |

| -                                                       | -       | 132     | 160     | B7       | PG15                                                 | I/O      | FT              | -    | USART6_CTS, DCMI_D13,<br>EVENTOUT                                                                                          | -                       |

| 55                                                      | 89      | 133     | 161     | A10      | PB3<br>(JTDO/TRACESWO)                               | I/O      | FT              | -    | JTDO/TRACESWO,<br>SPI3_SCK, I2S3_SCK,<br>TIM2_CH2, SPI1_SCK,<br>EVENTOUT                                                   | -                       |

| 56                                                      | 90      | 134     | 162     | A9       | PB4                                                  | I/O      | FT              | -    | NJTRST, SPI3_MISO,<br>TIM3_CH1, SPI1_MISO,<br>EVENTOUT                                                                     | -                       |

| 57                                                      | 91      | 135     | 163     | A6       | PB5                                                  | I/O      | FT              | -    | I2C1_SMBA, CAN2_RX,<br>OTG_HS_ULPI_D7,<br>ETH_PPS_OUT,TIM3_CH2,<br>SPI1_MOSI, SPI3_MOSI,<br>DCMI_D10, I2S3_SD,<br>EVENTOUT | -                       |

| 58                                                      | 92      | 136     | 164     | В6       | PB6                                                  | I/O      | FT              | -    | I2C1_SCL, TIM4_CH1,<br>CAN2_TX,<br>DCMI_D5,USART1_TX,<br>EVENTOUT                                                          | -                       |

| 59                                                      | 93      | 137     | 165     | B5       | PB7                                                  | I/O      | FT              | -    | I2C1_SDA, FSMC_NL <sup>(6)</sup> ,<br>DCMI_VSYNC, USART1_RX,<br>TIM4_CH2, EVENTOUT                                         | -                       |

| 60                                                      | 94      | 138     | 166     | D6       | BOOT0                                                | I        | В               | -    | -                                                                                                                          | V <sub>PP</sub>         |

| 61                                                      | 95      | 139     | 167     | A5       | PB8                                                  | I/O      | FT              | -    | TIM4_CH3,SDIO_D4,<br>TIM10_CH1, DCMI_D6,<br>ETH_MII_TXD3, I2C1_SCL,<br>CAN1_RX, EVENTOUT                                   | -                       |

| 62                                                      | 96      | 140     | 168     | B4       | PB9                                                  | I/O      | FT              | -    | SPI2_NSS, I2S2_WS,<br>TIM4_CH4, TIM11_CH1,<br>SDIO_D5, DCMI_D7,<br>I2C1_SDA, CAN1_TX,<br>EVENTOUT                          | -                       |

| -                                                       | 97      | 141     | 169     | A4       | PE0                                                  | I/O      | FT              | -    | TIM4_ETR, FSMC_NBL0,<br>DCMI_D2, EVENTOUT                                                                                  | -                       |

| -                                                       | 98      | 142     | 170     | A3       | PE1                                                  | I/O      | FT              | -    | FSMC_NBL1, DCMI_D3,<br>EVENTOUT                                                                                            | -                       |

| -                                                       | -       | -       | -       | D5       | V <sub>SS</sub>                                      | S        |                 | -    | -                                                                                                                          | -                       |

| Symbol                                 | Parameter                                                                                                      | Conditions                                               | Min   | Max                  | Unit |  |

|----------------------------------------|----------------------------------------------------------------------------------------------------------------|----------------------------------------------------------|-------|----------------------|------|--|

| $V_{DD}$                               | Standard operating voltage                                                                                     | -                                                        | 1.8   | 3.6                  |      |  |

| V <sub>DDA</sub> <sup>(1)</sup>        | Analog operating voltage<br>(ADC limited to 1 M samples)                                                       | Must be the same potential as $V_{DD}^{(2)}$             | 1.8   | 3.6                  |      |  |

| V DDA                                  | Analog operating voltage<br>(ADC limited to 2 M samples)                                                       |                                                          | 2.4   | 3.6                  |      |  |

| $V_{BAT}$                              | Backup operating voltage                                                                                       | -                                                        | 1.65  | 3.6                  |      |  |

|                                        | Input voltage on RST and FT pins                                                                               | $2 \text{ V} \le \text{V}_{\text{DD}} \le 3.6 \text{ V}$ | -0.3  | 5.5                  | V    |  |

| V                                      | input voltage on KST and FT pins                                                                               | $1.7 \text{ V} \le \text{V}_{\text{DD}} \le 2 \text{ V}$ | -0.3  | 5.2                  |      |  |

| V <sub>IN</sub>                        | Input voltage on TTa pins                                                                                      | -                                                        | -0.3  | V <sub>DD</sub> +0.3 |      |  |

|                                        | Input voltage on BOOT0 pin                                                                                     | -                                                        | 0     | 9                    |      |  |

| V <sub>CAP1</sub><br>V <sub>CAP2</sub> | Internal core voltage to be supplied externally in REGOFF mode                                                 | -                                                        | 1.1   | 1.3                  |      |  |

|                                        |                                                                                                                | LQFP64                                                   | -     | 444                  |      |  |

|                                        |                                                                                                                | LQFP100                                                  | - 434 |                      |      |  |

| PD                                     | Power dissipation at $T_A = 85 \degree C$ for<br>suffix 6 or $T_A = 105 \degree C$ for suffix 7 <sup>(3)</sup> | LQFP144                                                  | -     | 500                  | mW   |  |

|                                        |                                                                                                                | LQFP176                                                  | -     | 526                  |      |  |

|                                        |                                                                                                                | UFBGA176                                                 | -     | 513                  |      |  |

|                                        | Ambient temperature for 6 suffix                                                                               | Maximum power dissipation                                | -40   | 85                   | °C   |  |

| Та                                     | version                                                                                                        | Low-power dissipation <sup>(4)</sup>                     | -40   | 105                  | C    |  |

| IA                                     | Ambient temperature for 7 suffix                                                                               | Maximum power dissipation                                | -40   | 40 105               |      |  |

|                                        | version                                                                                                        | Low-power dissipation <sup>(4)</sup>                     | -40   | 125                  | °C   |  |

| TJ                                     | Junction temperature range                                                                                     | 6 suffix version                                         | -40   | 105                  | °C   |  |

| IJ                                     |                                                                                                                | 7 suffix version                                         | -40   | 125                  |      |  |

Table 13. General operating conditions (continued)

1. When the ADC is used, refer to *Table 65: ADC characteristics*.

2. It is recommended to power V<sub>DD</sub> and V<sub>DDA</sub> from the same source. A maximum difference of 300 mV between V<sub>DD</sub> and V<sub>DDA</sub> can be tolerated during power-up and power-down operation.

3. If  $T_A$  is lower, higher  $\mathsf{P}_D$  values are allowed as long as  $T_J$  does not exceed  $T_{Jmax}.$

4. In low-power dissipation state,  $T_A$  can be extended to this range as long as  $T_J$  does not exceed  $T_{Jmax}$ .

|                 |                | nning from Flash men                                                   |                       | Тур   | ,                      | ax <sup>(1)</sup>       |      |  |

|-----------------|----------------|------------------------------------------------------------------------|-----------------------|-------|------------------------|-------------------------|------|--|

| Symbol          | Parameter      | Conditions                                                             | f <sub>HCLK</sub>     | -     | T <sub>A</sub> = 85 °C | T <sub>A</sub> = 105 °C | Unit |  |

|                 |                |                                                                        | 120 MHz               | 61    | 81                     | 93                      |      |  |

|                 |                |                                                                        | 90 MHz                | 48    | 68                     | 80                      |      |  |

|                 |                |                                                                        | 60 MHz                | 33    | 53                     | 65                      |      |  |

|                 |                |                                                                        | 30 MHz                | 18    | 38                     | 50                      |      |  |

|                 |                | External clock <sup>(2)</sup> , all peripherals enabled <sup>(3)</sup> | 25 MHz                | 14    | 34                     | 46                      |      |  |

|                 |                |                                                                        | 16 MHz <sup>(4)</sup> | 10    | 30                     | 42                      |      |  |

|                 | Supply current |                                                                        |                       | 8 MHz | 6                      | 26                      | 38   |  |

|                 |                |                                                                        |                       | 4 MHz | 4                      | 24                      | 36   |  |

|                 |                |                                                                        | 2 MHz                 | 3     | 23                     | 35                      |      |  |

| I <sub>DD</sub> | in Run mode    |                                                                        | 120 MHz               | 33    | 54                     | 66                      | mA   |  |

|                 |                |                                                                        | 90 MHz                | 27    | 47                     | 59                      |      |  |

|                 |                |                                                                        | 60 MHz                | 19    | 39                     | 51                      |      |  |

|                 |                | (2)                                                                    | 30 MHz                | 11    | 31                     | 43                      |      |  |

|                 |                | External clock <sup>(2)</sup> , all peripherals disabled               | 25 MHz                | 8     | 28                     | 41                      |      |  |

|                 |                |                                                                        | 16 MHz <sup>(4)</sup> | 6     | 26                     | 38                      |      |  |

|                 |                |                                                                        | 8 MHz                 | 4     | 24                     | 36                      |      |  |

|                 |                |                                                                        | 4 MHz                 | 3     | 23                     | 35                      |      |  |

|                 |                |                                                                        | 2 MHz                 | 2     | 23                     | 34                      |      |  |

# Table 20. Typical and maximum current consumption in Run mode, code with data processingrunning from Flash memory (ART accelerator disabled)

1. Guaranteed by characterization results, tested in production at  $V_{DD}$  max and  $f_{HCLK}$  max with peripherals enabled.

2. External clock is 4 MHz and PLL is on when  $f_{HCLK}$  > 25 MHz.

3. When the ADC is on (ADON bit set in the ADC\_CR2 register), add an additional power consumption of 1.6 mA per ADC for the analog part.

4. In this case HCLK = system clock/2.

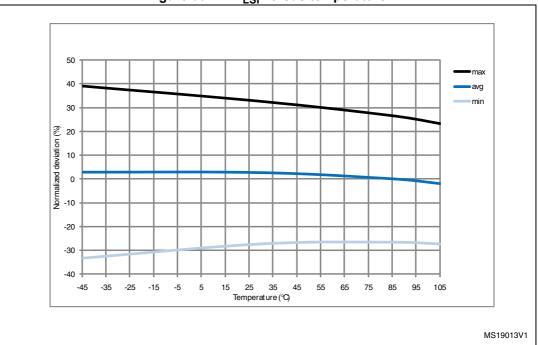

Figure 33. ACC<sub>LSI</sub> versus temperature

## 6.3.10 PLL characteristics

The parameters given in *Table 33* and *Table 34* are derived from tests performed under temperature and  $V_{DD}$  supply voltage conditions summarized in *Table 13*.

| Symbol                  | Parameter                             | Conditions         | Min                 | Тур | Max                 | Unit |  |

|-------------------------|---------------------------------------|--------------------|---------------------|-----|---------------------|------|--|

| f <sub>PLL_IN</sub>     | PLL input clock <sup>(1)</sup>        | -                  | 0.95 <sup>(2)</sup> | 1   | 2.10 <sup>(2)</sup> | MHz  |  |

| f <sub>PLL_OUT</sub>    | PLL multiplier output clock           | -                  | 24                  | -   | 120                 | MHz  |  |

| f <sub>PLL48_</sub> OUT | 48 MHz PLL multiplier output<br>clock | -                  | -                   | -   | 48                  | MHz  |  |

| f <sub>VCO_OUT</sub>    | PLL VCO output                        | -                  | 192                 | -   | 432                 | MHz  |  |

|                         | PLL lock time                         | VCO freq = 192 MHz | 75                  | -   | 200                 |      |  |

| <sup>t</sup> LOCK       |                                       | VCO freq = 432 MHz | 100                 | -   | 300                 | μs   |  |

Table 33. Main PLL characteristics

| Symbol          | Parameter      | Conditions                                           | Min | Тур | Max | Unit |

|-----------------|----------------|------------------------------------------------------|-----|-----|-----|------|

| I <sub>DD</sub> |                | Write / Erase 8-bit mode<br>V <sub>DD</sub> = 1.8 V  | -   | 5   | -   |      |

|                 | Supply current | Write / Erase 16-bit mode<br>V <sub>DD</sub> = 2.1 V | -   | 8   | -   | mA   |

|                 |                | Write / Erase 32-bit mode<br>V <sub>DD</sub> = 3.3 V | -   | 12  | -   |      |

Table 36. Flash memory characteristics

| Table 37. Fl | ash memory | programming |

|--------------|------------|-------------|

|--------------|------------|-------------|

| Symbol                  | Parameter                  | Conditions                                       | Min <sup>(1)</sup> | Тур  | Max <sup>(1)</sup> | Unit |  |

|-------------------------|----------------------------|--------------------------------------------------|--------------------|------|--------------------|------|--|

| t <sub>prog</sub>       | Word programming time      | Program/erase parallelism<br>(PSIZE) = x 8/16/32 | -                  | 16   | 100 <sup>(2)</sup> | μs   |  |

|                         |                            | Program/erase parallelism<br>(PSIZE) = x 8       | -                  | 400  | 800                |      |  |

| t <sub>ERASE16KB</sub>  | Sector (16 KB) erase time  | Program/erase parallelism<br>(PSIZE) = x 16      | -                  | 300  | 600                | ms   |  |

|                         |                            | Program/erase parallelism<br>(PSIZE) = x 32      | -                  | 250  | 500                |      |  |

|                         |                            | Program/erase parallelism<br>(PSIZE) = x 8       | -                  | 1200 | 2400               |      |  |

| t <sub>ERASE64KB</sub>  | Sector (64 KB) erase time  | Program/erase parallelism<br>(PSIZE) = x 16      | -                  | 700  | 1400               | ms   |  |

|                         |                            | Program/erase parallelism<br>(PSIZE) = x 32      | -                  | 550  | 1100               |      |  |

|                         |                            | Program/erase parallelism<br>(PSIZE) = x 8       | -                  | 2    | 4                  |      |  |

| t <sub>ERASE128KB</sub> | Sector (128 KB) erase time | Program/erase parallelism<br>(PSIZE) = x 16      | -                  | 1.3  | 2.6                | S    |  |

|                         |                            | Program/erase parallelism<br>(PSIZE) = x 32      | -                  | 1    | 2                  |      |  |

|                         |                            | Program/erase parallelism<br>(PSIZE) = x 8       | -                  | 16   | 32                 |      |  |

| t <sub>ME</sub>         | Mass erase time            | Program/erase parallelism<br>(PSIZE) = x 16      | -                  | 11   | 22                 | S    |  |

|                         |                            | Program/erase parallelism<br>(PSIZE) = x 32      | -                  | 8    | 16                 |      |  |

|                         |                            | 32-bit program operation                         | 2.7                | -    | 3.6                | V    |  |

| V <sub>prog</sub>       | Programming voltage        | 16-bit program operation                         | 2.1                | -    | 3.6                | V    |  |

|                         |                            | 8-bit program operation                          | 1.8                | -    | 3.6                | V    |  |

1. Guaranteed by characterization results, not tested in production.

2. The maximum programming time is measured after 100K erase operations.

### **Electromagnetic Interference (EMI)**

The electromagnetic field emitted by the device are monitored while a simple application, executing EEMBC<sup>®</sup> code, is running. This emission test is compliant with SAE IEC61967-2 standard which specifies the test board and the pin loading.

| Symbol Parameter |                             | Conditions                                                                                                                                     | Monitored<br>frequency band | Max vs.<br>[f <sub>HSE</sub> /f <sub>CPU</sub> ] | Unit |

|------------------|-----------------------------|------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------|--------------------------------------------------|------|

|                  |                             |                                                                                                                                                | irequency band              | 25/120 MHz                                       |      |

|                  | V = 2 2 V T = 25 °C LOED176 |                                                                                                                                                | 0.1 to 30 MHz               |                                                  |      |

|                  |                             | $V_{DD}$ = 3.3 V, $T_A$ = 25 °C, LQFP176<br>package, conforming to SAE J1752/3                                                                 | 30 to 130 MHz               | 25                                               | dBµV |

|                  |                             | EEMBC, code running with ART<br>enabled, peripheral clock disabled                                                                             | 130 MHz to 1GHz             |                                                  |      |

| S                | Peak level                  |                                                                                                                                                | SAE EMI Level               | 4                                                | -    |

| S <sub>EMI</sub> | Feak level                  | $V_{DD}$ = 3.3 V, $T_A$ = 25 °C, LQFP176<br>package, conforming to SAE J1752/3<br>EEMBC, code running with ART<br>enabled, PLL spread spectrum | 0.1 to 30 MHz               | 28                                               |      |

|                  |                             |                                                                                                                                                | 30 to 130 MHz               | 26                                               | dBµV |

|                  |                             |                                                                                                                                                | 130 MHz to 1GHz             | 22                                               |      |

|                  |                             | enabled, peripheral clock disabled                                                                                                             | SAE EMI level               | 4                                                | -    |

## 6.3.14 Absolute maximum ratings (electrical sensitivity)

Based on three different tests (ESD, LU) using specific measurement methods, the device is stressed in order to determine its performance in terms of electrical sensitivity.

### Electrostatic discharge (ESD)

Electrostatic discharges (a positive then a negative pulse separated by 1 second) are applied to the pins of each sample according to each pin combination. The sample size depends on the number of supply pins in the device (3 parts  $\times$  (n+1) supply pins). This test conforms to the JESD22-A114/C101 standard.

| Symbol                | Ratings                                                  | Conditions                                       | Class | Maximum<br>value <sup>(1)</sup> | Unit |

|-----------------------|----------------------------------------------------------|--------------------------------------------------|-------|---------------------------------|------|

| V <sub>ESD(HBM)</sub> | Electrostatic discharge<br>voltage (human body<br>model) | $T_A = +25 \text{ °C conforming to JESD22-A114}$ | 2     | 2000 <sup>(2)</sup>             | v    |

| V <sub>ESD(CDM)</sub> | Electrostatic discharge voltage (charge device model)    | $T_A = +25 \text{ °C conforming to JESD22-C101}$ | II    | 500                             | v    |

#### Table 42. ESD absolute maximum ratings

1. Guaranteed by characterization results, not tested in production.

2. On  $V_{BAT}$  pin,  $V_{ESD(HBM)}$  is limited to 1000 V.

### **Electrical characteristics**

| OSPEEDRy<br>[1:0] bit<br>value <sup>(1)</sup> | Symbol                  | Parameter                                                                       | Conditions                                          | Min | Тур | Мах                | Unit    |  |

|-----------------------------------------------|-------------------------|---------------------------------------------------------------------------------|-----------------------------------------------------|-----|-----|--------------------|---------|--|

|                                               |                         |                                                                                 | C <sub>L</sub> = 50 pF, V <sub>DD &gt;</sub> 2.70 V | -   | -   | 25                 |         |  |

|                                               | £                       | Maximum fraguana (2)                                                            | C <sub>L</sub> = 50 pF, V <sub>DD &gt;</sub> 1.8 V  | -   | -   | 12.5               | MHz     |  |

|                                               | Imax(IO)out             | Maximum frequency <sup>(2)</sup>                                                | C <sub>L</sub> = 10 pF, V <sub>DD &gt;</sub> 2.70 V | -   | -   | 50 <sup>(3)</sup>  |         |  |

| 01                                            |                         |                                                                                 | C <sub>L</sub> = 10 pF, V <sub>DD &gt;</sub> 1.8 V  | -   | -   | 20                 |         |  |

| 01                                            |                         |                                                                                 | C <sub>L</sub> = 50 pF, V <sub>DD</sub> >2.7 V      | -   | -   | 10                 |         |  |

|                                               | t <sub>f(IO)out</sub> / | Output high to low level fall                                                   | C <sub>L</sub> = 50 pF, V <sub>DD &gt;</sub> 1.8 V  | -   | -   | 20                 |         |  |

|                                               | t <sub>r(IO)out</sub>   | time and output low to high<br>level rise time                                  | C <sub>L</sub> = 10 pF, V <sub>DD &gt;</sub> 2.70 V | -   | -   | 6                  | ns      |  |

|                                               |                         |                                                                                 | C <sub>L</sub> = 10 pF, V <sub>DD &gt;</sub> 1.8 V  | -   | -   | 10                 |         |  |

|                                               |                         |                                                                                 | C <sub>L</sub> = 40 pF, V <sub>DD &gt;</sub> 2.70 V | -   | -   | 25                 |         |  |

|                                               | £                       | Maximum frequency <sup>(2)</sup>                                                | C <sub>L</sub> = 40 pF, V <sub>DD &gt;</sub> 1.8 V  | -   | -   | 20                 | N 41 1- |  |

|                                               | Imax(IO)out             |                                                                                 | C <sub>L</sub> = 10 pF, V <sub>DD &gt;</sub> 2.70 V | -   | -   | 100 <sup>(3)</sup> | MHz     |  |

| 10                                            |                         |                                                                                 | C <sub>L</sub> = 10 pF, V <sub>DD &gt;</sub> 1.8 V  | -   | -   | 50 <sup>(3)</sup>  |         |  |

| 10                                            |                         | Output high to low level fall<br>time and output low to high<br>level rise time | C <sub>L</sub> = 40 pF, V <sub>DD &gt;</sub> 2.70 V | -   | -   | 6                  | ns      |  |

|                                               | t <sub>f(IO)out</sub> / |                                                                                 | C <sub>L</sub> = 40 pF, V <sub>DD &gt;</sub> 1.8 V  | -   | -   | 10                 |         |  |

|                                               | t <sub>r(IO)out</sub>   |                                                                                 | C <sub>L</sub> = 10 pF, V <sub>DD &gt;</sub> 2.70 V | -   | -   | 4                  |         |  |

|                                               |                         |                                                                                 | C <sub>L</sub> = 10 pF, V <sub>DD &gt;</sub> 1.8 V  | -   | -3  | 6                  |         |  |

|                                               |                         |                                                                                 | C <sub>L</sub> = 30 pF, V <sub>DD &gt;</sub> 2.70 V | -   | -   | 100 <sup>(3)</sup> |         |  |

|                                               | £                       | Mari income for an er (2)                                                       | C <sub>L</sub> = 30 pF, V <sub>DD &gt;</sub> 1.8 V  | -   | -   | 50 <sup>(3)</sup>  | N 41 1- |  |

|                                               | Tmax(IO)out             | Maximum frequency <sup>(2)</sup>                                                | C <sub>L</sub> = 10 pF, V <sub>DD &gt;</sub> 2.70 V | -   | -   | 120 <sup>(3)</sup> | MHz     |  |

| 44                                            |                         |                                                                                 | C <sub>L</sub> = 10 pF, V <sub>DD &gt;</sub> 1.8 V  | -   | -   | 100 <sup>(3)</sup> |         |  |

| 11                                            |                         |                                                                                 | C <sub>L</sub> = 30 pF, V <sub>DD &gt;</sub> 2.70 V | -   | -   | 4                  |         |  |

|                                               | t <sub>f(IO)out</sub> / | Output high to low level fall                                                   | C <sub>L</sub> = 30 pF, V <sub>DD &gt;</sub> 1.8 V  | -   | -   | 6                  |         |  |

|                                               | t <sub>r(IO)out</sub>   | time and output low to high<br>level rise time                                  | C <sub>L</sub> = 10 pF, V <sub>DD &gt;</sub> 2.70 V | -   | -   | 2.5                | ns      |  |

|                                               |                         |                                                                                 | C <sub>L</sub> = 10 pF, V <sub>DD &gt;</sub> 1.8 V  | -   | -   | 4                  |         |  |

| -                                             | t <sub>EXTIpw</sub>     | Pulse width of external<br>signals detected by the<br>EXTI controller           | -                                                   | 10  | -   | -                  | ns      |  |

| Table 47. I/O AC characteristics <sup>(1)</sup> | (continued) |

|-------------------------------------------------|-------------|

|-------------------------------------------------|-------------|

The I/O speed is configured using the OSPEEDRy[1:0] bits. Refer to the STM32F20/21xxx reference manual for a description of the GPIOx\_SPEEDR GPIO port output speed register.

2. The maximum frequency is defined in *Figure 37*.

3. For maximum frequencies above 50 MHz and  $V_{\text{DD}}$  above 2.4 V, the compensation cell should be used.

| Symbol                                                       | Parameter                                 | Conditions                                                                                 | Min     | Max                             | Unit |

|--------------------------------------------------------------|-------------------------------------------|--------------------------------------------------------------------------------------------|---------|---------------------------------|------|

| f <sub>CK</sub><br>1/t <sub>c(CK)</sub>                      | I <sup>2</sup> S clock frequency          | Master, 16-bit data,<br>audio frequency = 48 kHz, main<br>clock disabled                   | 1.23    | 1.24                            | MHz  |

|                                                              |                                           | Slave                                                                                      | 0       | 64F <sub>S</sub> <sup>(1)</sup> |      |

| t <sub>r(CK)</sub><br>t <sub>f(CK)</sub>                     | I <sup>2</sup> S clock rise and fall time | Capacitive load $C_L = 50 \text{ pF}$                                                      | -       | (2)                             |      |

| t <sub>v(WS)</sub> <sup>(3)</sup>                            | WS valid time                             | Master                                                                                     | 0.3     | -                               |      |

| t <sub>h(WS)</sub> <sup>(3)</sup>                            | WS hold time                              | Master                                                                                     | 0       | -                               |      |

| t <sub>su(WS)</sub> <sup>(3)</sup>                           | WS setup time                             | Slave                                                                                      | 3       | -                               |      |

| t <sub>h(WS)</sub> <sup>(3)</sup>                            | WS hold time                              | Slave                                                                                      | 0       | -                               |      |

| t <sub>w(CKH)</sub> (3)<br>t <sub>w(CKL)</sub> (3)           | CK high and low time                      | Master f <sub>PCLK</sub> = 30 MHz                                                          | 396     | -                               | •    |

| $t_{su(SD\_MR)}^{(3)}_{(3)}$<br>$t_{su(SD\_SR)}^{(3)}$       | Data input setup time                     | Master receiver<br>Slave receiver                                                          | 45<br>0 | -                               | ns   |

| t <sub>h(SD_MR)</sub> (3)(4)<br>t <sub>h(SD_SR)</sub> (3)(4) | Data input hold time                      | Master receiver: f <sub>PCLK</sub> = 30 MHz,<br>Slave receiver: f <sub>PCLK</sub> = 30 MHz | 13<br>0 | -                               | *    |

| t <sub>v(SD_ST)</sub> (3)(4)                                 | Data output valid time                    | Slave transmitter (after enable edge)                                                      | -       | 30                              | *    |

| t <sub>h(SD_ST)</sub> <sup>(3)</sup>                         | Data output hold time                     | Slave transmitter (after enable edge)                                                      | 10      | -                               | •    |

| t <sub>v(SD_MT)</sub> <sup>(3)(4)</sup>                      | Data output valid time                    | Master transmitter (after enable edge)                                                     | -       | 6                               | 1    |

| t <sub>h(SD_MT)</sub> <sup>(3)</sup>                         | Data output hold time                     | Master transmitter (after enable edge)                                                     | 0       | -                               |      |

## Table 54. I<sup>2</sup>S characteristics

F<sub>S</sub> is the sampling frequency. Refer to the I2S section of the STM32F20xxx/21xxx reference manual for more details. f<sub>CK</sub> values reflect only the digital peripheral behavior which leads to a minimum of (I2SDIV/(2\*I2SDIV+ODD), a maximum of (I2SDIV+ODD)/(2\*I2SDIV+ODD) and F<sub>S</sub> maximum values for each mode/condition.

2. Refer to Table 47: I/O AC characteristics.

3. Guaranteed by design, not tested in production.

4. Depends on  $f_{PCLK}$ . For example, if  $f_{PCLK}$ =8 MHz, then  $T_{PCLK}$  = 1/ $f_{PLCLK}$  =125 ns.

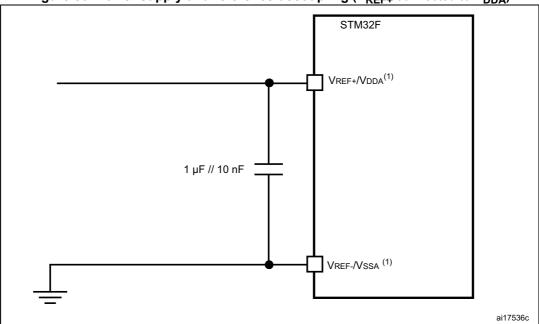

Figure 53. Power supply and reference decoupling ( $V_{REF+}$  connected to  $V_{DDA}$ )

| Symbol                           | Parameter                             | Min | Тур | Мах                    | Unit | Comments                                                                                                                                       |  |  |  |

|----------------------------------|---------------------------------------|-----|-----|------------------------|------|------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| V <sub>DDA</sub>                 | Analog supply voltage                 | 1.8 | -   | 3.6                    | V    | -                                                                                                                                              |  |  |  |

| V <sub>REF+</sub>                | Reference supply voltage              | 1.8 | -   | 3.6                    | V    | V <sub>REF+</sub> ≤V <sub>DDA</sub>                                                                                                            |  |  |  |

| V <sub>SSA</sub>                 | Ground                                | 0   | -   | 0                      | V    | -                                                                                                                                              |  |  |  |

| R <sub>LOAD</sub> <sup>(1)</sup> | Resistive load with buffer<br>ON      | 5   | -   | -                      | kΩ   | -                                                                                                                                              |  |  |  |

| R <sub>0</sub> <sup>(1)</sup>    | Impedance output with<br>buffer OFF   | -   | -   | 15                     | kΩ   | When the buffer is OFF, the Minimum resistive load between DAC_OUT and $V_{SS}$ to have a 1% accuracy is 1.5 M $\Omega$                        |  |  |  |

| C <sub>LOAD</sub> <sup>(1)</sup> | Capacitive load                       | -   | -   | 50                     | pF   | Maximum capacitive load at DAC_OUT pin (when the buffer is ON).                                                                                |  |  |  |

| DAC_OUT<br>min <sup>(1)</sup>    | Lower DAC_OUT voltage with buffer ON  | 0.2 | -   | -                      | v    | It gives the maximum output excursion<br>of the DAC.<br>It corresponds to 12-bit input code<br>(0x0E0) to (0xF1C) at V <sub>REF+</sub> = 3.6 V |  |  |  |

| DAC_OUT<br>max <sup>(1)</sup>    | Higher DAC_OUT voltage with buffer ON |     |     | V <sub>DDA</sub> – 0.2 | V    | and (0x1C7) to (0xE38) at $V_{REF+} = 3.0 \text{ V}$<br>1.8 V                                                                                  |  |  |  |

## 6.3.21 DAC electrical characteristics

Table 67. DAC characteristics

V<sub>REF+</sub> and V<sub>REF-</sub> inputs are both available on UFBGA176 package. V<sub>REF+</sub> is also available on all packages except for LQFP64. When V<sub>REF+</sub> and V<sub>REF-</sub> are not available, they are internally connected to V<sub>DDA</sub> and V<sub>SSA</sub>.

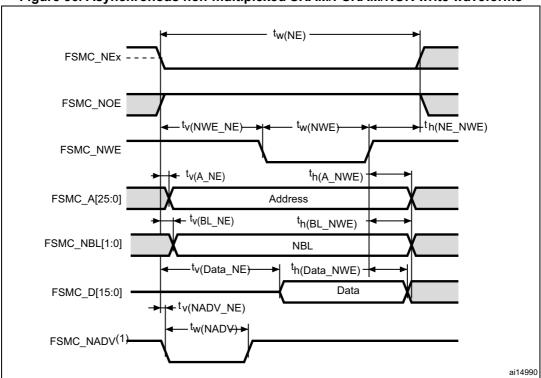

Figure 56. Asynchronous non-multiplexed SRAM/PSRAM/NOR write waveforms

1. Mode 2/B, C and D only. In Mode 1, FSMC\_NADV is not used.

| Table 72. / | Asynchronous non-multiplexed SRA | M/PSRAM/NO | R write timin | gs <sup>(1)(2)</sup> |

|-------------|----------------------------------|------------|---------------|----------------------|

|             |                                  |            |               |                      |

| Symbol                   | Parameter                                | Min                     | Max                     | Unit |

|--------------------------|------------------------------------------|-------------------------|-------------------------|------|

| t <sub>w(NE)</sub>       | FSMC_NE low time                         | 3T <sub>HCLK</sub>      | 3T <sub>HCLK</sub> + 4  | ns   |

| t <sub>v(NWE_NE</sub> )  | FSMC_NEx low to FSMC_NWE low             | T <sub>HCLK</sub> – 0.5 | T <sub>HCLK</sub> + 0.5 | ns   |

| t <sub>w(NWE)</sub>      | FSMC_NWE low time                        | T <sub>HCLK</sub> – 0.5 | T <sub>HCLK</sub> + 3   | ns   |

| t <sub>h(NE_NWE)</sub>   | FSMC_NWE high to FSMC_NE high hold time  | T <sub>HCLK</sub>       | -                       | ns   |

| t <sub>v(A_NE)</sub>     | FSMC_NEx low to FSMC_A valid             | -                       | 0                       | ns   |

| t <sub>h(A_NWE)</sub>    | Address hold time after FSMC_NWE high    | T <sub>HCLK</sub> - 3   | -                       | ns   |

| t <sub>v(BL_NE)</sub>    | FSMC_NEx low to FSMC_BL valid            | -                       | 0.5                     | ns   |

| t <sub>h(BL_NWE)</sub>   | FSMC_BL hold time after FSMC_NWE<br>high | T <sub>HCLK</sub> – 1   | -                       | ns   |

| t <sub>v(Data_NE)</sub>  | Data to FSMC_NEx low to Data valid       | -                       | T <sub>HCLK</sub> + 5   | ns   |

| t <sub>h(Data_NWE)</sub> | Data hold time after FSMC_NWE high       | T <sub>HCLK</sub> +0.5  | -                       | ns   |

| t <sub>v(NADV_NE)</sub>  | FSMC_NEx low to FSMC_NADV low            | -                       | 2                       | ns   |

| t <sub>w(NADV)</sub>     | FSMC_NADV low time                       | -                       | T <sub>HCLK</sub> + 1.5 | ns   |

1. C<sub>L</sub> = 30 pF.

2. Guaranteed by characterization results, not tested in production.

| Symbol                         | Parameter                                  | Min | Max | Unit |

|--------------------------------|--------------------------------------------|-----|-----|------|

| t <sub>d(CLKL-</sub><br>NADVL) | FSMC_CLK low to FSMC_NADV low              | -   | 5   | ns   |

| t <sub>d(CLKL-</sub><br>NADVH) | FSMC_CLK low to FSMC_NADV high             | 6   | -   | ns   |

| t <sub>d(CLKL-AV)</sub>        | FSMC_CLK low to FSMC_Ax valid (x=1625)     | -   | 0   | ns   |

| t <sub>d(CLKL-AIV)</sub>       | FSMC_CLK low to FSMC_Ax invalid (x=1625)   | 8   | -   | ns   |

| t <sub>d(CLKL-NWEL)</sub>      | FSMC_CLK low to FSMC_NWE low               | -   | 1   | ns   |

| t <sub>d(CLKL-NWEH)</sub>      | FSMC_CLK low to FSMC_NWE high              | 1   | -   | ns   |

| t <sub>d(CLKL-Data)</sub>      | FSMC_D[15:0] valid data after FSMC_CLK low | -   | 2   | ns   |

| t <sub>d(CLKL-NBLH)</sub>      | FSMC_CLK low to FSMC_NBL high              | 2   | -   | ns   |

Table 78. Synchronous non-multiplexed PSRAM write timings<sup>(1)(2)</sup> (continued)

1. C<sub>L</sub> = 30 pF.

2. Guaranteed by characterization results, not tested in production.

## PC Card/CompactFlash controller waveforms and timings

*Figure 63* through *Figure 68* represent synchronous waveforms, with *Table 79* and *Table 80* providing the corresponding timings. The results shown in these table are obtained with the following FSMC configuration:

- COM.FSMC\_SetupTime = 0x04;

- COM.FSMC\_WaitSetupTime = 0x07;

- COM.FSMC\_HoldSetupTime = 0x04;

- COM.FSMC\_HiZSetupTime = 0x00;

- ATT.FSMC\_SetupTime = 0x04;

- ATT.FSMC\_WaitSetupTime = 0x07;

- ATT.FSMC HoldSetupTime = 0x04;

- ATT.FSMC\_HiZSetupTime = 0x00;

- IO.FSMC\_SetupTime = 0x04;

- IO.FSMC\_WaitSetupTime = 0x07;

- IO.FSMC HoldSetupTime = 0x04;

- IO.FSMC\_HiZSetupTime = 0x00;

- TCLRSetupTime = 0;

- TARSetupTime = 0;

In all timing tables, the  $T_{HCLK}$  is the HCLK clock period.

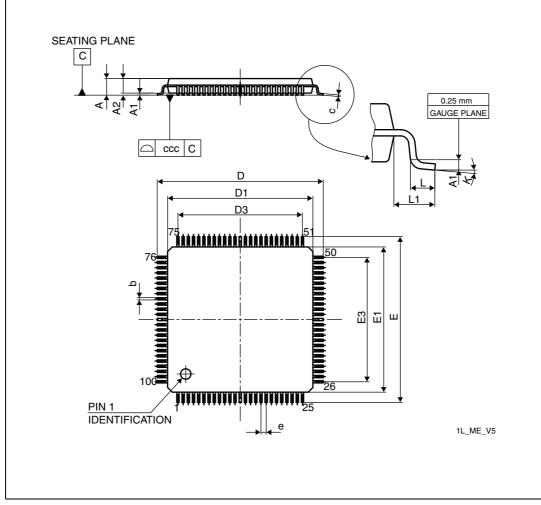

# 7.2 LQFP100 package information

Figure 77. LQFP100 - 100-pin, 14 x 14 mm low-profile quad flat package outline

1. Drawing is not to scale.

| mechanical data |             |        |        |                       |        |        |  |  |

|-----------------|-------------|--------|--------|-----------------------|--------|--------|--|--|

| Symbol          | millimeters |        |        | inches <sup>(1)</sup> |        |        |  |  |

|                 | Min         | Тур    | Max    | Min                   | Тур    | Мах    |  |  |

| А               | -           | -      | 1.600  | -                     | -      | 0.0630 |  |  |

| A1              | 0.050       | -      | 0.150  | 0.0020                | -      | 0.0059 |  |  |

| A2              | 1.350       | 1.400  | 1.450  | 0.0531                | 0.0551 | 0.0571 |  |  |

| b               | 0.170       | 0.220  | 0.270  | 0.0067                | 0.0087 | 0.0106 |  |  |

| С               | 0.090       | -      | 0.200  | 0.0035                | -      | 0.0079 |  |  |

| D               | 15.800      | 16.000 | 16.200 | 0.6220                | 0.6299 | 0.6378 |  |  |

| D1              | 13.800      | 14.000 | 14.200 | 0.5433                | 0.5512 | 0.5591 |  |  |

Table 87. LQPF100 - 100-pin, 14 x 14 mm low-profile quad flat package mechanical data

| Date        | Revision | Changes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |  |  |

|-------------|----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| 14-Jun-2011 | 5        | Added SDIO in <i>Table 2: STM32F215xx and STM32F217xx: features</i><br>and peripheral counts.<br>Updated V <sub>IN</sub> for 5V tolerant pins in <i>Table 10: Voltage characteristics</i> .<br>Updated jitter parameters description in <i>Table 33: Main PLL</i><br><i>characteristics</i> .<br>Remove jitter values for system clock in <i>Table 34: PLLI2S (audio PLL)</i><br><i>characteristics</i> .<br>Updated <i>Table 41: EMI characteristics</i> .<br>Updated <i>Table 41: EMI characteristics</i> .<br>Updated Avg_Slope typical value and $T_{S\_temp}$ minimum value in<br><i>Table 68: Temperature sensor characteristics</i> .<br>Updated $T_{S\_vbat}$ minimum value in <i>Table 69: VBAT monitoring</i><br><i>characteristics</i> .<br>Updated $T_{S\_vbat}$ minimum value in <i>Table 70: Embedded internal</i><br><i>reference voltage</i> .<br>Added Software option in <i>Section 8: Ordering information</i> .<br>In <i>Table 93: Main applications versus package for STM32F2xxx</i><br><i>microcontrollers</i> , renamed USB1 and USB2, USB OTG FS and USB<br>OTG HS, respectively; and removed USB OTG HS on 64-pin package;<br>and added <i>Note 1</i> and <i>Note 2</i> .<br>Updated disclaimer on cover page. |  |  |  |  |

|             |          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |  |  |  |

| Table 94. Document revision history (continued) | Table 94 | . Document | revision | history | (continued) |

|-------------------------------------------------|----------|------------|----------|---------|-------------|

|-------------------------------------------------|----------|------------|----------|---------|-------------|

#### IMPORTANT NOTICE - PLEASE READ CAREFULLY

STMicroelectronics NV and its subsidiaries ("ST") reserve the right to make changes, corrections, enhancements, modifications, and improvements to ST products and/or to this document at any time without notice. Purchasers should obtain the latest relevant information on ST products before placing orders. ST products are sold pursuant to ST's terms and conditions of sale in place at the time of order acknowledgement.

Purchasers are solely responsible for the choice, selection, and use of ST products and ST assumes no liability for application assistance or the design of Purchasers' products.

No license, express or implied, to any intellectual property right is granted by ST herein.

Resale of ST products with provisions different from the information set forth herein shall void any warranty granted by ST for such product.

ST and the ST logo are trademarks of ST. All other product or service names are the property of their respective owners.

Information in this document supersedes and replaces information previously supplied in any prior versions of this document.

© 2016 STMicroelectronics – All rights reserved

DocID17050 Rev 13