#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

-XF

| Product Status             | Active                                                                     |

|----------------------------|----------------------------------------------------------------------------|

| Core Processor             | ARM® Cortex®-M3                                                            |

| Core Size                  | 32-Bit Single-Core                                                         |

| Speed                      | 48MHz                                                                      |

| Connectivity               | I <sup>2</sup> C, IrDA, SmartCard, SPI, UART/USART                         |

| Peripherals                | Brown-out Detect/Reset, DMA, LCD, POR, PWM, WDT                            |

| Number of I/O              | 53                                                                         |

| Program Memory Size        | 512KB (512K x 8)                                                           |

| Program Memory Type        | FLASH                                                                      |

| EEPROM Size                | -                                                                          |

| RAM Size                   | 128K x 8                                                                   |

| Voltage - Supply (Vcc/Vdd) | 1.98V ~ 3.8V                                                               |

| Data Converters            | A/D 8x12b; D/A 2x12b                                                       |

| Oscillator Type            | Internal                                                                   |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                          |

| Mounting Type              | Surface Mount                                                              |

| Package / Case             | 64-VFQFN Exposed Pad                                                       |

| Supplier Device Package    | 64-QFN (9x9)                                                               |

| Purchase URL               | https://www.e-xfl.com/product-detail/silicon-labs/efm32gg940f512g-e-qfn64r |

|                            |                                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# **1 Ordering Information**

Table 1.1 (p. 2) shows the available EFM32GG940 devices.

#### Table 1.1. Ordering Information

| Ordering Code            | Flash (kB) | RAM (kB) | Max<br>Speed<br>(MHz) | Supply<br>Voltage<br>(V) | Temperature<br>(ºC) | Package |

|--------------------------|------------|----------|-----------------------|--------------------------|---------------------|---------|

| EFM32GG940F512G-E-QFN64  | 512        | 128      | 48                    | 1.98 - 3.8               | -40 - 85            | QFN64   |

| EFM32GG940F1024G-E-QFN64 | 1024       | 128      | 48                    | 1.98 - 3.8               | -40 - 85            | QFN64   |

Adding the suffix 'R' to the part number (e.g. EFM32GG940F512G-E-QFN64R) denotes tape and reel.

Visit www.silabs.com for information on global distributors and representatives.

# 2.1.3 Memory System Controller (MSC)

The Memory System Controller (MSC) is the program memory unit of the EFM32GG microcontroller. The flash memory is readable and writable from both the Cortex-M3 and DMA. The flash memory is divided into two blocks; the main block and the information block. Program code is normally written to the main block. Additionally, the information block is available for special user data and flash lock bits. There is also a read-only page in the information block containing system and device calibration data. Read and write operations are supported in the energy modes EM0 and EM1.

# 2.1.4 Direct Memory Access Controller (DMA)

The Direct Memory Access (DMA) controller performs memory operations independently of the CPU. This has the benefit of reducing the energy consumption and the workload of the CPU, and enables the system to stay in low energy modes when moving for instance data from the USART to RAM or from the External Bus Interface to a PWM-generating timer. The DMA controller uses the PL230  $\mu$ DMA controller licensed from ARM.

## 2.1.5 Reset Management Unit (RMU)

The RMU is responsible for handling the reset functionality of the EFM32GG.

### 2.1.6 Energy Management Unit (EMU)

The Energy Management Unit (EMU) manage all the low energy modes (EM) in EFM32GG microcontrollers. Each energy mode manages if the CPU and the various peripherals are available. The EMU can also be used to turn off the power to unused SRAM blocks.

### 2.1.7 Clock Management Unit (CMU)

The Clock Management Unit (CMU) is responsible for controlling the oscillators and clocks on-board the EFM32GG. The CMU provides the capability to turn on and off the clock on an individual basis to all peripheral modules in addition to enable/disable and configure the available oscillators. The high degree of flexibility enables software to minimize energy consumption in any specific application by not wasting power on peripherals and oscillators that are inactive.

## 2.1.8 Watchdog (WDOG)

The purpose of the watchdog timer is to generate a reset in case of a system failure, to increase application reliability. The failure may e.g. be caused by an external event, such as an ESD pulse, or by a software failure.

## 2.1.9 Peripheral Reflex System (PRS)

The Peripheral Reflex System (PRS) system is a network which lets the different peripheral module communicate directly with each other without involving the CPU. Peripheral modules which send out Reflex signals are called producers. The PRS routes these reflex signals to consumer peripherals which apply actions depending on the data received. The format for the Reflex signals is not given, but edge triggers and other functionality can be applied by the PRS.

## 2.1.10 Universal Serial Bus Controller (USB)

The USB is a full-speed USB 2.0 compliant OTG host/device controller. The USB can be used in Device, On-the-go (OTG) Dual Role Device or Host-only configuration. In OTG mode the USB supports both Host Negotiation Protocol (HNP) and Session Request Protocol (SRP). The device supports both full-speed (12MBit/s) and low speed (1.5MBit/s) operation. The USB device includes an internal dedicated

Descriptor-Based Scatter/Gather DMA and supports up to 6 OUT endpoints and 6 IN endpoints, in addition to endpoint 0. The on-chip PHY includes all OTG features, except for the voltage booster for supplying 5V to VBUS when operating as host.

## 2.1.11 Inter-Integrated Circuit Interface (I2C)

The I<sup>2</sup>C module provides an interface between the MCU and a serial I<sup>2</sup>C-bus. It is capable of acting as both a master and a slave, and supports multi-master buses. Both standard-mode, fast-mode and fast-mode plus speeds are supported, allowing transmission rates all the way from 10 kbit/s up to 1 Mbit/s. Slave arbitration and timeouts are also provided to allow implementation of an SMBus compliant system. The interface provided to software by the I<sup>2</sup>C module, allows both fine-grained control of the transmission process and close to automatic transfers. Automatic recognition of slave addresses is provided in all energy modes.

# 2.1.12 Universal Synchronous/Asynchronous Receiver/Transmitter (US-ART)

The Universal Synchronous Asynchronous serial Receiver and Transmitter (USART) is a very flexible serial I/O module. It supports full duplex asynchronous UART communication as well as RS-485, SPI, MicroWire and 3-wire. It can also interface with ISO7816 SmartCards, IrDA and I2S devices.

# 2.1.13 Pre-Programmed USB/UART Bootloader

The bootloader presented in application note AN0042 is pre-programmed in the device at factory. The bootloader enables users to program the EFM32 through a UART or a USB CDC class virtual UART without the need for a debugger. The autobaud feature, interface and commands are described further in the application note.

# 2.1.14 Low Energy Universal Asynchronous Receiver/Transmitter (LEUART)

The unique LEUART<sup>TM</sup>, the Low Energy UART, is a UART that allows two-way UART communication on a strict power budget. Only a 32.768 kHz clock is needed to allow UART communication up to 9600 baud/s. The LEUART includes all necessary hardware support to make asynchronous serial communication possible with minimum of software intervention and energy consumption.

## 2.1.15 Timer/Counter (TIMER)

The 16-bit general purpose Timer has 3 compare/capture channels for input capture and compare/Pulse-Width Modulation (PWM) output. TIMER0 also includes a Dead-Time Insertion module suitable for motor control applications.

# 2.1.16 Real Time Counter (RTC)

The Real Time Counter (RTC) contains a 24-bit counter and is clocked either by a 32.768 kHz crystal oscillator, or a 32.768 kHz RC oscillator. In addition to energy modes EM0 and EM1, the RTC is also available in EM2. This makes it ideal for keeping track of time since the RTC is enabled in EM2 where most of the device is powered down.

## 2.1.17 Backup Real Time Counter (BURTC)

The Backup Real Time Counter (BURTC) contains a 32-bit counter and is clocked either by a 32.768 kHz crystal oscillator, a 32.768 kHz RC oscillator or a 1 kHz ULFRCO. The BURTC is available in all Energy Modes and it can also run in backup mode, making it operational even if the main power should drain out.

| Module   | Configuration                             | Pin Connections                                                                    |  |

|----------|-------------------------------------------|------------------------------------------------------------------------------------|--|

| СМU      | Full configuration                        | CMU_OUT0, CMU_OUT1                                                                 |  |

| WDOG     | Full configuration                        | NA                                                                                 |  |

| PRS      | Full configuration                        | NA                                                                                 |  |

| USB      | Full configuration                        | USB_VBUS, USB_VBUSEN,<br>USB_VREGI, USB_VREGO, USB_DM,<br>USB_DMPU, USB_DP, USB_ID |  |

| 12C0     | Full configuration                        | I2C0_SDA, I2C0_SCL                                                                 |  |

| I2C1     | Full configuration                        | I2C1_SDA, I2C1_SCL                                                                 |  |

| USART0   | Full configuration with IrDA              | US0_TX, US0_RX. US0_CLK, US0_CS                                                    |  |

| USART1   | Full configuration with I2S               | US1_TX, US1_RX, US1_CLK, US1_CS                                                    |  |

| USART2   | Full configuration with I2S               | US2_TX, US2_RX, US2_CLK, US2_CS                                                    |  |

| LEUART0  | Full configuration                        | LEU0_TX, LEU0_RX                                                                   |  |

| LEUART1  | Full configuration                        | LEU1_TX, LEU1_RX                                                                   |  |

| TIMER0   | Full configuration with DTI               | TIM0_CC[2:0], TIM0_CDTI[2:0]                                                       |  |

| TIMER1   | Full configuration                        | TIM1_CC[2:0]                                                                       |  |

| TIMER2   | Full configuration                        | TIM2_CC[2:0]                                                                       |  |

| TIMER3   | Full configuration                        | TIM3_CC[2:0]                                                                       |  |

| RTC      | Full configuration                        | NA                                                                                 |  |

| BURTC    | Full configuration                        | NA                                                                                 |  |

| LETIMER0 | Full configuration                        | LET0_O[1:0]                                                                        |  |

| PCNT0    | Full configuration, 16-bit count register | PCNT0_S[1:0]                                                                       |  |

| PCNT1    | Full configuration, 8-bit count register  | PCNT1_S[1:0]                                                                       |  |

| PCNT2    | Full configuration, 8-bit count register  | PCNT2_S[1:0]                                                                       |  |

| ACMP0    | Full configuration                        | ACMP0_CH[7:0], ACMP0_O                                                             |  |

| ACMP1    | Full configuration                        | ACMP1_CH[7:0], ACMP1_O                                                             |  |

| VCMP     | Full configuration                        | NA                                                                                 |  |

| ADC0     | Full configuration                        | ADC0_CH[7:0]                                                                       |  |

| DAC0     | Full configuration                        | DAC0_OUT[1:0], DAC0_OUTxALT                                                        |  |

| OPAMP    | Full configuration                        | Outputs: OPAMP_OUTx,<br>OPAMP_OUTxALT, Inputs:<br>OPAMP_Px, OPAMP_Nx               |  |

| AES      | Full configuration                        | NA                                                                                 |  |

| GPIO     | 52 pins                                   | Available pins are shown in<br>Table 4.3 (p. 59)                                   |  |

| LCD      | Full configuration                        | LCD_SEG[17:0], LCD_COM[7:0],<br>LCD_BCAP_P, LCD_BCAP_N,<br>LCD_BEXT                |  |

# 2.3 Memory Map

The *EFM32GG940* memory map is shown in Figure 2.2 (p. 9), with RAM and Flash sizes for the largest memory configuration.

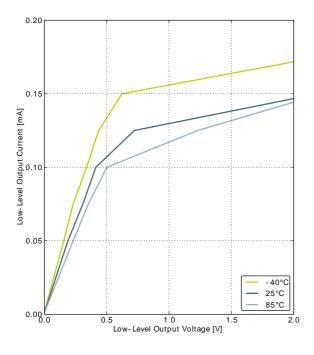

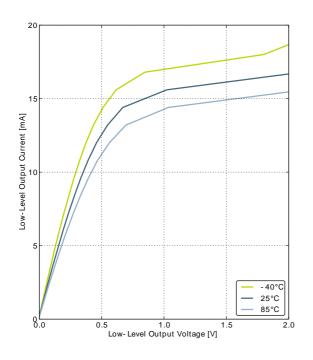

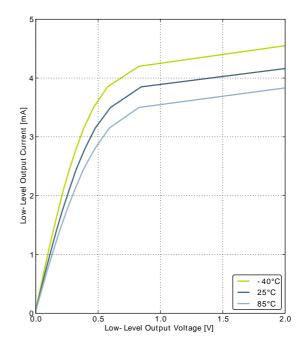

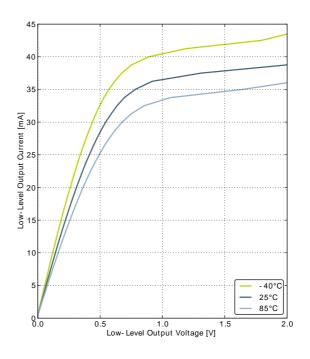

### Figure 3.4. Typical Low-Level Output Current, 2V Supply Voltage

GPIO\_Px\_CTRL DRIVEMODE = LOWEST

GPIO\_Px\_CTRL DRIVEMODE = STANDARD

GPIO\_Px\_CTRL DRIVEMODE = LOW

GPIO\_Px\_CTRL DRIVEMODE = HIGH

# 3.9 Oscillators

## 3.9.1 LFXO

#### Table 3.8. LFXO

| Symbol              | Parameter                                                      | Condition                                                                                                      | Min            | Тур    | Max  | Unit |

|---------------------|----------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------|----------------|--------|------|------|

| f <sub>LFXO</sub>   | Supported nominal crystal frequency                            |                                                                                                                |                | 32.768 |      | kHz  |

| ESR <sub>LFXO</sub> | Supported crystal<br>equivalent series re-<br>sistance (ESR)   |                                                                                                                |                | 30     | 120  | kOhm |

| C <sub>LFXOL</sub>  | Supported crystal external load range                          |                                                                                                                | X <sup>1</sup> |        | 25   | pF   |

| DC <sub>LFXO</sub>  | Duty cycle                                                     |                                                                                                                | 48             | 50     | 53.5 | %    |

| I <sub>LFXO</sub>   | Current consump-<br>tion for core and<br>buffer after startup. | ESR=30 kOhm, C <sub>L</sub> =10 pF,<br>LFXOBOOST in CMU_CTRL is<br>1                                           |                | 190    |      | nA   |

| t <sub>LFXO</sub>   | Start- up time.                                                | ESR=30 kOhm, C <sub>L</sub> =10 pF,<br>40% - 60% duty cycle has<br>been reached, LFXOBOOST in<br>CMU_CTRL is 1 |                | 400    |      | ms   |

<sup>1</sup>See Minimum Load Capacitance (C<sub>LFXOL</sub>) Requirement For Safe Crystal Startup in energyAware Designer in Simplicity Studio

For safe startup of a given crystal, the Configurator tool in Simplicity Studio contains a tool to help users configure both load capacitance and software settings for using the LFXO. For details regarding the crystal configuration, the reader is referred to application note "AN0016 EFM32 Oscillator Design Consideration".

## 3.9.2 HFXO

#### Table 3.9. HFXO

| Symbol              | Parameter                                                                       | Condition                                                                            | Min | Тур | Max  | Unit |

|---------------------|---------------------------------------------------------------------------------|--------------------------------------------------------------------------------------|-----|-----|------|------|

| f <sub>HFXO</sub>   | Supported nominal crystal Frequency                                             |                                                                                      | 4   |     | 48   | MHz  |

|                     | Supported crystal                                                               | Crystal frequency 48 MHz                                                             |     |     | 50   | Ohm  |

| ESR <sub>HFXO</sub> | equivalent series re-                                                           | Crystal frequency 32 MHz                                                             |     | 30  | 60   | Ohm  |

|                     | sistance (ESR)                                                                  | Crystal frequency 4 MHz                                                              |     | 400 | 1500 | Ohm  |

| g <sub>mHFXO</sub>  | The transconduc-<br>tance of the HFXO<br>input transistor at<br>crystal startup | HFXOBOOST in CMU_CTRL<br>equals 0b11                                                 | 20  |     |      | mS   |

| C <sub>HFXOL</sub>  | Supported crystal external load range                                           |                                                                                      | 5   |     | 25   | pF   |

| 1 .                 | Current consump-                                                                | 4 MHz: ESR=400 Ohm,<br>C <sub>L</sub> =20 pF, HFXOBOOST in<br>CMU_CTRL equals 0b11   |     | 85  |      | μA   |

| IHFXO               | startup                                                                         | 32 MHz: ESR=30 Ohm,<br>C <sub>L</sub> =10 pF, HFXOBOOST in<br>CMU_CTRL equals $0b11$ |     | 165 |      | μA   |

| t <sub>HFXO</sub>   | Startup time                                                                    | 32 MHz: ESR=30 Ohm,<br>C <sub>L</sub> =10 pF, HFXOBOOST in<br>CMU_CTRL equals 0b11   |     | 400 |      | μs   |

| Symbol                         | Parameter                                           | Condition                    | Min | Тур              | Max | Unit |

|--------------------------------|-----------------------------------------------------|------------------------------|-----|------------------|-----|------|

|                                |                                                     | f <sub>HFRCO</sub> = 28 MHz  |     | 165              | 190 | μA   |

|                                |                                                     | f <sub>HFRCO</sub> = 21 MHz  |     | 134              | 155 | μA   |

| 1                              | Current consump-                                    | f <sub>HFRCO</sub> = 14 MHz  |     | 106              | 120 | μA   |

| IHFRCO                         | tion (Production test<br>condition = 14MHz)         | f <sub>HFRCO</sub> = 11 MHz  |     | 94               | 110 | μA   |

|                                |                                                     | f <sub>HFRCO</sub> = 6.6 MHz |     | 77               | 90  | μA   |

|                                |                                                     | f <sub>HFRCO</sub> = 1.2 MHz |     | 25               | 32  | μA   |

| TUNESTEP <sub>H-</sub><br>FRCO | Frequency step<br>for LSB change in<br>TUNING value |                              |     | 0.3 <sup>3</sup> |     | %    |

<sup>1</sup>For devices with prod. rev. < 19, Typ = 7MHz and Min/Max values not applicable.

$^{2}$ For devices with prod. rev. < 19, Typ = 1MHz and Min/Max values not applicable.

<sup>3</sup>The TUNING field in the CMU\_HFRCOCTRL register may be used to adjust the HFRCO frequency. There is enough adjustment range to ensure that the frequency bands above 7 MHz will always have some overlap across supply voltage and temperature. By using a stable frequency reference such as the LFXO or HFXO, a firmware calibration routine can vary the TUNING bits and the frequency band to maintain the HFRCO frequency at any arbitrary value between 7 MHz and 28 MHz across operating conditions.

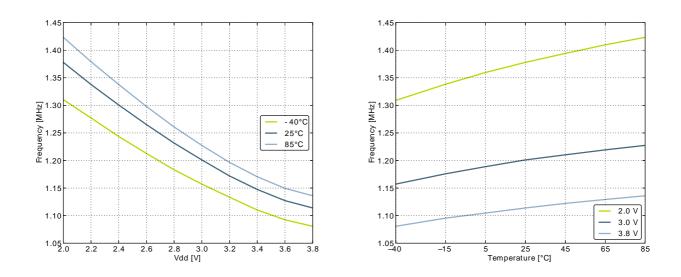

Figure 3.11. Calibrated HFRCO 1 MHz Band Frequency vs Supply Voltage and Temperature

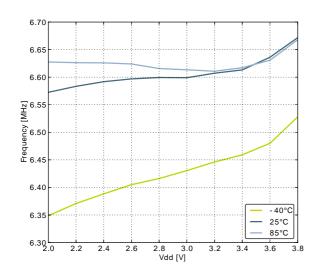

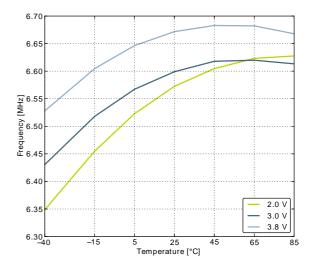

Figure 3.12. Calibrated HFRCO 7 MHz Band Frequency vs Supply Voltage and Temperature

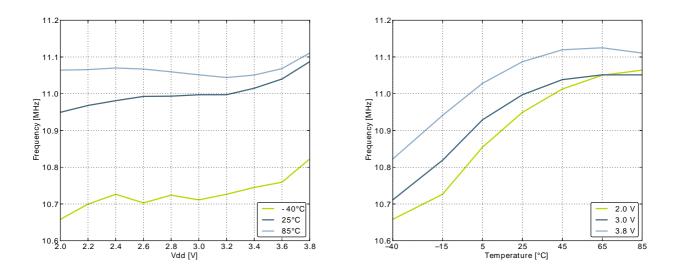

Figure 3.13. Calibrated HFRCO 11 MHz Band Frequency vs Supply Voltage and Temperature

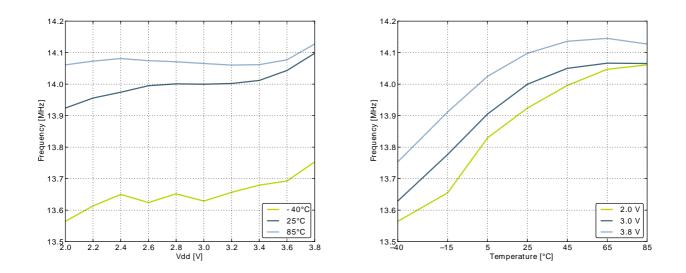

Figure 3.14. Calibrated HFRCO 14 MHz Band Frequency vs Supply Voltage and Temperature

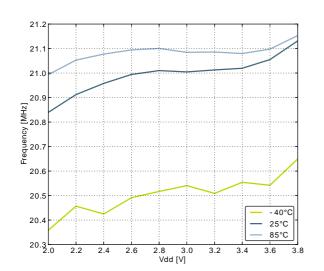

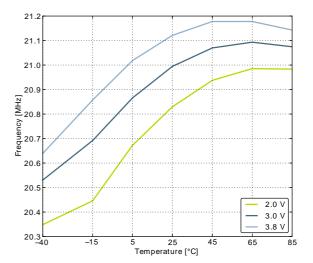

Figure 3.15. Calibrated HFRCO 21 MHz Band Frequency vs Supply Voltage and Temperature

| Symbol                 | Parameter                          | Condition                                                                | Min | Тур | Max | Unit |

|------------------------|------------------------------------|--------------------------------------------------------------------------|-----|-----|-----|------|

|                        |                                    | 500 kSamples/s, 12 bit, differ-<br>ential, internal 2.5V reference       |     | 58  |     | dB   |

|                        |                                    | 500 kSamples/s, 12 bit, differential, $V_{DD}$ reference                 |     | 59  |     | dB   |

|                        |                                    | 500 kSamples/s, 12 bit, sin-<br>gle ended, internal 1.25V refer-<br>ence |     | 57  |     | dB   |

|                        | Signal to Noise-                   | 500 kSamples/s, 12 bit, single ended, internal 2.5V reference            |     | 54  |     | dB   |

| SNDR <sub>DAC</sub>    | pulse Distortion Ra-<br>tio (SNDR) | 500 kSamples/s, 12 bit, differ-<br>ential, internal 1.25V reference      |     | 56  |     | dB   |

|                        |                                    | 500 kSamples/s, 12 bit, differ-<br>ential, internal 2.5V reference       |     | 53  |     | dB   |

|                        |                                    | 500 kSamples/s, 12 bit, differential, $V_{\text{DD}}$ reference          |     | 55  |     | dB   |

|                        |                                    | 500 kSamples/s, 12 bit, sin-<br>gle ended, internal 1.25V refer-<br>ence |     | 62  |     | dBc  |

|                        | Spurious-Free                      | 500 kSamples/s, 12 bit, single ended, internal 2.5V reference            |     | 56  |     | dBc  |

| SFDR <sub>DAC</sub>    | Dynamic<br>Range(SFDR)             | 500 kSamples/s, 12 bit, differ-<br>ential, internal 1.25V reference      |     | 61  |     | dBc  |

|                        |                                    | 500 kSamples/s, 12 bit, differ-<br>ential, internal 2.5V reference       |     | 55  |     | dBc  |

|                        |                                    | 500 kSamples/s, 12 bit, differential, $V_{\text{DD}}$ reference          |     | 60  |     | dBc  |

| N/                     | Offeet veltege                     | After calibration, single ended                                          |     | 2   | 12  | mV   |

| V <sub>DACOFFSET</sub> | Offset voltage                     | After calibration, differential                                          |     | 2   |     | mV   |

| DNL <sub>DAC</sub>     | Differential non-lin-<br>earity    |                                                                          |     | ±1  |     | LSB  |

| INL <sub>DAC</sub>     | Integral non-lineari-<br>ty        |                                                                          |     | ±5  |     | LSB  |

| MC <sub>DAC</sub>      | No missing codes                   |                                                                          |     | 12  |     | bits |

<sup>1</sup>Measured with a static input code and no loading on the output.

# 3.12 Operational Amplifier (OPAMP)

The electrical characteristics for the Operational Amplifiers are based on simulations.

#### Table 3.16. OPAMP

| Symbol | Parameter      | Condition                                                | Min | Тур | Max | Unit |

|--------|----------------|----------------------------------------------------------|-----|-----|-----|------|

|        |                | (OPA2)BIASPROG=0xF,<br>(OPA2)HALFBIAS=0x0, Unity<br>Gain | 350 | 405 | μA  |      |

|        | Active Current | (OPA2)BIASPROG=0x7,<br>(OPA2)HALFBIAS=0x1, Unity<br>Gain |     | 95  | 115 | μA   |

| Symbol | Parameter | Condition                                                                                                                                  | Min | Тур  | Max | Unit              |

|--------|-----------|--------------------------------------------------------------------------------------------------------------------------------------------|-----|------|-----|-------------------|

|        |           | V <sub>out</sub> =1V, RESSEL=0, 0.1<br>Hz <f<1 mhz,="" opaxhcmdis="0&lt;/td"><td></td><td>196</td><td></td><td>μV<sub>RMS</sub></td></f<1> |     | 196  |     | μV <sub>RMS</sub> |

|        |           | V <sub>out</sub> =1V, RESSEL=0, 0.1<br>Hz <f<1 mhz,="" opaxhcmdis="1&lt;/td"><td></td><td>229</td><td></td><td>μV<sub>RMS</sub></td></f<1> |     | 229  |     | μV <sub>RMS</sub> |

|        |           | RESSEL=7, 0.1 Hz <f<10 khz,<br="">OPAxHCMDIS=0</f<10>                                                                                      |     | 1230 |     | μV <sub>RMS</sub> |

|        |           | RESSEL=7, 0.1 Hz <f<10 khz,<br="">OPAxHCMDIS=1</f<10>                                                                                      |     | 2130 |     | μV <sub>RMS</sub> |

|        |           | RESSEL=7, 0.1 Hz <f<1 mhz,<br="">OPAxHCMDIS=0</f<1>                                                                                        |     | 1630 |     | μV <sub>RMS</sub> |

|        |           | RESSEL=7, 0.1 Hz <f<1 mhz,<br="">OPAxHCMDIS=1</f<1>                                                                                        |     | 2590 |     | μV <sub>RMS</sub> |

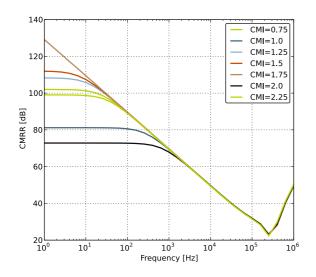

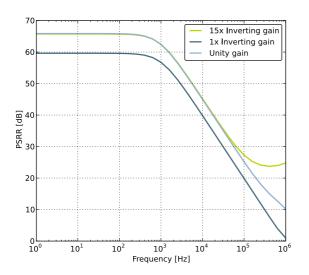

Figure 3.26. OPAMP Positive Power Supply Rejection Ratio

# 3.14 Voltage Comparator (VCMP)

#### Table 3.18. VCMP

| Symbol                  | Parameter                             | Condition                                                             | Min  | Тур             | Мах | Unit |

|-------------------------|---------------------------------------|-----------------------------------------------------------------------|------|-----------------|-----|------|

| V <sub>VCMPIN</sub>     | Input voltage range                   |                                                                       |      | V <sub>DD</sub> |     | V    |

| V <sub>VCMPCM</sub>     | VCMP Common<br>Mode voltage range     |                                                                       |      | V <sub>DD</sub> |     | V    |

| 1                       | Active current                        | BIASPROG=0b0000 and<br>HALFBIAS=1 in VCMPn_CTRL<br>register           |      | 0.3             | 0.6 | μA   |

| IVCMP                   |                                       | BIASPROG=0b1111 and<br>HALFBIAS=0 in VCMPn_CTRL<br>register. LPREF=0. |      | 22              | 30  | μA   |

| t <sub>VCMPREF</sub>    | Startup time refer-<br>ence generator | NORMAL                                                                |      | 10              |     | μs   |

| M                       | Offect veltage                        | Single ended                                                          | -230 | -40             | 190 | mV   |

| V <sub>VCMPOFFSET</sub> | Offset voltage                        | Differential                                                          |      | 10              |     | mV   |

| V <sub>VCMPHYST</sub>   | VCMP hysteresis                       |                                                                       |      | 40              |     | mV   |

| t <sub>VCMPSTART</sub>  | Startup time                          |                                                                       |      |                 | 10  | μs   |

The  $V_{DD}$  trigger level can be configured by setting the TRIGLEVEL field of the VCMP\_CTRL register in accordance with the following equation:

VCMP Trigger Level as a Function of Level Setting

V<sub>DD Trigger Level</sub>=1.667V+0.034 ×TRIGLEVEL

(3.2)

# **4 Pinout and Package**

#### Note

Please refer to the application note "AN0002 EFM32 Hardware Design Considerations" for guidelines on designing Printed Circuit Boards (PCB's) for the EFM32GG940.

### 4.1 Pinout

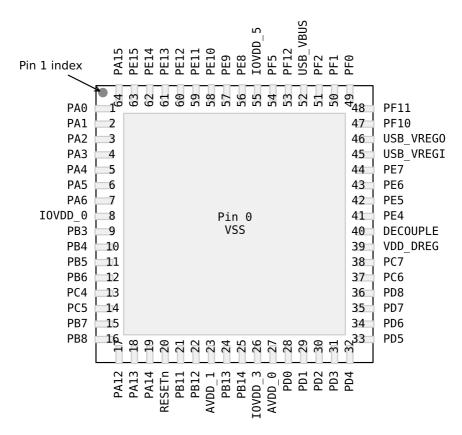

The *EFM32GG940* pinout is shown in Figure 4.1 (p. 51) and Table 4.1 (p. 51). Alternate locations are denoted by "#" followed by the location number (Multiple locations on the same pin are split with "/"). Alternate locations can be configured in the LOCATION bitfield in the \*\_ROUTE register in the module in question.

#### Figure 4.1. EFM32GG940 Pinout (top view, not to scale)

Table 4.1. Device Pinout

|       | QFN64 Pin#<br>and Name |           |                 |                           |                           |

|-------|------------------------|-----------|-----------------|---------------------------|---------------------------|

| Pin # | Pin Name               | Analog    | Timers          | Communication             | Other                     |

| 0     | VSS                    | Ground.   |                 |                           |                           |

| 1     | PA0                    | LCD_SEG13 | TIM0_CC0 #0/1/4 | I2C0_SDA #0<br>LEU0_RX #4 | PRS_CH0 #0<br>GPIO_EM4WU0 |

| 2     | PA1                    | LCD_SEG14 | TIM0_CC1 #0/1   | I2C0_SCL #0               | CMU_CLK1 #0<br>PRS_CH1 #0 |

# **EFM°32**

#### ...the world's most energy friendly microcontrollers

| Alternate                       |      |      | LOC | ATION |     |     |      |                                                                                                                                                                       |

|---------------------------------|------|------|-----|-------|-----|-----|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Functionality                   | 0    | 1    | 2   | 3     | 4   | 5   | 6    | Description                                                                                                                                                           |

| OPAMP_N1                        | PD7  |      |     |       |     |     |      | Operational Amplifier 1 external negative input.                                                                                                                      |

| OPAMP_N2                        | PD3  |      |     |       |     |     |      | Operational Amplifier 2 external negative input.                                                                                                                      |

| DAC0_OUT0 /<br>OPAMP_OUT0       | PB11 |      |     |       |     |     |      | Digital to Analog Converter DAC0_OUT0 / OPAMP output channel number 0.                                                                                                |

| DAC0_OUT0ALT /<br>OPAMP_OUT0ALT |      |      |     |       | PD0 |     |      | Digital to Analog Converter DAC0_OUT0ALT / OPAMP alternative output for channel 0.                                                                                    |

| DAC0_OUT1 /<br>OPAMP_OUT1       | PB12 |      |     |       |     |     |      | Digital to Analog Converter DAC0_OUT1 /<br>OPAMP output channel number 1.                                                                                             |

| DAC0_OUT1ALT /<br>OPAMP_OUT1ALT |      |      |     |       | PD1 |     |      | Digital to Analog Converter DAC0_OUT1ALT / OPAMP alternative output for channel 1.                                                                                    |

| OPAMP_OUT2                      | PD5  | PD0  |     |       |     |     |      | Operational Amplifier 2 output.                                                                                                                                       |

| OPAMP_P0                        | PC4  |      |     |       |     |     |      | Operational Amplifier 0 external positive input.                                                                                                                      |

| OPAMP_P1                        | PD6  |      |     |       |     |     |      | Operational Amplifier 1 external positive input.                                                                                                                      |

| OPAMP_P2                        | PD4  |      |     |       |     |     |      | Operational Amplifier 2 external positive input.                                                                                                                      |

|                                 |      |      |     |       |     |     |      | Debug-interface Serial Wire clock input.                                                                                                                              |

| DBG_SWCLK                       | PF0  | PF0  | PF0 | PF0   |     |     |      | Note that this function is enabled to pin out of reset, and has a built-in pull down.                                                                                 |

|                                 |      |      |     |       |     |     |      | Debug-interface Serial Wire data input / output.                                                                                                                      |

| DBG_SWDIO                       | PF1  | PF1  | PF1 | PF1   |     |     |      | Note that this function is enabled to pin out of reset, and has a built-in pull up.                                                                                   |

|                                 |      |      |     |       |     |     |      | Debug-interface Serial Wire viewer Output.                                                                                                                            |

| DBG_SWO                         | PF2  |      | PD1 | PD2   |     |     |      | Note that this function is not enabled after reset, and must be enabled by software to be used.                                                                       |

| ETM_TCLK                        | PD7  |      | PC6 | PA6   |     |     |      | Embedded Trace Module ETM clock .                                                                                                                                     |

| ETM_TD0                         | PD6  |      | PC7 | PA2   |     |     |      | Embedded Trace Module ETM data 0.                                                                                                                                     |

| ETM_TD1                         | PD3  |      | PD3 | PA3   |     |     |      | Embedded Trace Module ETM data 1.                                                                                                                                     |

| ETM_TD2                         | PD4  |      | PD4 | PA4   |     |     |      | Embedded Trace Module ETM data 2.                                                                                                                                     |

| ETM_TD3                         | PD5  |      | PD5 | PA5   |     |     |      | Embedded Trace Module ETM data 3.                                                                                                                                     |

| GPIO_EM4WU0                     | PA0  |      |     |       |     |     |      | Pin can be used to wake the system up from EM4                                                                                                                        |

| GPIO_EM4WU1                     | PA6  |      |     |       |     |     |      | Pin can be used to wake the system up from EM4                                                                                                                        |

| GPIO_EM4WU3                     | PF1  |      |     |       |     |     |      | Pin can be used to wake the system up from EM4                                                                                                                        |

| GPIO_EM4WU4                     | PF2  |      |     |       |     |     |      | Pin can be used to wake the system up from EM4                                                                                                                        |

| GPIO_EM4WU5                     | PE13 |      |     |       |     |     |      | Pin can be used to wake the system up from EM4                                                                                                                        |

| HFXTAL_N                        | PB14 |      |     |       |     |     |      | High Frequency Crystal negative pin. Also used as exter-<br>nal optional clock input pin.                                                                             |

| HFXTAL_P                        | PB13 |      |     |       |     |     |      | High Frequency Crystal positive pin.                                                                                                                                  |

| I2C0_SCL                        | PA1  | PD7  | PC7 |       |     | PF1 | PE13 | I2C0 Serial Clock Line input / output.                                                                                                                                |

| I2C0_SDA                        | PA0  | PD6  | PC6 |       |     | PF0 | PE12 | I2C0 Serial Data input / output.                                                                                                                                      |

| I2C1_SCL                        | PC5  | PB12 |     |       |     |     |      | I2C1 Serial Clock Line input / output.                                                                                                                                |

| I2C1_SDA                        | PC4  | PB11 |     |       |     |     |      | I2C1 Serial Data input / output.                                                                                                                                      |

| LCD_BCAP_N                      | PA13 |      |     |       |     |     |      | LCD voltage booster (optional), boost capacitor, negative<br>pin. If using the LCD voltage booster, connect a 22 nF ca-<br>pacitor between LCD_BCAP_N and LCD_BCAP_P. |

| LCD_BCAP_P                      | PA12 |      |     |       |     |     |      | LCD voltage booster (optional), boost capacitor, positive<br>pin. If using the LCD voltage booster, connect a 22 nF ca-<br>pacitor between LCD_BCAP_N and LCD_BCAP_P. |

| LCD_BEXT                        | PA14 |      |     |       |     |     |      | LCD voltage booster (optional), boost output. If using the LCD voltage booster, connect a 1 uF capacitor between this pin and VSS.                                    |

# **EFM°32**

#### ...the world's most energy friendly microcontrollers

| Alternate     |      |      | LOC  | ATION |     |     |   |                                                                                                               |  |  |

|---------------|------|------|------|-------|-----|-----|---|---------------------------------------------------------------------------------------------------------------|--|--|

| Functionality | 0    | 1    | 2    | 3     | 4   | 5   | 6 | Description                                                                                                   |  |  |

| LES_ALTEX0    | PD6  |      |      |       |     |     |   | LESENSE alternate exite output 0.                                                                             |  |  |

| LES_ALTEX1    | PD7  |      |      |       |     |     |   | LESENSE alternate exite output 1.                                                                             |  |  |

| LES_ALTEX2    | PA3  |      |      |       |     |     |   | LESENSE alternate exite output 2.                                                                             |  |  |

| LES_ALTEX3    | PA4  |      |      |       |     |     |   | LESENSE alternate exite output 3.                                                                             |  |  |

| LES_ALTEX4    | PA5  |      |      |       |     |     |   | LESENSE alternate exite output 4.                                                                             |  |  |

| LES_ALTEX5    | PE11 |      |      |       |     |     |   | LESENSE alternate exite output 5.                                                                             |  |  |

| LES_ALTEX6    | PE12 |      |      |       |     |     |   | LESENSE alternate exite output 6.                                                                             |  |  |

| LES_ALTEX7    | PE13 |      |      |       |     |     |   | LESENSE alternate exite output 7.                                                                             |  |  |

| LES_CH4       | PC4  |      |      |       |     |     |   | LESENSE channel 4.                                                                                            |  |  |

| LES_CH5       | PC5  |      |      |       |     |     |   | LESENSE channel 5.                                                                                            |  |  |

| LES_CH6       | PC6  |      |      |       |     |     |   | LESENSE channel 6.                                                                                            |  |  |

| LES_CH7       | PC7  |      |      |       |     |     |   | LESENSE channel 7.                                                                                            |  |  |

| LETIM0_OUT0   | PD6  | PB11 | PF0  | PC4   |     |     |   | Low Energy Timer LETIM0, output channel 0.                                                                    |  |  |

| LETIM0_OUT1   | PD7  | PB12 | PF1  | PC5   |     |     |   | Low Energy Timer LETIM0, output channel 1.                                                                    |  |  |

| LEU0_RX       | PD5  | PB14 | PE15 | PF1   | PA0 |     |   | LEUARTO Receive input.                                                                                        |  |  |

| LEU0_TX       | PD4  | PB13 | PE14 | PF0   | PF2 |     |   | LEUART0 Transmit output. Also used as receive input in half duplex communication.                             |  |  |

| LEU1_RX       | PC7  | PA6  |      |       |     |     |   | LEUART1 Receive input.                                                                                        |  |  |

| LEU1_TX       | PC6  | PA5  |      |       |     |     |   | LEUART1 Transmit output. Also used as receive input in half duplex communication.                             |  |  |

| LFXTAL_N      | PB8  |      |      |       |     |     |   | Low Frequency Crystal (typically 32.768 kHz) negative pin. Also used as an optional external clock input pin. |  |  |

| LFXTAL_P      | PB7  |      |      |       |     |     |   | Low Frequency Crystal (typically 32.768 kHz) positive pin.                                                    |  |  |

| PCNT0_S0IN    |      |      |      | PD6   |     |     |   | Pulse Counter PCNT0 input number 0.                                                                           |  |  |

| PCNT0_S1IN    |      |      |      | PD7   |     |     |   | Pulse Counter PCNT0 input number 1.                                                                           |  |  |

| PCNT1_S0IN    | PC4  | PB3  |      |       |     |     |   | Pulse Counter PCNT1 input number 0.                                                                           |  |  |

| PCNT1_S1IN    | PC5  | PB4  |      |       |     |     |   | Pulse Counter PCNT1 input number 1.                                                                           |  |  |

| PCNT2_S0IN    | PD0  | PE8  |      |       |     |     |   | Pulse Counter PCNT2 input number 0.                                                                           |  |  |

| PCNT2_S1IN    | PD1  | PE9  |      |       |     |     |   | Pulse Counter PCNT2 input number 1.                                                                           |  |  |

| PRS_CH0       | PA0  |      |      |       |     |     |   | Peripheral Reflex System PRS, channel 0.                                                                      |  |  |

| PRS_CH1       | PA1  |      |      |       |     |     |   | Peripheral Reflex System PRS, channel 1.                                                                      |  |  |

| PRS_CH2       |      | PF5  |      |       |     |     |   | Peripheral Reflex System PRS, channel 2.                                                                      |  |  |

| PRS_CH3       |      | PE8  |      |       |     |     |   | Peripheral Reflex System PRS, channel 3.                                                                      |  |  |

| TIM0_CC0      | PA0  | PA0  | 1    | PD1   | PA0 | PF0 |   | Timer 0 Capture Compare input / output channel 0.                                                             |  |  |

| TIM0_CC1      | PA1  | PA1  |      | PD2   |     | PF1 |   | Timer 0 Capture Compare input / output channel 1.                                                             |  |  |

| TIM0_CC2      | PA2  | PA2  |      | PD3   |     | PF2 |   | Timer 0 Capture Compare input / output channel 2.                                                             |  |  |

| TIM0_CDTI0    | PA3  |      |      |       |     |     |   | Timer 0 Complimentary Deat Time Insertion channel 0.                                                          |  |  |

| TIM0_CDTI1    | PA4  |      |      |       |     |     |   | Timer 0 Complimentary Deat Time Insertion channel 1.                                                          |  |  |

| TIM0_CDTI2    | PA5  |      | PF5  |       | PC4 | PF5 |   | Timer 0 Complimentary Deat Time Insertion channel 2.                                                          |  |  |

| TIM1_CC0      |      | PE10 |      | PB7   | PD6 |     |   | Timer 1 Capture Compare input / output channel 0.                                                             |  |  |

| TIM1_CC1      |      | PE11 | 1    | PB8   | PD7 |     |   | Timer 1 Capture Compare input / output channel 1.                                                             |  |  |

| TIM1_CC2      |      | PE12 |      | PB11  |     |     |   | Timer 1 Capture Compare input / output channel 2.                                                             |  |  |

| TIM2_CC0      |      | PA12 |      |       |     |     |   | Timer 2 Capture Compare input / output channel 0.                                                             |  |  |

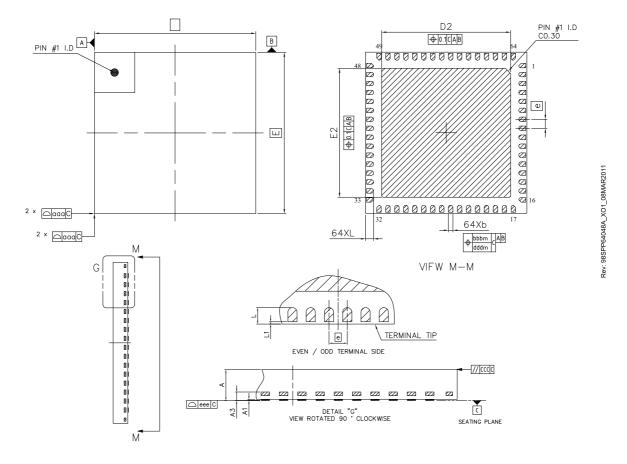

# 4.5 QFN64 Package

#### Figure 4.3. QFN64

Note:

Nom

Max

- 1. Dimensioning & tolerancing confirm to ASME Y14.5M-1994.

- 2. All dimensions are in millimeters. Angles are in degrees.

- 3. Dimension 'b' applies to metallized terminal and is measured between 0.25 mm and 0.30 mm from the terminal tip. Dimension L1 represents terminal full back from package edge up to 0.1 mm is acceptable.

- 4. Coplanarity applies to the exposed heat slug as well as the terminal.

- 5. Radius on terminal is optional

0.85

0.90

| Symbol | Α    | A1 | A3    | b    | D    | E    | D2   | E2   | e    | L    | L1   | aaa  |  |

|--------|------|----|-------|------|------|------|------|------|------|------|------|------|--|

| Min    | 0.80 |    |       | 0.20 |      |      | 7.10 |      |      |      | 0.00 |      |  |

| Nom    | 0.95 |    | 0.203 | 0.25 | 9.00 | 9.00 | 7 20 | 7 20 | 0.50 | 0.45 |      | 0 10 |  |

#### Table 4.4. QFN64 (Dimensions in mm)

0.05

The QFN64 Package uses Nickel-Palladium-Gold preplated leadframe.

BSC

All EFM32 packages are RoHS compliant and free of Bromine (Br) and Antimony (Sb).

BSC

7.20

7.30

7.20

7.30

BSC

0.45

0.50

0.10

For additional Quality and Environmental information, please see: http://www.silabs.com/support/quality/pages/default.aspx

0.25

0.30

REF

ddd

0.05

0.08

bbb

0.10

0.10

0.10

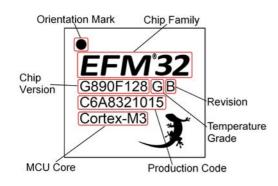

# 6 Chip Marking, Revision and Errata

# 6.1 Chip Marking

In the illustration below package fields and position are shown.

Figure 6.1. Example Chip Marking (top view)

# 6.2 Revision

The revision of a chip can be determined from the "Revision" field in Figure 6.1 (p. 64).

# 6.3 Errata

Please see the errata document for EFM32GG940 for description and resolution of device erratas. This document is available in Simplicity Studio and online at: http://www.silabs.com/support/pages/document-library.aspx?p=MCUs--32-bit

# 7.5 Revision 1.10

June 28th, 2013

Updated power requirements in the Power Management section.

Removed minimum load capacitance figure and table. Added reference to application note.

Other minor corrections.

# 7.6 Revision 1.00

September 11th, 2012

Updated the HFRCO 1 MHz band typical value to 1.2 MHz.

Updated the HFRCO 7 MHz band typical value to 6.6 MHz.

Other minor corrections.

# 7.7 Revision 0.98

May 25th, 2012

Corrected EM3 current consumption in the Electrical Characteristics section.

# 7.8 Revision 0.96

February 28th, 2012

Added reference to errata document.

Corrected QFN64 package drawing.

Updated PCB land pattern, solder mask and stencil design.

# 7.9 Revision 0.95

September 28th, 2011

Flash configuration for Giant Gecko is now 1024KB or 512KB. For flash sizes below 512KB, see the Leopard Gecko Family.

Corrected operating voltage from 1.8 V to 1.85 V.

Added rising POR level to Electrical Characteristics section.

Updated Minimum Load Capacitance (C<sub>LFXOL</sub>) Requirement For Safe Crystal Startup.

Added Gain error drift and Offset error drift to ADC table.

Added Opamp pinout overview.

Added reference to errata document.

Corrected QFN64 package drawing.

Updated PCB land pattern, solder mask and stencil design.

# A Disclaimer and Trademarks

# A.1 Disclaimer

Silicon Laboratories intends to provide customers with the latest, accurate, and in-depth documentation of all peripherals and modules available for system and software implementers using or intending to use the Silicon Laboratories products. Characterization data, available modules and peripherals, memory sizes and memory addresses refer to each specific device, and "Typical" parameters provided can and do vary in different applications. Application examples described herein are for illustrative purposes only. Silicon Laboratories reserves the right to make changes without further notice and limitation to product information, specifications, and descriptions herein, and does not give warranties as to the accuracy or completeness of the included information. Silicon Laboratories shall have no liability for the consequences of use of the information supplied herein. This document does not imply or express copyright licenses granted hereunder to design or fabricate any integrated circuits. The products must not be used within any Life Support System without the specific written consent of Silicon Laboratories. A "Life Support System" is any product or system intended to support or sustain life and/or health, which, if it fails, can be reasonably expected to result in significant personal injury or death. Silicon Laboratories products are generally not intended for military applications. Silicon Laboratories products shall under no circumstances be used in weapons of mass destruction including (but not limited to) nuclear, biological or chemical weapons, or missiles capable of delivering such weapons.

# A.2 Trademark Information

Silicon Laboratories Inc., Silicon Laboratories, Silicon Labs, SiLabs and the Silicon Labs logo, CMEMS®, EFM, EFM32, EFR, Energy Micro, Energy Micro logo and combinations thereof, "the world's most energy friendly microcontrollers", Ember®, EZLink®, EZMac®, EZRadio®, EZRadioPRO®, DSPLL®, ISO-modem®, Precision32®, ProSLIC®, SiPHY®, USBXpress® and others are trademarks or registered trademarks of Silicon Laboratories Inc. ARM, CORTEX, Cortex-M3 and THUMB are trademarks or registered trademarks of ARM Holdings. Keil is a registered trademark of ARM Limited. All other products or brand names mentioned herein are trademarks of their respective holders.

# **B** Contact Information

Silicon Laboratories Inc. 400 West Cesar Chavez Austin, TX 78701

Please visit the Silicon Labs Technical Support web page: http://www.silabs.com/support/pages/contacttechnicalsupport.aspx and register to submit a technical support request.

# List of Equations

| 3.1. Total ACMP Active Current                                      | 43 |

|---------------------------------------------------------------------|----|

| 3.2. VCMP Trigger Level as a Function of Level Setting              | 45 |

| 3.3. Total LCD Current Based on Operational Mode and Internal Boost |    |