Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                            |

|----------------------------|------------------------------------------------------------|

| Product Status             | Obsolete                                                   |

| Core Processor             | HC08                                                       |

| Core Size                  | 8-Bit                                                      |

| Speed                      | 8MHz                                                       |

| Connectivity               | I <sup>2</sup> C, IRSCI, SCI, SPI                          |

| Peripherals                | LED, LVD, POR, PWM                                         |

| Number of I/O              | 30                                                         |

| Program Memory Size        | 16KB (16K x 8)                                             |

| Program Memory Type        | FLASH                                                      |

| EEPROM Size                | -                                                          |

| RAM Size                   | 1K x 8                                                     |

| Voltage - Supply (Vcc/Vdd) | 4.5V ~ 5.5V                                                |

| Data Converters            | A/D 8x10b                                                  |

| Oscillator Type            | Internal                                                   |

| Operating Temperature      | -40°C ~ 85°C (TA)                                          |

| Mounting Type              | Through Hole                                               |

| Package / Case             | 42-SDIP (0.600", 15.24mm)                                  |

| Supplier Device Package    | 42-PDIP                                                    |

| Purchase URL               | https://www.e-xfl.com/pro/item?MUrl=&PartUrl=mc908ap16acbe |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# **Table of Contents**

Chapter 1

General Description

|                | deficial bescription                                                                              |

|----------------|---------------------------------------------------------------------------------------------------|

| 1.1            | Introduction                                                                                      |

| 1.2            | Features19                                                                                        |

| 1.3            | MCU Block Diagram 20                                                                              |

| 1.4            | Pin Assignment                                                                                    |

| 1.5            | Pin Functions                                                                                     |

| 1.6            | Power Supply Bypassing (V <sub>DD</sub> , V <sub>DDA</sub> , V <sub>SS</sub> , V <sub>SSA</sub> ) |

| 1.7            | Regulator Power Supply Configuration (VREG)                                                       |

|                | Chapter 2                                                                                         |

|                | Memory                                                                                            |

| 2.1            | Introduction 29                                                                                   |

| 2.2            | Input/Output (I/O) Section                                                                        |

| 2.3            | Monitor ROM                                                                                       |

| 2.4            | Random-Access Memory (RAM)                                                                        |

| 2.5            | FLASH Memory                                                                                      |

| 2.5.1          | Functional Description                                                                            |

| 2.5.2          | FLASH Control Register                                                                            |

| 2.5.3          | FLASH Page Erase Operation                                                                        |

| 2.5.4<br>2.5.5 | FLASH Mass Erase Operation                                                                        |

| 2.5.6          | FLASH Program Operation                                                                           |

| 2.5.7          | FLASH Block Protect Register                                                                      |

|                | Chapter 3                                                                                         |

|                | Configuration & Mask Option Registers (CONFIG & MOR)                                              |

| 3.1            | Introduction                                                                                      |

| 3.2            | Functional Description                                                                            |

| 3.3            | Configuration Register 1 (CONFIG1)                                                                |

| 3.4            | Configuration Register 2 (CONFIG2)                                                                |

| 3.5            | Mask Option Register (MOR)                                                                        |

| 0.0            |                                                                                                   |

|                | Chapter 4 Central Processor Unit (CPU)                                                            |

| 4.1            | ` ,                                                                                               |

| 4.1            | Introduction                                                                                      |

|                | Features                                                                                          |

| 4.3<br>4.3.1   | CPU Registers                                                                                     |

| 4.0.1          | Accumulator                                                                                       |

|                |                                                                                                   |

MC68HC908AP A-Family Data Sheet, Rev. 3

Freescale Semiconductor

| Table o | f Contents                         |

|---------|------------------------------------|

| 17.5    | IRQ Module During Break Interrupts |

| 17.6    | IRQ Registers                      |

|         | IRQ1 Status and Control Register   |

| 17.6.2  | IRQ2 Status and Control Register   |

. . . . . . . . 272 . . . . . . . . 272 . . . . . . . . . 272

| 17.6.2           | IRQ2 Status and Control Register              | 273 |

|------------------|-----------------------------------------------|-----|

|                  | Chapter 18<br>Keyboard Interrupt Module (KBI) |     |

| 18.1             | Introduction                                  | 275 |

| 18.2             | Features                                      | 275 |

| 18.3             | I/O Pins                                      | 275 |

| 18.4             | Functional Description                        | 276 |

| 18.4.1           | Keyboard Initialization                       | 277 |

| 18.5             | Keyboard Interrupt Registers                  |     |

| 18.5.1           | Keyboard Status and Control Register          |     |

| 18.5.2           | Keyboard Interrupt Enable Register            |     |

| 18.6             | Low-Power Modes                               |     |

| 18.6.1<br>18.6.2 | Wait Mode                                     |     |

| 18.7             | Keyboard Module During Break Interrupts.      |     |

| 10.7             | Reyboard Module During Break Interrupts       | 213 |

|                  | Chapter 19                                    |     |

|                  | Computer Operating Properly (COP)             |     |

| 19.1             | Introduction                                  | 281 |

| 19.2             | Functional Description                        | 281 |

| 19.3             | I/O Signals                                   |     |

| 19.3.1           | ICLK                                          |     |

| 19.3.2           | STOP Instruction                              |     |

| 19.3.3<br>19.3.4 | COPCTL Write                                  |     |

| 19.3.5           | Internal Reset.                               |     |

| 19.3.6           | Reset Vector Fetch                            |     |

| 19.3.7           | COPD (COP Disable)                            | 282 |

| 19.3.8           | COPRS (COP Rate Select)                       | 283 |

| 19.4             | COP Control Register                          | 283 |

| 19.5             | Interrupts                                    | 283 |

| 19.6             | Monitor Mode                                  | 283 |

| 19.7             | Low-Power Modes                               | 283 |

| 19.7.1           | Wait Mode                                     |     |

| 19.7.2           | Stop Mode                                     |     |

| 19.8             | COP Module During Break Mode                  | 284 |

|                  | Chapter 20                                    |     |

|                  | Low-Voltage Inhibit (LVI)                     |     |

| 20.1             | Introduction                                  | 285 |

| 20.2             | Features                                      | 285 |

|      | <b>3</b>               |     |

|------|------------------------|-----|

| 20.1 | Introduction           | 285 |

| 20.2 | Features               | 285 |

| 20.3 | Functional Description | 285 |

# MC68HC908AP A-Family Data Sheet, Rev. 3

## **Table of Contents**

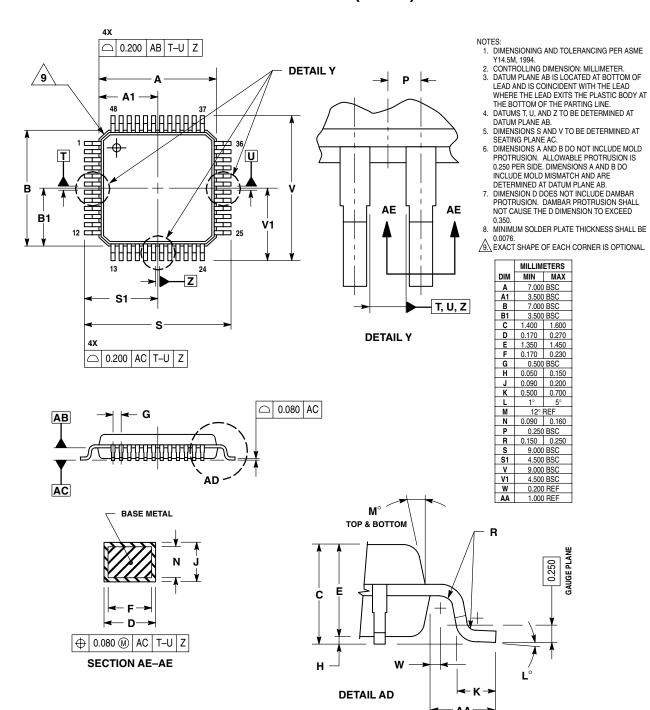

# Chapter 23 Mechanical Specifications

| 23.1 | Introduction                              | 309 |

|------|-------------------------------------------|-----|

| 23.2 | 48-Pin Low-Profile Quad Flat Pack (LQFP)  | 310 |

| 23.3 | 44-Pin Quad Flat Pack (QFP)               | 311 |

| 23.4 | 42-Pin Shrink Dual In-Line Package (SDIP) | 312 |

|      | Chapter 24                                |     |

|      | Ordering Information                      |     |

| 24.1 | Introduction                              | 313 |

| 24.2 | MC Order Numbers                          | 313 |

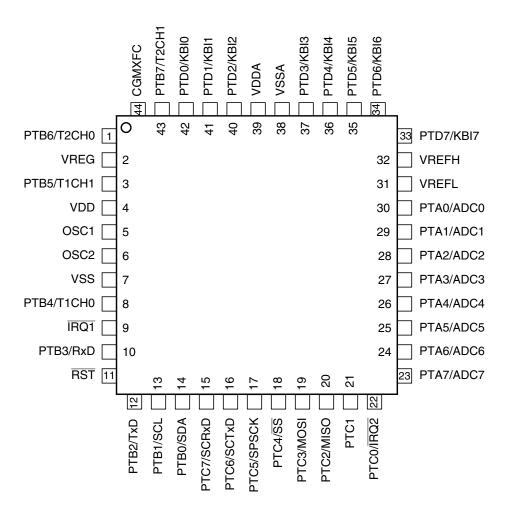

Figure 1-3. 44-Pin QFP Pin Assignments

#### SCIBDSRC — SCI Baud Rate Clock Source

SCIBDSRC selects the clock source used for the standard SCI module (non-infrared SCI). The setting of this bit affects the frequency at which the SCI operates.

- 1 = Internal data bus clock, f<sub>BUS</sub>, is used as clock source for SCI

- 0 = Oscillator clock, CGMXCLK, is used as clock source for SCI

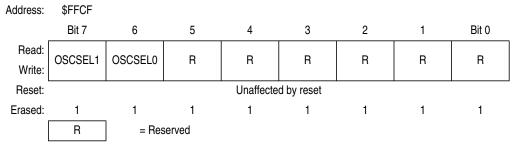

# 3.5 Mask Option Register (MOR)

The mask option register (MOR) is used for selecting one of the three clock options for the MCU. The MOR is a byte located in FLASH memory, and is written to by a FLASH programming routine.

Figure 3-4. Mask Option Register (MOR)

#### OSCSEL1, OSCSEL0 — Oscillator Selection Bits

OSCSEL1 and OSCSEL0 select which oscillator is used for the MCU CGMXCLK clock. The erase state of these two bits is logic 1. These bits are unaffected by reset. (See Table 3-1).

#### Bits 5-0 — Should be left as 1's

**Table 3-1. CGMXCLK Clock Selection**

| OSCSEL1 | OSCSEL0 | CGMXCLK | OSC2 pin Comments                                                                              |                                                                                                   |

|---------|---------|---------|------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------|

| 0       | 0       | _       | _                                                                                              | Not used                                                                                          |

| 0       | 1       | ICLK    | f <sub>BUS</sub> Internal oscillator generates the CGMXCLK                                     |                                                                                                   |

| 1       | 0       | RCCLK   | RC oscillator generates the CGMXCLiffBUS Internal oscillator is available after each or reset. |                                                                                                   |

| 1       | 1       | X-TAL   | Inverting output of XTAL                                                                       | X-tal oscillator generates the CGMXCLK. Internal oscillator is available after each POR or reset. |

#### NOTE

The internal oscillator is a free running oscillator and is available after each POR or reset. It is turned-off in stop mode by setting the STOP\_ICLKDIS bit in CONFIG2.

# Chapter 5 Oscillator (OSC)

# 5.1 Introduction

The oscillator module consist of three types of oscillator circuits:

- Internal oscillator

- RC oscillator

- 1 MHz to 8 MHz crystal (x-tal) oscillator

The reference clock for the CGM and other MCU sub-systems is selected by programming the mask option register located at \$FFCF.

The reference clock for the timebase module (TBM) is selected by the two bits, OSCCLK1 and OSCCLK0, in the CONFIG2 register.

The internal oscillator runs continuously after a POR or reset, and is always available. The RC and crystal oscillator cannot run concurrently; one is disabled while the other is selected; because the RC and x-tal circuits share the same OSC1 pin.

#### NOTE

The oscillator circuits are powered by the on-chip  $V_{REG}$  regulator, therefore, the output swing on OSC1 and OSC2 is from  $V_{SS}$  to  $V_{REG}$ .

Figure 5-1. shows the block diagram of the oscillator module.

## 5.2 Clock Selection

Reference clocks are selectable for the following sub-systems:

- CGMXCLK and CGMRCLK Reference clock for clock generator module (CGM) and other MCU sub-systems other than TBM and COP. This is the main reference clock for the MCU.

- OSCCLK Reference clock for timebase module (TBM).

# **Chapter 7 System Integration Module (SIM)**

## 7.1 Introduction

This section describes the system integration module (SIM). Together with the CPU, the SIM controls all MCU activities. A block diagram of the SIM is shown in Figure 7-1. Figure 7-2 is a summary of the SIM input/output (I/O) registers. The SIM is a system state controller that coordinates CPU and exception timing. The SIM is responsible for:

- Bus clock generation and control for CPU and peripherals:

- Stop/wait/reset/break entry and recovery

- Internal clock control

- Master reset control, including power-on reset (POR) and COP timeout

- Interrupt control:

- Acknowledge timing

- Arbitration control timing

- Vector address generation

- CPU enable/disable timing

Table 7-1 shows the internal signal names used in this section.

**Table 7-1. Signal Name Conventions**

| Signal Name      | Description                                                                             |  |

|------------------|-----------------------------------------------------------------------------------------|--|

| ICLK             | Internal oscillator clock                                                               |  |

| CGMXCLK          | Selected oscillator clock from oscillator module                                        |  |

| CGMVCLK, CGMPCLK | PLL output and the divided PLL output                                                   |  |

| CGMOUT           | CGMPCLK-based or oscillator-based clock output from CGM module (Bus clock = CGMOUT ÷ 2) |  |

| IAB              | Internal address bus                                                                    |  |

| IDB              | Internal data bus                                                                       |  |

| PORRST           | Signal from the power-on reset module to the SIM                                        |  |

| IRST             | Internal reset signal                                                                   |  |

| R/W              | Read/write signal                                                                       |  |

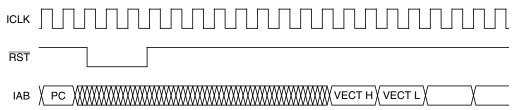

Figure 7-4. External Reset Timing

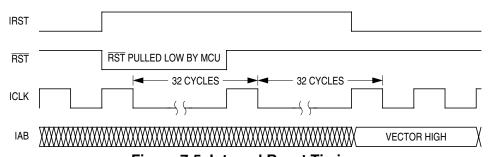

#### 7.3.2 Active Resets from Internal Sources

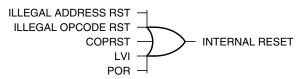

All internal reset sources actively pull the  $\overline{RST}$  pin low for 32 ICLK cycles to allow resetting of external peripherals. The internal reset signal IRST continues to be asserted for an additional 32 cycles (see Figure 7-5). An internal reset can be caused by an illegal address, illegal opcode, COP timeout, LVI, or POR (see Figure 7-6).

#### NOTE

For LVI or POR resets, the SIM cycles through 4096 + 32 ICLK cycles during which the SIM forces the  $\overline{RST}$  pin low. The internal reset signal then follows the sequence from the falling edge of  $\overline{RST}$  shown in Figure 7-5.

Figure 7-5. Internal Reset Timing

The COP reset is asynchronous to the bus clock.

Figure 7-6. Sources of Internal Reset

The active reset feature allows the part to issue a reset to peripherals and other chips within a system built around the MCU.

#### 7.3.2.1 Power-On Reset

When power is first applied to the MCU, the power-on reset module (POR) generates a pulse to indicate that power-on has occurred. The external reset pin (RST) is held low while the SIM counter counts out 4096 + 32 ICLK cycles. Thirty-two ICLK cycles later, the CPU and memories are released from reset to allow the reset vector sequence to occur.

# **Chapter 8 Monitor Mode (MON)**

#### 8.1 Introduction

The monitor module allows debugging and programming of the microcontroller unit (MCU) through a single-wire interface with a host computer. Monitor mode entry can be achieved without use of the higher test voltage, V<sub>TST</sub>, as long as vector addresses \$FFFE and \$FFFF are blank, thus reducing the hardware requirements for in-circuit programming.

#### 8.2 Features

Features of the monitor ROM include:

- Normal user-mode pin functionality

- One pin dedicated to serial communication between monitor ROM and host computer

- Standard mark/space non-return-to-zero (NRZ) communication with host computer

- · Execution of code in RAM or FLASH

- FLASH memory security feature<sup>(1)</sup>

- 959 bytes monitor ROM code size (\$FC00-\$FDFF and \$FE10-\$FFCE)

- Monitor mode entry without high voltage, V<sub>TST</sub>, if reset vector is blank (\$FFFE and \$FFFF contain \$FF)

- Standard monitor mode entry if high voltage, V<sub>TST</sub>, is applied to IRQ1

- Resident routines for in-circuit programming

# 8.3 Functional Description

The monitor module receives and executes commands from a host computer. Figure 8-1 shows an example circuit used to enter monitor mode and communicate with a host computer via a standard RS-232 interface.

Simple monitor commands can access any memory address. In monitor mode, the MCU can execute code downloaded into RAM by a host computer while most MCU pins retain normal operating mode functions. All communication between the host computer and the MCU is through the PTA0 pin. A level-shifting and multiplexing interface is required between PTA0 and the host computer. PTA0 is used in a wired-OR configuration and requires a pullup resistor.

MC68HC908AP A-Family Data Sheet, Rev. 3

<sup>1.</sup> No security feature is absolutely secure. However, Freescale's strategy is to make reading or copying the FLASH difficult for unauthorized users.

**Monitor Mode (MON)**

## 8.5 ROM-Resident Routines

Seven routines stored in the monitor ROM area (thus ROM-resident) are provided for FLASH memory manipulation. Five of the seven routines are intended to simplify FLASH program, erase, and load operations. The other two routines are intended to simplify the use of the FLASH memory as EEPROM. Table 8-10 shows a summary of the ROM-resident routines.

| Routine Name | Routine Description                                      | Call Address | Stack Used (bytes) |

|--------------|----------------------------------------------------------|--------------|--------------------|

| PRGRNGE      | PRGRNGE Program a range of locations                     |              | 15                 |

| ERARNGE      | \$FCE4                                                   | 9            |                    |

| LDRNGE       | Loads data from a range of locations                     | \$FC00       | 7                  |

| MON_PRGRNGE  | MON_PRGRNGE Program a range of locations in monitor mode |              | 17                 |

| MON_ERARNGE  | Erase a page or the entire array in monitor mode         | \$FF28       | 11                 |

Table 8-10. Summary of ROM-Resident Routines

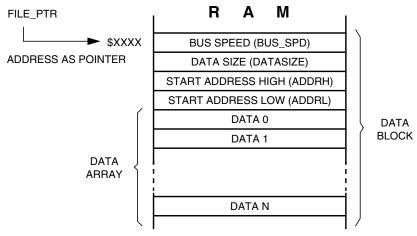

The routines are designed to be called as stand-alone subroutines in the user program or monitor mode. The parameters that are passed to a routine are in the form of a contiguous data block, stored in RAM. The index register (H:X) is loaded with the address of the first byte of the data block (acting as a pointer), and the subroutine is called (JSR). Using the start address as a pointer, multiple data blocks can be used, any area of RAM be used. A data block has the control and data bytes in a defined order, as shown in Figure 8-9.

During the software execution, it does not consume any dedicated RAM location, the run-time heap will extend the system stack, all other RAM location will not be affected.

Figure 8-9. Data Block Format for ROM-Resident Routines

The control and data bytes are described below.

#### **Monitor Mode (MON)**

|         |         | ORG        | RAM           |    |                            |

|---------|---------|------------|---------------|----|----------------------------|

|         | :       |            |               |    |                            |

| FILE_P  | TR:     |            |               |    |                            |

| BUS_SP  | D       | DS.B       | 1             | ;  | Indicates 4x bus frequency |

| DATASI  | ZE      | DS.B       | 1             |    | Data size to be programmed |

| START_  | ADDR    | DS.W       | 1             | ;  | FLASH start address        |

| DATAAR  | RAY     | DS.B       | 64            | ;  | Reserved data array        |

| PRGRNG: | E       | EQU        | \$FC34        |    |                            |

| FLASH_  | START   | EQU        | \$EE00        |    |                            |

|         |         | ORG        | FLASH         |    |                            |

| INITIA  | LISATIO | V:         |               |    |                            |

|         | MOV     | #20,       | BUS SI        | PD |                            |

|         | MOV     |            |               |    | F.                         |

|         | LDHX    |            |               |    | _                          |

|         | STHX    |            |               |    |                            |

|         | RTS     | D1711(1711 | JDIC          |    |                            |

| MAIN:   | KID     |            |               |    |                            |

| LIVIII. | BSR     | INITIAL    | r c z m t O z | т  |                            |

|         |         | TNTITAL    | LSATION       | ı  |                            |

|         | :       |            |               |    |                            |

|         | :       |            |               |    |                            |

|         | LDHX    | #FILE_P    | ľR            |    |                            |

|         | JSR     | PRGRNGE    |               |    |                            |

#### 8.5.2 ERARNGE

ERARNGE is used to erase a range of locations in FLASH.

**Table 8-12. ERARNGE Routine**

| Routine Name        | ERARNGE                                                                                    |  |

|---------------------|--------------------------------------------------------------------------------------------|--|

| Routine Description | Erase a page or the entire array                                                           |  |

| Calling Address     | \$FCE4                                                                                     |  |

| Stack Used          | 9 bytes                                                                                    |  |

| Data Block Format   | Bus speed (BUS_SPD) Data size (DATASIZE) Starting address (ADDRH) Starting address (ADDRL) |  |

There are two sizes of erase ranges: a page or the entire array. The ERARNGE will erase the page (512 consecutive bytes) in FLASH specified by the address ADDRH:ADDRL. This address can be any address within the page. Calling ERARNGE with ADDRH:ADDRL equal to \$FFFF will erase the entire FLASH array (mass erase). Therefore, care must be taken when calling this routine to prevent an accidental mass erase.

The ERARNGE routine do not use a data array. The DATASIZE byte is a dummy byte that is also not used.

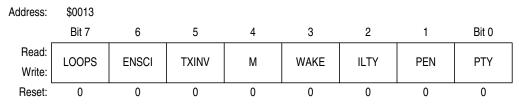

# 11.8.1 SCI Control Register 1

SCI control register 1:

- Enables loop mode operation

- Enables the SCI

- Controls output polarity

- · Controls character length

- · Controls SCI wakeup method

- Controls idle character detection

- Enables parity function

- · Controls parity type

Figure 11-9. SCI Control Register 1 (SCC1)

#### LOOPS — Loop Mode Select Bit

This read/write bit enables loop mode operation. In loop mode the RxD pin is disconnected from the SCI, and the transmitter output goes into the receiver input. Both the transmitter and the receiver must be enabled to use loop mode. Reset clears the LOOPS bit.

- 1 = Loop mode enabled

- 0 = Normal operation enabled

#### **ENSCI** — Enable SCI Bit

This read/write bit enables the SCI and the SCI baud rate generator. Clearing ENSCI sets the SCTE and TC bits in SCI status register 1 and disables transmitter interrupts. Reset clears the ENSCI bit.

- 1 = SCI enabled

- 0 = SCI disabled

#### TXINV — Transmit Inversion Bit

This read/write bit reverses the polarity of transmitted data. Reset clears the TXINV bit.

- 1 = Transmitter output inverted

- 0 = Transmitter output not inverted

#### NOTE

Setting the TXINV bit inverts all transmitted values, including idle, break, start, and stop bits.

# M — Mode (Character Length) Bit

This read/write bit determines whether SCI characters are eight or nine bits long. (See Table 11-5.) The ninth bit can serve as an extra stop bit, as a receiver wakeup signal, or as a parity bit. Reset clears the M bit.

- 1 = 9-bit SCI characters

- 0 = 8-bit SCI characters

| RT8, RT9, and RT10<br>Samples | Framing<br>Error Flag | Noise Flag |

|-------------------------------|-----------------------|------------|

| 010                           | 1                     | 1          |

| 011                           | 0                     | 1          |

| 100                           | 1                     | 1          |

| 101                           | 0                     | 1          |

| 110                           | 0                     | 1          |

| 111                           | 0                     | 0          |

**Table 12-4. Stop Bit Recovery**

# 12.5.3.4 Framing Errors

If the data recovery logic does not detect a logic 1 where the stop bit should be in an incoming character, it sets the framing error bit, FE, in IRSCS1. The FE flag is set at the same time that the SCRF bit is set. A break character that has no stop bit also sets the FE bit.

#### 12.5.3.5 Baud Rate Tolerance

A transmitting device may be operating at a baud rate below or above the receiver baud rate. Accumulated bit time misalignment can cause one of the three stop bit data samples to fall outside the actual stop bit. Then a noise error occurs. If more than one of the samples is outside the stop bit, a framing error occurs. In most applications, the baud rate tolerance is much more than the degree of misalignment that is likely to occur.

As the receiver samples an incoming character, it resynchronizes the RT clock on any valid falling edge within the character. Resynchronization within characters corrects misalignments between transmitter bit times and receiver bit times.

## **Slow Data Tolerance**

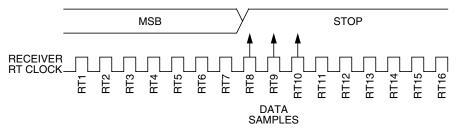

Figure 12-10 shows how much a slow received character can be misaligned without causing a noise error or a framing error. The slow stop bit begins at RT8 instead of RT1 but arrives in time for the stop bit data samples at RT8, RT9, and RT10.

Figure 12-10. Slow Data

For an 8-bit character, data sampling of the stop bit takes the receiver 9 bit times  $\times$  16 RT cycles + 10 RT cycles = 154 RT cycles.

With the misaligned character shown in Figure 12-10, the receiver counts 154 RT cycles at the point when the count of the transmitting device is 9 bit times  $\times$  16 RT cycles + 3 RT cycles = 147 RT cycles.

MC68HC908AP A-Family Data Sheet, Rev. 3

**Serial Peripheral Interface Module (SPI)**

# 13.12.5 CGND (Clock Ground)

CGND is the ground return for the serial clock pin, SPSCK, and the ground for the port output buffers. It is internally connected to  $V_{SS}$  as shown in Table 13-1.

# 13.13 I/O Registers

Three registers control and monitor SPI operation:

- SPI control register (SPCR)

- SPI status and control register (SPSCR)

- SPI data register (SPDR)

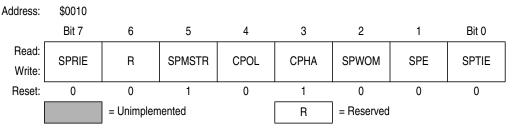

# 13.13.1 SPI Control Register

The SPI control register:

- Enables SPI module interrupt requests

- Configures the SPI module as master or slave

- Selects serial clock polarity and phase

- Configures the SPSCK, MOSI, and MISO pins as open-drain outputs

- Enables the SPI module

Figure 13-13. SPI Control Register (SPCR)

#### SPRIE — SPI Receiver Interrupt Enable Bit

This read/write bit enables CPU interrupt requests generated by the SPRF bit. The SPRF bit is set when a byte transfers from the shift register to the receive data register. Reset clears the SPRIE bit.

- 1 = SPRF CPU interrupt requests enabled

- 0 = SPRF CPU interrupt requests disabled

#### SPMSTR — SPI Master Bit

This read/write bit selects master mode operation or slave mode operation. Reset sets the SPMSTR bit.

- 1 = Master mode

- 0 = Slave mode

# **CPOL** — Clock Polarity Bit

This read/write bit determines the logic state of the SPSCK pin between transmissions. (See Figure 13-4 and Figure 13-6.) To transmit data between SPI modules, the SPI modules must have identical CPOL values. Reset clears the CPOL bit.

#### **CPHA** — Clock Phase Bit

# 15.7 I/O Registers

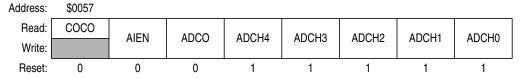

These I/O registers control and monitor ADC operation:

- ADC status and control register (ADSCR) \$0057

- ADC clock control register (ADICLK) \$0058

- ADC data register high:low 0 (ADRH0:ADRL0) \$0059:\$005A

- ADC data register low 1–3 (ADRL1–ADRL3) \$005B–\$005D

- ADC auto-scan control register (ADASCR) \$005E

# 15.7.1 ADC Status and Control Register

Function of the ADC status and control register is described here.

Figure 15-3. ADC Status and Control Register (ADSCR)

### **COCO** — Conversions Complete Bit

In non-interrupt mode (AIEN = 0), COCO is a read-only bit that is set at the end of each conversion. COCO will stay set until cleared by a read of the ADC data register. Reset clears this bit.

In interrupt mode (AIEN = 1), COCO is a read-only bit that is not set at the end of a conversion. It always reads as a 0.

- 1 = Conversion completed (AIEN = 0)

- 0 = Conversion not completed (AIEN = 0) or CPU interrupt enabled (AIEN = 1)

#### NOTE

The write function of the COCO bit is reserved. When writing to the ADSCR register, always have a 0 in the COCO bit position.

#### **AIEN** — **ADC** Interrupt Enable Bit

When this bit is set, an interrupt is generated at the end of an ADC conversion. The interrupt signal is cleared when the data register, ADR0, is read or the ADSCR is written. Reset clears the AIEN bit.

- 1 = ADC interrupt enabled

- 0 = ADC interrupt disabled

## ADCO — ADC Continuous Conversion Bit

When set, the ADC will convert samples continuously and update the ADC data register at the end of each conversion. Only one conversion is allowed when this bit is cleared. Reset clears the ADCO bit.

- 1 = Continuous ADC conversion

- 0 = One ADC conversion

This bit should not be set when auto-scan mode is enabled; i.e. when ASCAN=1.

### ADCH[4:0] — ADC Channel Select Bits

ADCH[4:0] form a 5-bit field which is used to select one of the ADC channels when not in auto-scan mode. The five channel select bits are detailed in Table 15-1.

#### NOTE

Care should be taken when using a port pin as both an analog and a digital input simultaneously to prevent switching noise from corrupting the analog

MC68HC908AP A-Family Data Sheet, Rev. 3

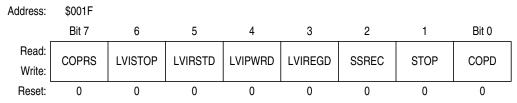

# 19.3.8 COPRS (COP Rate Select)

The COPRS signal reflects the state of the COP rate select bit (COPRS) in the CONFIG1 register.

Figure 19-2. Configuration Register 1 (CONFIG1)

#### COPRS — COP Rate Select Bit

COPRS selects the COP time out period. Reset clears COPRS.

- 1 = COP time out period =  $2^{13} 2^4$  ICLK cycles 0 = COP time out period =  $2^{18} 2^4$  ICLK cycles

#### COPD — COP Disable Bit

COPD disables the COP module.

- 1 = COP module disabled

- 0 = COP module enabled

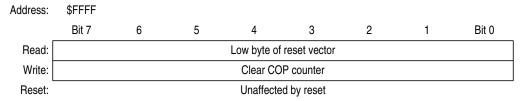

# 19.4 COP Control Register

The COP control register is located at address \$FFFF and overlaps the reset vector. Writing any value to \$FFFF clears the COP counter and starts a new timeout period. Reading location \$FFFF returns the low byte of the reset vector.

Figure 19-3. COP Control Register (COPCTL)

# 19.5 Interrupts

The COP does not generate CPU interrupt requests.

## 19.6 Monitor Mode

When monitor mode is entered with V<sub>TST</sub> on the IRQ1 pin, the COP is disabled as long as V<sub>TST</sub> remains on the IRQ1 pin or the RST pin. When monitor mode is entered by having blank reset vectors and not having  $V_{TST}$  on the  $\overline{IRQ1}$  pin, the COP is automatically disabled until a POR occurs.

# 19.7 Low-Power Modes

The WAIT and STOP instructions put the MCU in low power-consumption standby modes.

MC68HC908AP A-Family Data Sheet, Rev. 3

# 22.7 5V Oscillator Characteristics

Table 22-6. Oscillator Specifications (5V)

| Characteristic <sup>(1)</sup>                   | Symbol               | Min             | Тур                 | Max  | Unit |

|-------------------------------------------------|----------------------|-----------------|---------------------|------|------|

| Internal oscillator clock frequency             | f <sub>ICLK</sub>    | 64k             | 88 k <sup>(2)</sup> | 104k | Hz   |

| External reference clock to OSC1 <sup>(3)</sup> | f <sub>OSC</sub>     | dc              |                     | 32M  | Hz   |

| Crystal reference frequency <sup>(4)</sup>      | f <sub>XTALCLK</sub> | 1 M             | _                   | 8M   | Hz   |

| Crystal load capacitance <sup>(5)</sup>         | C <sub>L</sub>       | _               | _                   | _    |      |

| Crystal fixed capacitance <sup>(5)</sup>        | C <sub>1</sub>       | _               | $2 \times C_L$      | _    |      |

| Crystal tuning capacitance <sup>(5)</sup>       | C <sub>2</sub>       | _               | $2 \times C_L$      | _    |      |

| Feedback bias resistor                          | R <sub>B</sub>       | _               | 1 M                 | _    | Ω    |

| Series resistor <sup>(5)</sup>                  | R <sub>S</sub>       | _               | 0                   | _    | Ω    |

| External RC clock frequency                     | f <sub>RCCLK</sub>   |                 |                     | 7.6M | Hz   |

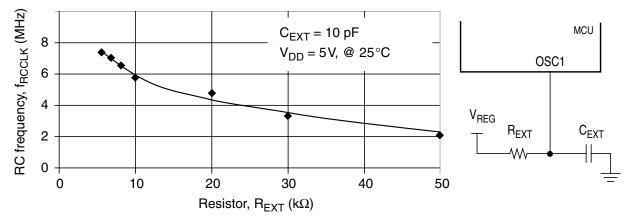

| RC oscillator external R                        | R <sub>EXT</sub>     | See Figure 22-1 |                     |      | Ω    |

| RC oscillator external C                        | C <sub>EXT</sub>     | _               | 10                  | _    | pF   |

- 1. The oscillator circuit operates at  $V_{REG}$ . 2. Typical value reflect average measurements at midpoint of voltage range, 25 °C only.

- 3. No more than 10% duty cycle deviation from 50%. The max. frequency is limited by an EMC filter.

- 4. Fundamental mode crystals only.

- 5. Consult crystal vendor data sheet.

Figure 22-1. RC vs. Frequency

## **Electrical Specifications**

# 22.8 5V ADC Electrical Characteristics

Table 22-7. ADC Electrical Characteristics (5 V)

| Characteristic <sup>(1)</sup>        | Symbol            | Min                    | Max                    | Unit                     | Notes                                                                                           |  |

|--------------------------------------|-------------------|------------------------|------------------------|--------------------------|-------------------------------------------------------------------------------------------------|--|

| Supply voltage                       | V <sub>DDA</sub>  | 4.5                    | 5.5                    | V                        | $V_{DDA}$ is an dedicated pin and should be tied to $V_{DD}$ on the PCB with proper decoupling. |  |

| Input range                          | V <sub>ADIN</sub> | 0                      | V <sub>DDA</sub>       | V                        | $V_{ADIN} \le V_{DDA}$                                                                          |  |

| Resolution                           | B <sub>AD</sub>   | 10                     | 10                     | bits                     |                                                                                                 |  |

| Absolute accuracy                    | A <sub>AD</sub>   | _                      | ± 1.5                  | LSB                      | Includes quantization.<br>±0.5 LSB = ±1 ADC step.                                               |  |

| ADC internal clock                   | f <sub>ADIC</sub> | 500k                   | 1.048M                 | Hz                       | $t_{ADIC} = 1/f_{ADIC}$                                                                         |  |

| Conversion range                     | R <sub>AD</sub>   | V <sub>REFL</sub>      | V <sub>REFH</sub>      | V                        |                                                                                                 |  |

| ADC voltage reference high           | V <sub>REFH</sub> | _                      | V <sub>DDA</sub> + 0.1 | V                        |                                                                                                 |  |

| ADC voltage reference low            | V <sub>REFL</sub> | V <sub>SSA</sub> – 0.1 | _                      | V                        |                                                                                                 |  |

| Conversion time                      | t <sub>ADC</sub>  | 16                     | 17                     | t <sub>ADIC</sub> cycles |                                                                                                 |  |

| Sample time                          | t <sub>ADS</sub>  | 5                      | _                      | t <sub>ADIC</sub> cycles |                                                                                                 |  |

| Monotonicity                         | M <sub>AD</sub>   | Guaranteed             |                        |                          |                                                                                                 |  |

| Zero input reading                   | Z <sub>ADI</sub>  | 000                    | 001                    | HEX                      | $V_{ADIN} = V_{REFL}$                                                                           |  |

| Full-scale reading                   | F <sub>ADI</sub>  | 3FD                    | 3FF                    | HEX                      | $V_{ADIN} = V_{REFH}$                                                                           |  |

| Input capacitance                    | C <sub>ADI</sub>  | _                      | 20                     | pF                       | Not tested.                                                                                     |  |

| Input impedance                      | R <sub>ADI</sub>  | 20M                    | _                      | Ω                        |                                                                                                 |  |

| V <sub>REFH</sub> /V <sub>REFL</sub> | I <sub>VREF</sub> | _                      | 1.6                    | mA                       | Not tested.                                                                                     |  |

<sup>1.</sup>  $V_{DD}$  = 4.5 to 5.5 Vdc,  $V_{SS}$  = 0 Vdc,  $T_A$  =  $T_L$  to  $T_H$ , unless otherwise noted.

MC68HC908AP A-Family Data Sheet, Rev. 3

# 22.12 Memory Characteristics

**Table 22-12. Memory Characteristics**

| Characteristic                       | Symbol                           | Min. | Max.  | Unit   |

|--------------------------------------|----------------------------------|------|-------|--------|

| Data retention voltage               | V <sub>RDR</sub>                 | 1.3  | _     | V      |

| Number of rows per page              |                                  | 8    |       | Rows   |

| Number of bytes per page             |                                  | 5    | Bytes |        |

| Read bus clock frequency             | f <sub>read</sub> <sup>(1)</sup> | 32k  | 8M    | Hz     |

| Page erase time                      | t <sub>erase</sub> (2)           | 20   | _     | ms     |

| Mass erase time                      | t <sub>me</sub> <sup>(3)</sup>   | 200  | _     | ms     |

| PGM/ERASE to HVEN setup time         | t <sub>nvs</sub>                 | 5    | _     | μs     |

| High-voltage hold time               | t <sub>nvh</sub>                 | 5    | _     | μs     |

| High-voltage hold time (mass erase)  | t <sub>nvh1</sub>                | 100  | _     | μs     |

| Program hold time                    | t <sub>pgs</sub>                 | 10   | _     | μs     |

| Program time                         | t <sub>prog</sub>                | 20   | 40    | μs     |

| Address/data setup time              | t <sub>ads</sub>                 | 20   | _     | ns     |

| Address/data hold time               | t <sub>adh</sub>                 | _    | 30    | ns     |

| Recovery time                        | t <sub>rcv</sub> <sup>(4)</sup>  | 1    | _     | μs     |

| Cumulative HV period                 | t <sub>hv</sub> <sup>(5)</sup>   | _    | 8     | ms     |

| Row erase endurance <sup>(6)</sup>   | _                                | 10k  | _     | Cycles |

| Row program endurance <sup>(7)</sup> | _                                | 10k  | _     | Cycles |

| Data retention time <sup>(8)</sup>   | _                                | 10   | _     | Years  |

- 1.  $f_{\text{read}}$  is defined as the frequency range for which the FLASH memory can be read.

- 2. If the page erase time is longer than t<sub>erase</sub> (Min.), there is no erase-disturb, but it reduces the endurance of the FLASH memory.

- 3. If the mass erase time is longer than t<sub>me</sub> (Min.), there is no erase-disturb, but it reduces the endurance of the FLASH memory.

- 4. It is defined as the time it needs before the FLASH can be read after turning off the high voltage charge pump, by clearing HVEN to logic 0.

- 5. t<sub>hv</sub> is the cumulative high voltage programming time to the same row before next erase, and the same address can not be programmed twice before next erase.

- 6. The minimum row endurance value specifies each row of the FLASH memory is guaranteed to work for at least this many erase/program cycles.

- 7. The minimum row endurance value specifies each row of the FLASH memory is guaranteed to work for at least this many erase/program cycle.

- 8. The FLASH is guaranteed to retain data over the entire operating temperature range for at least the minimum time specified.

#### **Mechanical Specifications**

# 23.2 48-Pin Low-Profile Quad Flat Pack (LQFP)

Figure 23-1. 48-Pin LQFP (Case #932)