#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Obsolete                                                               |

|----------------------------|------------------------------------------------------------------------|

| Core Processor             | M68HC08                                                                |

| Core Size                  | 8-Bit                                                                  |

| Speed                      | 8MHz                                                                   |

| Connectivity               | I²C, SCI, SPI                                                          |

| Peripherals                | LED, LVD, POR, PWM                                                     |

| Number of I/O              | 31                                                                     |

| Program Memory Size        | 16KB (16K x 8)                                                         |

| Program Memory Type        | FLASH                                                                  |

| EEPROM Size                | -                                                                      |

| RAM Size                   | 1K x 8                                                                 |

| Voltage - Supply (Vcc/Vdd) | 4.5V ~ 5.5V                                                            |

| Data Converters            | A/D 8x10b SAR                                                          |

| Oscillator Type            | External, Internal                                                     |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                      |

| Mounting Type              | Surface Mount                                                          |

| Package / Case             | 48-LQFP                                                                |

| Supplier Device Package    | 48-LQFP (7x7)                                                          |

| Purchase URL               | https://www.e-xfl.com/product-detail/nxp-semiconductors/mc908ap16acfae |

|                            |                                                                        |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### Memory

| S0000         Unimplemented         Write:<br>Reset:         Reset:         Image: Reset:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | Addr.                | Register Name                     |   | Bit 7 | 6     | 5      | 4         | 3          | 2      | 1    | Bit 0 |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------|-----------------------------------|---|-------|-------|--------|-----------|------------|--------|------|-------|

| S000E         Unimplemented         Rest:<br>Rest:<br>Rest:         Image: Rest:<br>Rest:<br>Rest:<br>Rest:<br>S000         Image: Rest:<br>Rest:<br>Rest:<br>S000         Image: Rest:<br>Rest:<br>S000         Image: Rest:<br>Rest:<br>S000         SPI Control Register<br>(SPCR)<br>Rest:<br>SPI Status and Control<br>Register<br>(SPCR)<br>Rest:<br>S0010         SPI Control Register<br>Rest:<br>SPI Status and Control<br>Register<br>(SPCR)<br>Rest:<br>SPI Data Register<br>(SPCR)<br>Rest:<br>S0010         SPI Status and Control<br>Register<br>(SPCR)<br>Rest:<br>SPI Data Register<br>(SCCR)<br>Rest:<br>SCI Control Register<br>(SCCR)         Rest:<br>Rest:<br>SO 0         O         O         Image: Rest:<br>SPI RE<br>Rest:<br>SPI RE<br>Rest:<br>SCI Control Register<br>(SCCR)         SPI RE<br>Rest:<br>SCI Control Register<br>(SCCR)         SPI RE<br>Rest:<br>SCI Control Register<br>(SCCR)         SPI RE<br>Rest:<br>SCI Control Register<br>(SCCR)         SCI Control Register<br>(SCCR)         Rest:<br>Rest:<br>SCI Control Register<br>(SCCR)         COL<br>Rest:<br>Rest:<br>SCI Control Register<br>(SCCR)         Rest:<br>Rest:<br>SCI Control Register<br>(SCCR)         Rest:<br>Rest:<br>SCI Control Register<br>(SCCR)         Rest:<br>Rest:<br>Rest:<br>SCI Control Register<br>(SCCR)         Rest:<br>Rest:<br>Rest:<br>SCTE         DMARE<br>SCI Control Register<br>(SCCR)         NEIE         FEIE         PIEE           S0010         SCI Control Register<br>(SCCR)         Read:<br>Rest:<br>Rest:<br>SCI Control Register<br>(SCCR)         Read:<br>Rest:<br>Rest:<br>SCTE         SCI Control Register<br>(SCCR)         Read:<br>Rest:<br>SCTE         SCI Control Register<br>(SCCR)         Read:<br>Rest:<br>SCTE         SCI Control Register<br>(SCCR)         Read:<br>Rest:<br>SCTE         SCI Control Register<br>(SCCR)         Read:<br>Rest:<br>SCTE         SCI Control Register<br>(SCCR)         Read:<br>Rest:<br>SCTE |                      |                                   |   |       |       |        |           |            |        |      |       |

| S000E         Unimplemented         Read:<br>Reset         Image: reset                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | \$000D Unimplemented |                                   |   |       |       |        |           |            |        |      |       |

| \$000E         Unimplemented         Write<br>Read:         SPI Control Register<br>(SPCR)         SPI Control Register<br>(SPCR)         SPI E         SPIE         R         SPMSTR         CPOL         CPHA         SPWOM         SPE         SPTIE           \$0010         SPI Control Register<br>(SPCR)         Write:         0         0         1         0         0         0           \$0011         SPI Status and Control<br>(SPCR)         Read:         SPRF         ERRIE         0/VFF         MODF         SPTE         MODFEN         SPR1         SPR0           \$0011         SPI Status and Control<br>(SPCR)         Read:         SPRF         ERRIE         0/VFF         MODF         SPTE         MODFEN         SPR1         SPR0           \$0012         SPI Data Register<br>(SPCR)         Read:         RT         R6         R5         R4         R3         R2         R1         R0           \$0013         SCI Control Register 1<br>(SCCI         Read:         R7         R6         R5         R4         R3         R2         R1         R0           \$0014         SCI Control Register 1<br>(SCCI         Read:         RC         0         0         0         0         0         0         0         0         0         0<                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                      |                                   |   |       |       |        |           |            |        |      |       |

| S000F         Unimplemental         Reset:<br>Reset:<br>(SPCR)         SPI Control Register<br>Write:<br>(SPCR)         SPRIE         R         SPMSTR         CPOL         CPHA         SPWOM         SPE         SPTIE           S0010         SPI Control Register<br>(SPCR)         Reset:         0         0         1         0         1         0         0         0           S0011         SPI Status and Control<br>(SPCR)         Reset:         0         0         1         0         1         0         0         0         0           S0011         SPI Status and Control<br>(SPCR)         Reset:         0         0         0         1         0         0         0           S0012         SPI Data Register<br>(SPCR)         Reset:         0         0         0         1         0         0         0           S0013         SCI Control Register 1<br>(SCC1)         Write:         LOOPS         ENSCI         TXINV         M         WAKE         ILITY         PEN         PTY           Read:<br>(SCC1)         SCI Control Register 2<br>(SCC1)         Read:<br>(SCC2)         SCIE         TCI         SCRIE         ILIE         TE         RE         RWU         SBK           S0014         SCI Control Register 3<br>(SCC3)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                      |                                   |   |       |       |        |           |            |        |      |       |

| S000F         Unimplemented         Read:<br>Write:<br>(SPCR)         Image:<br>Write:<br>(SPCR)         SPI control Register<br>Write:<br>Reset:         SPIIE         R         SPMSTR         CPOL         CPHA         SPWOM         SPE         SPTIE           \$0010         SPI Control Register<br>(SPCR)         Read:<br>Register         SPIIE         R         SPMSTR         CPOL         CPHA         SPWOM         SPE         SPTIE           \$0011         SPI Status and Control<br>Register         Read:<br>(SPCR)         SPIF         ERRIE         O         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | \$000E               | •                                 |   |       |       |        |           |            |        |      |       |

| S000F         Unimplemented         Write:         Image: control Register (SPCR)         Read: (SPCR)         Read: (SPCR)         Read: (SPCR)         Read: (SPCR)         Read: (SPCR)         Read: (SPCR)         SPRIE         Image: Control Register (SPCR)         SPRIE         O         O         1         O         0         0         0           S0010         SPI Status and Control Register (SPCR)         Read:         SPRIE         OVRF         MODF         SPTE         MODFEN         SPRI         SPRI         SPRI           S0011         SPI Status and Control Register (SPCR)         Read:         T7         T6         T5         T4         T3         T2         T1         T0           S0012         SPI Data Register (SCC)         Write:         T7         T6         T5         T4         T3         T2         T1         T0           R0013         SCI Control Register (SCC)         Write:         LOOPS         ENSCI         TXINV         M         WAKE         ILITY         PEN         PTY           R0013         SCI Control Register (SCC)         Read:         SCTE         TC         SCRIE         ILIE         TE         RE         RWU         SBK           R0014         SCI Control Register (SCC)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                      |                                   |   |       |       |        |           |            |        |      |       |

| Soliton         SPI Control Register<br>(SPCR)         Readt<br>Write:         SPRIE         R         SPMSTR         CPOL         CPHA         SPWOM         SPE         SPTIE           S0010         SPI Control Register<br>(SPCR)         Reset:         0         0         1         0         0         0           S0111         Register<br>(SPSCR)         Write:         SPRIE         ERRIE         OVRF         MODF         SPTIE         MODFEN         SPRI         SPRID           S0011         CSPSCR)         Reset:         0         0         0         1         0         0         0           S0012         SPI Data Register<br>(SPDR)         Reset:         0         0         0         1         0         0         0           S0013         SCI Control Register 1<br>(SCC2)         Read:<br>(SCC2)         TXINV         M         WAKE         ILTY         PEN         PTY           Read:<br>(SCC2)         Read:<br>(SCC2)         SCTIE         TCIE         SCRIE         ILLE         TE         RE         RWU         SBK           S0014         SCI Control Register 2<br>(SCC3)         Read:<br>(SCC2)         SCTIE         TCIE         SCRIE         ILLE         TE         RE         RWU         SBK <td><b>-</b></td> <td></td>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | <b>-</b>             |                                   |   |       |       |        |           |            |        |      |       |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | \$000F               | Unimplemented                     |   |       |       |        |           |            |        |      |       |

| S0010         SPI Control Register<br>(SPCR)         Write:<br>Reset:         SPRIE         R         SPMSTR         CPOL         CPHA         SPWOM         SPE         SPTIE           S0011         SPI Status and Control<br>Register         Read:<br>(SPSCR)         SPRF         ERRIE         OVRF         MODF         SPTE         MODFEN         SPRI         SPRO           S0012         SPI Data Register<br>(SPCR)         Reset:         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                      |                                   |   |       |       | 1      |           |            | 1      |      |       |

| Sourio         (SPCR)         Write:<br>Reset:         0         0         1         0         1         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | <b>\$0010</b>        | SPI Control Register              |   | SPRIE | R     | SPMSTR | CPOL      | CPHA       | SPWOM  | SPE  | SPTIE |

| SPI Status and Control<br>Register<br>(SPSC)         Read:<br>Register<br>(SPSC)         SPRF<br>Reset:         ERRIE         OVRF         MODF         SPTE         MODFEN         SPR1         SPR0           S0012         SPI Data Register<br>(SPDC)         Read:         R7         R6         R5         R4         R3         R2         R1         R0           S0012         SPI Data Register<br>(SPDR)         Write:         T7         T6         T5         T4         T3         T2         T1         T0           S0013         SCI Control Register<br>(SCC1)         Mrite:         LOOPS         ENSCI         TXINV         M         WAKE         ILTY         PEN         PTY           S0013         SCI Control Register 2<br>(SCC2)         Write:         SCTE         TCIE         SCRIE         ILLE         TE         RE         RWU         SBK           S0014         SCI Control Register 2<br>(SCC2)         Write:         SCTE         TCIE         SCRE         ILLE         TE         RE         RWU         SBK           S0016         SCI Status Register 1 (SCS)         Write:         SCTE         TC         SCRF         IDLE         OR         NF         FE         PE           S0017         SCI Status Register 2<br>(SCC3)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | \$0010               | (SPCR)                            |   |       |       |        |           |            |        |      |       |

| Sol 1 Sala Biolow Wite:<br>(SPSCR)         ERRIE         MODFEN         SPR1         SPR0           Sol 1         Register<br>(SPSCR)         Reset:         0         0         0         1         0         0         0           Sol 12         SPI Data Register<br>(SPDR)         Read:<br>(SPDR)         R7         R6         R5         R4         R3         R2         R1         R0           Sol 12         SPI Data Register<br>(SPDR)         Write:         T7         T6         T5         T4         T3         T2         T1         T0           Sol 13         SCI Control Register<br>(SCC)         Read:         LOOPS         ENSCI         TXINV         M         WAKE         ILTY         PEN         PTY           Reset:         0         0         0         0         0         0         0         0         0           Sol 14         SCI Control Register 2<br>(SCC2)         Write:         SCTIE         TCIE         SCRIE         ILLE         TE         RE         RWU         SBK           Sol 15         SCI Control Register 3<br>(SCC3)         Write:         SCTE         TC         SCRF         IDLE         OR         0         0         0         0         0         0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                      |                                   |   |       | 0     | 1      |           |            | 0      | 0    | 0     |

| (SPSCR)         Reset:         0         0         0         0         1         0         0         0           \$0012         SPI Data Register<br>(SPDR)         Radi<br>(SPDR)         R7         R6         R5         R4         R3         R2         R1         R0           \$0012         SPI Data Register<br>(SPDR)         Write:         T7         T6         T5         T4         T3         T2         T1         T0           \$0013         SCI Control Register 1<br>(SCC1)         Read:<br>(SCC2)         Read:<br>(SCC2)         LOOPS         ENSCI         TXINV         M         WAKE         ILTY         PEN         PTY           \$0014         SCI Control Register 2<br>(SCC2)         Read:<br>(SCC3)         SCTIE         TCIE         SCRIE         ILIE         TE         RE         RWU         SBK           \$0015         SCI Control Register 2<br>(SCC3)         Write:         SCTIE         TC         SCRIE         ILIE         TE         RE         PEUE         PEIE         PEIE <td><b>0011</b></td> <td></td> <td></td> <td>SPRF</td> <td>ERRIE</td> <td>OVRF</td> <td>MODE</td> <td>SPIE</td> <td>MODFEN</td> <td>SPR1</td> <td>SPR0</td>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | <b>0011</b>          |                                   |   | SPRF  | ERRIE | OVRF   | MODE      | SPIE       | MODFEN | SPR1 | SPR0  |

| Sould         SPI Data Register<br>(SPDR)         Read:<br>Price         R7         R6         R5         R4         R3         R2         R1         R0           Sould         SPI Data Register<br>(SPDR)         Reset:         T7         T6         T5         T4         T3         T2         T1         T0           Sould         SCI Control Register 1<br>(SCC)         Read:<br>(SCC)         Read:<br>Write:         LOOPS         ENSCI         TXINV         M         WAKE         ILTY         PEN         PTY           Sould         SCI Control Register 2<br>(SCC2)         Read:<br>(SCC2)         SCTIE         TCIE         SCRIE         ILIE         TE         RE         RWU         SBK           Sould         SCI Control Register 2<br>(SCC2)         Read:<br>(SCC2)         SCTIE         TCIE         SCRIE         ILIE         TE         RE         RWU         SBK           Sould         SCI Control Register 3<br>(SCC2)         Write:         SCTE         TCIE         SCRIE         ILIE         TE         RE         RWU         SBK           Sould         SCI Control Register 3<br>(SCC2)         Write:         SCTE         TC         SCRF         IDLE         OR         NF         FE         PE           Sould                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | \$0011               |                                   |   |       |       |        |           |            |        |      |       |

| S0012         SPI Data Register<br>(SPDR)         Write:<br>Reset:         T7         T6         T5         T4         T3         T2         T1         T0           \$0013         SCI Control Register 1<br>(SCC1)         Read:<br>(SCC2)         Read:<br>Write:<br>(SCC2)         Read:<br>Peset:         LOOPS         ENSCI         TXINV         M         WAKE         ILTY         PEN         PTY           \$0014         SCI Control Register 2<br>(SCC2)         Read:<br>Write:<br>(SCC2)         SCTIE         TCIE         SCRIE         ILIE         TE         RE         RWU         SBK           \$0014         SCI Control Register 2<br>(SCC2)         Read:<br>Write:<br>Reset:         SCTIE         TCIE         SCRIE         ILIE         TE         RE         RWU         SBK           \$0015         SCI Control Register 3<br>(SCC3)         Write:<br>Reset:         SCTE         TCIE         SCRF         IDIA RE         ORIE         NEIE         FEIE         PEIE           \$0016         SCI Status Register 1 (SCS1)         Write:<br>Reset:         U         U         0         0         0         0         0           \$0016         SCI Status Register 2 (SCS2)         Write:<br>(SCRP)         Read:<br>R7         R6         R5         R4         R3         R2         R1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                      |                                   |   |       |       |        |           |            | i      |      |       |

| 30012       (SPDR)       Write:       17       10       13       12       11       10         Reset:       Unaffected by reset         \$0013       SCI Control Register 1<br>(SCC1)       Read:       LOOPS       ENSCI       TXINV       M       WAKE       ILTY       PEN       PTY         \$0014       SCI Control Register 2<br>(SCC2)       Read:       LOOPS       ENSCI       TXINV       M       WAKE       ILTY       PEN       PTY         \$0014       SCI Control Register 2<br>(SCC2)       Read:       LOOPS       ENSCI       TXINV       M       WAKE       ILTY       PEN       PTY         \$0015       SCI Control Register 2<br>(SCC2)       Read:       SCTIE       TCIE       SCRIE       ILIE       TE       RE       RWU       SBK         \$0015       SCI Control Register 3<br>(SCC3)       Write:       SCTE       TC       SCRF       IDLE       ORIE       NEIE       FEIE       PEIE         \$0016       SCI Status Register 1 (SCS1)       Write:       Read:       I       0       0       0       0       0         \$0017       SCI Status Register 2 (SCS2)       Write:       I       1       0       0       0       0       0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | ¢0010                | SPI Data Register                 |   |       |       |        |           |            |        |      |       |

| S0013         SCI Control Register 1<br>(SCC)         Read:<br>Write:<br>Reset:         LOOPS         ENSCI         TXINV         M         WAKE         ILTY         PEN         PTY           S0014         SCI Control Register 2<br>(SCC)         Read:<br>Write:         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | \$0012               | (SPDR)                            |   | 17    | 16    | 15     |           |            | 12     | 11   | 10    |

| S0013         SCI Control Register 1<br>(SCC1)         Write:<br>Reset:         LOOPS         ENSCI         TXINV         M         WAKE         ILTY         PEN         PTY           S0014         SCI Control Register 2<br>(SCC2)         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                      |                                   |   |       |       | Ì      | Unaffecte | a by reset | 1      |      |       |

| SO14         SCI Control Register 2<br>(SCC)         Read:<br>Write:         SCTIE         TCIE         SCRIE         ILIE         TE         RE         RWU         SBK           \$0014         SCI Control Register 2<br>(SCC)         Mrite:         SCTIE         TCIE         SCRIE         ILIE         TE         RE         RWU         SBK           \$0015         SCI Control Register 3<br>(SCC)         Read:         R8         T8         DMARE         DMATE         ORIE         NEIE         FEIE         PEIE           \$0016         SCI Status Register 1 (SCS1)         Write:         TC         SCRF         IDLE         OR         NF         FE         PE           \$0017         SCI Status Register 2 (SCS2)         Write:         TC         SCRF         IDLE         OR         NF         FE         PE           \$0017         SCI Status Register 2 (SCS2)         Write:         T         1         0         0         0         0         0         0           \$0018         SCI Data Register 3 (SCS2)         Write:         T7         T6         T5         T4         T3         T2         T1         T0           \$0018         SCI Data Register (SCSP)         Read:         O         O                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | \$0013               |                                   |   | LOOPS | ENSCI | TXINV  | М         | WAKE       | ILTY   | PEN  | PTY   |

| S0014         SCI Control Register 2<br>(SCC2)         Write:<br>Reset:         SCTIE         TCIE         SCRIE         ILIE         TE         RE         RWU         SBK           80015         SCI Control Register 3<br>(SCC3)         Write:<br>Reset:         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                      | (5001)                            |   | 0     | 0     | 0      | 0         | 0          | 0      | 0    | 0     |

| SOU14         (SCC2)         Write:         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | <b>\$</b> 0014       | SCI Control Register 2            |   | SCTIE | TCIE  | SCRIE  | ILIE      | TE         | RE     | RWU  | SBK   |

| S0015SCI Control Register (SCG)Read:<br>Write:<br>Reset:R8<br>T8T8DMAREDMATEORIENEIEFEIEPEIE $0015$ SCI Status Register 1 (SC1)Read:UU00000 $80016$ SCI Status Register 1 (SC1)Write:SCTETCSCRFIDLEORNFFEPE $80017$ SCI Status Register 2 (SC2)Write:I1000000 $80017$ SCI Status Register 2 (SC2)Write:IIIIIIIIIIIIIIIIIIIIIIIIIIIIIIIIIIIIIIIIIIIIIIIIIIIIIIIIIIIIIIIIIIIIIIIIIIIIIIIIIIIIIIIIIIIIIIIIIIIIIIIIIIIIIIIIIIIIIIIIIIIIIIIII <td< td=""><td>\$0014</td><td colspan="2"></td><td></td><td></td><td></td><td></td><td></td><td></td><td></td><td></td></td<>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | \$0014               |                                   |   |       |       |        |           |            |        |      |       |

| S0015         SCI Control Register 3<br>(SCC3)         Write:<br>Reset:         T8         DMARE         DMATE         ORIE         NEIE         FEIE         PEIE           80015         SCI Control Register 3<br>(SCC3)         Write:         I         U         U         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0<                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                      |                                   |   |       | 0     | 0      | 0         | 0          | 0      | 0    | 0     |

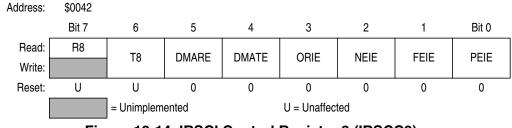

| S0013         (SC3)         Write:         Reset:         U         U         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | ¢0015                | SCI Control Register 3            |   | R8    | Т8    | DMARE  | DMATE     | ORIE       | NEIE   | FEIE | PEIE  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | \$0015               |                                   |   |       |       |        |           |            |        |      |       |

| \$0016       SCI Status Register 1 (SCS1)       Write:<br>Reset:       1       1       0       0       0       0       0         \$0017       SCI Status Register 2 (SCS2)       Read:       0       0       0       0       0       0       0       0       0       0         \$0017       SCI Status Register 2 (SCS2)       Write:       Image: Comparison of the comparison                                                                                                                                                                                |                      |                                   |   |       |       |        |           |            | i      |      |       |

| Reset:         1         1         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0 <td>\$001C</td> <td>CCI Status Decister 1 (SCS1)</td> <td></td> <td>SUIE</td> <td></td> <td>SURF</td> <td>IDLE</td> <td>UK</td> <td></td> <td>FE</td> <td>۲E</td>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | \$001C               | CCI Status Decister 1 (SCS1)      |   | SUIE  |       | SURF   | IDLE      | UK         |        | FE   | ۲E    |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | φυυισ                | 3013 action negative 1 ( $3031$ ) | - | 1     | 4     | 0      | 0         | 0          | 0      | 0    | 0     |

| \$0017       SCI Status Register 2 (SCS2)       Write:       Image: Sci Status Register 2 (SCS2)       Write:       Image: Reset:       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                      |                                   |   |       |       | 1      |           | 1          |        |      |       |

| S0018         SCI Data Register<br>(SCDR)         Reset:         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | \$0017               | SCI Status Register 2 (SCS2)      |   | 0     | 0     | 0      | 0         | 0          | 0      | DRF  | nrr   |

| \$0018         SCI Data Register<br>(SCDR)         Read:<br>Write:         R7         R6         R5         R4         R3         R2         R1         R0           \$0018         SCI Data Register<br>(SCDR)         Write:         T7         T6         T5         T4         T3         T2         T1         T0           \$0019         SCI Baud Rate Register<br>(SCBR)         Read:<br>Nrite:         0         0         SCP1         SCP0         R         SCR2         SCR1         SCR0           \$0019         SCI Baud Rate Register<br>(SCBR)         0         0         0         0         0         0         0         0         0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | φυστη                |                                   |   | 0     | 0     | 0      | 0         | 0          | 0      | 0    | 0     |

| \$0018         SCI Data Register<br>(SCDR)         Write:         T7         T6         T5         T4         T3         T2         T1         T0           \$0019         SCI Baud Rate Register<br>(SCBR)         Write:         T7         T6         T5         T4         T3         T2         T1         T0           \$0019         SCI Baud Rate Register<br>(SCBR)         Write:         0         0         SCP1         SCP0         R         SCR2         SCR1         SCR0           \$0019         SCI Baud Rate Register<br>(SCBR)         Write:         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                      |                                   |   |       |       |        |           |            | i      |      |       |

| SO019         SCI Baud Rate Register<br>(SCBR)         Reset:         Unaffected by reset           \$0019         SCI Baud Rate Register<br>(SCBR)         0         0         SCP1         SCP0         R         SCR2         SCR1         SCR0           \$0019         SCI Baud Rate Register<br>(SCBR)         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | \$0018               |                                   |   |       |       |        |           |            |        |      |       |

| \$0019     SCI Baud Rate Register<br>(SCBR)     Read:     0     0     SCP1     SCP0     R     SCR2     SCR1     SCR0       ************************************                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | (SCDR)               |                                   |   |       |       | 15     |           |            |        |      | 10    |

| \$0019SCI Baud Rate Register<br>(SCBR)Write:SCP1SCP0RSCR2SCR1SCR0Reset:00000000                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                      |                                   |   | 0     | 0     |        |           |            |        |      | ]     |

| (SCBR) Reset: 0 0 0 0 0 0 0 0 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | \$0019               |                                   |   |       |       | SCP1   | SCP0      | R          | SCR2   | SCR1 | SCR0  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | <i></i>              | (SCBR)                            |   | 0     | 0     | 0      | 0         | 0          | 0      | 0    | 0     |