Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Product Status             | Obsolete                                                   |

|----------------------------|------------------------------------------------------------|

| Core Processor             | HC08                                                       |

| Core Size                  | 8-Bit                                                      |

| Speed                      | 8MHz                                                       |

| Connectivity               | I <sup>2</sup> C, IRSCI, SCI, SPI                          |

| Peripherals                | LED, LVD, POR, PWM                                         |

| Number of I/O              | 30                                                         |

| Program Memory Size        | 64KB (64K x 8)                                             |

| Program Memory Type        | FLASH                                                      |

| EEPROM Size                | -                                                          |

| RAM Size                   | 2K x 8                                                     |

| Voltage - Supply (Vcc/Vdd) | 4.5V ~ 5.5V                                                |

| Data Converters            | A/D 8x10b                                                  |

| Oscillator Type            | Internal                                                   |

| Operating Temperature      | -40°C ~ 85°C (TA)                                          |

| Mounting Type              | Through Hole                                               |

| Package / Case             | 42-SDIP (0.600", 15.24mm)                                  |

| Supplier Device Package    | 42-PDIP                                                    |

| Purchase URL               | https://www.e-xfl.com/pro/item?MUrl=&PartUrl=mc908ap64acbe |

|                            |                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

**Table of Contents**

# Chapter 23 Mechanical Specifications

| 23.1 | Introduction                              | 309 |

|------|-------------------------------------------|-----|

| 23.2 | 48-Pin Low-Profile Quad Flat Pack (LQFP)  | 310 |

| 23.3 | 44-Pin Quad Flat Pack (QFP)               | 311 |

| 23.4 | 42-Pin Shrink Dual In-Line Package (SDIP) | 312 |

|      |                                           |     |

# Chapter 24 Ordering Information

| 24.1 | Introduction     | 313 |

|------|------------------|-----|

| 24.2 | MC Order Numbers | 313 |

#### Memory

| Addr.  | Register Name                             |                 | Bit 7        | 6      | 5     | 4           | 3              | 2     | 1          | Bit 0     |

|--------|-------------------------------------------|-----------------|--------------|--------|-------|-------------|----------------|-------|------------|-----------|

| \$0026 | Timer 1 Channel 0<br>Register High        | Read:<br>Write: | Bit 15       | 14     | 13    | 12          | 11             | 10    | 9          | Bit 8     |

|        | (T1CH0H)                                  | Reset:          |              |        |       | Indetermina | te after reset |       |            |           |

| \$0027 | Timer 1 Channel 0<br>Register Low         | Read:<br>Write: | Bit 7        | 6      | 5     | 4           | 3              | 2     | 1          | Bit 0     |

|        | (T1CH0L)                                  | Reset:          |              | •      |       | Indetermina | te after reset |       |            |           |

|        | Timer 1 Channel 1 Status and              | Read:           | CH1F         | CH1IE  | 0     | MS1A        | ELS1B          | ELS1A | TOV1       | CH1MAX    |

| \$0028 | Control Register (T1SC1)                  | Write:          | 0            |        |       |             |                |       | 1011       | OTTIM/ UX |

|        | <b>0</b> ( )                              | Reset:          | 0            | 0      | 0     | 0           | 0              | 0     | 0          | 0         |

| \$0029 | Timer 1 Channel 1<br>Register High        | Read:<br>Write: | Bit 15       | 14     | 13    | 12          | 11             | 10    | 9          | Bit 8     |

|        | (T1CH1H)                                  | Reset:          |              |        | -     | Indetermina | te after reset |       |            |           |

| \$002A | Timer 1 Channel 1<br>Register Low         | Read:<br>Write: | Bit 7        | 6      | 5     | 4           | 3              | 2     | 1          | Bit 0     |

|        | (T1CH1L)                                  | Reset:          |              |        |       | Indetermina | te after reset |       |            |           |

|        | Timer 2 Status and                        | Read:           | TOF          | TOIE   | TSTOP | 0           | 0              | PS2   | PS1        | PS0       |

| \$002B | Control Register                          | Write:          | 0            |        | 1310F | TRST        |                | F JZ  | FOI        | F 30      |

|        | (T2SC)                                    | Reset:          | 0            | 0      | 1     | 0           | 0              | 0     | 0          | 0         |

|        | Timer 2 Counter                           | Read:           | Bit 15       | 14     | 13    | 12          | 11             | 10    | 9          | Bit 8     |

| \$002C | Register High                             | Write:          |              |        |       |             |                |       |            |           |

|        | (T2CNTH)                                  |                 | 0            | 0      | 0     | 0           | 0              | 0     | 0          | 0         |

|        | Timer 2 Counter                           | Read:           | Bit 7        | 6      | 5     | 4           | 3              | 2     | 1          | Bit 0     |

| \$002D | Register Low<br>(T2CNTL)                  |                 |              |        |       |             |                | -     |            |           |

|        |                                           | Reset:          | 0            | 0      | 0     | 0           | 0              | 0     | 0          | 0         |

| \$002E | Timer 2 Counter Modulo Reg-<br>ister High | Read:<br>Write: | Bit 15       | 14     | 13    | 12          | 11             | 10    | 9          | Bit 8     |

|        | (T2MODH)                                  | Reset:          | 1            | 1      | 1     | 1           | 1              | 1     | 1          | 1         |

| \$002F | Timer 2 Counter Modulo<br>Register Low    | Read:<br>Write: | Bit 7        | 6      | 5     | 4           | 3              | 2     | 1          | Bit 0     |

|        | (T2MODL)                                  | Reset:          | 1            | 1      | 1     | 1           | 1              | 1     | 1          | 1         |

|        | Timer 2 Channel 0 Status and              | Read:           | CH0F         | CHOIE  | MS0B  | MS0A        | ELS0B          | ELS0A | TOV0       | CH0MAX    |

| \$0030 | Control Register (T2SC0)                  | Write:          | 0            |        |       |             |                |       | 1010       |           |

|        | <b>0</b> ( )                              | Reset:          | 0            | 0      | 0     | 0           | 0              | 0     | 0          | 0         |

| \$0031 | Timer 2 Channel 0<br>Register High        | Read:<br>Write: | Bit 15       | 14     | 13    | 12          | 11             | 10    | 9          | Bit 8     |

|        | (T2CH0H) R                                |                 |              |        |       | Indetermina | te after reset |       |            |           |

| \$0032 | Timer 2 Channel 0<br>Register Low         | Read:<br>Write: | Bit 7        | 6      | 5     | 4           | 3              | 2     | 1          | Bit 0     |

|        | (T2CH0L)                                  | Reset:          |              |        |       | Indetermina | te after reset |       |            |           |

|        | U = Unaffected                            |                 | X = Indetern | ninate |       | = Unimplem  | ented          | R     | = Reserved |           |

|        |                                           |                 |              | _      |       |             |                |       |            |           |

Figure 2-2. Control, Status, and Data Registers (Sheet 4 of 9)

MC68HC908AP A-Family Data Sheet, Rev. 3

# MC68HC908AP A-Family Data Sheet, Rev. 3

| Table | 4-2. | Opcode | Мар |

|-------|------|--------|-----|

|-------|------|--------|-----|

|            | Bit Mani             | pulation            | Branch            |                    |                     | Read-Mo             | dify-Write          |                    |                    | Con                | trol -            |                   |                   |                   | Register          | /Memory           |                   |                   |                  |

|------------|----------------------|---------------------|-------------------|--------------------|---------------------|---------------------|---------------------|--------------------|--------------------|--------------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|

|            | DIR                  | DIR                 | REL               | DIR                | INH                 | INH                 | IX1                 | SP1                | IX                 | INH                | INH               | IMM               | DIR               | EXT               | IX2               | SP2               | IX1               | SP1               | IX               |

| MSB<br>LSB | 0                    | 1                   | 2                 | 3                  | 4                   | 5                   | 6                   | 9E6                | 7                  | 8                  | 9                 | A                 | В                 | с                 | D                 | 9ED               | E                 | 9EE               | F                |

| 0          | 5<br>BRSET0<br>3 DIR | 4<br>BSET0<br>2 DIR | 3<br>BRA<br>2 REL | 4<br>NEG<br>2 DIR  | 1<br>NEGA<br>1 INH  | 1<br>NEGX<br>1 INH  | 4<br>NEG<br>2 IX1   | 5<br>NEG<br>3 SP1  | 3<br>NEG<br>1 IX   | 7<br>RTI<br>1 INH  | 3<br>BGE<br>2 REL | 2<br>SUB<br>2 IMM | 3<br>SUB<br>2 DIR | 4<br>SUB<br>3 EXT | 4<br>SUB<br>3 IX2 | 5<br>SUB<br>4 SP2 | 3<br>SUB<br>2 IX1 | 4<br>SUB<br>3 SP1 | 2<br>SUB<br>1 IX |

| 1          | 5<br>BRCLR0<br>3 DIR | 4<br>BCLR0<br>2 DIR | 3<br>BRN<br>2 REL | 5<br>CBEQ<br>3 DIR | 4<br>CBEQA<br>3 IMM | 4<br>CBEQX<br>3 IMM | 5<br>CBEQ<br>3 IX1+ | 6<br>CBEQ<br>4 SP1 | 4<br>CBEQ<br>2 IX+ | 4<br>RTS<br>1 INH  | 3<br>BLT<br>2 REL | 2<br>CMP<br>2 IMM | 3<br>CMP<br>2 DIR | 4<br>CMP<br>3 EXT | 4<br>CMP<br>3 IX2 | 5<br>CMP<br>4 SP2 | 3<br>CMP<br>2 IX1 | 4<br>CMP<br>3 SP1 | 2<br>CMP<br>1 IX |

| 2          | 5<br>BRSET1<br>3 DIR | 4<br>BSET1<br>2 DIR |                   |                    | 5<br>MUL<br>1 INH   | 7<br>DIV<br>1 INH   | 3<br>NSA<br>1 INH   |                    | 2<br>DAA<br>1 INH  |                    | BGT<br>2 REL      | 2<br>SBC<br>2 IMM |                   | 3 EXT             | 4<br>SBC<br>3 IX2 | SBC<br>4 SP2      | 3<br>SBC<br>2 IX1 | 4<br>SBC<br>3 SP1 | SBC<br>1 IX      |

| 3          | 5<br>BRCLR1<br>3 DIR |                     |                   | 4<br>COM<br>2 DIR  | 1<br>COMA<br>1 INH  | 1<br>COMX<br>1 INH  | 4<br>COM<br>2 IX1   | 5<br>COM<br>3 SP1  | 3<br>COM<br>1 IX   |                    | 3<br>BLE<br>2 REL |                   |                   | CPX<br>3 EXT      |                   |                   | 3<br>CPX<br>2 IX1 | 4<br>CPX<br>3 SP1 | 2<br>CPX<br>1 IX |

| 4          | 5<br>BRSET2<br>3 DIR | 4<br>BSET2<br>2 DIR |                   | 4<br>LSR<br>2 DIR  | 1<br>LSRA<br>1 INH  |                     | 4<br>LSR<br>2 IX1   | 5<br>LSR<br>3 SP1  | 3<br>LSR<br>1 IX   | 2<br>TAP<br>1 INH  | 2<br>TXS<br>1 INH |                   |                   | 4<br>AND<br>3 EXT |                   |                   | 3<br>AND<br>2 IX1 | 4<br>AND<br>3 SP1 | 2<br>AND<br>1 IX |

| 5          | 5<br>BRCLR2<br>3 DIR |                     |                   | 4<br>STHX<br>2 DIR | 3<br>LDHX<br>3 IMM  | 4<br>LDHX<br>2 DIR  | 3<br>CPHX<br>3 IMM  |                    | 4<br>CPHX<br>2 DIR | 1<br>TPA<br>1 INH  | 2<br>TSX<br>1 INH |                   |                   |                   |                   | 5<br>BIT<br>4 SP2 |                   | 4<br>BIT<br>3 SP1 | BIT<br>1 IX      |

| 6          | -                    | 4<br>BSET3<br>2 DIR |                   | 4<br>ROR<br>2 DIR  |                     | 1<br>RORX<br>1 INH  | 4<br>ROR<br>2 IX1   | 80R<br>3 SP1       |                    | 2<br>PULA<br>1 INH |                   | 2<br>LDA<br>2 IMM |                   |                   | -                 | 5<br>LDA<br>4 SP2 |                   | 4<br>LDA<br>3 SP1 | 2<br>LDA<br>1 IX |

| 7          | 5<br>BRCLR3<br>3 DIR |                     |                   | 4<br>ASR<br>2 DIR  | 1<br>ASRA<br>1 INH  |                     | 4<br>ASR<br>2 IX1   | 5<br>ASR<br>3 SP1  |                    | 2<br>PSHA<br>1 INH | 1<br>TAX<br>1 INH |                   |                   |                   | 4<br>STA<br>3 IX2 | 5<br>STA<br>4 SP2 |                   | 4<br>STA<br>3 SP1 |                  |

| 8          | 5<br>BRSET4<br>3 DIR | 4<br>BSET4<br>2 DIR |                   | 4<br>LSL<br>2 DIR  | 1<br>LSLA<br>1 INH  |                     | 4<br>LSL<br>2 IX1   | 5<br>LSL<br>3 SP1  | 3<br>LSL<br>1 IX   | 2<br>PULX<br>1 INH | 1<br>CLC<br>1 INH |                   |                   |                   | 4<br>EOR<br>3 IX2 | -                 | 3<br>EOR<br>2 IX1 | 4<br>EOR<br>3 SP1 | EOR<br>1 IX      |

| 9          | 5<br>BRCLR4<br>3 DIR |                     |                   | 4<br>ROL<br>2 DIR  | 1<br>ROLA<br>1 INH  |                     | 4<br>ROL<br>2 IX1   | 5<br>ROL<br>3 SP1  | 3<br>ROL<br>1 IX   | 2<br>PSHX<br>1 INH |                   | 2<br>ADC<br>2 IMM |                   | 4<br>ADC<br>3 EXT |                   |                   | 3<br>ADC<br>2 IX1 | 4<br>ADC<br>3 SP1 | ADC<br>1 IX      |

| A          | -                    | 4<br>BSET5<br>2 DIR |                   | 4<br>DEC<br>2 DIR  |                     |                     | 4<br>DEC<br>2 IX1   | 5<br>DEC<br>3 SP1  |                    | 2<br>PULH<br>1 INH | 2<br>CLI<br>1 INH |                   |                   | 4<br>ORA<br>3 EXT |                   |                   | 3<br>ORA<br>2 IX1 | 4<br>ORA<br>3 SP1 | 2<br>ORA<br>1 IX |

| В          |                      | 4<br>BCLR5<br>2 DIR |                   |                    |                     | 3<br>DBNZX<br>2 INH | 5<br>DBNZ<br>3 IX1  | 6<br>DBNZ<br>4 SP1 |                    | PSHH<br>1 INH      | SEI<br>1 INH      | ADD<br>2 IMM      |                   |                   |                   | 5<br>ADD<br>4 SP2 |                   | 4<br>ADD<br>3 SP1 | ADD<br>1 IX      |

| с          |                      | 4<br>BSET6<br>2 DIR |                   | 4<br>INC<br>2 DIR  | 1<br>INCA<br>1 INH  | 1<br>INCX<br>1 INH  |                     | 5<br>INC<br>3 SP1  |                    | 1<br>CLRH<br>1 INH | 1<br>RSP<br>1 INH |                   | 2<br>JMP<br>2 DIR |                   |                   |                   | 3<br>JMP<br>2 IX1 |                   | 2<br>JMP<br>1 IX |

| D          | -                    | 4<br>BCLR6<br>2 DIR |                   | 3<br>TST<br>2 DIR  | 1<br>TSTA<br>1 INH  |                     | 3<br>TST<br>2 IX1   | 4<br>TST<br>3 SP1  |                    |                    | 1<br>NOP<br>1 INH |                   |                   | 5<br>JSR<br>3 EXT |                   |                   | 5<br>JSR<br>2 IX1 |                   | 4<br>JSR<br>1 IX |

| E          | 5<br>BRSET7<br>3 DIR |                     | 3<br>BIL<br>2 REL |                    | 5<br>MOV<br>3 DD    | 4<br>MOV<br>2 DIX+  | 4<br>MOV<br>3 IMD   |                    | 4<br>MOV<br>2 IX+D | 1<br>STOP<br>1 INH | *                 | 2<br>LDX<br>2 IMM |                   | 4<br>LDX<br>3 EXT |                   | 5<br>LDX<br>4 SP2 |                   | 4<br>LDX<br>3 SP1 |                  |

| F          | 5<br>BRCLR7<br>3 DIR | 4<br>BCLR7<br>2 DIR | 3<br>BIH<br>2 REL | 3<br>CLR<br>2 DIR  | 1<br>CLRA<br>1 INH  | 1<br>CLRX<br>1 INH  | 3<br>CLR<br>2 IX1   | 4<br>CLR<br>3 SP1  | 2<br>CLR<br>1 IX   | 1<br>WAIT<br>1 INH | 1<br>TXA<br>1 INH | AIX<br>2 IMM      | 3<br>STX<br>2 DIR | STX<br>3 EXT      | 4<br>STX<br>3 IX2 | 5<br>STX<br>4 SP2 | 3<br>STX<br>2 IX1 | 4<br>STX<br>3 SP1 | STX<br>1 IX      |

INH Inherent IMM Immediate DIR Direct EXT Extended DD Direct-Direct

- INH Inherent IMM Immediate DIR Direct EXT Extended DD Direct-Direct IX+D Indexed-Direct IX+D Indexed-Direct IX+D Indexed-Direct IX+D Indexed-Direct IX+D Indexed-Direct IX+D Indexed-Direct

SP1 Stack Pointer, 8-Bit Offset SP2 Stack Pointer, 16-Bit Offset IX+ Indexed, No Offset with Post Increment IX1+ Indexed, 1-Byte Offset with Post Increment

MSB LSB Low Byte of Opcode in Hexadecimal 0

High Byte of Opcode in Hexadecimal 0

5 Cycles BRSET0 Opcode Mnemonic 3 DIR Number of Bytes / Addressing Mode

\*Pre-byte for stack pointer indexed instructions

MC68HC908AP A-Family Data Sheet, Rev. 3

#### **Functional Description**

| Addr.  | Register Name                         |                 | Bit 7 | 6          | 5     | 4    | 3     | 2          | 1    | Bit 0  |

|--------|---------------------------------------|-----------------|-------|------------|-------|------|-------|------------|------|--------|

| \$0036 | PLL Control Register<br>(PTCL)        | Read:<br>Write: | PLLIE | PLLF       | PLLON | BCS  | PRE1  | PRE0       | VPR1 | VPR0   |

|        |                                       | Reset:          | 0     | 0          | 1     | 0    | 0     | 0          | 0    | 0      |

| \$0037 | PLL Bandwidth Control<br>Register     | Read:<br>Write: | AUTO  | LOCK       | ACQ   | 0    | 0     | 0          | 0    | R      |

|        | (PBWC)                                | Reset:          | 0     | 0          | 0     | 0    | 0     | 0          | 0    |        |

|        | PLL Multiplier Select                 | Read:           | 0     | 0          | 0     | 0    | MUL11 | MUL10      | MUL9 | MUL8   |

| \$0038 | Register High                         | Write:          |       |            |       |      | WOLTT | MOLIU      | MOL9 | IVIULO |

|        | (PMSH)                                | Reset:          | 0     | 0          | 0     | 0    | 0     | 0          | 0    | 0      |

| \$0039 | PLL Multiplier Select<br>Register Low | Read:<br>Write: | MUL7  | MUL6       | MUL5  | MUL4 | MUL3  | MUL2       | MUL1 | MUL0   |

|        | (PMSL)                                | Reset:          | 0     | 1          | 0     | 0    | 0     | 0          | 0    | 0      |

| \$003A | PLL VCO Range Select<br>Register      | Read:<br>Write: | VRS7  | VRS6       | VRS5  | VRS4 | VRS3  | VRS2       | VRS1 | VRS0   |

|        | (PMRS)                                | Reset:          | 0     | 1          | 0     | 0    | 0     | 0          | 0    | 0      |

|        | PLL Reference Divider                 | Read:           | 0     | 0          | 0     | 0    | RDS3  | RDS2       | RDS1 | RDS0   |

| \$003B | Select Register                       | Write:          |       |            |       |      |       |            | -    |        |

|        | (PMDS)                                | Reset:          | 0     | 0          | 0     | 0    | 0     | 0          | 0    | 1      |

|        |                                       | l               |       | = Unimplem | ented |      | R     | = Reserved |      |        |

NOTES:

1. When AUTO = 0, PLLIE is forced clear and is read-only.

2. When AUTO = 0, PLLF and LOCK read as clear.

3. When AUTO = 1,  $\overline{ACQ}$  is read-only.

4. When PLLON = 0 or VRS7:VRS0 = \$0, BCS is forced clear and is read-only.

5. When PLLON = 1, the PLL programming register is read-only.

6. When BCS = 1, PLLON is forced set and is read-only.

#### Figure 6-2. CGM I/O Register Summary

#### 6.3.1 Oscillator Module

The oscillator module provides two clock outputs CGMXCLK and CGMRCLK to the CGM module. CGMXCLK when selected, is driven to SIM module to generate the system bus clock. CGMRCLK is used by the phase-lock-loop to provide a higher frequency system bus clock. The oscillator module also provides the reference clock for the timebase module (TBM). See Chapter 5 Oscillator (OSC) for detailed oscillator circuit description. See Chapter 10 Timebase Module (TBM) for detailed description on TBM.

#### 6.3.2 Phase-Locked Loop Circuit (PLL)

The PLL is a frequency generator that can operate in either acquisition mode or tracking mode, depending on the accuracy of the output frequency. The PLL can change between acquisition and tracking modes either automatically or manually.

#### 6.3.3 PLL Circuits

The PLL consists of these circuits:

- Voltage-controlled oscillator (VCO)

- Reference divider

- Frequency pre-scaler

- Modulo VCO frequency divider

# Chapter 7 System Integration Module (SIM)

# 7.1 Introduction

•

This section describes the system integration module (SIM). Together with the CPU, the SIM controls all MCU activities. A block diagram of the SIM is shown in Figure 7-1. Figure 7-2 is a summary of the SIM input/output (I/O) registers. The SIM is a system state controller that coordinates CPU and exception timing. The SIM is responsible for:

- Bus clock generation and control for CPU and peripherals:

- Stop/wait/reset/break entry and recovery

- Internal clock control

- Master reset control, including power-on reset (POR) and COP timeout

- Interrupt control:

- Acknowledge timing

- Arbitration control timing

- Vector address generation

- CPU enable/disable timing

Table 7-1 shows the internal signal names used in this section.

#### Table 7-1. Signal Name Conventions

| Signal Name                                            | Description                                                                                |  |  |  |  |  |

|--------------------------------------------------------|--------------------------------------------------------------------------------------------|--|--|--|--|--|

| ICLK                                                   | Internal oscillator clock                                                                  |  |  |  |  |  |

| CGMXCLK                                                | Selected oscillator clock from oscillator module                                           |  |  |  |  |  |

| CGMVCLK, CGMPCLK PLL output and the divided PLL output |                                                                                            |  |  |  |  |  |

| CGMOUT                                                 | CGMPCLK-based or oscillator-based clock output from CGM module<br>(Bus clock = CGMOUT ÷ 2) |  |  |  |  |  |

| IAB                                                    | Internal address bus                                                                       |  |  |  |  |  |

| IDB                                                    | Internal data bus                                                                          |  |  |  |  |  |

| PORRST                                                 | Signal from the power-on reset module to the SIM                                           |  |  |  |  |  |

| IRST                                                   | Internal reset signal                                                                      |  |  |  |  |  |

| R/W                                                    | Read/write signal                                                                          |  |  |  |  |  |

System Integration Module (SIM)

#### 7.2.2 Clock Start-up from POR or LVI Reset

When the power-on reset module or the low-voltage inhibit module generates a reset, the clocks to the CPU and peripherals are inactive and held in an inactive phase until after the 4096 ICLK cycle POR timeout has completed. The RST pin is driven low by the SIM during this entire period. The IBUS clocks start upon completion of the timeout.

#### 7.2.3 Clocks in Stop Mode and Wait Mode

Upon exit from stop mode by an interrupt, break, or reset, the SIM allows ICLK to clock the SIM counter. The CPU and peripheral clocks do not become active until after the stop delay timeout. This timeout is selectable as 4096 or 32 ICLK cycles. (See 7.6.2 Stop Mode.)

In wait mode, the CPU clocks are inactive. The SIM also produces two sets of clocks for other modules. Refer to the wait mode subsection of each module to see if the module is active or inactive in wait mode. Some modules can be programmed to be active in wait mode.

# 7.3 Reset and System Initialization

The MCU has these reset sources:

- Power-on reset module (POR)

- External reset pin (RST)

- Computer operating properly module (COP)

- Low-voltage inhibit module (LVI)

- Illegal opcode

- Illegal address

All of these resets produce the vector \$FFFE:\$FFFF (\$FEFE:\$FEFF in monitor mode) and assert the internal reset signal (IRST). IRST causes all registers to be returned to their default values and all modules to be returned to their reset states.

An internal reset clears the SIM counter (see 7.4 SIM Counter), but an external reset does not. Each of the resets sets a corresponding bit in the SIM reset status register (SRSR). (See 7.7 SIM Registers.)

#### 7.3.1 External Pin Reset

The  $\overline{RST}$  pin circuit includes an internal pull-up device. Pulling the asynchronous  $\overline{RST}$  pin low halts all processing. The PIN bit of the SIM reset status register (SRSR) is set as long as  $\overline{RST}$  is held low for at least the minimum t<sub>RL</sub>time and no other reset sources are present. See Table 7-2 for details. Figure 7-4 shows the relative timing.

| Reset Recovery Type | Actual Number of Cycles |

|---------------------|-------------------------|

| POR/LVI             | 4163 (4096 + 64 + 3)    |

| All others          | 67 (64 + 3)             |

| Table 7 | -2. Reset | Recovery |

|---------|-----------|----------|

|---------|-----------|----------|

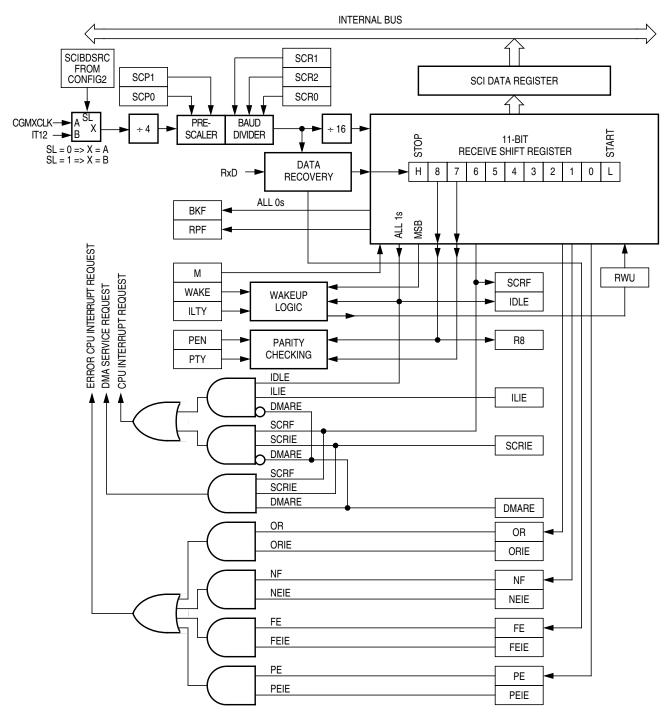

the received byte can be read. If the SCI receive interrupt enable bit, SCRIE, in SCC2 is also set, the SCRF bit generates a receiver CPU interrupt request.

Figure 11-5. SCI Receiver Block Diagram

- The shift register is cleared.

- The SPI state counter is cleared, making it ready for a new complete transmission.

- All the SPI port logic is defaulted back to being general-purpose I/O.

These items are reset only by a system reset:

- All control bits in the SPCR register

- All control bits in the SPSCR register (MODFEN, ERRIE, SPR1, and SPR0)

- The status flags SPRF, OVRF, and MODF

By not resetting the control bits when SPE is low, the user can clear SPE between transmissions without having to set all control bits again when SPE is set back high for the next transmission.

By not resetting the SPRF, OVRF, and MODF flags, the user can still service these interrupts after the SPI has been disabled. The user can disable the SPI by writing 0 to the SPE bit. The SPI can also be disabled by a mode fault occurring in an SPI that was configured as a master with the MODFEN bit set.

# 13.10 Low-Power Modes

The WAIT and STOP instructions put the MCU in low power-consumption standby modes.

#### 13.10.1 Wait Mode

The SPI module remains active after the execution of a WAIT instruction. In wait mode the SPI module registers are not accessible by the CPU. Any enabled CPU interrupt request from the SPI module can bring the MCU out of wait mode.

If SPI module functions are not required during wait mode, reduce power consumption by disabling the SPI module before executing the WAIT instruction.

To exit wait mode when an overflow condition occurs, enable the OVRF bit to generate CPU interrupt requests by setting the error interrupt enable bit (ERRIE). (See 13.8 Interrupts.)

#### 13.10.2 Stop Mode

The SPI module is inactive after the execution of a STOP instruction. The STOP instruction does not affect register conditions. SPI operation resumes after an external interrupt. If stop mode is exited by reset, any transfer in progress is aborted, and the SPI is reset.

# 13.11 SPI During Break Interrupts

The system integration module (SIM) controls whether status bits in other modules can be cleared during the break state. The BCFE bit in the SIM break flag control register (SBFCR) enables software to clear status bits during the break state. (See Chapter 7 System Integration Module (SIM).)

To allow software to clear status bits during a break interrupt, write a logic 1 to the BCFE bit. If a status bit is cleared during the break state, it remains cleared when the MCU exits the break state.

To protect status bits during the break state, write a logic 0 to the BCFE bit. With BCFE at logic 0 (its default state), software can read and write I/O registers during the break state without affecting status bits. Some status bits have a 2-step read/write clearing procedure. If software does the first step on such a bit before the break, the bit cannot change during the break state as long as BCFE is at logic 0. After the break, doing the second step clears the status bit.

#### Multi-Master IIC Interface (MMIIC)

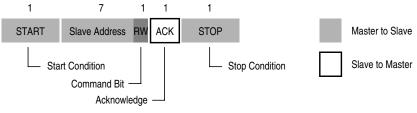

Only the slave with a matched address will respond by sending back an acknowledge bit by pulling SDA low on the 9th clock cycle.

(See Figure 14-2.)

#### 14.5.3 Data Transfer

Once a successful slave addressing is achieved, the data transfer can proceed byte by byte in the direction specified by the R/W-bit sent by the calling master.

Each data byte is 8 bits. Data can be changed only when SCL is low and must be held stable when SCL is high as shown in Figure 14-2. The MSB is transmitted first and each byte has to be followed by an acknowledge bit. This is signalled by the receiving device by pulling the SDA low on the 9th clock cycle. Therefore, one complete data byte transfer requires 9 clock cycles.

If the slave receiver does not acknowledge the master, the SDA line should be left high by the slave. The master can then generate a STOP signal to abort the data transfer or a START signal (repeated START) to commence a new transfer.

If the master receiver does not acknowledge the slave transmitter after a byte has been transmitted, it means an "end of data" to the slave. The slave should release the SDA line for the master to generate a STOP or START signal.

#### 14.5.4 Repeated START Signal

As shown in Figure 14-2, a repeated START signal is used to generate START signal without first generating a STOP to terminate the communication. This is used by the master to communicate with another slave or with the same slave in a different mode (transmit/receive mode) without releasing the bus.

#### 14.5.5 STOP Signal

The master can terminate the communication by generating a STOP signal to free the bus. However, the master may generate a START signal followed by a calling command without first generating a STOP signal. This is called repeat START. A STOP signal is defined as a low to high transition of SDA while SCL is at logic high (see Figure 14-2).

#### 14.5.6 Arbitration Procedure

The interface circuit is a multi-master system which allows more than one master to be connected. If two or more masters try to control the bus at the same time, a clock synchronization procedure determines the bus clock. The clock low period is equal to the longest clock low period and the clock high period is equal to the shortest one among the masters. A data arbitration procedure determines the priority. A master will lose arbitration if it transmits a logic 1 while another transmits a logic 0. The losing master will immediately switch over to slave receive mode and stops its data and clock outputs. The transition from master to slave will not generate a STOP condition. Meanwhile a software bit will be set by hardware to indicates loss of arbitration.

#### 14.5.7 Clock Synchronization

Since wired-AND logic is performed on SCL line, a high to low transition on the SCL line will affect the devices connected to the bus. The devices start counting their low period once a device's clock has gone low, it will hold the SCL line low until the clock high state is reached. However, the change of low to high

Multi-Master IIC Interface (MMIIC)

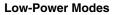

# 14.6.1 MMIIC Address Register (MMADR)

Figure 14-4. MMIIC Address Register (MMADR)

#### MMAD[7:1] — Multi-Master Address

These seven bits represent the MMIIC interface's own specific slave address when in slave mode, and the calling address when in master mode. Software must update MMAD[7:1] as the calling address while entering master mode and restore its own slave address after master mode is relinquished. This register is cleared as \$A0 upon reset.

#### MMEXTAD — Multi-Master Expanded Address

This bit is set to expand the address of the MMIIC in slave mode. When set, the MMIIC will acknowledge the following addresses from a calling master: \$MMAD[7:1], 0000000, and 0001100. Reset clears this bit.

1 = MMIIC responds to the following calling addresses:

\$MMAD[7:1], 0000000, and 0001100.

0 = MMIIC responds to address \$MMAD[7:1]

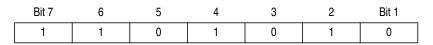

For example, when MMADR is configured as:

| MMAD7 | MMAD6 | MMAD5 | MMAD4 | MMAD3 | MMAD2 | MMAD1 | MMEXTAD |

|-------|-------|-------|-------|-------|-------|-------|---------|

| 1     | 1     | 0     | 1     | 0     | 1     | 0     | 1       |

The MMIIC module will respond to the calling address:

or the general calling address:

or the calling address:

Note that bit-0 of the 8-bit calling address is the MMRW bit from the calling master.

| MMBR2 | MMBR1 | MMBR0 | Divider | MMIIC Baud Rates for Bus Clocks: |           |            |            |  |  |  |

|-------|-------|-------|---------|----------------------------------|-----------|------------|------------|--|--|--|

|       |       |       | Divider | 8MHz                             | 4MHz      | 2MHz       | 1 MHz      |  |  |  |

| 0     | 0     | 0     | 20      | 400kHz                           | 200kHz    | 100kHz     | 50kHz      |  |  |  |

| 0     | 0     | 1     | 40      | 200kHz                           | 100kHz    | 50kHz      | 25kHz      |  |  |  |

| 0     | 1     | 0     | 80      | 100kHz                           | 50kHz     | 25kHz      | 12.5kHz    |  |  |  |

| 0     | 1     | 1     | 160     | 50kHz                            | 25kHz     | 12.5kHz    | 6.25kHz    |  |  |  |

| 1     | 0     | 0     | 320     | 25kHz                            | 12.5kHz   | 6.25kHz    | 3.125kHz   |  |  |  |

| 1     | 0     | 1     | 640     | 12.5kHz                          | 6.25kHz   | 3.125kHz   | 1.5625kHz  |  |  |  |

| 1     | 1     | 0     | 1280    | 6.25kHz                          | 3.125kHz  | 1.5625kHz  | 0.78125kHz |  |  |  |

| 1     | 1     | 1     | 2560    | 3.125kHz                         | 1.5625kHz | 0.78125kHz | 0.3906kHz  |  |  |  |

#### Table 14-2. MMIIC Baud Rate Selection

#### NOTE

The frequency of the MMIIC baud rate is only guaranteed for 100kHz to 10kHz. The divider is available for the flexibility on bus frequency selection.

# 14.7 Program Algorithm

When the MMIIC module detects an arbitration loss in master mode, it releases both SDA and SCL lines immediately. But if there are no further STOP conditions detected, the module will hang up. Therefore, it is recommended to have time-out software to recover from this condition. The software can start the time-out counter by looking at the MMBB (bus busy) flag and reset the counter on the completion of one byte transmission. If a time-out has occurred, software can clear the MMEN bit (disable MMIIC module) to release the bus, and hence clear the MMBB flag. This is the only way to clear the MMBB flag by software if the module hangs up due to a no STOP condition received. The MMIIC can resume operation again by setting the MMEN bit.

# 14.8 SMBus Protocols with PEC and without PEC

Following is a description of the various MMIIC bus protocols with and without a packet error code (PEC).

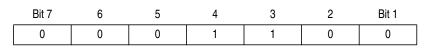

#### 14.8.1 Quick Command

#### 14.8.2 Send Byte

| START                           | Slave Address | W | ACK | Command Code | ACK | STOP |     |   |      |

|---------------------------------|---------------|---|-----|--------------|-----|------|-----|---|------|

| (a) Send Byte I                 | Protocol      |   |     |              |     |      |     |   |      |

| START                           | Slave Address | W | ACK | Command Code | ACK | PEC  | ACK | : | STOP |

| (b) Send Byte Protocol with PEC |               |   |     |              |     |      |     |   |      |

Figure 14-14. Send Byte

#### 14.8.3 Receive Byte

| START          | Slave Address | R | ACK | Data Byte | NAK | STOP |   |     |      |

|----------------|---------------|---|-----|-----------|-----|------|---|-----|------|

| (a) Receive By | te Protocol   |   |     |           |     |      |   |     |      |

| START          | Slave Address | R | ACK | Data Byte | ACK | PEC  | 1 | VAK | STOP |

| •••••          |               |   |     | -         |     |      |   |     |      |

Figure 14-15. Receive Byte

#### Analog-to-Digital Converter (ADC)

#### 15.5.1 Wait Mode

The ADC continues normal operation in wait mode. Any enabled CPU interrupt request from the ADC can bring the MCU out of wait mode. If the ADC is not required to bring the MCU out of wait mode, power down the ADC by setting the ADCH[4:0] bits to logic 1's before executing the WAIT instruction.

#### 15.5.2 Stop Mode

The ADC module is inactive after the execution of a STOP instruction. Any pending conversion is aborted. ADC conversions resume when the MCU exits stop mode. Allow one conversion cycle to stabilize the analog circuitry before attempting a new ADC conversion after exiting stop mode.

# 15.6 I/O Signals

The ADC module has eight channels shared with port A I/O pins.

#### 15.6.1 ADC Voltage In (V<sub>ADIN</sub>)

V<sub>ADIN</sub> is the input voltage signal from one of the eight ADC channels to the ADC module.

#### 15.6.2 ADC Analog Power Pin (V<sub>DDA</sub>)

The ADC analog portion uses  $V_{DDA}$  as its power pin. Connect the  $V_{DDA}$  pin to the same voltage potential as  $V_{DD}$ . External filtering may be necessary to ensure clean  $V_{DDA}$  for good results.

#### NOTE

Route  $V_{DDA}$  carefully for maximum noise immunity and place bypass capacitors as close as possible to the package.

#### 15.6.3 ADC Analog Ground Pin (V<sub>SSA</sub>)

The ADC analog portion uses  $V_{SSA}$  as its ground pin. Connect the  $V_{SSA}$  pin to the same voltage potential as  $V_{SS}$ .

#### 15.6.4 ADC Voltage Reference High Pin (V<sub>REFH</sub>)

$V_{REFH}$  is the power supply for setting the reference voltage  $V_{REFH}$ . Connect the  $V_{REFH}$  pin to the same voltage potential as  $V_{DDA}$ . There will be a finite current associated with  $V_{REFH}$  (see Chapter 22 Electrical Specifications).

#### NOTE

Route  $V_{REFH}$  carefully for maximum noise immunity and place bypass capacitors as close as possible to the package.

#### 15.6.5 ADC Voltage Reference Low Pin (V<sub>REFL</sub>)

$V_{REFL}$  is the lower reference supply for the ADC. Connect the  $V_{REFL}$  pin to the same voltage potential as  $V_{SSA}$ . There will be a finite current associated with  $V_{REFL}$  (see Chapter 22 Electrical Specifications).

**IRQ Registers**

#### IMASK1 — IRQ1 Interrupt Mask Bit

Writing a logic 1 to this read/write bit disables IRQ1 interrupt requests. Reset clears IMASK1.

- $1 = \overline{IRQ1}$  interrupt requests disabled

- $0 = \overline{IRQ1}$  interrupt requests enabled

#### MODE1 — IRQ1 Edge/Level Select Bit

This read/write bit controls the triggering sensitivity of the IRQ1 pin. Reset clears MODE1.

- $1 = \overline{IRQ1}$  interrupt requests on falling edges and low levels

- $0 = \overline{IRQ1}$  interrupt requests on falling edges only

#### 17.6.2 IRQ2 Status and Control Register

The IRQ2 status and control register (INTSCR2) controls and monitors operation of IRQ2. The INTSCR2 has the following functions:

- Enables/disables the internal pullup device on IRQ2 pin

- Shows the state of the IRQ2 flag

- Clears the IRQ2 latch

- Masks IRQ2 interrupt request

- Controls triggering sensitivity of the IRQ2 interrupt pin

- Address: \$001C

|        | Bit 7           | 6        | 5 | 4 | 3     | 2    | 1       | Bit 0 |

|--------|-----------------|----------|---|---|-------|------|---------|-------|

| Read:  | 0               | PUC0ENB  | 0 | 0 | IRQ2F | 0    | IMASK2  | MODE2 |

| Write: |                 | FUCUEIND |   |   |       | ACK2 | IWIAGNZ | WODEZ |

| Reset: | 0               | 0        | 0 | 0 | 0     | 0    | 0       | 0     |

|        | = Unimplemented |          |   |   |       |      |         |       |

Figure 17-5. IRQ2 Status and Control Register (INTSCR2)

#### PUC0ENB — IRQ2 Pin Pullup Enable Bit.

Setting this bit to logic 1 disables the pullup on PTC0/IRQ2 pin.

Reset clears this bit.

- $1 = \overline{IRQ2}$  pin internal pullup is disabled

- $0 = \overline{IRQ2}$  pin internal pullup is enabled

#### IRQ2F — IRQ2 Flag Bit

This read-only status bit is high when the IRQ2 interrupt is pending.

- $1 = \overline{IRQ2}$  interrupt pending

- $0 = \overline{IRQ2}$  interrupt not pending

#### ACK2 — IRQ2 Interrupt Request Acknowledge Bit

Writing a logic 1 to this write-only bit clears the IRQ2 latch. ACK2 always reads as logic 0. Reset clears ACK2.

#### IMASK2 — IRQ2 Interrupt Mask Bit

Writing a logic 1 to this read/write bit disables IRQ2 interrupt requests. Reset clears IMASK2.

- 1 = IRQ2 interrupt requests disabled

- 0 = IRQ2 interrupt requests enabled

#### MODE2 — IRQ2 Edge/Level Select Bit

This read/write bit controls the triggering sensitivity of the IRQ2 pin. Reset clears MODE2.

- $1 = \overline{IRQ2}$  interrupt requests on falling edges and low levels

- $0 = \overline{IRQ2}$  interrupt requests on falling edges only

#### MC68HC908AP A-Family Data Sheet, Rev. 3

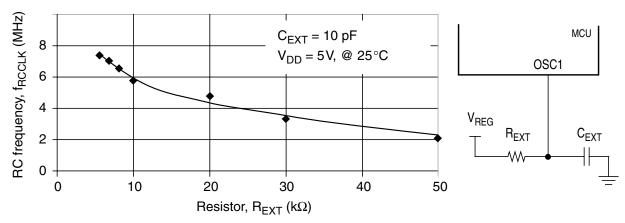

# 22.7 5V Oscillator Characteristics

|                                                 |                   |     |                    | -    |      |

|-------------------------------------------------|-------------------|-----|--------------------|------|------|

| Characteristic <sup>(1)</sup>                   | Symbol            | Min | Тур                | Мах  | Unit |

| Internal oscillator clock frequency             | f <sub>ICLK</sub> | 64k | 88k <sup>(2)</sup> | 104k | Hz   |

| External reference clock to OSC1 <sup>(3)</sup> | f <sub>OSC</sub>  | dc  |                    | 32M  | Hz   |

| Crystal reference frequency <sup>(4)</sup>      | fxtalclk          | 1 M | _                  | 8M   | Hz   |

| Crystal load capacitance <sup>(5)</sup>         | CL                | _   | _                  | _    |      |

| Crystal fixed capacitance <sup>(5)</sup>        | C <sub>1</sub>    | _   | $2 \times C_L$     |      |      |

| Crystal tuning capacitance <sup>(5)</sup>       | C <sub>2</sub>    | —   | $2 \times C_L$     | _    |      |

| Feedback bias resistor                          | R <sub>B</sub>    | —   | 1 M                | _    | Ω    |

| Series resistor <sup>(5)</sup>                  | R <sub>S</sub>    |     | 0                  | —    | Ω    |

| External RC clock frequency                     | fRCCLK            |     |                    | 7.6M | Hz   |

| RC oscillator external R                        | R <sub>EXT</sub>  |     | See Figure 22-     | 1    | Ω    |

| RC oscillator external C                        | C <sub>EXT</sub>  | _   | 10                 | _    | pF   |

#### Table 22-6. Oscillator Specifications (5V)

The oscillator circuit operates at V<sub>REG</sub>.

Typical value reflect average measurements at midpoint of voltage range, 25 °C only.

3. No more than 10% duty cycle deviation from 50%. The max. frequency is limited by an EMC filter.

4. Fundamental mode crystals only.

5. Consult crystal vendor data sheet.

Figure 22-1. RC vs. Frequency

Electrical Specifications

# 22.8 5V ADC Electrical Characteristics

| Characteristic <sup>(1)</sup>        | Symbol            | Min                    | Мах                    | Unit                        | Notes                                                                                           |

|--------------------------------------|-------------------|------------------------|------------------------|-----------------------------|-------------------------------------------------------------------------------------------------|

| Supply voltage                       | V <sub>DDA</sub>  | 4.5                    | 5.5                    | v                           | $V_{DDA}$ is an dedicated pin and should be tied to $V_{DD}$ on the PCB with proper decoupling. |

| Input range                          | V <sub>ADIN</sub> | 0                      | V <sub>DDA</sub>       | V                           | $V_{ADIN} \leq V_{DDA}$                                                                         |

| Resolution                           | B <sub>AD</sub>   | 10                     | 10                     | bits                        |                                                                                                 |

| Absolute accuracy                    | A <sub>AD</sub>   | —                      | ± 1.5                  | LSB                         | Includes quantization.<br>$\pm 0.5 \text{ LSB} = \pm 1 \text{ ADC step.}$                       |

| ADC internal clock                   | f <sub>ADIC</sub> | 500k                   | 1.048M                 | Hz                          | $t_{ADIC} = 1/f_{ADIC}$                                                                         |

| Conversion range                     | R <sub>AD</sub>   | V <sub>REFL</sub>      | V <sub>REFH</sub>      | V                           |                                                                                                 |

| ADC voltage reference high           | V <sub>REFH</sub> | _                      | V <sub>DDA</sub> + 0.1 | V                           |                                                                                                 |

| ADC voltage reference low            | V <sub>REFL</sub> | V <sub>SSA</sub> – 0.1 | _                      | v                           |                                                                                                 |

| Conversion time                      | t <sub>ADC</sub>  | 16                     | 17                     | t <sub>ADIC</sub><br>cycles |                                                                                                 |

| Sample time                          | t <sub>ADS</sub>  | 5                      | _                      | t <sub>ADIC</sub><br>cycles |                                                                                                 |

| Monotonicity                         | M <sub>AD</sub>   |                        | Guaranteed             |                             |                                                                                                 |

| Zero input reading                   | Z <sub>ADI</sub>  | 000                    | 001                    | HEX                         | V <sub>ADIN</sub> = V <sub>REFL</sub>                                                           |

| Full-scale reading                   | F <sub>ADI</sub>  | 3FD                    | 3FF                    | HEX                         | V <sub>ADIN</sub> = V <sub>REFH</sub>                                                           |

| Input capacitance                    | C <sub>ADI</sub>  | —                      | 20                     | pF                          | Not tested.                                                                                     |

| Input impedance                      | R <sub>ADI</sub>  | 20M                    | _                      | Ω                           |                                                                                                 |

| V <sub>REFH</sub> /V <sub>REFL</sub> | I <sub>VREF</sub> | _                      | 1.6                    | mA                          | Not tested.                                                                                     |

## Table 22-7. ADC Electrical Characteristics (5V)

1.  $V_{DD}$  = 4.5 to 5.5 Vdc,  $V_{SS}$  = 0 Vdc,  $T_A$  =  $T_L$  to  $T_H,$  unless otherwise noted.

# 22.10 CGM Electrical Specification

| Characteristic                    | Symbol            | Min  | Тур | Мах                                                      | Unit |

|-----------------------------------|-------------------|------|-----|----------------------------------------------------------|------|

| Reference frequency               | f <sub>RDV</sub>  | 1    | _   | 8                                                        | MHz  |

| Range nominal multiplies          | f <sub>NOM</sub>  | _    | 125 | _                                                        | kHz  |

| VCO center-of-range frequency     | f <sub>VRS</sub>  | 125k | _   | 40M                                                      | Hz   |

| VCO range linear range multiplier | L                 | 1    | —   | 255                                                      |      |

| VCO power-of-two-range multiplier | 2 <sup>E</sup>    | 1    | _   | 4                                                        |      |

| VCO multiply factor               | N                 | 1    | _   | 4095                                                     |      |

| VCO prescale multiplier           | 2 <sup>P</sup>    | 1    | _   | 8                                                        |      |

| Reference divider factor          | R                 | 1    | 1   | 15                                                       |      |

| VCO operating frequency           | f <sub>VCLK</sub> | 125k | —   | 40M                                                      | Hz   |

| Manual acquisition time           | t <sub>LOCK</sub> | _    | _   | 50                                                       | ms   |

| Automatic lock time               | t <sub>LOCK</sub> | _    | _   | 50                                                       | ms   |

| PLL jitter <sup>(1)</sup>         | fj                | 0    | _   | $f_{\text{RCLK}} \times 0.025\% \times 2^{\text{P}} N/4$ | Hz   |

#### Table 22-10. CGM Electrical Specifications

1. Deviation of average bus frequency over 2ms. N = VCO multiplier.

**Electrical Specifications**

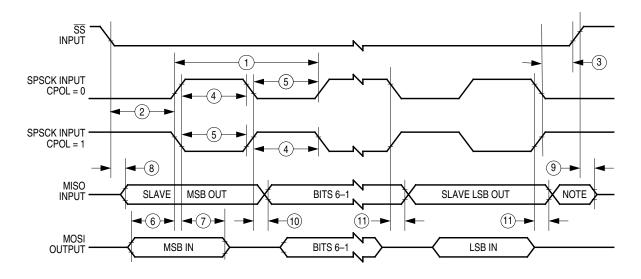

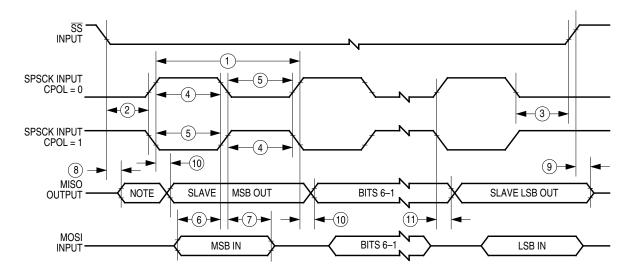

# 22.11 5V SPI Characteristics

| Diagram<br>Number <sup>(1)</sup> | Characteristic <sup>(2)</sup>                                        | Symbol                                       | Min                                              | Мах                                   | Unit                                 |

|----------------------------------|----------------------------------------------------------------------|----------------------------------------------|--------------------------------------------------|---------------------------------------|--------------------------------------|

|                                  | Operating frequency<br>Master<br>Slave                               | f <sub>OP(M)</sub><br>f <sub>OP(S)</sub>     | f <sub>OP</sub> /128<br>dc                       | f <sub>OP</sub> /2<br>f <sub>OP</sub> | MHz<br>MHz                           |

| 1                                | Cycle time<br>Master<br>Slave                                        | t <sub>CYC(M)</sub><br>t <sub>CYC(S)</sub>   | 2<br>1                                           | 128<br>—                              | t <sub>CYC</sub><br>t <sub>CYC</sub> |

| 2                                | Enable lead time                                                     | t <sub>Lead(S)</sub>                         | 1                                                |                                       | t <sub>CYC</sub>                     |

| 3                                | Enable lag time                                                      | t <sub>Lag(S)</sub>                          | 1                                                |                                       | t <sub>CYC</sub>                     |

| 4                                | Clock (SPSCK) high time<br>Master<br>Slave                           | t <sub>SCKH(M)</sub><br>t <sub>SCKH(S)</sub> | t <sub>CYC</sub> –25<br>1/2 t <sub>CYC</sub> –25 | 64 t <sub>CYC</sub>                   | ns<br>ns                             |

| 5                                | Clock (SPSCK) low time<br>Master<br>Slave                            | t <sub>SCKL(M)</sub><br>t <sub>SCKL(S)</sub> | t <sub>CYC</sub> –25<br>1/2 t <sub>CYC</sub> –25 | 64 t <sub>CYC</sub>                   | ns<br>ns                             |

| 6                                | Data setup time (inputs)<br>Master<br>Slave                          | t <sub>SU(M)</sub><br>t <sub>SU(S)</sub>     | 30<br>30                                         |                                       | ns<br>ns                             |

| 7                                | Data hold time (inputs)<br>Master<br>Slave                           | t <sub>H(M)</sub><br>t <sub>H(S)</sub>       | 30<br>30                                         |                                       | ns<br>ns                             |

| 8                                | Access time, slave <sup>(3)</sup><br>CPHA = 0<br>CPHA = 1            | t <sub>A(CP0)</sub><br>t <sub>A(CP1)</sub>   | 0<br>0                                           | 40<br>40                              | ns<br>ns                             |

| 9                                | Disable time, slave <sup>(4)</sup>                                   | t <sub>DIS(S)</sub>                          | _                                                | 40                                    | ns                                   |

| 10                               | Data valid time, after enable edge<br>Master<br>Slave <sup>(5)</sup> | t <sub>V(M)</sub><br>t <sub>V(S)</sub>       |                                                  | 50<br>50                              | ns<br>ns                             |

| 11                               | Data hold time, outputs, after enable edge<br>Master<br>Slave        | t <sub>HO(M)</sub><br>t <sub>HO(S)</sub>     | 0<br>0                                           |                                       | ns<br>ns                             |

| Table 22-11 | . SPI Characte | eristics (5V) |

|-------------|----------------|---------------|

|-------------|----------------|---------------|

Numbers refer to dimensions in Figure 22-3 and Figure 22-4.

All timing is shown with respect to 20% V<sub>DD</sub> and 70% V<sub>DD</sub>, unless noted; 100 pF load on all SPI pins.

Time to data active from high-impedance state

Hold time to high-impedance state

With 100 pF on all SPI pins

**Electrical Specifications**

Note: Not defined but normally MSB of character just received

a) SPI Slave Timing (CPHA = 0)

Note: Not defined but normally LSB of character previously transmitted

b) SPI Slave Timing (CPHA = 1)

#### Figure 22-4. SPI Slave Timing

MC68HC908AP A-Family Data Sheet, Rev. 3