Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Details                    |                                                                               |

|----------------------------|-------------------------------------------------------------------------------|

| Product Status             | Obsolete                                                                      |

| Core Processor             | Н8/300Н                                                                       |

| Core Size                  | 16-Bit                                                                        |

| Speed                      | 25MHz                                                                         |

| Connectivity               | SCI, SmartCard                                                                |

| Peripherals                | PWM, WDT                                                                      |

| Number of I/O              | 70                                                                            |

| Program Memory Size        | 128KB (128K x 8)                                                              |

| Program Memory Type        | FLASH                                                                         |

| EEPROM Size                | -                                                                             |

| RAM Size                   | 4K x 8                                                                        |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                     |

| Data Converters            | A/D 8x10b; D/A 2x8b                                                           |

| Oscillator Type            | Internal                                                                      |

| Operating Temperature      | -20°C ~ 75°C (TA)                                                             |

| Mounting Type              | Surface Mount                                                                 |

| Package / Case             | 100-BFQFP                                                                     |

| Supplier Device Package    | 100-QFP (14x14)                                                               |

| Purchase URL               | https://www.e-xfl.com/product-detail/renesas-electronics-america/df3024fbl25v |

|                            |                                                                               |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# Section 4 Exception Handling

## 4.1 Overview

#### 4.1.1 Exception Handling Types and Priority

As table 4.1 indicates, exception handling may be caused by a reset, interrupt, or trap instruction. Exception handling is prioritized as shown in table 4.1. If two or more exceptions occur simultaneously, they are accepted and processed in priority order. Trap instruction exceptions are accepted at all times in the program execution state.

Table 4.1

Exception Types and Priority

| Priority | Exception Type              | Start of Exception Handling                                                                                                |

|----------|-----------------------------|----------------------------------------------------------------------------------------------------------------------------|

| High     | Reset                       | Starts immediately after a low-to-high transition at the $\overline{\text{RES}}$ pin                                       |

| Ť        | Interrupt                   | Interrupt requests are handled when execution of the current instruction or handling of the current exception is completed |

| Low      | Trap instruction<br>(TRAPA) | Started by execution of a trap instruction (TRAPA)                                                                         |

#### 4.1.2 Exception Handling Operation

Exceptions originate from various sources. Trap instructions and interrupts are handled as follows.

- 1. The program counter (PC) and condition code register (CCR) are pushed onto the stack.

- 2. The CCR interrupt mask bit is set to 1.

- 3. A vector address corresponding to the exception source is generated, and program execution starts from that address.

Note: For a reset exception, steps 2 and 3 above are carried out.

## Renesas

# Section 7 I/O Ports

## 7.1 Overview

The H8/3024 Group has 10 input/output ports (ports 1, 2, 3, 4, 5, 6, 8, 9, A, and B) and one inputonly port (port 7). Table 7.1 summarizes the port functions. The pins in each port are multiplexed as shown in table 7.1.

Each port has a data direction register (DDR) for selecting input or output, and a data register (DR) for storing output data. In addition to these registers, ports 2, 4, and 5 have an input pull-up control register (PCR) for switching input pull-up transistors on and off.

Ports 1 to 6 and port 8 can drive one TTL load and a 90-pF capacitive load. Ports 9, A, and B can drive one TTL load and a 30-pF capacitive load. Ports 1 to 6 and 8 to B can drive a darlington pair. Ports 1, 2, and 5 can drive LEDs (with 10-mA current sink). Pins P8<sub>2</sub> to P8<sub>0</sub>, PA<sub>7</sub> to PA<sub>0</sub> have Schmitt-trigger input circuits.

For block diagrams of the ports see appendix C, I/O Port Block Diagrams.

| Port   | Description                                                                                                                | Pins                             |           | I            |                         | Single-Chip<br>Modes                                                                                                    |                                                                                                                           |                     |        |

|--------|----------------------------------------------------------------------------------------------------------------------------|----------------------------------|-----------|--------------|-------------------------|-------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------|---------------------|--------|

|        |                                                                                                                            |                                  | Mode 1    | Mode 2       | Mode 3                  | Mode 4                                                                                                                  | Mode 5                                                                                                                    | Mode 6              | Mode 7 |

| Port 1 | <ul> <li>8-bit I/O<br/>port</li> <li>Can drive<br/>LEDs</li> </ul>                                                         | $P1_7$ to $P1_0/A_7$ to $A_0$    | Address   | output pin   | s ( $A_7$ to $A_0$      | )                                                                                                                       | Address output<br>$(A_7 \text{ to } A_0)$ and<br>generic input<br>DDR = 0:<br>generic input<br>DDR = 1:<br>address output | Generic i<br>output | nput/  |

| Port 2 | <ul> <li>8-bit I/O<br/>port</li> <li>Built-in<br/>input<br/>pull-up<br/>transistors</li> <li>Can drive<br/>LEDs</li> </ul> | P27 to P20/<br>A15 to A8         | Address   | output pin   | s (A <sub>15</sub> to A | Address output<br>( $A_{15}$ to $A_8$ ) and<br>generic input<br>DDR = 0:<br>generic input<br>DDR = 1:<br>address output | Generic i<br>output                                                                                                       | nput/               |        |

| Port 3 | • 8-bit I/O<br>port                                                                                                        | $P3_7$ to $P3_0/D_{15}$ to $D_8$ | Data inpu | ut/output (I | 1                       | Generic input/<br>output                                                                                                |                                                                                                                           |                     |        |

Table 7.1Port Functions

## Renesas

#### Section 7 I/O Ports

| Port   | Description                                                                                                                | Pins                                                                                                           |                                                                                                                                                                                                                        |                          | Single-Chip<br>Modes              |           |                                                                                                                                     |                          |                                                                                                                    |  |  |  |  |  |

|--------|----------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------|-----------------------------------|-----------|-------------------------------------------------------------------------------------------------------------------------------------|--------------------------|--------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

|        | -                                                                                                                          |                                                                                                                | Mode 1                                                                                                                                                                                                                 | Mode 2                   | Mode 3                            | Mode 4    | Mode 5                                                                                                                              | Mode 6                   | Mode 7                                                                                                             |  |  |  |  |  |

| Port 4 | <ul> <li>8-bit I/O<br/>port</li> <li>Built-in<br/>input<br/>pull-up<br/>transistors</li> </ul>                             | P4 <sub>7</sub> to P4 <sub>0</sub> /<br>D <sub>7</sub> to D <sub>0</sub>                                       | input/out<br>8-bit bus                                                                                                                                                                                                 |                          | neric inpu                        |           | eneric                                                                                                                              | Generic input/<br>output |                                                                                                                    |  |  |  |  |  |

| Port 5 | <ul> <li>4-bit I/O<br/>port</li> <li>Built-in<br/>input<br/>pull-up<br/>transistors</li> <li>Can drive<br/>LEDs</li> </ul> | P5 <sub>3</sub> to P5 <sub>0</sub> /<br>A <sub>19</sub> to A <sub>16</sub>                                     | Address                                                                                                                                                                                                                | output (A                | <sub>9</sub> to A <sub>16</sub> ) |           | Address output<br>( $A_{19}$ to $A_{16}$ ) and<br>4-bit generic<br>input<br>DDR = 0:<br>generic input<br>DDR = 1:<br>address output |                          | input/                                                                                                             |  |  |  |  |  |

| Port 6 | • 8-bit I/O                                                                                                                | P6 <sub>7</sub> /φ                                                                                             | Clock output (                                                                                                                                                                                                         |                          |                                   |           |                                                                                                                                     |                          |                                                                                                                    |  |  |  |  |  |

|        | port                                                                                                                       | P6 <sub>6</sub> /LWR<br>P6₅/HWR<br>P6₄/RD<br>P6₃/AS                                                            | Bus cont                                                                                                                                                                                                               | Generic<br>output        |                                   |           |                                                                                                                                     |                          |                                                                                                                    |  |  |  |  |  |

|        |                                                                                                                            | P6 <sub>2</sub> /BACK<br>P6 <sub>1</sub> /BREQ<br>P6 <sub>0</sub> /WAIT                                        |                                                                                                                                                                                                                        | rol signal<br>generic ir | Generic<br>output                 | input/    |                                                                                                                                     |                          |                                                                                                                    |  |  |  |  |  |

| Port 7 | • 8-bit I/O<br>port                                                                                                        | P7 <sub>7</sub> /AN <sub>7</sub> /<br>DA <sub>1</sub><br>P7 <sub>6</sub> /AN <sub>6</sub> /<br>DA <sub>0</sub> | D/A conv                                                                                                                                                                                                               | verter, and              | generic i                         | nput      | er, analog output                                                                                                                   |                          | λ <sub>0</sub> ) from                                                                                              |  |  |  |  |  |

|        |                                                                                                                            | $P7_5$ to $P7_0/$<br>AN <sub>5</sub> to AN <sub>0</sub>                                                        | Analog ir                                                                                                                                                                                                              | nput (AN₅                | to AN <sub>0</sub> ) to           | A/D conve | erter, and generic                                                                                                                  | : input                  |                                                                                                                    |  |  |  |  |  |

| Port 8 |                                                                                                                            |                                                                                                                | $DDR = 0: generic input$ $DDR = 1 (reset value): \overline{CS}_0 output$ $DDR = 1: \overline{CS}_0 output$ $DDR = 1: \overline{CS}_0 output$ $DDR = 1: \overline{CS}_0 output$                                         |                          |                                   |           |                                                                                                                                     |                          | Generic input/<br>output                                                                                           |  |  |  |  |  |

|        | inputs                                                                                                                     | P8 <sub>3</sub> /IRQ <sub>3</sub> /<br>CS <sub>1</sub> /ADTRG                                                  | output $\overline{IRQ}_3$ input, $\overline{CS}_1$ output, external trigger input (ADTRG)       to A/D converter, and generic input       DDR = 0 (after reset): generic input       DDR = 1: $\overline{CS}_1$ output |                          |                                   |           |                                                                                                                                     |                          | $\overline{IRQ}_3$ input,<br>external trigger<br>input (ADTRG) to<br>A/D converter,<br>and generic<br>input/output |  |  |  |  |  |

7.3.2 Register Descriptions

Table 7.3 summarizes the registers of port 2.

#### Table 7.3 Port 2 Registers

|           |                                           |              |     | Initial Value |              |  |  |  |

|-----------|-------------------------------------------|--------------|-----|---------------|--------------|--|--|--|

| Address * | Name                                      | Abbreviation | R/W | Modes 1 to 4  | Modes 5 to 7 |  |  |  |

| H'EE001   | Port 2 data direction register            | P2DDR        | W   | H'FF          | H'00         |  |  |  |

| H'FFFD1   | Port 2 data register                      | P2DR         | R/W | H'00          | H'00         |  |  |  |

| H'EE03C   | Port 2 input pull-up MOS control register | P2PCR        | R/W | H'00          | H'00         |  |  |  |

Note: \* Lower 20 bits of the address in advanced mode.

Port 2 Data Direction Register (P2DDR):P2DDR is an 8-bit write-only register that can select input or output for each pin in port 2.

| Bit              |         | 7      | 6                   | 5      | 4                   | 3                   | 2                   | 1      | 0      |

|------------------|---------|--------|---------------------|--------|---------------------|---------------------|---------------------|--------|--------|

|                  | I       | P27DDR | P2 <sub>6</sub> DDR | P25DDR | P2 <sub>4</sub> DDR | P2 <sub>3</sub> DDR | P2 <sub>2</sub> DDR | P21DDR | P20DDR |

| Modes∫Initia     |         |        | 1                   | 1      | 1                   | 1                   | 1                   | 1      | 1      |

| 1 to 4 Read/W    | d/Write | » —    | —                   | —      | —                   | —                   | —                   | —      | —      |

| Modes∫Initial va | l value | e 0    | 0                   | 0      | 0                   | 0                   | 0                   | 0      | 0      |

| 5 to 7 Read      | d/Write | e W    | W                   | W      | W                   | W                   | W                   | W      | W      |

Port 2 data direction 7 to 0 These bits select input or output for port 2 pins

Modes 1 to 4 (Expanded Modes with On-Chip ROM Disabled)

P2DDR values are fixed at 1. Port 2 functions as an address bus.

Mode 5 (Expanded Modes with On-Chip ROM Enabled)

Following a reset, port 2 is an input port. A pin in port 2 becomes an address output pin if the corresponding P2DDR bit is set to 1, and a generic input port if this bit is cleared to 0. Modes 6 and 7 (Single-Chip Mode)

Port 2 functions as an input/output port. A pin in port 2 becomes an output port if the corresponding P2DDR bit is set to 1, and an input port if this bit is cleared to 0.

In modes 1 to 4, P2DDR bits are always read as 1, and cannot be modified.

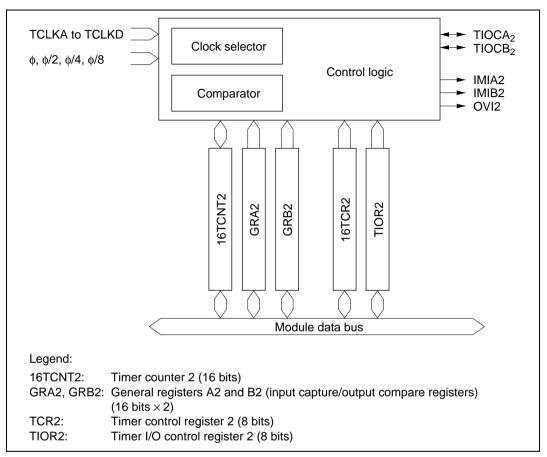

Block Diagram of Channel 2: Figure 8.3 is a block diagram of channel 2

#### Figure 8.3 Block Diagram of Channel 2

**Bit 1—Input Capture/Compare Match Flag B1 (IMFB1):** This status flag indicates GRB1 compare match or input capture events.

| Bit 1<br>IMFB1 | Description                                                                                   |

|----------------|-----------------------------------------------------------------------------------------------|

| 0              | [Clearing condition] (Initial value)                                                          |

|                | Read IMFB1 flag when IMFB1 =1, then write 0 in IMFB1 flag                                     |

| 1              | [Setting conditions]                                                                          |

|                | <ul> <li>16TCNT1 = GRB1 when GRB1 functions as an output compare register</li> </ul>          |

|                | <ul> <li>16TCNT1 value is transferred to GRB1 by an input capture signal when GRB1</li> </ul> |

|                | functions as an input capture register                                                        |

Bit 0—Input Capture/Compare Match Flag B0 (IMFB0): This status flag indicates GRB0 compare match or input capture events.

| Bit 0<br>IMFB0 | Description                                                                                   |  |  |  |  |  |  |  |  |  |  |  |

|----------------|-----------------------------------------------------------------------------------------------|--|--|--|--|--|--|--|--|--|--|--|

| 0              | [Clearing condition] (Initial value)                                                          |  |  |  |  |  |  |  |  |  |  |  |

|                | Read IMFB0 flag when IMFB0 =1, then write 0 in IMFB0 flag                                     |  |  |  |  |  |  |  |  |  |  |  |

| 1              | [Setting conditions]                                                                          |  |  |  |  |  |  |  |  |  |  |  |

|                | <ul> <li>16TCNT0 = GRB0 when GRB0 functions as an output compare register</li> </ul>          |  |  |  |  |  |  |  |  |  |  |  |

|                | <ul> <li>16TCNT0 value is transferred to GRB0 by an input capture signal when GRB0</li> </ul> |  |  |  |  |  |  |  |  |  |  |  |

|                | functions as an input capture register                                                        |  |  |  |  |  |  |  |  |  |  |  |

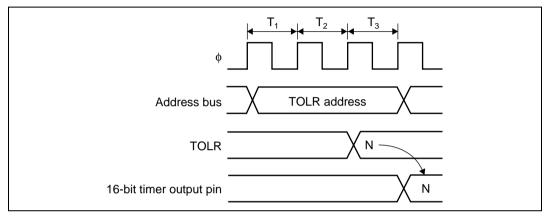

#### 8.4.6 16-Bit Timer Output Timing

The initial value of 16-bit timer output when a timer count operation begins can be specified arbitrarily by making a setting in TOLR.

Figure 8.32 shows the timing for setting the initial value with TOLR.

Only write to TOLR when the corresponding bit in TSTR is cleared to 0.

Figure 8.32 Timing for Setting 16-Bit Timer Output Level by Writing to TOLR

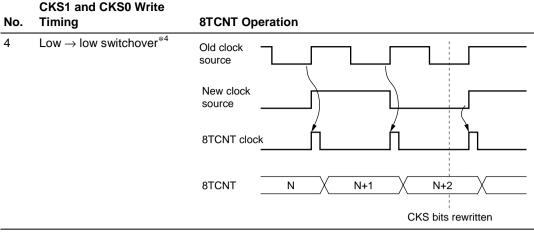

- Notes: 1. Including switchovers from the high level to the halted state, and from the halted state to the high level.

- 2. Including switchover from the halted state to the low level.

- 3. Including switchover from the low level to the halted state.

- 4. The switchover is regarded as a rising edge, causing 8TCNT to increment.

#### 12.2.3 Transmit Shift Register (TSR)

TSR is the register that transmits serial data.

The SCI loads transmit data from TDR to TSR, then transmits the data serially from the TxD pin, LSB (bit 0) first. After transmitting one data byte, the SCI automatically loads the next transmit data from TDR into TSR and starts transmitting it. If the TDRE flag is set to 1 in SSR, however, the SCI does not load the TDR contents into TSR. The CPU cannot read or write RSR directly.

#### 12.2.4 Transmit Data Register (TDR)

TDR is an 8-bit register that stores data for serial transmission.

| Bit           | 7   | 6   | 5   | 4   | 3   | 2   | 1   | 0   |

|---------------|-----|-----|-----|-----|-----|-----|-----|-----|

|               |     |     |     |     |     |     |     |     |

| Initial value | 1   | 1   | 1   | 1   | 1   | 1   | 1   | 1   |

| Read/Write    | R/W |

When the SCI detects that TSR is empty, it moves transmit data written in TDR from TDR into TSR and starts serial transmission. Continuous serial transmission is possible by writing the next transmit data in TDR during serial transmission from TSR.

The CPU can always read and write TDR. TDR is initialized to H'FF by a reset and in standby mode.

## Renesas

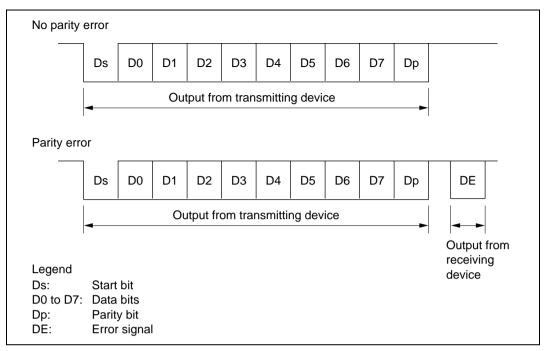

Figure 13.3 Smart Card Interface Data Format

The operating sequence is as follows.

- 1. When the data line is not in use it is in the high-impedance state, and is fixed high with a pullup resistor.

- 2. The transmitting device starts transfer of one frame of data. The data frame starts with a start bit (Ds, low-level), followed by 8 data bits (D0 to D7) and a parity bit (Dp).

- 3. With the smart card interface, the data line then returns to the high-impedance state. The data line is pulled high with a pull-up resistor.

- 4. The receiving device carries out a parity check. If there is no parity error and the data is received normally, the receiving device waits for reception of the next data. If a parity error occurs, however, the receiving device outputs an error signal (DE, low-level) to request retransmission of the data. After outputting the error signal for the prescribed length of time, the receiving device places the signal line in the high-impedance state again. The signal line is pulled high again by a pull-up resistor.

- 5. If the transmitting device does not receive an error signal, it proceeds to transmit the next data frame. If it receives an error signal, however, it returns to step 2 and transmits the same data again.

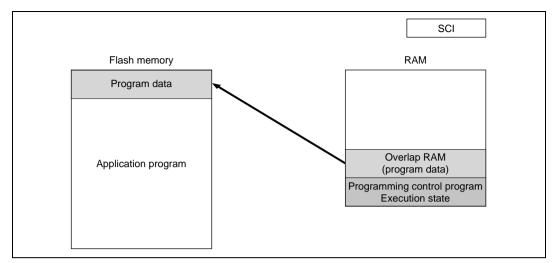

Figure 17.4 Writing Overlap RAM Data in User Program Mode

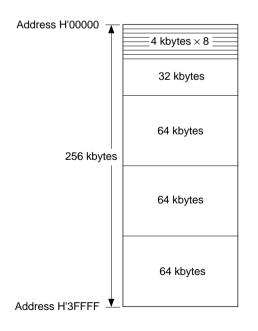

### 17.4.4 Block Configuration

The flash memory in the H8/3026F-ZTAT version is divided into three 64-kbyte blocks, one 32-kbyte block, and eight 4-kbyte blocks. Erasing can be carried out in block units.

#### Example of Flash Memory Block Area EB0 Overlapping

- 1. Set bits RAMS and RAM2 to RAM0 in RAMCR to 1,0, 0, 0, to overlap part of RAM onto the area (EB0) for which realtime programming is required.

- 2. Realtime programming is performed using the overlapping RAM.

- 3. After the program data has been confirmed, the RAMS bit is cleared, releasing RAM overlap.

- 4. The data written in the overlapping RAM is written into the flash memory space (EB0).

- Notes: 1. When the RAMS bit is set to 1, program/erase protection is enabled for all blocks regardless of the value of RAM2 to RAM0 (emulation protection). In this state, setting the P or E bit in FLMCR1 will not cause a transition to program mode or erase mode. When actually programming or erasing a flash memory area, the RAMS bit should be cleared to 0.

- 2. A RAM area cannot be erased by execution of software in accordance with the erase algorithm while flash memory emulation in RAM is being used.

- 3. Block area EB0 contains the vector table. When performing RAM emulation, the vector table is needed in the overlap RAM.

- 4. As in on-board programming mode, care is required when applying and releasing FWE to prevent erroneous programming or erasing. To prevent erroneous programming and erasing due to program runaway during FWE application, in particular, the watchdog timer should be set when the PSU, P, ESU, or E bit is set to 1 in FLMCR1, even while the emulation function is being used.

- 5. When the emulation function is used, NMI input is prohibited when the P bit or E bit is set to 1 in FLMCR1, in the same way as with normal programming and erasing.

The P and E bits are cleared by a reset (including a watchdog timer reset), in standby mode, when a high level is not being input to the FWE pin, or when the SWE bit in FLMCR1 is 0 while a high level is being input to the FWE pin.

## Renesas

#### 10. Do not touch the socket adapter or chip during programming.

Touching either of these can cause contact faults and write errors.

- 11. A wait time of 100 µs or more is necessary when performing a read after a transition to normal mode from program, erase, or verify mode.

- 12. Use byte access on the registers that control the flash memory (FLMCR1, FLMCR2, EBR1, EBR2, and RAMCR).

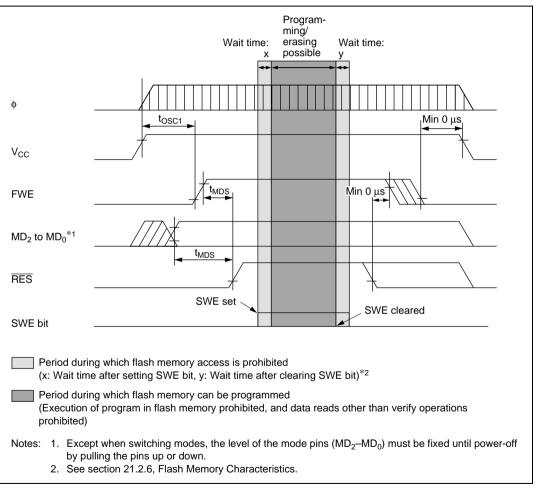

## Figure 17.16 Power-On/Off Timing (Boot Mode)

## 17.14 Notes when Converting the F-ZTAT Application Software to the Mask ROM Versions

Please note the following when converting the F-ZTAT application software to the mask ROM versions.

The values read from the internal registers for the flash ROM or the mask ROM version and F-ZTAT version differ as follows.

|          |     |       | Status                       |                                                 |  |  |  |  |  |  |

|----------|-----|-------|------------------------------|-------------------------------------------------|--|--|--|--|--|--|

| Register | Bit | Value | F-ZTAT Version               | Mask ROM Version                                |  |  |  |  |  |  |

| FLMCR    | FWE | 0     | Application software running | — (Is not read out)                             |  |  |  |  |  |  |

|          |     | 1     | Programming                  | Application software running (Always read as 1) |  |  |  |  |  |  |

Note: This difference applies to all the F-ZTAT versions and all the mask ROM versions that have different ROM size.

#### Notes on Use of Emulation in RAM:

1. Flash write enable (FWE) application and releasing

As in on-board program mode, care is required when applying and releasing FWE to prevent erroneous programming or erasing. To prevent erroneous programming and erasing due to program runaway during FWE application, in particular, the watchdog timer should be set when the PSU, P, ESU, or E bit is set to 1 in FLMCR1, even while the emulation function is being used. For details, see section 18.11, Flash Memory Programming and Erasing Precautions.

2. NMI input disabling conditions

When the emulation function is used, NMI input is disabled when the P bit or E bit is set to 1 in FLMCR1, in the same way as with normal programming and erasing.

The P and E bits are cleared by a reset (including a watchdog timer reset), in standby mode, when a high level is not being input to the FWE pin, or when the SWE bit in FLMCR1 is 0 while a high level is being input to the FWE pin.

- 3. When the RAMS bit is set to 1, program/erase protection is enabled for all blocks regardless of the value of RAM2 to RAM0 (emulation protection). In this state, setting the P or E bit in FLMCR1 will not cause a transition to program mode or erase mode. When actually programming or erasing a flash memory area, the RAMS bit should be cleared to 0.

- 4. A RAM area cannot be erased by execution of software in accordance with the erase algorithm while flash memory emulation in RAM is being used.

- 5. Block area EB0 contains the vector table. When performing RAM emulation, the vector table is needed in the overlap RAM.

# 18.9 NMI Input Disabling Conditions

All interrupts, including NMI input, should be disabled while flash memory is being programmed or erased (while the P bit or E bit is set in FLMCR1), and while the boot program is executing in boot mode<sup>\*1</sup>, to give priority to the program or erase operation. There are three reasons for this:

- 1. NMI input during programming or erasing might cause a violation of the programming or erasing algorithm, with the result that normal operation could not be assured.

- 2. In the NMI exception handling sequence during programming or erasing, the vector would not be read correctly<sup>\*2</sup>, possibly resulting in MCU runaway.

- 3. If NMI input occurred during boot program execution, it would not be possible to execute the normal boot mode sequence.

#### Table 21.15 Bus Timing

Conditions:  $V_{CC} = 3.0$  to 3.6 V,  $AV_{CC} = 3.0$  to 3.6 V,  $V_{REF} = 3.0$  to  $AV_{CC}$ ,  $V_{SS} = AV_{SS} = 0$  V,  $T_a = -20^{\circ}$ C to  $+75^{\circ}$ C (regular specifications),  $T_a = -40^{\circ}$ C to  $+85^{\circ}$ C (wide-range specifications)

| Item                         | Symbol             | Min                       | Мах                       | Unit | <b>Test Conditions</b> |

|------------------------------|--------------------|---------------------------|---------------------------|------|------------------------|

| Address delay time           | t <sub>AD</sub>    | _                         | 25                        | ns   | Figure 21.11,          |

| Address hold time            | t <sub>AH</sub>    | $0.5 t_{cyc} - 20$        | —                         | ns   | figure 21.12           |

| Read strobe delay time       | t <sub>RSD</sub>   |                           | 25                        | ns   | _                      |

| Address strobe delay time    | t <sub>ASD</sub>   |                           | 25                        | ns   | _                      |

| Write strobe delay time      | t <sub>WSD</sub>   | —                         | 25                        | ns   |                        |

| Strobe delay time            | t <sub>SD</sub>    | —                         | 25                        | ns   |                        |

| Write strobe pulse width 1   | t <sub>WSW1</sub>  | $1.0 t_{cyc} - 25$        | —                         | ns   |                        |

| Write strobe pulse width 2   | t <sub>WSW2</sub>  | 1.5 t <sub>cyc</sub> – 25 | —                         | ns   |                        |

| Address setup time 1         | t <sub>AS1</sub>   | $0.5 t_{\text{cyc}} - 20$ | —                         | ns   | _                      |

| Address setup time 2         | t <sub>AS2</sub>   | $1.0 t_{cyc} - 20$        | —                         | ns   | _                      |

| Read data setup time         | t <sub>RDS</sub>   | 40                        | —                         | ns   |                        |

| Read data hold time          | t <sub>RDH</sub>   | 0                         | —                         | ns   |                        |

| Write data delay time        | t <sub>WDD</sub>   | _                         | 35                        | ns   |                        |

| Write data setup time 1      | t <sub>WDS1</sub>  | $1.0 \ t_{cyc} - 30$      | —                         | ns   |                        |

| Write data setup time 2      | t <sub>WDS2</sub>  | $2.0 t_{\text{cyc}} - 30$ | —                         | ns   |                        |

| Write data hold time         | t <sub>WDH</sub>   | $0.5 t_{cyc} - 15$        | —                         | ns   | _                      |

| Read data access time 1      | t <sub>ACC1</sub>  | —                         | $2.0 \ t_{cyc} - 45$      | ns   | _                      |

| Read data access time 2      | t <sub>ACC2</sub>  | —                         | $3.0 t_{\text{cyc}} - 45$ | ns   |                        |

| Read data access time 3      | t <sub>ACC3</sub>  | —                         | 1.5 t <sub>cyc</sub> – 45 | ns   |                        |

| Read data access time 4      | t <sub>ACC4</sub>  | —                         | $2.5 t_{\text{cyc}} - 45$ | ns   |                        |

| Precharge time 1             | t <sub>PCH1</sub>  | 1.0 t <sub>cyc</sub> – 20 | —                         | ns   | _                      |

| Precharge time 2             | t <sub>PCH2</sub>  | $0.5 t_{cyc} - 20$        | —                         | ns   | _                      |

| Wait setup time              | t <sub>WTS</sub>   | 25                        | —                         | ns   | Figure 21.13           |

| Wait hold time               | t <sub>WTH</sub>   | 5                         | —                         | ns   | _                      |

| Bus request setup time       | t <sub>BRQS</sub>  | 25                        | —                         | ns   | Figure 21.14           |

| Bus acknowledge delay time 1 | t <sub>BACD1</sub> | _                         | 30                        | ns   | _                      |

| Bus acknowledge delay time 2 | t <sub>BACD2</sub> | _                         | 30                        | ns   | _                      |

| Bus-floating time            | t <sub>BZD</sub>   | _                         | 30                        | ns   |                        |

Note: In order to secure the address hold time relative to the rise of the RD strobe, address update mode 2 should be used. For details see section 6.3.5, Address Output Method.

|                   |                     |     |    | ddro |           | •           |     |          |        | ) |                                                                                                           |   |          |       |                |                |        | No. of<br>States <sup>*1</sup> |          |  |

|-------------------|---------------------|-----|----|------|-----------|-------------|-----|----------|--------|---|-----------------------------------------------------------------------------------------------------------|---|----------|-------|----------------|----------------|--------|--------------------------------|----------|--|

| Mnemonic          | <b>Operand Size</b> | #xx | Rn | @ERn | @(d, ERn) | @-ERn/@ERn+ | @aa | @(d, PC) | @ @ aa | 1 | Operation                                                                                                 | 1 | Con<br>H | ditio | on C<br>Z      | Code           | e<br>C | Normal                         | Advanced |  |

| DIVXU. W Rs, ERd  | W                   |     | 2  |      |           |             |     |          |        |   | $ERd32 \div Rs16 \rightarrow ERd32$<br>(Ed: remainder,<br>Rd: quotient)<br>(unsigned division)            | — | _        | (6)   | (7)            | _              | -      | 2                              | 22       |  |

| DIVXS. B Rs, Rd   | В                   |     | 4  |      |           |             |     |          |        |   | $Rd16 \div Rs8 \rightarrow Rd16$<br>(RdH: remainder,<br>RdL: quotient)<br>(signed division)               |   |          | (8)   | (7)            |                | _      | 16                             |          |  |

| DIVXS. W Rs, ERd  | W                   |     | 4  |      |           |             |     |          |        |   | ERd32 + Rs16 → ERd32<br>(Ed: remainder,<br>Rd: quotient)<br>(signed division)                             | _ |          | (8)   | (7)            | _              | _      | 24                             |          |  |

| CMP.B #xx:8, Rd   | В                   | 2   |    |      |           |             |     |          |        |   | Rd8–#xx:8                                                                                                 | — | ≎        | €     | €              | €              | €      | 2                              | 2        |  |

| CMP.B Rs, Rd      | В                   |     | 2  |      |           |             |     |          |        |   | Rd8–Rs8                                                                                                   | — | \$       | €     | €              | \$             | \$     | 2                              | 2        |  |

| CMP.W #xx:16, Rd  | W                   | 4   |    |      |           |             |     |          |        |   | Rd16–#xx:16                                                                                               | _ | (1)      | €     | €              | €              | €      | 4                              | 1        |  |

| CMP.W Rs, Rd      | W                   |     | 2  |      |           |             |     |          |        |   | Rd16–Rs16                                                                                                 | - | (1)      | €     | €              | €              | \$     | 2                              | 2        |  |

| CMP.L #xx:32, ERd | L                   | 6   |    |      |           |             |     |          |        |   | ERd32-#xx:32                                                                                              | — | (2)      | €     | €              | €              | €      | e                              | ;        |  |

| CMP.L ERs, ERd    | L                   |     | 2  |      |           |             |     |          |        |   | ERd32–ERs32                                                                                               | _ | (2)      | €     | $\updownarrow$ | $\updownarrow$ | €      | 2                              | 2        |  |

| NEG.B Rd          | В                   |     | 2  |      |           |             |     |          |        |   | $0Rd8 \rightarrow Rd8$                                                                                    | _ | \$       | €     | €              | $\updownarrow$ | €      | 2                              | 2        |  |

| NEG.W Rd          | W                   |     | 2  |      |           |             |     |          |        |   | $0-Rd16 \rightarrow Rd16$                                                                                 | — | ≎        | €     | €              | €              | €      | 2                              | 2        |  |

| NEG.L ERd         | L                   |     | 2  |      |           |             |     |          |        |   | $0-ERd32 \rightarrow ERd32$                                                                               | - | \$       | €     | €              | €              | \$     | 2                              | 2        |  |

| EXTU.W Rd         | w                   |     | 2  |      |           |             |     |          |        |   | $0 \rightarrow$ ( <bits 15="" 8="" to=""> of Rd16)</bits>                                                 | - | -        | 0     | \$             | 0              | -      | 2                              | 2        |  |

| EXTU.L ERd        | L                   |     | 2  |      |           |             |     |          |        |   | $0 \rightarrow$ ( <bits 16="" 31="" to=""> of ERd32)</bits>                                               | _ | -        | 0     | \$             | 0              | -      | 2                              | 2        |  |

| EXTS.W Rd         | w                   |     | 2  |      |           |             |     |          |        |   | ( <bit 7=""> of Rd16) <math>\rightarrow</math><br/>(<bits 15="" 8="" to=""> of Rd16)</bits></bit>         | — | _        | \$    | \$             | 0              | -      | 2                              | 2        |  |

| EXTS.L ERd        | L                   |     | 2  |      |           |             |     |          |        |   | ( <bit 15=""> of ERd32) <math>\rightarrow</math><br/>(<bits 16="" 31="" to=""> of<br/>ERd32)</bits></bit> | _ | _        | \$    | \$             | 0              | _      | 2                              | 2        |  |

| Instruction | Mnemonic          | Instruction<br>Fetch<br>I | Branch<br>Addr. Read<br>J | Stack<br>Operation<br>K | • | Word Data<br>Access<br>M | Internal<br>Operation<br>N |

|-------------|-------------------|---------------------------|---------------------------|-------------------------|---|--------------------------|----------------------------|

| ADD         | ADD.B #xx:8, Rd   | 1                         |                           |                         |   |                          |                            |

|             | ADD.B Rs, Rd      | 1                         |                           |                         |   |                          |                            |

|             | ADD.W #xx:16, Rd  | 2                         |                           |                         |   |                          |                            |

|             | ADD.W Rs, Rd      | 1                         |                           |                         |   |                          |                            |

|             | ADD.L #xx:32, ERd | 3                         |                           |                         |   |                          |                            |

|             | ADD.L ERs, ERd    | 1                         |                           |                         |   |                          |                            |

| ADDS        | ADDS #1/2/4, ERd  | 1                         |                           |                         |   |                          |                            |

| ADDX        | ADDX #xx:8, Rd    | 1                         |                           |                         |   |                          |                            |

|             | ADDX Rs, Rd       | 1                         |                           |                         |   |                          |                            |

| AND         | AND.B #xx:8, Rd   | 1                         |                           |                         |   |                          |                            |

|             | AND.B Rs, Rd      | 1                         |                           |                         |   |                          |                            |

|             | AND.W #xx:16, Rd  | 2                         |                           |                         |   |                          |                            |

|             | AND.W Rs, Rd      | 1                         |                           |                         |   |                          |                            |

|             | AND.L #xx:32, ERd | 3                         |                           |                         |   |                          |                            |

|             | AND.L ERs, ERd    | 2                         |                           |                         |   |                          |                            |

| ANDC        | ANDC #xx:8, CCR   | 1                         |                           |                         |   |                          |                            |

| BAND        | BAND #xx:3, Rd    | 1                         |                           |                         |   |                          |                            |

|             | BAND #xx:3, @ERd  | 2                         |                           |                         | 1 |                          |                            |

|             | BAND #xx:3, @aa:8 | 2                         |                           |                         | 1 |                          |                            |

| Bcc         | BRA d:8 (BT d:8)  | 2                         |                           |                         |   |                          |                            |

|             | BRN d:8 (BF d:8)  | 2                         |                           |                         |   |                          |                            |

|             | BHI d:8           | 2                         |                           |                         |   |                          |                            |

|             | BLS d:8           | 2                         |                           |                         |   |                          |                            |

|             | BCC d:8 (BHS d:8) | 2                         |                           |                         |   |                          |                            |

|             | BCS d:8 (BLO d:8) | 2                         |                           |                         |   |                          |                            |

|             | BNE d:8           | 2                         |                           |                         |   |                          |                            |

|             | BEQ d:8           | 2                         |                           |                         |   |                          |                            |

|             | BVC d:8           | 2                         |                           |                         |   |                          |                            |

|             | BVS d:8           | 2                         |                           |                         |   |                          |                            |

|             | BPL d:8           | 2                         |                           |                         |   |                          |                            |

|             | BMI d:8           | 2                         |                           |                         |   |                          |                            |

|             | BGE d:8           | 2                         |                           |                         |   |                          |                            |

|             | BLT d:8           | 2<br>2                    |                           |                         |   |                          |                            |

|             | BGT d:8           |                           |                           |                         |   |                          |                            |

|             | BLE d:8           | 2                         |                           |                         |   |                          |                            |

Table A.4

Number of Cycles per Instruction

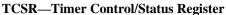

#### H'FFF8C

WDT

TCNT changes from H'FF to H'00

Note: \* Only 0 can be written to clear the flag.

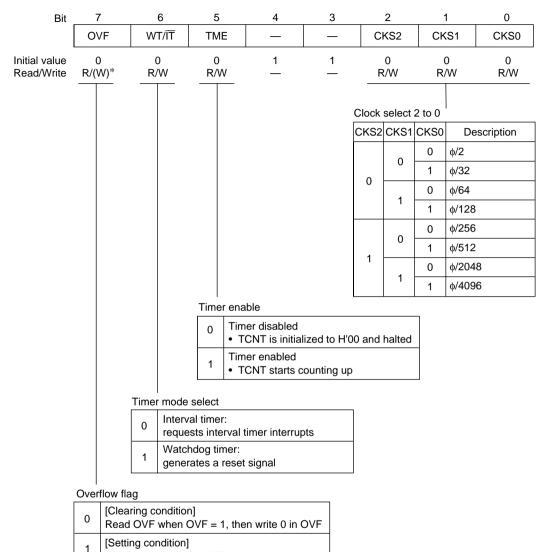

| 0 | DA1 analog output is disabled                              |

|---|------------------------------------------------------------|

| 1 | Channel-1 D/A conversion and DA1 analog output are enabled |