Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Obsolete                                                                      |

|----------------------------|-------------------------------------------------------------------------------|

| Core Processor             | H8/300H                                                                       |

| Core Size                  | 16-Bit                                                                        |

| Speed                      | 25MHz                                                                         |

| Connectivity               | SCI, SmartCard                                                                |

| Peripherals                | PWM, WDT                                                                      |

| Number of I/O              | 70                                                                            |

| Program Memory Size        | 256KB (256K x 8)                                                              |

| Program Memory Type        | FLASH                                                                         |

| EEPROM Size                | -                                                                             |

| RAM Size                   | 8K x 8                                                                        |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                     |

| Data Converters            | A/D 8x10b; D/A 2x8b                                                           |

| Oscillator Type            | Internal                                                                      |

| Operating Temperature      | -20°C ~ 75°C (TA)                                                             |

| Mounting Type              | Surface Mount                                                                 |

| Package / Case             | 100-TQFP                                                                      |

| Supplier Device Package    | -                                                                             |

| Purchase URL               | https://www.e-xfl.com/product-detail/renesas-electronics-america/df3026xbl25v |

|                            |                                                                               |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# Section 1 Overview

# 1.1 Overview

The H8/3024 Group is a series of microcontrollers (MCUs) that integrate system supporting functions together with an H8/300H CPU core having an original Renesas Technology architecture.

The H8/300H CPU has a 32-bit internal architecture with sixteen 16-bit general registers, and a concise, optimized instruction set designed for speed. It can address a 16-Mbyte linear address space. Its instruction set is upward-compatible at the object-code level with the H8/300 CPU, enabling easy porting of software from the H8/300 Series.

The on-chip system supporting functions include ROM, RAM, a 16-bit timer, an 8-bit timer, a programmable timing pattern controller (TPC), a watchdog timer (WDT), a serial communication interface (SCI), an A/D converter, a D/A converter, I/O ports, and other facilities.

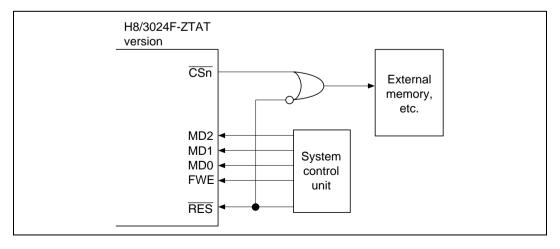

The four members of the H8/3024 Group are the H8/3024F-ZTAT, H8/3026F-ZTAT, H8/3024 (mask ROM version), and H8/3026 (mask ROM version).

Seven MCU operating modes offer a choice of bus width and address space size. The modes (modes 1 to 7) include two single-chip modes and five expanded modes.

In addition to its mask ROM versions, the H8/3024 Group has F-ZTAT<sup>TM\*</sup> versions with on-chip flash memory that allows programs to be freely rewritten by the user. This version enables users to respond quickly and flexibly to changing application specifications, growing production volumes, and other conditions.

Table 1.1 summarizes the features of the H8/3024 Group.

Note: \* F-ZTAT<sup>TM</sup> (Flexible ZTAT) is a trademark of Renesas Technology Corp.

### Interrupt Priority Register A (IPRA)

IPRA is an 8-bit readable/writable register in which interrupt priority levels can be set.

| Bit           | 7           | 6             | 5                                    | 4                                                                   | 3                                                                                                                  | 2                                                                                                                                       | 1                                                                                                                                                                          | 0                                                                                                                                                                                    |

|---------------|-------------|---------------|--------------------------------------|---------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|               | IPRA7       | IPRA6         | IPRA5                                | IPRA4                                                               | IPRA3                                                                                                              | IPRA2                                                                                                                                   | IPRA1                                                                                                                                                                      | IPRA0                                                                                                                                                                                |

| Initial value | 0           | 0             | 0                                    | 0                                                                   | 0                                                                                                                  | 0                                                                                                                                       | 0                                                                                                                                                                          | 0                                                                                                                                                                                    |

| Read/Write    | R/W         | R/W           | R/W                                  | R/W                                                                 | R/W                                                                                                                | R/W                                                                                                                                     | R/W                                                                                                                                                                        | R/W                                                                                                                                                                                  |

|               |             | Priority le   | Priority le<br>Selects th<br>evel A6 | Priority le<br>Selects th<br>interrupt r<br>svel A5<br>e priority l | P<br>S<br>16<br>re<br>Priority le<br>Selects th<br>and A/D c<br>evel A4<br>re priority l<br>equests<br>evel of IR0 | Pr<br>Se<br>of<br>int<br>riority lev<br>elects the<br>6-bit timer<br>equests<br>evel A3<br>e priority le<br>onverter in<br>level of IRC | Fiority level<br>elects the p<br>16-bit time<br>terrupt req<br>el A2<br>priority level<br>channel 0<br>evel of WE<br>aterrupt red<br>24 and IR4<br>Q <sub>3</sub> interrup | Priority<br>evel A0<br>Selects the<br>riority level<br>f 16-bit timer<br>hannel 2<br>hterrupt<br>equests<br>el A1<br>priority level<br>er channel 1<br>juests<br>vel of<br>interrupt |

|               | Priority le | vel A7        |                                      |                                                                     |                                                                                                                    |                                                                                                                                         |                                                                                                                                                                            |                                                                                                                                                                                      |

|               | -           | e priority le | evel of IRC                          | Q <sub>0</sub> interrup                                             | ot requests                                                                                                        | 6                                                                                                                                       |                                                                                                                                                                            |                                                                                                                                                                                      |

IPRA is initialized to H'00 by a reset and in hardware standby mode.

#### Pin Pin Functions and Selection Method

PA<sub>6</sub>/TP<sub>6</sub>/ Bit PWM2 in TMDR, bits IOA2 to IOA0 in TIOR2, bit NDER6 in NDERA, bit A21E in TIOCA<sub>2</sub>/A<sub>21</sub> BRCR, and bit PA<sub>6</sub>DDR select the pin function as follows.

| A21E                               |                           |                          | 0                                                   |                                             |                           |

|------------------------------------|---------------------------|--------------------------|-----------------------------------------------------|---------------------------------------------|---------------------------|

| 16-bit timer<br>channel 2 settings | (1) in table below        | (2) in table below       |                                                     |                                             | _                         |

| PA <sub>6</sub> DDR                | —                         | 0                        | 1                                                   | 1                                           | _                         |

| NDER6                              | —                         | _                        | 0                                                   | 1                                           | _                         |

| Pin function                       | TIOCA <sub>2</sub> output | PA <sub>6</sub><br>input | PA <sub>6</sub><br>output<br>IOCA <sub>2</sub> inpu | TP <sub>6</sub><br>output<br>t <sup>*</sup> | A <sub>21</sub><br>output |

Note: \* TIOCA<sub>2</sub> input when IOA2 = 1.

| 16-bit timer channel 2 settings | (2) | (* | 1) | (2) | (1) |

|---------------------------------|-----|----|----|-----|-----|

| PWM2                            | 0   |    |    | 1   |     |

| IOA2                            | 0   |    |    | 1   | _   |

| IOA1                            | 0   | 0  | 1  | _   | _   |

| IOA0                            | 0   | 1  | —  |     |     |

$\begin{array}{ll} PA_5/TP_5/ & \text{Bit PWM1 in TMDR, bits IOB2 to IOB0 in TIOR1, bit NDER5 in NDERA, bit A22E in }\\ TIOCB_1/A_{22} & \text{BRCR, and bit PA}_5\text{DDR select the pin function as follows.} \end{array}$

| A22E                               |                           | 0                                     |                             |                                 |                           |

|------------------------------------|---------------------------|---------------------------------------|-----------------------------|---------------------------------|---------------------------|

| 16-bit timer<br>channel 1 settings | (1) in table below        | (1) in table below (2) in table below |                             |                                 |                           |

| PA₅DDR                             | —                         | 0                                     | 1                           | 1                               |                           |

| NDER5                              | —                         | _                                     | 0                           | 1                               |                           |

| Pin function                       | TIOCB <sub>1</sub> output | PA₅<br>input<br>T                     | PA₅<br>output<br>IOCB₁ inpu | TP₅<br>output<br>t <sup>*</sup> | A <sub>22</sub><br>output |

Note: \* TIOCB<sub>1</sub> input when IOB2 = 1 and PWM1 = 0.

| 16-bit timer<br>channel 1 settings | (2) | (' | 1) | (2) |

|------------------------------------|-----|----|----|-----|

| IOB2                               | (   | 1  |    |     |

| IOB1                               | 0   | 0  | 1  | —   |

| IOB0                               | 0   | 1  | —  | —   |

Rev. 2.00 Sep 20, 2005 page 194 of 800 REJ09B0260-0200

| Pin                                                                 | Pin Functions and Selection Method                                                                                                                                                                                                  |                           |              |    |                                        |                           |                           |  |  |  |

|---------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------|--------------|----|----------------------------------------|---------------------------|---------------------------|--|--|--|

| PA <sub>2</sub> /TP <sub>2</sub> /<br>TIOCA <sub>0</sub> /<br>TCLKC | Bit PWM0 in TMDR, bits IOA2 to IOA0 in TIOR0, bits TPSC2 to TPSC0 in 16TCR2 to 16TCR0 of the 16-bit timer, bits CKS2 to CKS0 in 8TCR0 of the 8-bit timer, bit NDER2 in NDERA, and bit $PA_2DDR$ select the pin function as follows. |                           |              |    |                                        |                           |                           |  |  |  |

|                                                                     | 16-bit timer<br>channel 0 settings                                                                                                                                                                                                  | (1)                       | in table bel | ow | (2)                                    | ) in table be             | low                       |  |  |  |

|                                                                     | PA <sub>2</sub> DDR                                                                                                                                                                                                                 |                           | —            |    | 0                                      | 1                         | 1                         |  |  |  |

|                                                                     | NDER2                                                                                                                                                                                                                               |                           | —            |    | —                                      | 0                         | 1                         |  |  |  |

|                                                                     | Pin function                                                                                                                                                                                                                        | TIOCA <sub>0</sub> output |              |    | PA <sub>2</sub><br>input               | PA <sub>2</sub><br>output | TP <sub>2</sub><br>output |  |  |  |

|                                                                     |                                                                                                                                                                                                                                     |                           |              |    | TIOCA <sub>0</sub> input <sup>*1</sup> |                           |                           |  |  |  |

|                                                                     | -                                                                                                                                                                                                                                   | TCLKC input <sup>*2</sup> |              |    |                                        |                           |                           |  |  |  |

|                                                                     | <ul> <li>Notes: 1. TIOCA<sub>0</sub> input when IOA2 = 1.</li> <li>2. TCLKC input when TPSC2 = TPSC1 = 1 and TPSC0 = 0 in any of 16TCR2 to 16TCR0, or bits CKS2 to CKS0 in 8TCR0 are as shown in (3) in the table below.</li> </ul> |                           |              |    |                                        |                           |                           |  |  |  |

|                                                                     | 16-bit timer<br>channel 0 settings                                                                                                                                                                                                  | (2)                       | ) (1)        |    | (2)                                    | (1)                       |                           |  |  |  |

|                                                                     | PWM0                                                                                                                                                                                                                                |                           | (            | )  |                                        |                           | 1                         |  |  |  |

|                                                                     | IOA2                                                                                                                                                                                                                                |                           | 0            |    | 1                                      |                           |                           |  |  |  |

|                                                                     | IOA1                                                                                                                                                                                                                                | 0                         | 0            | 1  | _                                      | -                         | _                         |  |  |  |

|                                                                     | IOA0                                                                                                                                                                                                                                | 0                         | 1            |    |                                        |                           |                           |  |  |  |

| 8-bit timer<br>channel 0 settings | (4 | 4) |   | (3) |  |

|-----------------------------------|----|----|---|-----|--|

| CKS2                              | 0  | 1  |   |     |  |

| CKS1                              |    | (  | 0 | 1   |  |

| CKS0                              |    | 0  | 1 | —   |  |

#### 7.12.2 Register Descriptions

Table 7.22 summarizes the registers of port B.

#### Table 7.22 Port B Registers

| Address* | Name                           | Abbreviation | R/W | Initial Value |

|----------|--------------------------------|--------------|-----|---------------|

| H'EE00A  | Port B data direction register | PBDDR        | W   | H'00          |

| H'FFFDA  | Port B data register           | PBDR         | R/W | H'00          |

Note: \* Lower 20 bits of the address in advanced mode.

**Port B Data Direction Register (PBDDR):** PBDDR is an 8-bit write-only register that can select input or output for each pin in port B. When pins are used for TPC output, the corresponding PBDDR bits must also be set.

| Bit           | 7      | 6                   | 5         | 4                   | 3                   | 2                   | 1                   | 0                   |

|---------------|--------|---------------------|-----------|---------------------|---------------------|---------------------|---------------------|---------------------|

|               | PB7DDR | PB <sub>6</sub> DDR | $PB_5DDR$ | PB <sub>4</sub> DDR | PB <sub>3</sub> DDR | PB <sub>2</sub> DDR | PB <sub>1</sub> DDR | PB <sub>0</sub> DDR |

| Initial value | 0      | 0                   | 0         | 0                   | 0                   | 0                   | 0                   | 0                   |

| Read/Write    | W      | W                   | W         | W                   | W                   | W                   | W                   | W                   |

|               |        |                     |           |                     |                     |                     |                     |                     |

Port B data direction 7 to 0 These bits select input or output for port B pins

The pin functions that can be selected for port B differ between modes 1 to 5, and modes 6 and 7. For the method of selecting the pin functions, see tables 7.23 and 7.24.

When port B functions as an input/output port, a pin in port B becomes an output port if the corresponding PBDDR bit is set to 1, and an input port if this bit is cleared to 0.

PBDDR is a write-only register. Its value cannot be read. All bits return 1 when read.

PBDDR is initialized to H'00 by a reset and in hardware standby mode. In software standby mode it retains its previous setting. Therefore, if a transition is made to software standby mode while port B is functioning as an input/output port and a PBDDR bit is set to 1, the corresponding pin maintains its output state.

# Section 9 8-Bit Timers

## 9.1 Overview

The H8/3024 Group has a built-in 8-bit timer module with four channels (TMR0, TMR1, TMR2, and TMR3), based on 8-bit counters. Each channel has an 8-bit timer counter (8TCNT) and two 8-bit time constant registers (TCORA and TCORB) that are constantly compared with the 8TCNT value to detect compare match events. The timers can be used as multifunctional timers in a variety of applications, including the generation of a rectangular-wave output with an arbitrary duty cycle.

#### 9.1.1 Features

The features of the 8-bit timer module are listed below.

• Selection of four clock sources

The counters can be driven by one of three internal clock signals ( $\phi/8$ ,  $\phi/64$ , or  $\phi/8192$ ) or an external clock input (enabling use as an external event counter).

- Selection of three ways to clear the counters The counters can be cleared on compare match A or B, or input capture B.

- Timer output controlled by two compare match signals

The timer output signal in each channel is controlled by two independent compare match signals, enabling the timer to generate output waveforms with an arbitrary duty cycle or PWM output.

- A/D converter can be activated by a compare match

- Two channels can be cascaded

- Channels 0 and 1 can be operated as the upper and lower halves of a 16-bit timer (16-bit count mode).

- Channels 2 and 3 can be operated as the upper and lower halves of a 16-bit timer (16-bit count mode).

- Channel 1 can count channel 0 compare match events (compare match count mode).

- Channel 3 can count channel 2 compare match events (compare match count mode).

- Input capture function can be set

8-bit or 16-bit input capture operation is available.

| Bits 3 and 2—Group 1 Compare Match Select 1 and 0 (G1CMS1, G1CMS0): These bits        |

|---------------------------------------------------------------------------------------|

| select the compare match event that triggers TPC output group 1 ( $TP_7$ to $TP_4$ ). |

| Bit 3<br>G1CMS1 | Bit 2<br>G1CMS0 | Description                                                                                                      |                   |

|-----------------|-----------------|------------------------------------------------------------------------------------------------------------------|-------------------|

| 0               | 0               | TPC output group 1 (TP <sub>7</sub> to TP <sub>4</sub> ) is triggered by compare timer channel 0                 | e match in 16-bit |

|                 | 1               | TPC output group 1 (TP <sub>7</sub> to TP <sub>4</sub> ) is triggered by compare timer channel 1                 | e match in 16-bit |

| 1               | 0               | TPC output group 1 (TP <sub>7</sub> to TP <sub>4</sub> ) is triggered by compare timer channel 2                 | e match in 16-bit |

|                 | 1               | TPC output group 1 (TP <sub>7</sub> to TP <sub>4</sub> ) is triggered by compare match in 16-bit timer channel 2 | (Initial value)   |

**Bits 1 and 0—Group 0 Compare Match Select 1 and 0 (G0CMS1, G0CMS0):** These bits select the compare match event that triggers TPC output group 0 (TP<sub>3</sub> to TP<sub>0</sub>).

| Bit 1<br>G0CMS1 | Bit 0<br>G0CMS0 | Description                                                                                      |

|-----------------|-----------------|--------------------------------------------------------------------------------------------------|

| 0               | 0               | TPC output group 0 (TP $_3$ to TP $_0$ ) is triggered by compare match in 16-bit timer channel 0 |

|                 | 1               | TPC output group 0 (TP $_3$ to TP $_0$ ) is triggered by compare match in 16-bit timer channel 1 |

| 1               | 0               | TPC output group 0 (TP $_3$ to TP $_0$ ) is triggered by compare match in 16-bit timer channel 2 |

|                 | 1               | $\begin{array}{llllllllllllllllllllllllllllllllllll$                                             |

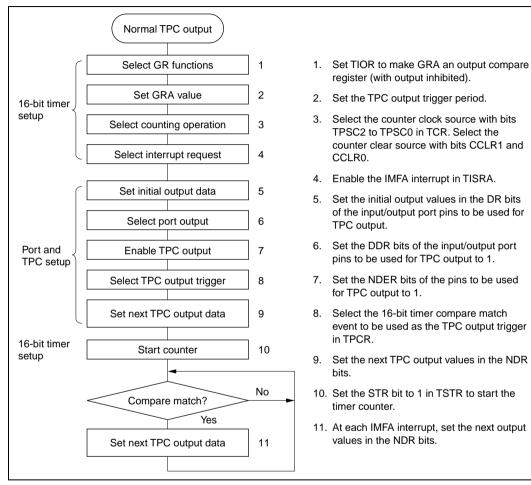

### 10.3.3 Normal TPC Output

Sample Setup Procedure for Normal TPC Output: Figure 10.4 shows a sample procedure for setting up normal TPC output.

Figure 10.4 Setup Procedure for Normal TPC Output (Example)

**Bit 4—Parity Mode (O**/ $\overline{E}$ ): Specifies whether even parity or odd parity is used for parity addition and checking. The O/ $\overline{E}$  bit setting is only valid when the PE bit is set to 1, enabling parity bit addition and checking, in asynchronous mode. The O/ $\overline{E}$  bit setting is ignored in synchronous mode, or when parity addition and checking is disabled in asynchronous mode.

| Bit 4    |                                      |                                                                                                                                                |

|----------|--------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------|

| O/E      | Description                          |                                                                                                                                                |

| 0        | Even parity <sup>*1</sup>            | (Initial value)                                                                                                                                |

| 1        | Odd parity <sup>*2</sup>             |                                                                                                                                                |

| Notes: 1 | number of 1s in the transmitted char | rity bit added to transmit data makes an even<br>acter and parity bit combined. Receive data must<br>ceived character and parity bit combined. |

| 2        |                                      | ty bit added to transmit data makes an odd number<br>d parity bit combined. Receive data must have an<br>aracter and parity bit combined.      |

**Bit 3—Stop Bit Length (STOP):** Selects one or two stop bits in asynchronous mode. This setting is used only in asynchronous mode. In synchronous mod no stop bit is added, so the STOP bit setting is ignored.

| Bit 3<br>STOP | Description                           |                                             |

|---------------|---------------------------------------|---------------------------------------------|

| 0             | 1 stop bit <sup>*1</sup>              | (Initial value)                             |

| 1             | 2 stop bits <sup>*2</sup>             |                                             |

| Notes: 1      | . One stop bit (with value 1) is adde | d to the end of each transmitted character. |

s: 1. One stop bit (with value 1) is added to the end of each transmitted character.

2. Two stop bits (with value 1) are added to the end of each transmitted character.

In receiving, only the first stop bit is checked, regardless of the STOP bit setting. If the second stop bit is 1, it is treated as a stop bit. If the second stop bit is 0, it is treated as the start bit of the next incoming character.

### 13.3.6 Transmitting and Receiving Data

**Initialization:** Before transmitting or receiving data, the smart card interface must be initialized as described below. Initialization is also necessary when switching from transmit mode to receive mode, or vice versa.

- 1. Clear the TE and RE bits to 0 in the serial control register (SCR).

- 2. Clear error flags ERS, PER, and ORER to 0 in the serial status register (SSR).

- 3. Set the parity bit  $(O/\overline{E})$  and baud rate generator select bits (CKS1 and CKS0) in the serial mode register (SMR). Clear the C/ $\overline{A}$ , CHR, and MP bits to 0, and set the STOP and PE bits to 1.

- Set the SMIF, SDIR, and SINV bits in the smart card mode register (SCMR).

When the SMIF bit is set to 1, the TxD pin and RxD pin are both switched from port to SCI pin functions and go to the high-impedance state.

- 5. Set a value corresponding to the desired bit rate in the bit rate register (BRR).

- 6. Set the CKE0 bit in SCR. Clear the TIE, RIE, TE, RE, MPIE, TEIE, and CKE1 bits to 0. If the CKE0 bit is set to 1, the clock is output from the SCK pin.

- 7. Wait at least one bit interval, then set the TIE, RIE, TE, and RE bits in SCR. Do not set the TE bit and RE bit at the same time, except for self-diagnosis.

**Transmitting Serial Data:** As data transmission in smart card mode involves error signal sampling and retransmission processing, the processing procedure is different from that for the normal SCI. Figure 13.5 shows a sample transmission processing flowchart.

- 1. Perform smart card interface mode initialization as described in Initialization above.

- 2. Check that the ERS error flag is cleared to 0 in SSR.

- 3. Repeat steps 2 and 3 until it can be confirmed that the TEND flag is set to 1 in SSR.

- 4. Write the transmit data in TDR, clear the TDRE flag to 0, and perform the transmit operation. The TEND flag is cleared to 0.

- 5. To continue transmitting data, go back to step 2.

- 6. To end transmission, clear the TE bit to 0.

The above processing may include interrupt handling.

If transmission ends and the TEND flag is set to 1 while the TIE bit is set to 1 and interrupt requests are enabled, a transmit-data-empty interrupt (TXI) will be requested. If an error occurs in transmission and the ERS flag is set to 1 while the RIE bit is set to 1 and interrupt requests are enabled, a transmit/receive-error interrupt (ERI) will be requested.

**Bit 1—Erase Mode (E):** Selects erase mode transition or clearing. (Do not set the SWE, ESU, PSU, EV, PV, or P bit at the same time.)

| Bit 1 |                                            |                 |

|-------|--------------------------------------------|-----------------|

| Е     | Description                                |                 |

| 0     | Erase mode cleared                         | (Initial value) |

| 1     | Transition to erase mode                   |                 |

|       | [Setting condition]                        |                 |

|       | When $FWE = 1$ , $SWE = 1$ , and $ESU = 1$ |                 |

Note: Do not access the flash memory while the E bit is set.

**Bit 0—Program (P):** Selects program mode transition or clearing. (Do not set the SWE, ESU, PSU, EV, PV, or E bit at the same time.)

| Bit 0 |                                            |                 |

|-------|--------------------------------------------|-----------------|

| Р     | Description                                |                 |

| 0     | Program mode cleared                       | (Initial value) |

| 1     | Transition to program mode                 |                 |

|       | [Setting condition]                        |                 |

|       | When $FWE = 1$ , $SWE = 1$ , and $PSU = 1$ |                 |

Note: Do not access the flash memory while the P bit is set.

#### 18.3.2 Flash Memory Control Register 2 (FLMCR2)

| Bit           | 7    | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

|---------------|------|---|---|---|---|---|---|---|

|               | FLER | _ |   | — | — | — | — | — |

| Initial value | 0    | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

| Read/Write    | R    | R | R | R | R | R | R | R |

FLMCR2 is an 8-bit register used for flash memory operating mode control. FLMCR2 is initialized to H'00 by a reset, and in hardware standby mode and software standby mode. When the on-chip flash memory is disabled, a read will return H'00.

Note: FLMCR2 is a read-only register, and should not be written to.

(BRR). The transmit data output pin,  $TxD_1$ , goes to the high-level output state (P9<sub>1</sub>DDR = 1 in P9DDR, P9<sub>1</sub>DR = 1 in P9DR).

The contents of the CPU's internal general registers are undefined at this time, so these registers must be initialized immediately after branching to the user program. In particular, since the stack pointer (SP) is used implicitly in subroutine calls, etc., a stack area must be specified for use by the user program.

The initial values of other on-chip registers are not changed.

- 6. Boot mode can be entered by setting pins  $MD_0$  to  $MD_2$  and FWE in accordance with the mode setting conditions shown in table 18.6, and then executing a reset-start.

- a. When switching from boot mode to normal mode, the boot mode state within the chip must first be cleared by reset input via the  $\overline{\text{RES}}$  pin<sup>\*1</sup>. The  $\overline{\text{RES}}$  pin must be held low for at least 20 system clock cycles.<sup>\*2</sup>

- b. Do not change the input levels of the mode pins  $(MD_2 \text{ to } MD_0)$  or the FWE pin in boot mode. To change the mode, the  $\overline{RES}$  pin must first be driven low to set the reset state. Also, if a watchdog timer reset occurs in the boot mode state, the MCU's internal state will not be cleared, and the on-chip boot program will be restarted regardless of the mode pin states.

- c. The FWE pin must not be driven low while the boot program is running or flash memory is being programmed or erased.<sup>\*3</sup>

- 7. If the mode pin input levels are changed (for example, from low to high) during a reset, the state of ports with multiplexed address functions and bus control output signals (CSn, AS, RD, LWR, HWR) may also change according to the change in the MCU's operating mode. Therefore, care must be taken to make pin settings to prevent these pins from being used directly as output signal pins during a reset, or to prevent collision with signals outside the MCU.

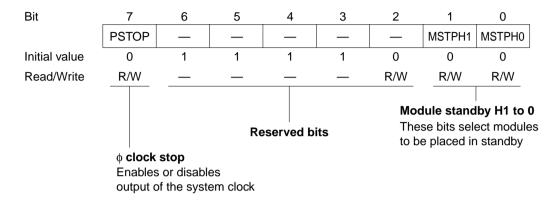

#### 20.2.2 Module Standby Control Register H (MSTCRH)

MSTCRH is an 8-bit readable/writable register that controls output of the system clock ( $\phi$ ). It also controls the module standby function, which places individual on-chip supporting modules in the standby state. Module standby can be designated for the SCI0, SCI1.

MSTCRH is initialized to H'78 by a reset and in hardware standby mode. It is not initialized in software standby mode.

Bit 7— $\phi$  Clock Stop (PSTOP): Enables or disables output of the system clock ( $\phi$ ).

| Bit 7<br>PSTOP | Description                     |                 |

|----------------|---------------------------------|-----------------|

| 0              | System clock output is enabled  | (Initial value) |

| 1              | System clock output is disabled |                 |

Bits 6 to 3—Reserved: These bits cannot be modified and are always read as 1.

Bit 2—Reserved: This bit can be written and read.

Bit 1—Module Standby H1 (MSTPH1): Selects whether to place the SCI1 in standby.

| Bit 1<br>MSTPH1 | Description              |                 |

|-----------------|--------------------------|-----------------|

| 0               | SCI1 operates normally   | (Initial value) |

| 1               | SCI1 is in standby state |                 |

#### Table 21.4 Clock Timing

Conditions:  $V_{CC} = 3.0$  to 3.6 V,  $AV_{CC} = 3.0$  to 3.6 V,  $V_{REF} = 3.0$  to  $AV_{CC}$ ,  $V_{SS} = AV_{SS} = 0$  V,  $T_a = -20^{\circ}$ C to  $+75^{\circ}$ C (regular specifications),  $T_a = -40^{\circ}$ C to  $+85^{\circ}$ C (wide-range specifications)

| Item                                               | Symbol            | Min | Max | Unit | Test Conditions |

|----------------------------------------------------|-------------------|-----|-----|------|-----------------|

| Clock cycle time                                   | t <sub>cyc</sub>  | 40  | 500 | ns   | Figure 21.11    |

| Clock pulse low width                              | t <sub>CL</sub>   | 10  | _   | ns   |                 |

| Clock pulse high width                             | t <sub>CH</sub>   | 10  | _   | ns   |                 |

| Clock rise time                                    | t <sub>Cr</sub>   |     | 10  | ns   |                 |

| Clock fall time                                    | t <sub>Cf</sub>   | _   | 10  | ns   |                 |

| Clock oscillator settling time at reset            | t <sub>OSC1</sub> | 20  | —   | ms   | Figure 21.7     |

| Clock oscillator settling time in software standby | tosc2             | 7   | —   | ms   | Figure 20.1     |

### Table 21.5 Control Signal Timing

Conditions:  $V_{CC} = 3.0$  to 3.6 V,  $AV_{CC} = 3.0$  to 3.6 V,  $V_{REF} = 3.0$  to  $AV_{CC}$ ,  $V_{SS} = AV_{SS} = 0$  V,  $T_a = -20^{\circ}$ C to  $+75^{\circ}$ C (regular specifications),  $T_a = -40^{\circ}$ C to  $+85^{\circ}$ C (wide-range specifications)

| Item                                                          | Symbol             | Min | Max | Unit             | <b>Test Conditions</b> |

|---------------------------------------------------------------|--------------------|-----|-----|------------------|------------------------|

| RES setup time                                                | t <sub>RESS</sub>  | 150 | _   | ns               | Figure 21.8            |

| RES pulse width                                               | t <sub>RESW</sub>  | 20  | _   | t <sub>cyc</sub> |                        |

| Mode programming setup time                                   | t <sub>MDS</sub>   | 200 | _   | ns               |                        |

| RESO output delay time                                        | t <sub>RESD</sub>  | _   | 50  | ns               | Figure 21.9            |

| RESO output pulse width                                       | t <sub>RESOW</sub> | 132 | _   | t <sub>cyc</sub> |                        |

| NMI, IRQ setup time                                           | t <sub>NMIS</sub>  | 150 | _   | ns               | Figure 21.10           |

| NMI, IRQ hold time                                            | t <sub>NMIH</sub>  | 10  | _   | ns               |                        |

| NMI, IRQ pulse width (in recovery from software standby mode) | t <sub>NMIW</sub>  | 200 |     | ns               | _                      |

- 2. Given current consumption values are when all the output pins are made to unloaded state and, furthermore, when the on-chip pull-up MOS is turned off under conditions that V<sub>IH</sub> min = V<sub>CC</sub> 0.5 V and V<sub>IL</sub> max = 0.5 V. Also, the aforesaid current consumption values are when V<sub>IH</sub> min = V<sub>CC</sub> × 0.9 and V<sub>IL</sub> max = 0.3 V under the condition of V<sub>RAM</sub>  $\leq$  V<sub>CC</sub> < 3.0 V.

- 3.  $I_{CC}$  max. (under normal operations) = 3.0 (mA) + 0.61 (mA/(MHz × V)) × V<sub>CC</sub> × f  $I_{CC}$  max. (when using the sleeve) = 3.0 (mA) + 0.49 (mA/(MHz × V)) × V<sub>CC</sub> × f  $I_{CC}$  max. (when the sleeve + module are standing by) = 3.0 (mA) + 0.38 (mA/(MHz × V)) × V<sub>CC</sub> × f

Also, the typ. values for current dissipation are reference values.

#### **Table 21.12 Permissible Output Currents**

Conditions:  $V_{CC} = 3.0$  V to 3.6 V,  $AV_{CC} = 3.0$  V to 3.6 V,  $V_{REF} = 3.0$  V to  $AV_{CC}$ ,  $V_{SS} = AV_{SS} = 0$  V,  $T_a = -20^{\circ}$ C to  $+75^{\circ}$ C (regular specifications),

$T_a = -40^{\circ}C$  to  $+85^{\circ}C$  (wide-range specifications)

| Item                                         |                                               | Symbol             | Min | Тур | Max | Unit |

|----------------------------------------------|-----------------------------------------------|--------------------|-----|-----|-----|------|

| Permissible output                           | Ports 1, 2, and 5                             | I <sub>OL</sub>    | _   | —   | 10  | mA   |

| low current (per pin)                        | Other output pins                             |                    | —   | —   | 2.0 | mA   |

| Permissible output<br>low current (total)    | Total of 20 pins in<br>Ports 1, 2, and 5      | Σl <sub>OL</sub>   | _   | _   | 80  | mA   |

|                                              | Total of all output pins, including the above |                    |     |     | 120 | mA   |

| Permissible output<br>high current (per pin) | All output pins                               | —І <sub>ОН</sub>   |     |     | 2.0 | mA   |

| Permissible output<br>high current (total)   | Total of all output pins                      | $ -\Sigma I_{OH} $ |     | —   | 40  | mA   |

Notes: 1. To protect chip reliability, do not exceed the output current values in table 21.12.

2. When directly driving a darlington pair or LED, always insert a current-limiting resistor in the output line, as shown in figures 21.4 and 21.5.

|                   |              |     | Addressing Mode and<br>Instruction Length (bytes) |     |           |             |     |          |        | ) |                                                                                |   |          | No. of<br>States <sup>*1</sup> |      |    |          |        |          |

|-------------------|--------------|-----|---------------------------------------------------|-----|-----------|-------------|-----|----------|--------|---|--------------------------------------------------------------------------------|---|----------|--------------------------------|------|----|----------|--------|----------|

|                   | Operand Size | #xx | Rn                                                | ERn | @(d, ERn) | @-ERn/@ERn+ | @aa | @(d, PC) | e @ aa |   |                                                                                |   | <u> </u> |                                | on C |    | <u> </u> | Normal | Advanced |

| Mnemonic          | -            | #   |                                                   | 0   | ø         | ø           | ø   | ø        | 0      |   | Operation                                                                      | 1 | н        | N                              | Z    | V  | С        |        | -        |

| INC.L #1, ERd     | L            |     | 2                                                 |     |           |             |     |          |        |   | $ERd32+1 \rightarrow ERd32$                                                    | - | -        | \$                             | \$   | \$ | -        | 2      |          |

| INC.L #2, ERd     | L            |     | 2                                                 |     |           |             |     |          |        |   | $ERd32+2 \rightarrow ERd32$                                                    | - | -        | \$                             | \$   | \$ | -        | 2      |          |

| DAA Rd            | В            |     | 2                                                 |     |           |             |     |          |        |   | Rd8 decimal adjust $\rightarrow$ Rd8                                           | _ | *        | \$                             | \$   | *  | _        | 2      |          |

| SUB.B Rs, Rd      | В            |     | 2                                                 |     |           |             |     |          |        |   | $Rd8-Rs8 \rightarrow Rd8$                                                      | — | \$       | $\updownarrow$                 | \$   | ↕  | \$       | 2      | !        |

| SUB.W #xx:16, Rd  | W            | 4   |                                                   |     |           |             |     |          |        |   | Rd16–#xx:16 $\rightarrow$ Rd16                                                 | - | (1)      | \$                             | \$   | €  | \$       | 4      |          |

| SUB.W Rs, Rd      | W            |     | 2                                                 |     |           |             |     |          |        |   | $Rd16-Rs16 \rightarrow Rd16$                                                   | — | (1)      | \$                             | \$   | €  | \$       | 2      | :        |

| SUB.L #xx:32, ERd | L            | 6   |                                                   |     |           |             |     |          |        |   | ERd32–#xx:32<br>$\rightarrow$ ERd32                                            | — | (2)      | \$                             | \$   | \$ | \$       | 6      | ;        |

| SUB.L ERs, ERd    | L            |     | 2                                                 |     |           |             |     |          |        |   | ERd32–ERs32<br>$\rightarrow$ ERd32                                             | - | (2)      | \$                             | \$   | \$ | \$       | 2      | !        |

| SUBX.B #xx:8, Rd  | в            | 2   |                                                   |     |           |             |     |          |        |   | Rd8–#xx:8–C $\rightarrow$ Rd8                                                  | _ | \$       | \$                             | (3)  | \$ | \$       | 2      |          |

| SUBX.B Rs, Rd     | в            |     | 2                                                 |     |           |             |     |          |        |   | Rd8–Rs8–C $\rightarrow$ Rd8                                                    | _ | \$       | \$                             | (3)  | \$ | \$       | 2      |          |

| SUBS.L #1, ERd    | L            |     | 2                                                 |     |           |             |     |          |        |   | ERd32–1 $\rightarrow$ ERd32                                                    | — | _        | _                              | _    | _  | —        | 2      |          |

| SUBS.L #2, ERd    | L            |     | 2                                                 |     |           |             |     |          |        |   | $ERd32-2 \rightarrow ERd32$                                                    | _ | _        | _                              | _    | _  | _        | 2      |          |

| SUBS.L #4, ERd    | L            |     | 2                                                 |     |           |             |     |          |        |   | $ERd32-4 \rightarrow ERd32$                                                    | — | _        | _                              | -    | _  | _        | 2      |          |

| DEC.B Rd          | В            |     | 2                                                 |     |           |             |     |          |        |   | $Rd8-1 \rightarrow Rd8$                                                        | _ | _        | \$                             | \$   | \$ | _        | 2      |          |

| DEC.W #1, Rd      | w            |     | 2                                                 |     |           |             |     |          |        |   | Rd16−1 $\rightarrow$ Rd16                                                      | — | -        | \$                             | \$   | ≎  | _        | 2      |          |

| DEC.W #2, Rd      | w            |     | 2                                                 |     |           |             |     |          |        |   | $Rd16-2 \rightarrow Rd16$                                                      | — | -        | $\updownarrow$                 | \$   | \$ | _        | 2      |          |

| DEC.L #1, ERd     | L            |     | 2                                                 |     |           |             |     |          |        |   | ERd32–1 $\rightarrow$ ERd32                                                    | — | -        | \$                             | \$   | \$ | —        | 2      |          |

| DEC.L #2, ERd     | L            |     | 2                                                 |     |           |             |     |          |        |   | $ERd32-2 \rightarrow ERd32$                                                    | — | _        | \$                             | \$   | ↕  | —        | 2      |          |

| DAS.Rd            | В            |     | 2                                                 |     |           |             |     |          |        |   | Rd8 decimal adjust<br>→ Rd8                                                    | — | *        | \$                             | \$   | *  | —        | 2      | :        |

| MULXU. B Rs, Rd   | в            |     | 2                                                 |     |           |             |     |          |        |   | $Rd8 \times Rs8 \rightarrow Rd16$<br>(unsigned multiplication)                 | — | -        | —                              | -    | _  | —        | 14     | 4        |

| MULXU. W Rs, ERd  | w            |     | 2                                                 |     |           |             |     |          |        |   | $Rd16 \times Rs16 \rightarrow ERd32$<br>(unsigned multiplication)              | - | -        | —                              | -    | —  | -        | 2:     | 2        |

| MULXS. B Rs, Rd   | в            |     | 4                                                 |     |           |             |     |          |        |   | $Rd8 \times Rs8 \rightarrow Rd16$<br>(signed multiplication)                   | — | -        | \$                             | \$   | _  | —        | 1      | 3        |

| MULXS. W Rs, ERd  | w            |     | 4                                                 |     |           |             |     |          |        |   | $Rd16 \times Rs16 \rightarrow ERd32$<br>(signed multiplication)                | - | -        | \$                             | \$   | _  | —        | 24     | 4        |

| DIVXU. B Rs, Rd   | В            |     | 2                                                 |     |           |             |     |          |        |   | Rd16 ÷ Rs8 → Rd16<br>(RdH: remainder, RdL:<br>quotient)<br>(unsigned division) |   |          | (6)                            | (7)  | _  |          | 1.     | 4        |

### 6. Branching instructions

|                     |                     |     |    |      |           | ng I<br>Ler |      |          |        | ) |                    |                     |                |   |   |   |   |        | No.<br>State       |    |

|---------------------|---------------------|-----|----|------|-----------|-------------|------|----------|--------|---|--------------------|---------------------|----------------|---|---|---|---|--------|--------------------|----|

| Mnemonic            |                     | #xx | Rn | @ERn | @(d, ERn) | @-ERn/@ERn+ | @ aa | @(d, PC) | @ @ aa |   | Operation          | Branch<br>Condition | Condition Code |   |   |   |   | e<br>C | Normal<br>Advanced |    |

| BRA d:8 (BT d:8)    | <b>Operand Size</b> | +#  |    | •    | •         |             |      | 2        |        | - | If condition       | Always              | -              | п | N | 2 | v |        | - 4                |    |

| BRA d:16 (BT d:16)  | _                   |     |    |      |           |             |      | 4        |        |   | is true then       | Always              |                |   |   |   |   |        | 6                  |    |

| BRN d:8 (BF d:8)    | _                   |     |    |      |           |             |      | 2        |        |   | PC ←               | Never               | <u> </u> _     | _ | _ | _ | _ | _      | 4                  |    |

| BRN d:16 (BF d:16)  | _                   |     |    |      |           |             |      | 4        |        |   | PC+d else<br>next; |                     | <u> </u>       | _ | _ | _ | _ | _      | 6                  |    |

| BHI d:8             | _                   |     |    |      |           |             |      | 2        |        |   | -                  | $C \lor Z = 0$      | _              | _ | _ |   | _ | _      | 4                  |    |

| BHI d:16            | _                   |     |    |      |           |             |      | 4        |        |   | -                  | 0, 2, 0             | <u> </u>       | _ | _ | - | _ | _      | 6                  | -  |

| BLS d:8             | _                   |     |    |      |           |             |      | 2        |        |   | -                  | C ∨ Z = 1           | -              | _ | _ | _ | _ | _      | 4                  |    |

| BLS d:16            | _                   |     |    |      |           |             |      | 4        |        |   | -                  | -                   | -              | _ | _ | _ | _ | _      | 6                  | 5  |

| BCC d:8 (BHS d:8)   | _                   |     |    |      |           |             |      | 2        |        |   | -                  | C = 0               | 1_             | _ | _ | _ | _ | _      | 4                  | ł  |

| BCC d:16 (BHS d:16) | _                   |     |    |      |           |             |      | 4        |        |   |                    |                     | -              | _ | _ | _ | _ | _      | 6                  | ;  |

| BCS d:8 (BLO d:8)   | _                   |     |    |      |           |             |      | 2        |        |   | 1                  | C = 1               | _              | _ | _ | _ | _ | _      | 4                  | +  |

| BCS d:16 (BLO d:16) | _                   |     |    |      |           |             |      | 4        |        |   |                    |                     | _              | _ | _ | _ | _ | _      | 6                  | ;  |

| BNE d:8             | _                   |     |    |      |           |             |      | 2        |        |   | 1                  | Z = 0               | -              | — | _ | _ | _ | _      | 4                  | ł  |

| BNE d:16            | _                   |     |    |      |           |             |      | 4        |        |   |                    |                     | -              | — | — | — | _ | _      | 6                  | ;  |

| BEQ d:8             | _                   |     |    |      |           |             |      | 2        |        |   | 1                  | Z = 1               | -              | _ | _ | _ | _ | -      | 4                  | ł  |

| BEQ d:16            | _                   |     |    |      |           |             |      | 4        |        |   |                    |                     | -              | — | — | — | _ | —      | 6                  | ;  |

| BVC d:8             | _                   |     |    |      |           |             |      | 2        |        |   | 1                  | V = 0               | -              | — | — | — | — | —      | 4                  | ł  |

| BVC d:16            | _                   |     |    |      |           |             |      | 4        |        |   | 1                  |                     | -              | — | — | — | — | —      | 6                  | ;  |

| BVS d:8             | _                   |     |    |      |           |             |      | 2        |        |   | 1                  | V = 1               | -              | _ | _ | — | _ | _      | 4                  | ŀ  |

| BVS d:16            | _                   |     |    |      |           |             |      | 4        |        |   | 1                  |                     | -              | — | — | — | — | —      | 6                  | ;  |

| BPL d:8             | —                   |     |    |      |           |             |      | 2        |        |   | ]                  | N = 0               | -              | — | — | — | — | -      | 4                  | ł  |

| BPL d:16            | —                   |     |    |      |           |             |      | 4        |        |   | 1                  |                     | -              | — | — | — | — | —      | 6                  | ;  |

| BMI d:8             | _                   |     |    |      |           |             |      | 2        |        |   |                    | N = 1               | -              | _ | — | — | _ | _      | 4                  | ł  |

| BMI d:16            | _                   |     |    |      |           |             |      | 4        |        |   | ]                  |                     | -              | — | — | — | — | —      | 6                  | ;  |

| BGE d:8             | —                   |     |    |      |           |             |      | 2        |        |   | ]                  | N⊕V = 0             | -              | — | — | — | — | —      | 4                  | ł  |

| BGE d:16            | —                   |     |    |      |           |             |      | 4        |        |   |                    |                     | -              | — | — | — | — | —      | 6                  | ;  |

| BLT d:8             | _                   |     |    |      |           |             |      | 2        |        |   |                    | N⊕V = 1             | _              | _ | _ | _ | _ | _      | 4                  | ł  |

| BLT d:16            | _                   |     |    |      |           |             |      | 4        |        |   |                    |                     | -              | _ | _ | — | _ | _      | 6                  | \$ |

| BGT d:8             | —                   |     |    |      |           |             |      | 2        |        |   |                    | Z ∨ (N⊕V)           | _              | _ | _ | _ | _ | -      | 4                  | ł  |

| BGT d:16            | -                   |     |    |      |           |             |      | 4        |        |   |                    | = 0                 | -              | — | — | — | _ | -      | 6                  | \$ |

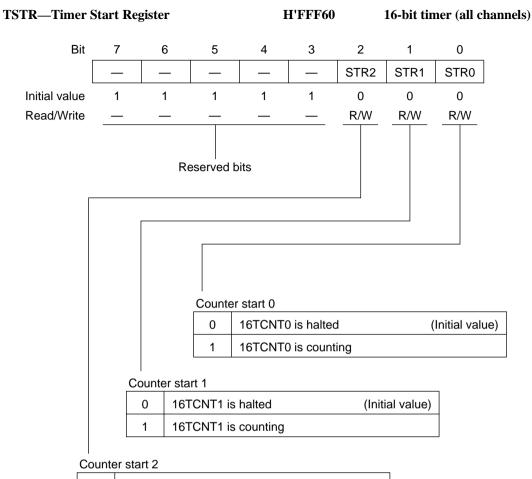

# **B.3** Functions

| 0 | 16TCNT2 is halted (Initial value | ) |

|---|----------------------------------|---|

| 1 | 16TCNT2 is counting              |   |

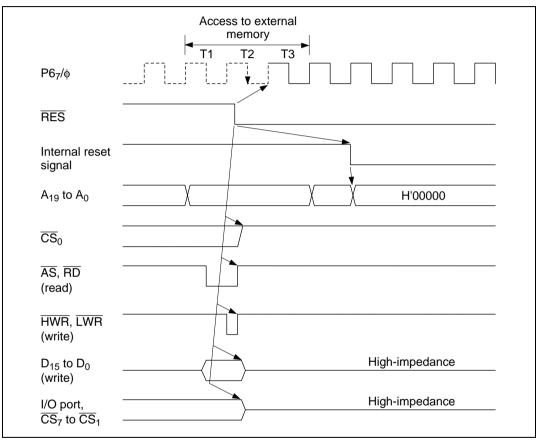

## **D.2 Pin States at Reset**

**Modes 1 and 2:** Figure D.1 is a timing diagram for the case in which  $\overline{\text{RES}}$  goes low during an external memory access in mode 1 or 2. As soon as  $\overline{\text{RES}}$  goes low, all ports are initialized to the input state.  $\overline{\text{AS}}$ ,  $\overline{\text{RD}}$ ,  $\overline{\text{HWR}}$ ,  $\overline{\text{LWR}}$ , and  $\overline{\text{CS}}_0$  go high, and D<sub>15</sub> to D<sub>0</sub> go to the high-impedance state. The address bus is initialized to the low output level 2.5  $\phi$  clock cycles after the low level of  $\overline{\text{RES}}$  is sampled. Clock pin P6<sub>7</sub>/ $\phi$  goes to the output state at the next rise of  $\phi$  after  $\overline{\text{RES}}$  goes low.

Figure D.1 Reset during Memory Access (Modes 1 and 2)