Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                  |

|----------------------------|------------------------------------------------------------------|

| Product Status             | Active                                                           |

| Core Processor             | CIP-51 8051                                                      |

| Core Size                  | 8-Bit                                                            |

| Speed                      | 25MHz                                                            |

| Connectivity               | SMBus (2-Wire/I <sup>2</sup> C), SPI, UART/USART                 |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, Temp Sensor, WDT               |

| Number of I/O              | 16                                                               |

| Program Memory Size        | 8KB (8K x 8)                                                     |

| Program Memory Type        | FLASH                                                            |

| EEPROM Size                | ·                                                                |

| RAM Size                   | 512 x 8                                                          |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                      |

| Data Converters            | A/D 9x12b                                                        |

| Oscillator Type            | Internal                                                         |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                |

| Mounting Type              | Surface Mount                                                    |

| Package / Case             | 20-UFQFN Exposed Pad                                             |

| Supplier Device Package    | 20-QFN (3x3)                                                     |

| Purchase URL               | https://www.e-xfl.com/product-detail/silicon-labs/c8051f980-c-gm |

|                            |                                                                  |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| Table 22.1. SMBus Clock Source Selection       24         Table 22.4. SMBus Clock Source Selection       24 |    |

|-------------------------------------------------------------------------------------------------------------|----|

| Table 22.2. Minimum SDA Setup and Hold Times       24                                                       |    |

| Table 22.3. Sources for Hardware Changes to SMB0CN                                                          | 45 |

| Table 22.4. Hardware Address Recognition Examples (EHACK = 1)                                               | 46 |

| Table 22.5. SMBus Status Decoding With Hardware ACK Generation Disabled                                     |    |

| (EHACK = 0)                                                                                                 | 53 |

| Table 22.6. SMBus Status Decoding With Hardware ACK Generation Enabled                                      |    |

| (EHACK = 1)                                                                                                 | 55 |

| Table 23.1. Timer Settings for Standard Baud Rates                                                          |    |

| Using The Internal 24.5 MHz Oscillator                                                                      | 64 |

| Table 23.2. Timer Settings for Standard Baud Rates                                                          |    |

| Using an External 22.1184 MHz Oscillator                                                                    | 64 |

| Table 24.1. SPI Slave Timing Parameters                                                                     | 77 |

| Table 25.1. Timer 0 Running Modes       28                                                                  | 80 |

| Table 26.1. PCA Timebase Input Options                                                                      | 01 |

| Table 26.2. PCA0CPM and PCA0PWM Bit Settings for PCA Capture/Compare                                        |    |

| Modules                                                                                                     | 03 |

| Table 26.3. Watchdog Timer Timeout Intervals1                                                               | 12 |

| Dimension | MIN      | MAX  |  |  |  |

|-----------|----------|------|--|--|--|

| C1        | 3.90     | 4.00 |  |  |  |

| C2        | 3.90     | 4.00 |  |  |  |

| E         | 0.50 BSC |      |  |  |  |

| X1        | 0.20     | 0.30 |  |  |  |

| X2        | 2.70     | 2.80 |  |  |  |

| Y1        | 0.65     | 0.75 |  |  |  |

| Y2        | 2.70     | 2.80 |  |  |  |

#### Table 3.5. PCB Land Pattern

#### Notes:

#### General

- 1. All dimensions shown are in millimeters (mm) unless otherwise noted.

- 2. This Land Pattern Design is based on the IPC-7351 guidelines.

#### Solder Mask Design

1. All metal pads are to be non-solder mask defined (NSMD). Clearance between the solder mask and the metal pad is to be  $60 \ \mu m$  minimum, all the way around the pad.

#### **Stencil Design**

- **1.** A stainless steel, laser-cut and electro-polished stencil with trapezoidal walls should be used to assure good solder paste release.

- 2. The stencil thickness should be 0.125 mm (5 mils).

- **3.** The ratio of stencil aperture to land pad size should be 1:1 for all perimeter pads.

- **4.** A 2x2 array of 1.10 mm x 1.10 mm openings on 1.30 mm pitch should be used for the center ground pad.

#### **Card Assembly**

- 1. A No-Clean, Type-3 solder paste is recommended.

- 2. The recommended card reflow profile is per the JEDEC/IPC J-STD-020 specification for Small Body Components.

## 7.2. Comparator Outputs

When a comparator is enabled, its output is a logic 1 if the voltage at the positive input is higher than the voltage at the negative input. When disabled, the comparator output is a logic 0. The comparator output is synchronized with the system clock as shown in Figure 7.2. The synchronous "latched" output (CP0) can be polled in software (CP0OUT bit), used as an interrupt source, or routed to a Port pin (configured for digital I/O) through the Crossbar.

The asynchronous "raw" comparator output (CP0A) is used by the low power mode wake-up logic and reset decision logic. See the Power Options chapter and the Reset Sources chapter for more details on how the asynchronous comparator outputs are used to make wake-up and reset decisions. The asynchronous comparator output can also be routed directly to a Port pin through the Crossbar, and is available for use outside the device even if the system clock is stopped.

When using a Comparator as an interrupt source, Comparator interrupts can be generated on rising-edge and/or falling-edge comparator output transitions. Two independent interrupt flags (CP0RIF and CP0FIF) allow software to determine which edge caused the Comparator interrupt. The comparator rising-edge and falling-edge interrupt flags are set by hardware when a corresponding edge is detected regardless of the interrupt enable state. Once set, these bits remain set until cleared by software.

The rising-edge and falling-edge interrupts can be individually enabled using the CPORIE and CPOFIE interrupt enable bits in the CPTOMD register. In order for the CPORIF and/or CPOFIF interrupt flags to generate an interrupt request to the CPU, the Comparator must be enabled as an interrupt source and global interrupts must be enabled. See the Interrupt Handler chapter for additional information.

## 7.3. Comparator Response Time

Comparator response time may be configured in software via the CPT0MD register described on "CPT0MD: Comparator 0 Mode Selection" on page 97. Four response time settings are available: Mode 0 (Fastest Response Time), Mode 1, Mode 2, and Mode 3 (Lowest Power). Selecting a longer response time reduces the Comparator active supply current. The Comparator also has a low power shutdown state, which is entered any time the comparator is disabled. Comparator rising edge and falling edge response times are typically not equal. See Table 4.14 on page 63 for complete comparator timing and supply current specifications.

## 7.4. Comparator Hysteresis

The Comparator features software-programmable hysteresis that can be used to stabilize the comparator output while a transition is occurring on the input. Using the CPT0CN register, the user can program both the amount of hysteresis voltage (referred to the input voltage) and the positive and negative-going symmetry of this hysteresis around the threshold voltage (i.e., the comparator negative input).

Figure 7.2 shows that when positive hysteresis is enabled, the comparator output does not transition from logic 0 to logic 1 until the comparator positive input voltage has exceeded the threshold voltage by an amount equal to the programmed hysteresis. It also shows that when negative hysteresis is enabled, the comparator output does not transition from logic 1 to logic 0 until the comparator positive input voltage has fallen below the threshold voltage by an amount equal to the programmed by the threshold voltage by an amount equal to the programmed hysteresis.

The amount of positive hysteresis is determined by the settings of the CP0HYP bits in the CPT0CN register and the amount of negative hysteresis voltage is determined by the settings of the CP0HYN bits in the same register. Settings of 20, 10, 5, or 0 mV can be programmed for both positive and negative hysteresis. See Section "Table 4.14. Comparator Electrical Characteristics" on page 63 for complete comparator hysteresis specifications.

## SFR Definition 8.12. CS0MD2: Capacitive Sense Mode 2

| Bit   | 7             | 6                                                                                                    | 5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 4           | 3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 2             | 1                                              | 0            |  |  |  |

|-------|---------------|------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------|------------------------------------------------|--------------|--|--|--|

| Name  | e CS0C        | R[1:0]                                                                                               | :0] CS0DT[2:0] CS0IA[2:0]                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |               |                                                |              |  |  |  |

| Туре  | e R/          | W                                                                                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | R/W         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |               | R/W                                            |              |  |  |  |

| Rese  | <b>t</b> 0    | 1                                                                                                    | 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 0           | 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 0             | 0                                              | 0            |  |  |  |

| SFR P | age = 0x0; SF | R Address =                                                                                          | = 0xF3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |               |                                                |              |  |  |  |

| Bit   | Name          |                                                                                                      | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |               |                                                |              |  |  |  |

| 7:6   | CS0CR[1:0]    | These bir<br>ifications<br>00: Conv<br>01: Conv<br>10: Conv                                          | <ul> <li>CS0 Conversion Rate.</li> <li>These bits control the conversion rate of the CS0 module. See the electrical sp ifications table for specific timing.</li> <li>00: Conversions last 12 internal CS0 clocks and are 12 bits in length.</li> <li>01: Conversions last 13 internal CS0 clocks and are 13 bits in length.</li> <li>10: Conversions last 14 internal CS0 clocks and are 14 bits in length.</li> <li>11: Conversions last 16 internal CS0 clocks.and are 16 bits in length.</li> </ul> |             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |               |                                                |              |  |  |  |

| 5:3   | CS0DT[2:0]    | These bit<br>the defau<br>informati<br>000: Disc<br>001: Disc<br>010: Disc<br>100: Disc<br>101: Disc | <b>CSO Discharge Time.</b><br>These bits adjust the primary CS0 reset time. For most touch-sensitive switches, the default (fastest) value is sufficient. See the discussion in Section 8.13 for more information.<br>000: Discharge time is 0.75 μs (recommended for most switches)<br>001: Discharge time is 1.0 μs<br>010: Discharge time is 1.2 μs<br>011: Discharge time is 1.5 μs<br>100: Discharge time is 2 μs<br>101: Discharge time is 3 μs<br>110: Discharge time is 6 μs                    |             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |               |                                                |              |  |  |  |

| 2:0   | CS0IA[2:0]    | These bi                                                                                             | ts allow the usor element.<br>Ifficient. See<br>Current<br>Current<br>Current<br>Current<br>Current<br>Current<br>Current<br>Current                                                                                                                                                                                                                                                                                                                                                                    | For most to | t the output output output output of the out | e switches, t | to charge up<br>he default (h<br>ore informati | ighest) cur- |  |  |  |

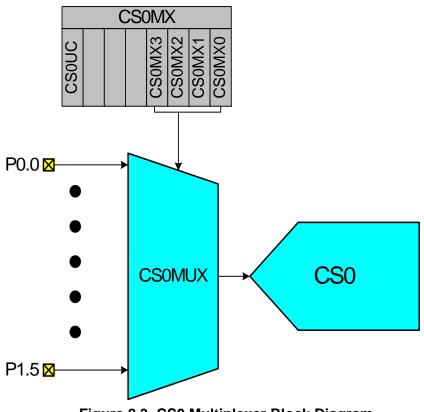

## 8.14. Capacitive Sense Multiplexer

The input multiplexer can be controlled through two methods. The CS0MX register can be written to through firmware, or the register can be configured automatically using the modules auto-scan functionality (see "8.8. Automatic Scanning (Method 1—CS0SMEN = 0)").

Figure 8.3. CS0 Multiplexer Block Diagram

# 11. On-Chip XRAM

The C8051F99x-C8051F98x MCUs include on-chip RAM mapped into the external data memory space (XRAM). The external memory space may be accessed using the external move instruction (MOVX) with the target address specified in either the data pointer (DPTR), or with the target address low byte in R0 or R1. On C8051F99x-C8051F98x devices, the target address high byte is a don't care.

When using the MOVX instruction to access on-chip RAM, no additional initialization is required and the MOVX instruction execution time is as specified in the CIP-51 chapter.

**Important Note**: MOVX write operations can be configured to target Flash memory, instead of XRAM. See Section "14. Flash Memory" on page 150 for more details. The MOVX instruction accesses XRAM by default.

**Important Note**: On device reset or upon waking up from Sleep mode, address 0x0000 of external memory may be overwritten by an indeterminate value. The indeterminate value is 0x00 in most situations. A dummy variable should be placed at address 0x0000 in external memory to ensure that the application firmware does not store any data that needs to be retained during sleep or reset at this memory location.

### 11.1. Accessing XRAM

The XRAM memory space is accessed using the MOVX instruction. The MOVX instruction has two forms, both of which use an indirect addressing method. The first method uses the Data Pointer, DPTR, a 16-bit register which contains the effective address of the XRAM location to be read from or written to. The second method uses R0 or R1 to generate the effective XRAM address. Examples of both of these methods are given below.

#### 11.1.1. 16-Bit MOVX Example

The 16-bit form of the MOVX instruction accesses the memory location pointed to by the contents of the DPTR register. The following series of instructions reads the value of the byte at address 0x1234 into the accumulator A:

| MOV  | DPTR, #0034h | ; load DPTR with 16-bit address to read (0x0034 | .) |

|------|--------------|-------------------------------------------------|----|

| MOVX | A, @DPTR     | ; load contents of 0x0034 into accumulator A    |    |

The above example uses the 16-bit immediate MOV instruction to set the contents of DPTR. Alternately, the DPTR can be accessed through the SFR registers DPH, which contains the upper 8-bits of DPTR, and DPL, which contains the lower 8-bits of DPTR.

#### 11.1.2. 8-Bit MOVX Example

The 8-bit form of the MOVX instruction uses the contents of R0 or R1 to determine the 8-bits of the effective address to be accessed. The following series of instructions read the contents of the byte at address 0x0034 into the accumulator A.

| MOV  | R0, #34h | ; | load | low byte | of | address into R0 (or R1)   |

|------|----------|---|------|----------|----|---------------------------|

| MOVX | a, @R0   | ; | load | contents | of | 0x0034 into accumulator A |

## SFR Definition 13.1. IE: Interrupt Enable

| Bit   | 7   | 6     | 5   | 4   | 3   | 2   | 1   | 0   |

|-------|-----|-------|-----|-----|-----|-----|-----|-----|

| Name  | EA  | ESPI0 | ET2 | ES0 | ET1 | EX1 | ET0 | EX0 |

| Туре  | R/W | R/W   | R/W | R/W | R/W | R/W | R/W | R/W |

| Reset | 0   | 0     | 0   | 0   | 0   | 0   | 0   | 0   |

#### SFR Page = All; SFR Address = 0xA8; Bit-Addressable

| Bit | Name  | Function                                                                                                                                                                                                                                                              |

|-----|-------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7   | EA    | <ul> <li>Enable All Interrupts.</li> <li>Globally enables/disables all interrupts. It overrides individual interrupt mask settings.</li> <li>0: Disable all interrupt sources.</li> <li>1: Enable each interrupt according to its individual mask setting.</li> </ul> |

| 6   | ESPI0 | <ul> <li>Enable Serial Peripheral Interface (SPI0) Interrupt.</li> <li>This bit sets the masking of the SPI0 interrupts.</li> <li>0: Disable all SPI0 interrupts.</li> <li>1: Enable interrupt requests generated by SPI0.</li> </ul>                                 |

| 5   | ET2   | <ul> <li>Enable Timer 2 Interrupt.</li> <li>This bit sets the masking of the Timer 2 interrupt.</li> <li>0: Disable Timer 2 interrupt.</li> <li>1: Enable interrupt requests generated by the TF2L or TF2H flags.</li> </ul>                                          |

| 4   | ES0   | Enable UART0 Interrupt.<br>This bit sets the masking of the UART0 interrupt.<br>0: Disable UART0 interrupt.<br>1: Enable UART0 interrupt.                                                                                                                             |

| 3   | ET1   | <ul> <li>Enable Timer 1 Interrupt.</li> <li>This bit sets the masking of the Timer 1 interrupt.</li> <li>0: Disable all Timer 1 interrupt.</li> <li>1: Enable interrupt requests generated by the TF1 flag.</li> </ul>                                                |

| 2   | EX1   | <ul> <li>Enable External Interrupt 1.</li> <li>This bit sets the masking of External Interrupt 1.</li> <li>0: Disable external interrupt 1.</li> <li>1: Enable interrupt requests generated by the INT1 input.</li> </ul>                                             |

| 1   | ET0   | <ul> <li>Enable Timer 0 Interrupt.</li> <li>This bit sets the masking of the Timer 0 interrupt.</li> <li>0: Disable all Timer 0 interrupt.</li> <li>1: Enable interrupt requests generated by the TF0 flag.</li> </ul>                                                |

| 0   | EX0   | <ul> <li>Enable External Interrupt 0.</li> <li>This bit sets the masking of External Interrupt 0.</li> <li>0: Disable external interrupt 0.</li> <li>1: Enable interrupt requests generated by the INTO input.</li> </ul>                                             |

## SFR Definition 13.3. EIE1: Extended Interrupt Enable 1

| Bit   | 7            | 6                                                                                                                                                                                                                                                                                 | 5                                                                                                                                                                                                                                                                            | 4                           | 3                          | 2             | 1         | 0     |  |  |  |  |  |

|-------|--------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------|----------------------------|---------------|-----------|-------|--|--|--|--|--|

| Nam   | e ET3        |                                                                                                                                                                                                                                                                                   | ECP0                                                                                                                                                                                                                                                                         | EPCA0                       | EADC0                      | EWADC0        | ERTC0A    | ESMB0 |  |  |  |  |  |

| Туре  | e R/W        | R                                                                                                                                                                                                                                                                                 | R/W                                                                                                                                                                                                                                                                          | R/W                         | R/W                        | R/W           | R/W       | R/W   |  |  |  |  |  |

| Rese  | t 0          | 0                                                                                                                                                                                                                                                                                 | 0                                                                                                                                                                                                                                                                            | 0                           | 0                          | 0             | 0         | 0     |  |  |  |  |  |

| SFR F | age = All; S | l; SFR Address = 0xE6                                                                                                                                                                                                                                                             |                                                                                                                                                                                                                                                                              |                             |                            |               |           |       |  |  |  |  |  |

| Bit   | Name         |                                                                                                                                                                                                                                                                                   |                                                                                                                                                                                                                                                                              |                             | Function                   |               |           |       |  |  |  |  |  |

| 7     | ET3          | Enable Timer<br>This bit sets th<br>0: Disable Tim<br>1: Enable inte                                                                                                                                                                                                              | ne masking o<br>her 3 interrup                                                                                                                                                                                                                                               | of the Timer                |                            | _ or TF3H fla | ags.      |       |  |  |  |  |  |

| 6     | Unused       | Read = 0b. W                                                                                                                                                                                                                                                                      | rite = Don't d                                                                                                                                                                                                                                                               | care.                       |                            |               |           |       |  |  |  |  |  |

| 5     | ECP0         | Enable Comp<br>This bit sets th<br>0: Disable CP<br>1: Enable inte                                                                                                                                                                                                                | ne masking o<br>0 interrupts.                                                                                                                                                                                                                                                | of the CP0 in               | iterrupt.                  | RIF or CP0F   | TF flags. |       |  |  |  |  |  |

| 4     | EPCA0        | Enable Progr<br>This bit sets th<br>0: Disable all I<br>1: Enable inte                                                                                                                                                                                                            | ne masking o<br>PCA0 interru                                                                                                                                                                                                                                                 | of the PCA0<br>ipts.        | interrupts.                | terrupt.      |           |       |  |  |  |  |  |

| 3     | EADC0        | Enable ADC0<br>This bit sets th<br>0: Disable AD<br>1: Enable inte                                                                                                                                                                                                                | ne masking o<br>C0 Conversi                                                                                                                                                                                                                                                  | of the ADC0<br>ion Complete | Conversion<br>e interrupt. | ·             | terrupt.  |       |  |  |  |  |  |

| 2     | EWADC0       | <ul> <li>Enable Window Comparison ADC0 Interrupt.</li> <li>This bit sets the masking of ADC0 Window Comparison interrupt.</li> <li>0: Disable ADC0 Window Comparison interrupt.</li> <li>1: Enable interrupt requests generated by ADC0 Window Compare flag (AD0WINT).</li> </ul> |                                                                                                                                                                                                                                                                              |                             |                            |               |           |       |  |  |  |  |  |

| 1     | ERTC0A       | Enable SmaRTClock Alarm Interrupts.<br>This bit sets the masking of the SmaRTClock Alarm interrupt.<br>0: Disable SmaRTClock Alarm interrupts.<br>1: Enable interrupt requests generated by a SmaRTClock Alarm.                                                                   |                                                                                                                                                                                                                                                                              |                             |                            |               |           |       |  |  |  |  |  |

| 0     | ESMB0        | This bit sets th<br>0: Disable all \$                                                                                                                                                                                                                                             | <ol> <li>Enable interrupt requests generated by a SmaRTClock Alarm.</li> <li>Enable SMBus (SMB0) Interrupt.</li> <li>This bit sets the masking of the SMB0 interrupt.</li> <li>Disable all SMB0 interrupts.</li> <li>Enable interrupt requests generated by SMB0.</li> </ol> |                             |                            |               |           |       |  |  |  |  |  |

## 13.6. External Interrupts INT0 and INT1

The INTO and INT1 external interrupt sources are configurable as active high or low, edge or level sensitive. The INOPL (INT0 Polarity) and IN1PL (INT1 Polarity) bits in the IT01CF register select active high or active low; the IT0 and IT1 bits in TCON (Section "25.1. Timer 0 and Timer 1" on page 280) select level or edge sensitive. The table below lists the possible configurations.

| IT0 | IN0PL | INT0 Interrupt               |

|-----|-------|------------------------------|

| 1   | 0     | Active low, edge sensitive   |

| 1   | 1     | Active high, edge sensitive  |

| 0   | 0     | Active low, level sensitive  |

| 0   | 1     | Active high, level sensitive |

| IT1 | IN1PL | INT1 Interrupt               |

|-----|-------|------------------------------|

| 1   | 0     | Active low, edge sensitive   |

| 1   | 1     | Active high, edge sensitive  |

| 0   | 0     | Active low, level sensitive  |

| 0   | 1     | Active high, level sensitive |

INT0 and INT1 are assigned to Port pins as defined in the IT01CF register (see SFR Definition 13.7). Note that INT0 and INT0 Port pin assignments are independent of any Crossbar assignments. INT0 and INT1 will monitor their assigned Port pins without disturbing the peripheral that was assigned the Port pin via the Crossbar. To assign a Port pin only to INT0 and/or INT1, configure the Crossbar to skip the selected pin(s). This is accomplished by setting the associated bit in register PnSKIP (see Section "21.3. Priority Crossbar Decoder" on page 219 for complete details on configuring the Crossbar).

IE0 (TCON.1) and IE1 (TCON.3) serve as the interrupt-pending flags for the INT0 and INT1 external interrupts, respectively. If an INT0 or INT1 external interrupt is configured as edge-sensitive, the corresponding interrupt-pending flag is automatically cleared by the hardware when the CPU vectors to the ISR. When configured as level sensitive, the interrupt-pending flag remains logic 1 while the input is active as defined by the corresponding polarity bit (IN0PL or IN1PL); the flag remains logic 0 while the input is inactive. The external interrupt source must hold the input active until the interrupt request is recognized. It must then deactivate the interrupt request before execution of the ISR completes or another interrupt request will be generated.

### 15.2. Idle Mode

Setting the Idle Mode Select bit (PCON.0) causes the CIP-51 to halt the CPU and enter Idle mode as soon as the instruction that sets the bit completes execution. All internal registers and memory maintain their original data. All analog and digital peripherals can remain active during Idle mode.

**Note:** To ensure the MCU enters a low power state upon entry into Idle Mode, the one-shot circuit should be enabled by clearing the BYPASS bit (FLSCL.6).

Idle mode is terminated when an enabled interrupt is asserted or a reset occurs. The assertion of an enabled interrupt will cause the Idle Mode Selection bit (PCON.0) to be cleared and the CPU to resume operation. The pending interrupt will be serviced and the next instruction to be executed after the return from interrupt (RETI) will be the instruction immediately following the one that set the Idle Mode Select bit. If Idle mode is terminated by an internal or external reset, the CIP-51 performs a normal reset sequence and begins program execution at address 0x0000.

If enabled, the Watchdog Timer (WDT) will eventually cause an internal watchdog reset and thereby terminate the Idle mode. This feature protects the system from an unintended permanent shutdown in the event of an inadvertent write to the PCON register. If this behavior is not desired, the WDT may be disabled by software prior to entering the idle mode if the WDT was initially configured to allow this operation. This provides the opportunity for additional power savings, allowing the system to remain in the idle mode indefinitely, waiting for an external stimulus to wake up the system. Refer to Section "18.6. PCA Watchdog Timer Reset" on page 185 for more information on the use and configuration of the WDT.

### 15.3. Stop Mode

Setting the Stop Mode Select bit (PCON.1) causes the CIP-51 to enter stop mode as soon as the instruction that sets the bit completes execution. In stop mode the precision internal oscillator and CPU are stopped; the state of the low power oscillator and the external oscillator circuit is not affected. Each analog peripheral (including the external oscillator circuit) may be shut down individually prior to entering stop mode. Stop mode can only be terminated by an internal or external reset. On reset, the CIP-51 performs the normal reset sequence and begins program execution at address 0x0000.

If enabled, the Missing Clock Detector will cause an internal reset and thereby terminate the Stop mode. The Missing Clock Detector should be disabled if the CPU is to be put to in STOP mode for longer than the MCD timeout.

Stop mode is a legacy 8051 power mode; it will not result in optimal power savings. Sleep or suspend mode will provide more power savings if the MCU needs to be inactive for a long period of time.

**Note:** To ensure the MCU enters a low power state upon entry into Stop Mode, the one-shot circuit should be enabled by clearing the BYPASS bit (FLSCL.6).

## 15.4. Suspend Mode

Setting the Suspend Mode Select bit (PMU0CF.6) causes the system clock to be gated off and all internal oscillators disabled. The system clock source must be set to the low power internal oscillator or the precision oscillator prior to entering Suspend Mode. All digital logic (timers, communication peripherals, interrupts, CPU, etc.) stops functioning until one of the enabled wake-up sources occurs.

The following wake-up sources can be configured to wake the device from Suspend Mode:

- CS0 End of Conversion or End of Scan

- SmaRTClock Oscillator Fail

- SmaRTClock Alarm

- Port Match Event

- Comparator0 Rising Edge

- Note: Upon wake-up from suspend mode, PMU0 requires two system clocks in order to update the PMU0CF wakeup flags. All flags will read back a value of '0' during the first two system clocks following a wake-up from suspend mode.

In addition, a noise glitch on  $\overline{RST}$  that is not long enough to reset the device will cause the device to exit suspend. In order for the MCU to respond to the pin reset event, software must not place the device back into suspend mode for a period of 15 µs. The PMU0CF register may be checked to determine if the wake-up was due to a falling edge on the /RST pin. If the wake-up source is not due to a falling edge on  $\overline{RST}$ , there is no time restriction on how soon software may place the device back into suspend mode. A 4.7 kW pullup resistor to VDD is recommend for RST to prevent noise glitches from waking the device.

## 15.5. Sleep Mode

Setting the Sleep Mode Select bit (PMU0CF.7) turns off the internal 1.8 V regulator (VREG0) and switches the power supply of all on-chip RAM to the VDD pin (see Figure 15.1). Power to most digital logic on the chip is disconnected; only PMU0 and the SmaRTClock remain powered. Analog peripherals remain powered in two-cell mode. Only the Comparators remain functional when the device enters Sleep Mode. All other analog peripherals (CS0, ADC0, IREF0, External Oscillator, etc.) should be disabled prior to entering Sleep Mode. The system clock source must be set to the low power internal oscillator prior to entering Sleep Mode.

**Important Note**: The precision internal oscillator may potentially lock up after exiting Sleep mode. Systems using Sleep Mode should switch to the low power oscillator prior to entering Sleep Mode:

- 1. Switch the system clock to the low power oscillator (CLKSEL = 0x04).

- 2. Turn off the Precision Oscillator (OSCICN &= ~0x80).

- 3. Enter Sleep.

- 4. Exit Sleep.

- 5. Turn on the Precision Oscillator (OSCICN |= 0x80).

- 6. Switch the system clock to the Precision Oscillator (CLKSEL = 0x00).

GPIO pins configured as digital outputs will retain their output state during sleep mode. In two-cell mode, they will maintain the same current drive capability in sleep mode as they have in normal mode.

GPIO pins configured as digital inputs can be used during sleep mode as wakeup sources using the port match feature. In two-cell mode, they will maintain the same input level specs in sleep mode as they have in normal mode.

C8051F99x-C8051F98x devices support a wakeup request for external devices. Upon exit from sleep mode, the wake-up request signal is driven low, allowing other devices in the system to wake up from their low power modes.

# SFR Definition 15.1. PMU0CF: Power Management Unit Configuration<sup>1,2,3</sup>

| Bit   | 7     | 6       | 5     | 4      | 3      | 2      | 1      | 0      |

|-------|-------|---------|-------|--------|--------|--------|--------|--------|

| Name  | SLEEP | SUSPEND | CLEAR | RSTWK  | RTCFWK | RTCAWK | PMATWK | CPT0WK |

| Туре  | W     | W       | W     | R      | R/W    | R/W    | R/W    | R/W    |

| Reset | 0     | 0       | 0     | Varies | Varies | Varies | Varies | Varies |

SFR Page = 0x0; SFR Address = 0xB5

| Bit | Name    | Description                                                     | Write                                                                                                 | Read                                                               |

|-----|---------|-----------------------------------------------------------------|-------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------|

| 7   | SLEEP   | Sleep Mode Select                                               | Writing 1 places the device in Sleep Mode.                                                            | N/A                                                                |

| 6   | SUSPEND | Suspend Mode Select                                             | Writing 1 places the device in Suspend Mode.                                                          | N/A                                                                |

| 5   | CLEAR   | Wake-up Flag Clear                                              | Writing 1 clears all wake-<br>up flags.                                                               | N/A                                                                |

| 4   | RSTWK   | Reset Pin Wake-up Flag                                          | N/A                                                                                                   | Set to 1 if a glitch <u>has</u><br>been detected on RST.           |

| S   | RTCFWK  | SmaRTClock Oscillator<br>Fail Wake-up Source<br>Enable and Flag | 0: Disable wake-up on<br>SmaRTClock Osc. Fail.<br>1: Enable wake-up on<br>SmaRTClock Osc. Fail.       | Set to 1 if the SmaRT-<br>Clock Oscillator has failed.             |

| 2   | RTCAWK  | SmaRTClock Alarm<br>Wake-up Source Enable<br>and Flag           | 0: Disable wake-up on<br>SmaRTClock Alarm.<br>1: Enable wake-up on<br>SmaRTClock Alarm.               | Set to 1 if a SmaRTClock<br>Alarm has occurred.                    |

| 1   | PMATWK  | Port Match Wake-up<br>Source Enable and Flag                    | 0: Disable wake-up on<br>Port Match Event.<br>1: Enable wake-up on<br>Port Match Event.               | Set to 1 if a Port Match<br>Event has occurred.                    |

| 0   | CPTOWK  | Comparator0 Wake-up<br>Source Enable and Flag                   | 0: Disable wake-up on<br>Comparator0 rising edge.<br>1: Enable wake-up on<br>Comparator0 rising edge. | Set to 1 if Comparator0<br>rising edge caused the last<br>wake-up. |

Notes:

1. Read-modify-write operations (ORL, ANL, etc.) should not be used on this register. Wake-up sources must be re-enabled each time the SLEEP or SUSPEND bits are written to 1.

2. The Low Power Internal Oscillator cannot be disabled and the MCU cannot be placed in Suspend or Sleep Mode if any wake-up flags are set to 1. Software should clear all wake-up sources after each reset and after each wake-up from Suspend or Sleep Modes.

3. PMU0 requires two system clocks to update the wake-up source flags after waking from Suspend mode. The wake-up source flags will read '0' during the first two system clocks following the wake from Suspend mode.

# SFR Definition 16.1. CRC0CN: CRC0 Control

| Bit   | 7 | 6 | 5 | 4 | 3        | 2       | 1 | 0       |

|-------|---|---|---|---|----------|---------|---|---------|

| Name  |   |   |   |   | CRC0INIT | CRC0VAL |   | CRC0PNT |

| Туре  | R | R | R | R | R/W      | R/W     | R | R/W     |

| Reset | 0 | 0 | 0 | 1 | 0        | 0       | 0 | 0       |

#### SFR Page = All; SFR Address = 0x84

| Bit   | Name                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Function                                                                      |  |  |  |  |

|-------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------|--|--|--|--|

| 7:4   | Unused                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | Read = 0001b; Write = Don't Care.                                             |  |  |  |  |

| 3     | CRC0INIT                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | CRC0 Result Initialization Bit.                                               |  |  |  |  |

|       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | Writing a 1 to this bit initializes the entire CRC result based on CRC0VAL.   |  |  |  |  |

| 2     | CRC0VAL                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | CRC0 Set Value Initialization Bit.                                            |  |  |  |  |

|       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | This bit selects the set value of the CRC result.                             |  |  |  |  |

|       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 0: CRC result is set to 0x00000000 on write of 1 to CRC0INIT.                 |  |  |  |  |

|       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 1: CRC result is set to 0xFFFFFFF on write of 1 to CRC0INIT.                  |  |  |  |  |

| 1     | Unused                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | Read = 0b; Write = Don't Care.                                                |  |  |  |  |

| 0     | CRC0PNT                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | CRC0 Result Pointer.                                                          |  |  |  |  |

|       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | Specifies the byte of the CRC result to be read/written on the next access to |  |  |  |  |

|       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | CRC0DAT. The value of these bits will auto-increment upon each read or write. |  |  |  |  |

|       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 0: CRC0DAT accesses bits 7–0 of the 16-bit CRC result.                        |  |  |  |  |

|       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 1: CRC0DAT accesses bits 15–8 of the 16-bit CRC result.                       |  |  |  |  |

| Note: | ote: Upon initiation of an automatic CRC calculation, the three cycles following a write to CRC0CN that initiate a CRC operation must only contain instructions which execute in the same number of cycles as the number of bytes in the instruction. An example of such an instruction is a 3-byte MOV that targets the CRC0FLIP register. When programming in C, the dummy value written to CRC0FLIP should be a non-zero value to prevent the compiler from generating a 2-byte MOV instruction. |                                                                               |  |  |  |  |

# SFR Definition 16.4. CRC0AUTO: CRC0 Automatic Control

| Bit   | 7      | 6       | 5 | 4           | 3 | 2 | 1 | 0 |

|-------|--------|---------|---|-------------|---|---|---|---|

| Name  | AUTOEN | CRCDONE |   | CRC0ST[4:0] |   |   |   |   |

| Туре  | R/W    | R       | R | R/W         |   |   |   |   |

| Reset | 0      | 1       | 0 | 0           | 0 | 0 | 0 | 0 |

#### SFR Page = All; SFR Address = 0x9E

| Bit | Name        | Function                                                                                                                                                                                                                                |

|-----|-------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7   | AUTOEN      | Automatic CRC Calculation Enable.                                                                                                                                                                                                       |

|     |             | When AUTOEN is set to 1, any write to CRC0CN will initiate an automatic CRC starting at Flash sector CRC0ST and continuing for CRC0CNT sectors.                                                                                         |

| 6   | CRCDONE     | CRCDONE Automatic CRC Calculation Complete.                                                                                                                                                                                             |

|     |             | Set to 0 when a CRC calculation is in progress. Code execution is stopped during a CRC calculation; therefore, reads from firmware will always return 1.                                                                                |

| 5   | Unused      | Read = 0b; Write = Don't Care.                                                                                                                                                                                                          |

| 4:0 | CRC0ST[4:0] | Automatic CRC Calculation Starting Block.                                                                                                                                                                                               |

|     |             | These bits specify the Flash block to start the automatic CRC calculation. The starting address of the first Flash block included in the automatic CRC calculation is CRC0ST x Block Size.<br><b>Note:</b> The block size is 256 bytes. |

## **19.4.** Special Function Registers for Selecting and Configuring the System Clock

The clocking sources on C8051F99x-C8051F98x devices are enabled and configured using the OSCICN, OSCICL, OSCXCN and the SmaRTClock internal registers. See Section "20. SmaRTClock (Real Time Clock)" on page 197 for SmaRTClock register descriptions. The system clock source for the MCU can be selected using the CLKSEL register. To minimize active mode current, the oneshot timer which sets Flash read time should by bypassed when the system clock is greater than 10 MHz. See the FLSCL register description for details.